M.2 NVME/M.2 SATA SSD PCIE X4

2024-03-14 22:02:08

M.2 NVME 80MM SSD PCIE X4 ADAPT

2024-03-14 22:02:08

M.2 NVMe SSD PCIe 4.0 Adapt w/HS

2024-03-14 22:02:08

M.2 NVME 110MM SSD PCIE X4

2024-03-14 22:02:08

6 6 Pin PCIe to (2) SATA 15 Pin

2024-03-14 22:02:05

8-CH RELAY & 8-CH IDI PCIE CARD

2024-03-14 20:33:38

實(shí)時(shí)傳遞到上位機(jī)采集緩沖區(qū)。在超帶寬視頻采集情況下,支持采集丟幀操作,后續(xù)視頻可以正常采集。視頻采集與顯示子系統(tǒng)使用高效的PCIe H2C DMA引擎讀取上位機(jī)顯示緩沖區(qū)的視頻幀,存儲到視頻顯示隊(duì)列中

2024-03-13 13:59:45

=512-byte3. DMA TransferLength = 4MBC2H& H2C DMA性能:1. PCIe3.0 x16,C2H DMA和H2C DMA速度大于13.5GB

2024-03-07 13:54:29

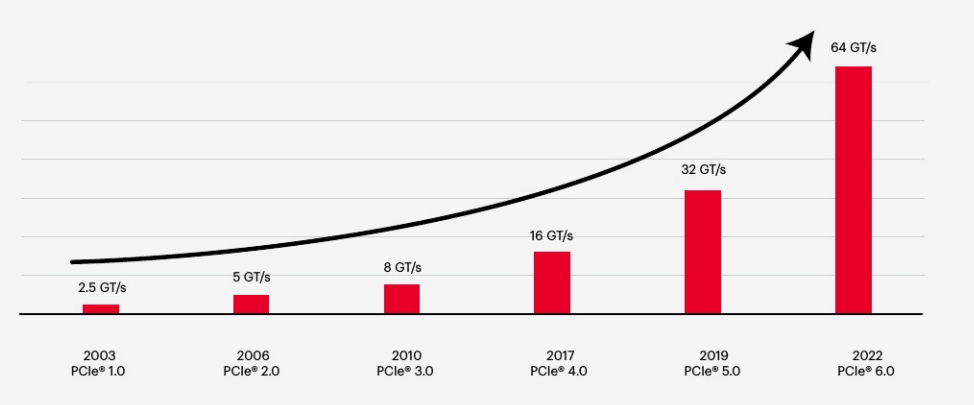

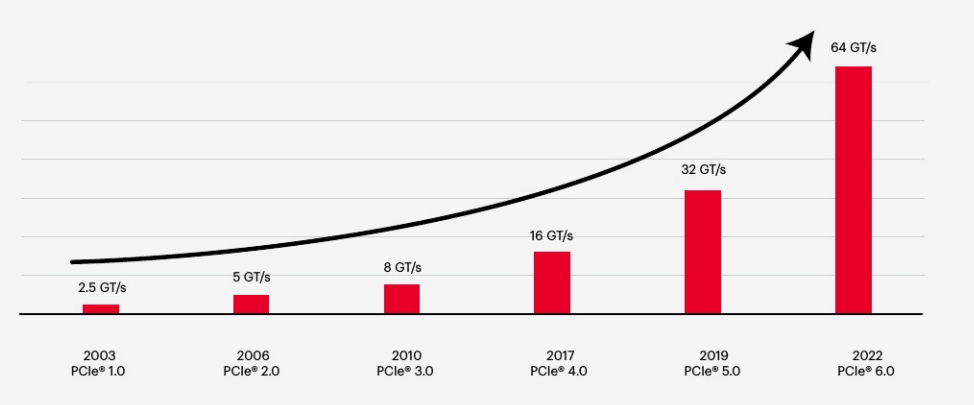

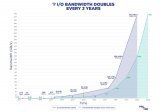

迫切。 一、PCIe 5.0 /6.0技術(shù)升級 1)信號速率方面 從PCIe 3.0、4.0、5.0 到 6.0,數(shù)據(jù)速率翻倍遞增,6.0支持64GT/s,16路雙向傳輸帶寬可達(dá)256GB

2024-03-06 10:35:33 138

138

消息透露,Nextorage 作為“索尼親兒子”首次發(fā)布了PCIe 5.0固態(tài)硬盤產(chǎn)品。其中,1TB容量版售價(jià)為239.99美元(約合人民幣1728元),2TB版本則為399.99美元(約合人民幣2880元)。

2024-03-01 11:47:57 133

133 PE047是一款PCIE擴(kuò)展卡,擴(kuò)展出1個(gè)HDMI顯示、2個(gè)SDI顯示和1個(gè)USB3.0HUB。強(qiáng)勁芯片功能強(qiáng)悍可實(shí)現(xiàn)一機(jī)多顯,穩(wěn)定傳輸,散熱快更穩(wěn)定。 USB-A3.0接口

2024-02-29 13:53:03

我現(xiàn)在的d2000和28dr已經(jīng)是pcie物理互聯(lián)了,我該怎么樣去通過pcie來在這兩個(gè)板子上進(jìn)行數(shù)據(jù)的傳輸呢?

2024-02-27 16:34:57

新品發(fā)布Newproductsrelease繼推出PCIe接口設(shè)備TP1013和TP1018新品之后,同星智能PCIe系列產(chǎn)品TP1026P正式亮相!這款產(chǎn)品不僅支持CANFD總線轉(zhuǎn)PCIe接口

2024-02-19 14:00:26 90

90

芯和半導(dǎo)體在剛剛結(jié)束的DesignCon 2024大會上正式發(fā)布了針對下一代電子系統(tǒng)的SI/PI/多物理場分析EDA解決方案,包括針對Chiplet先進(jìn)封裝及板級系統(tǒng)的信號完整性、電源完整性、電磁

2024-02-04 16:48:49 209

209 芯和半導(dǎo)體在剛剛結(jié)束的DesignCon2024大會上正式發(fā)布了針對下一代電子系統(tǒng)的SI/PI/多物理場分析EDA解決方案,包括針對Chiplet先進(jìn)封裝及板級系統(tǒng)的信號完整性、電源完整性、電磁仿真

2024-02-02 17:19:43 182

182

電子發(fā)燒友網(wǎng)報(bào)道(文/周凱揚(yáng))2022年1月,PCI-SIG發(fā)布了PCIe 6.0規(guī)范,正式拉開了接口帶寬大幅升級的序幕。然而,在規(guī)范公布的兩年時(shí)間里,也已經(jīng)更新了6.0.1和6.1版本,PCIe

2024-01-31 09:02:24 2200

2200 什么是PCIe?PCIe有什么用途?什么是PCIe通道,x1、x4、x8和x16是什么意思?PCIe 5.0有何不同? PCI-Express(peripheral component

2024-01-30 16:09:25 503

503 云計(jì)算機(jī)、高性能計(jì)算機(jī)、nVME存儲、以太網(wǎng)絡(luò)及AI加速器應(yīng)用。 原理方框圖典型特征◆符合PCIe 3.0◆PCIe 3.0相位抖動:0.48ps RMS(典型高頻)◆兼容LVDS輸出◆電源電壓為

2024-01-24 17:31:16

產(chǎn)品摘要正運(yùn)動技術(shù)PCIE464運(yùn)動控制卡,提供高效的工業(yè)運(yùn)動控制解決方案。用戶可直接將PCIE464嵌入標(biāo)準(zhǔn)PC機(jī)快速實(shí)現(xiàn)高性能的EtherCAT運(yùn)動控制功能。在“PC+運(yùn)動控制卡”的模式下,可

2024-01-24 09:48:21

PCIe-6328一塊8口USB3.0主控卡,專為工業(yè)自動化和機(jī)器視覺相關(guān)應(yīng)用設(shè)計(jì)。USB3.0或稱作高速USB,是一項(xiàng)新興總線技術(shù),10倍于USB2.0的傳輸速度,尤其適用于高速數(shù)據(jù)存儲和圖像設(shè)備

2024-01-22 17:05:01 142

142

PCIe-6328 是一塊 8 口 USB 3.0主控卡,專為工業(yè)自動化和機(jī)器視覺相關(guān)應(yīng)用設(shè)計(jì)。USB 3.0或稱作高速USB,是一項(xiàng)新興總線技術(shù),10倍于USB2.0的傳輸速度,尤其適用于高速數(shù)據(jù)

2024-01-22 17:00:01

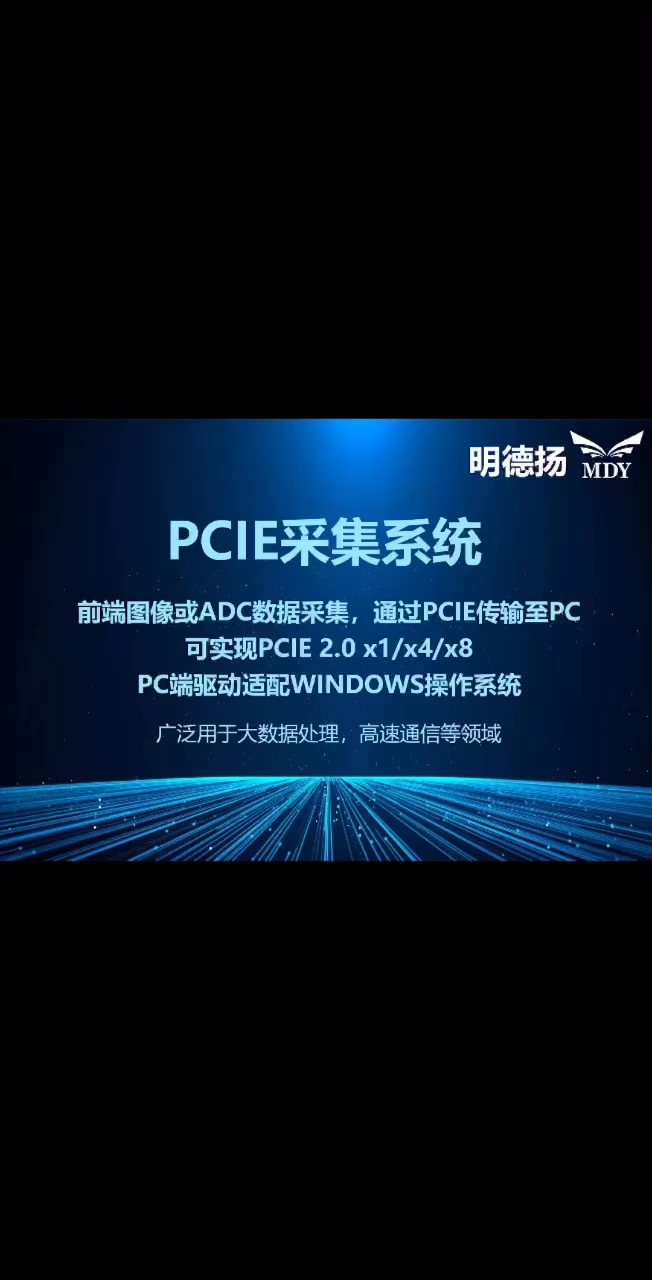

隨著PCIE版本的不斷升級,其應(yīng)用范圍也越來越廣泛。除了傳統(tǒng)的顯卡、網(wǎng)卡、聲卡等設(shè)備外,SSD、USB控制器、Thunderbolt接口等設(shè)備也開始支持PCIE接口。

2024-01-21 10:25:10 577

577 1個(gè)PCIe X4連接器電口,接插件為molex接口,在使用中可支持光纖傳輸。1個(gè)PCIe X8 標(biāo)準(zhǔn)接口,支持V2.0,V3.0規(guī)范,1個(gè)千兆網(wǎng)絡(luò)。

2024-01-09 11:07:59 216

216

要求卻是85ohm的標(biāo)準(zhǔn),那么這個(gè)時(shí)候我們的線路阻抗到底是按照85還是100歐姆會比較好呢?

如下是關(guān)于線路阻抗的一些芯片要求或者協(xié)議要求。

總結(jié)起來就是Pcie3.0以下是100ohm

2023-12-22 15:14:41

自2003年推出以來,PCIe發(fā)展至今已經(jīng)從最初的1.0升級到了6.0,本文則為大家簡單介紹一下PCIe標(biāo)準(zhǔn)的演進(jìn)歷史以及各代PCIe標(biāo)準(zhǔn)之間的主要差異。

2023-12-14 16:38:08 1525

1525

多路PCIe3.0的單CPU通用工作站

2023-11-23 09:38:33 157

157

隨著英特爾Alder Lake CPU的發(fā)布,以及AMD 7000 Ryzen CPU的即將發(fā)布,PCIe 5.0 硬件終于成為現(xiàn)實(shí)。但什么是 PCIe 5.0?

2023-11-18 16:48:14 1298

1298

生成工程路徑在剛才生成IP工程目錄下的..\\\\ipcore\\\\pcie_test\\\\pnr\\\\example_design,只需要打開該目錄下的pango_pcie_top.pds工程

2023-11-17 14:35:30

ORI-D3R600服務(wù)器-多路PCIe3.0的雙CPU通用工作站

2023-11-15 11:39:35 221

221

與其他設(shè)備共享帶寬。這有助于減少延遲并提高性能。

熱插拔支持: PCIe接口支持熱插拔,允許用戶在計(jì)算機(jī)運(yùn)行時(shí)添加或移除PCIe設(shè)備,而不需要重新啟動計(jì)算機(jī)。

廣泛應(yīng)用: PCIe接口廣泛用于連接圖形卡

2023-11-02 09:31:28

PCIe PHY,其中?種為pcie3.0PHY,含2個(gè)Port共4個(gè)Lane,另?種是pcie2.0的PHY有3個(gè),每個(gè)都是2.0 1Lane,跟SATA和USB combo使?。pcie3.0 PHY的4Lane可以根據(jù)實(shí)際需求拆分使?,拆分后需要合理配置對應(yīng)的控制器。

2023-11-02 09:22:37 525

525

本文我們將向大家介紹PCIe引腳定義以及PCIe協(xié)議層。

2023-09-26 11:39:14 5629

5629

在PPSSPP社區(qū)和賽昉科技軟件團(tuán)隊(duì)的共同努力下,PPSSPP 9月最新發(fā)布的1.16版本中增加了基于IR的全新RISC-V JIT后端,現(xiàn)在各位游戲愛好者們可以在VisionFive 2上玩PSP

2023-09-11 17:17:26

? 我們在進(jìn)行PCIe RTL仿真時(shí),由于PCIe ltssm協(xié)商過程比較復(fù)雜,導(dǎo)致PCIe ltssm進(jìn)入L0狀態(tài)所花費(fèi)的時(shí)間比較長(大概在20~60分鐘,因代碼復(fù)雜度、服務(wù)器性能、PCIe速率

2023-08-17 09:42:22 721

721

本文檔旨在提供關(guān)于將PCIe接口集成到基于AMBA的片上系統(tǒng)(SoC)的指導(dǎo)。

假設(shè)PCIe接口通過基于AXI或ACE協(xié)議的互連連接到SoC的其余部分。

讀者應(yīng)熟悉PCIe、AMBA AXI

2023-08-17 07:25:03

力科104Xs-A示波器LeCroy 104Xs-A 1G帶寬 5G采樣率力科104Xs-A示波器是一款體積小,采用強(qiáng)大的處理器,可以比任何競爭對手

2023-08-08 11:32:06

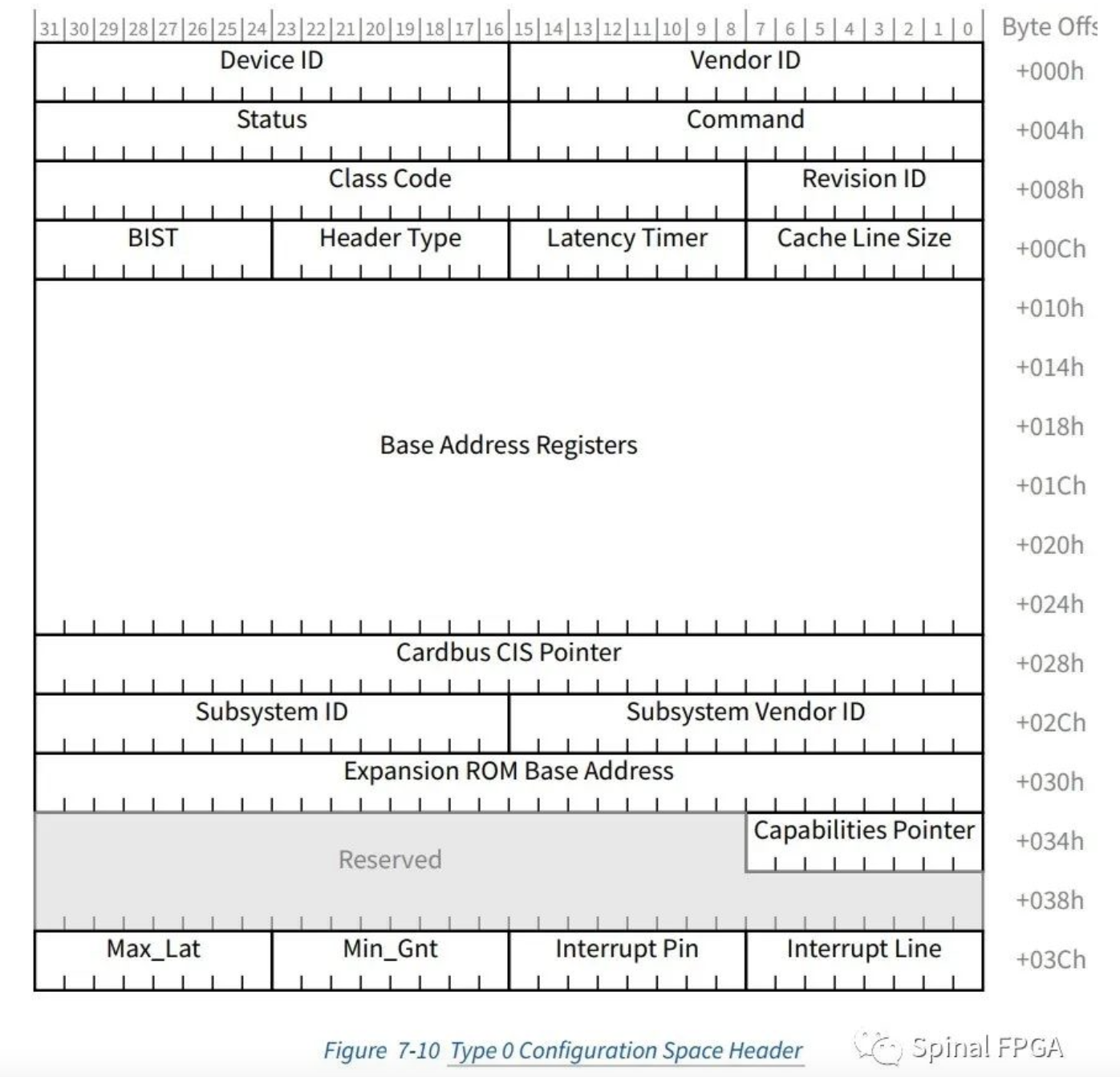

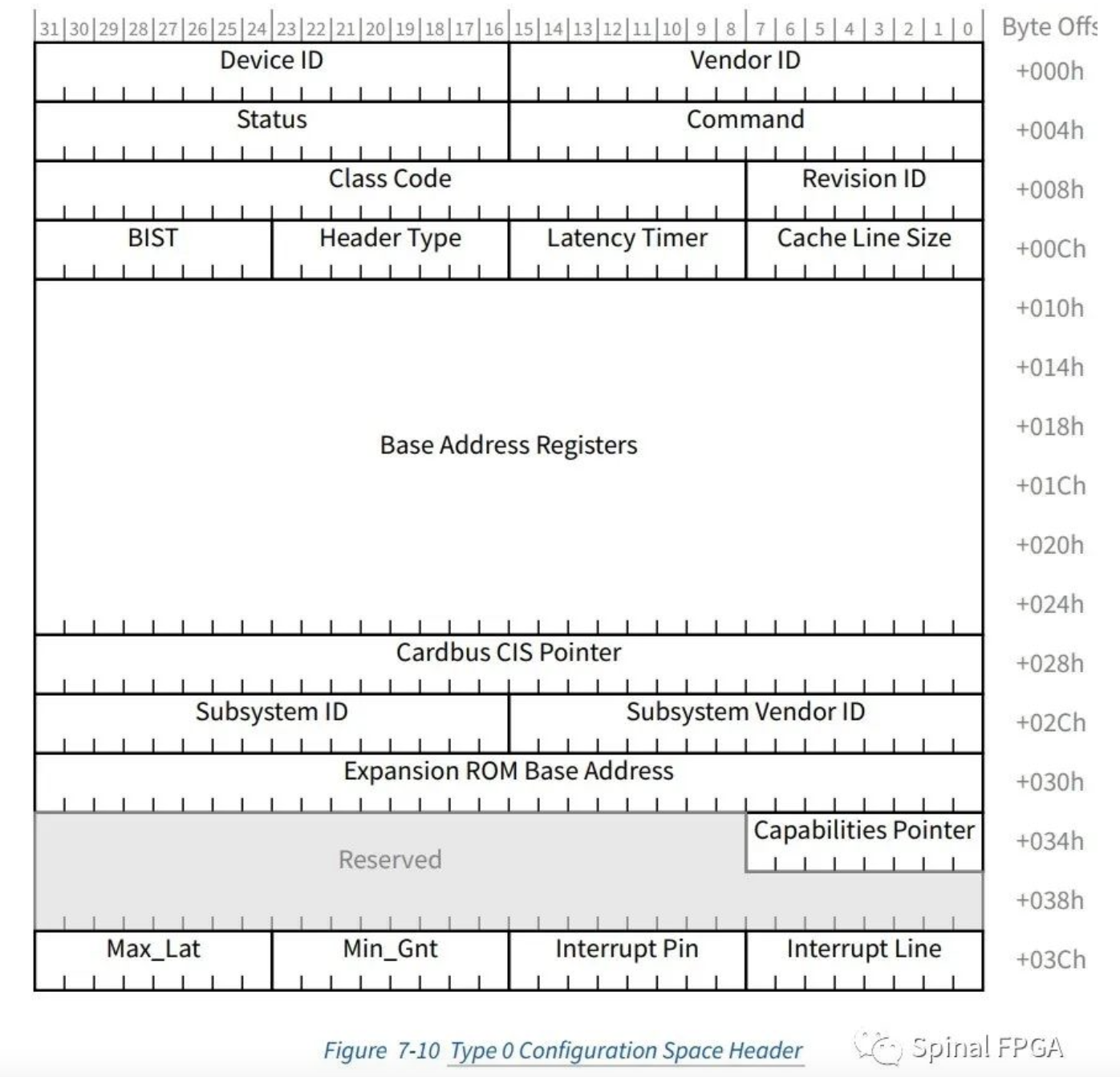

訪問 PCI/PCIe 設(shè)備的流程 PCI/PCIe 設(shè)備的配置信息 PCI/PCIe 設(shè)備上有配置空間(配置寄存器),用來表明自己"需要多大的地址空間"。 注意,這是 PCI/PCIe 地址空間

2023-07-30 09:44:54 941

941 電子發(fā)燒友網(wǎng)站提供《MegaRAID SAS 9341-8i/9341-4i PCIe 3.0 SATA+SAS RAID控制器.pdf》資料免費(fèi)下載

2023-07-29 09:49:02 0

0 各代 PCIe 標(biāo)準(zhǔn)之間的主要差異。 PCIe 3.0 PCIe2.0的傳輸速率為5 GT/s,但由于8b/10b編碼方案的開銷占比為20%,因此單lane的傳輸帶寬為4Gb/s。PCIe 3.0及以后

2023-07-26 08:05:01 867

867

要充分發(fā)揮PCIe 4.0的優(yōu)勢,需要具備兼容PCIe 4.0的主板和設(shè)備。如果你的設(shè)備只支持PCIe 3.0,那么你將無法享受到PCIe 4.0的速度和帶寬優(yōu)勢。

2023-07-18 15:10:30 18121

18121 型號:KL-040SD【變波+脫氣模式】功率:240W 頻率:40KHz容量:10L品牌:Kelisonic/科力超聲科力超聲支持定制各種雙頻超聲波清洗機(jī),高頻超聲波清洗器產(chǎn)品特點(diǎn)

2023-07-13 19:04:29

近二十年來,PCI Express?(PCIe?)規(guī)范一直是計(jì)算領(lǐng)域的首選互連標(biāo)準(zhǔn)。從2010年發(fā)布的PCIe 3.0開始,每一代新標(biāo)準(zhǔn)的信號傳輸速率都比上一代增加一倍,而且在滿足各種用例的帶寬需求方面遠(yuǎn)遠(yuǎn)領(lǐng)先于市場。

2023-07-11 16:47:48 392

392

華為常務(wù)董事、華為云CEO張平安以“AI重塑千行百業(yè)”為主題發(fā)表了開幕辭,宣布正式發(fā)布了華為盤古Model 3.0。

2023-07-07 18:02:11 1931

1931 7月7日,華為云正式發(fā)布盤古大模型3.0,建立業(yè)界首個(gè)萬卡AI集群,欲打造世界AI另一極!盤古大模型3.0的發(fā)布引發(fā)中國科技圈熱議,業(yè)內(nèi)人士認(rèn)為,這展現(xiàn)出了華為“遇強(qiáng)則強(qiáng)、置之死地而后生”的頑強(qiáng)一面,既是華為對于技術(shù)追求的一種執(zhí)念,更是在中美AI科技戰(zhàn)升級背景下的未雨綢繆。

2023-07-07 16:08:57 1405

1405 今天,華為開發(fā)者大會2023(Cloud)在中國東莞正式揭開帷幕。在下午舉行的大會主題演講中,華為常務(wù)董事、華為云CEO張平安重磅發(fā)布盤古大模型3.0,將圍繞“行業(yè)重塑”“技術(shù)扎根”“開放同飛”三大創(chuàng)新方向,持續(xù)打造核心競爭力,為行業(yè)客戶、伙伴及開發(fā)者提供更好的服務(wù)。

2023-07-07 15:35:44 799

799

PCIe是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),自2003年推出以來,已經(jīng)成為服務(wù)器(Server)和PC上的重要接口。今天為大家簡單介紹一下PCIe的發(fā)展歷史以及它的工作原理。 一、PCIe的由來

2023-07-04 18:15:03 9759

9759 最近在研究cocotbext-pcie的實(shí)現(xiàn),對于學(xué)習(xí)PCIe還是挺有幫助的,陸陸續(xù)續(xù)做個(gè)總結(jié),有時(shí)間也會在SpinalHDL下實(shí)現(xiàn)類似的方針功能。

2023-07-03 17:47:34 2282

2282

PCIe 7.0規(guī)范的數(shù)據(jù)傳輸速率將再次倍增,達(dá)到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一個(gè)PCIe 7.0 x16通道可以支持512 GB

2023-06-25 10:48:38 506

506

??編 者 按? ? ????讀cocotbext-pcie源碼,有部分牽涉到數(shù)據(jù)鏈路層。雖然自工作以來接觸到PCIe還是蠻多的,但一般往往專注在TLP層,對于數(shù)據(jù)鏈路層還是接觸的比較少的。PCIe

2023-06-25 10:31:17 1457

1457

PCIe 7.0規(guī)范的數(shù)據(jù)傳輸速率將再次倍增,達(dá)到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一個(gè)PCIe 7.0 x16通道可以支持512 GB

2023-06-21 11:32:14 494

494

本文是今年發(fā)布在DesignCon的文章,介紹了如何進(jìn)行仿真和設(shè)計(jì),以及過孔對系統(tǒng)的影響等等,最后結(jié)合仿真與測試,一并對比了前仿真、后仿真以及測量的結(jié)果,非常有參考意義,值得學(xué)習(xí)。

2023-06-19 11:14:58 875

875

PCIe M.2 接口規(guī)范

2023-06-19 10:02:30 18

18 由PCI-SIG發(fā)布的PCIe板卡結(jié)構(gòu)規(guī)范。Revision 4.0 Version 0.9.

2023-06-19 09:59:44 5

5 在我們的 S32R45 板上,PCIe_1 的 REFCLK 已經(jīng)連接到外部 100MHz 時(shí)鐘,并且在 uboot 中設(shè)置了 setenv hwconfig "pcie

2023-06-12 08:44:32

我是一名PCIe新手,想了解以下問題:

1、如何測試PCIe?

2、如何讀寫PCIe(兩塊開發(fā)板通過PCIe線互連,分別配置為RC和EP)?

3.如何支持NTB?

2023-06-12 06:05:51

大家好,

我正在 imx8mm 上以端點(diǎn)模式測試 PCIe。Linux內(nèi)核是4.19。我找不到讓它工作的方法。如果有任何問題,請發(fā)表評論。任何建議都可能有用。

按照內(nèi)核文檔,我應(yīng)該能夠在 /sys

2023-06-09 08:23:25

外界推測英偉達(dá)將與聯(lián)發(fā)科共同宣布雙方在 Arm PC 相關(guān)芯片的合作,但聯(lián)發(fā)科發(fā)布公告表示,這個(gè)傳聞純屬外界猜測,聯(lián)發(fā)科不做任何評論。

外界認(rèn)為,根據(jù)聯(lián)發(fā)科的活動邀請函內(nèi)容來看,將展示該公司產(chǎn)品在智能生活、移動通信、車用電子三領(lǐng)域的先進(jìn)技術(shù)應(yīng)用,持續(xù)朝向跨領(lǐng)域、跨平臺產(chǎn)品組合

2023-05-28 08:47:33

PCI Express? 6.0 (PCIe? 6.0) 規(guī)范由 PCI-SIG? 于 2022 年 1 月發(fā)布。最新一代的 PCIe 標(biāo)準(zhǔn)帶來了許多激動人心的新功能,旨在提高計(jì)算密集型工作負(fù)載的性能,包括數(shù)據(jù)中心、 AI/ML 和 HPC 應(yīng)用程序

2023-05-22 17:27:51 4385

4385

UD PCIe-404全國產(chǎn)化信號處理模塊為標(biāo)準(zhǔn)PCIe全高的結(jié)構(gòu),對外支持PCIe3.0×8通信,也可以采用千兆以太網(wǎng)(RJ45連接器)、萬兆以太網(wǎng)(或RapidIO、Aurora,QSFP+

2023-05-21 18:27:41

ZYNQ7045的PCIE電路設(shè)計(jì),板卡使用插針式連接器,引出了PCIE信號,未使用金手指。為了插入機(jī)箱設(shè)計(jì)了擴(kuò)展版,插座與插針對應(yīng),帶有PCIE金手指。目前遇到的問題是,當(dāng)板卡連接擴(kuò)展板使用金手指

2023-05-16 11:07:40

有沒有辦法確認(rèn) i.MX6SX PCIe RX 終端的設(shè)置。我在 i.MX6SX 上看到 PCIe 實(shí)現(xiàn)的 PCIe RX SI 結(jié)果可能表明 RX 終端設(shè)置為 OFF,我正在尋找一種方法來確認(rèn)。PCIe PHY 寄存器沒有內(nèi)存映射,我不確定控制器是否正在更改設(shè)置。

2023-05-12 06:40:33

差分探頭是一種常用的測試儀器,在PCIE測試中也有廣泛的應(yīng)用。本文將介紹差分探頭在PCIE測試上的應(yīng)用及其優(yōu)勢。

2023-05-11 10:54:14 450

450 你好

作為我們在 ls1028 上努力的一部分

我們通過 pcie 將自定義 fpga 連接到 M.2 連接器(通道 C/2 - j16)

相關(guān)uboot日志:

U-Boot

2023-05-09 12:00:30

我們可以將多個(gè) PCIe 設(shè)備 (IC) 連接到一般的單個(gè) PCIe 控制器(在我們的案例中更具體地說是 NXP LS20xxA 處理器)嗎?

例如,將四個(gè)不同的 PCIe x1 設(shè)備 (IC

2023-05-05 07:35:41

我們有將 SATA HDD 連接到 IMX8M Plus 處理器的要求,但我們只有單通道 PCIe 3.0 接口。

您能否建議從PCIe到sat接口的轉(zhuǎn)換器以支持外部硬盤驅(qū)動器(最大 2TB)

2023-05-04 07:19:49

和高達(dá)1080P 100fps的H.265+編碼,具備雙千兆GMAC、三路CAN以及USB3.0/SATA3.0/PCIE3.0等豐富接口,可實(shí)現(xiàn)中控、副駕、頭枕等的多屏異顯及多媒體播放,帶來更多的可

2023-04-17 10:14:03

NPT2010MACOM 的 NPT2010 是一款射頻晶體管,頻率 DC 至 2.2 GHz,功率 50 dBm,功率(W)100 W,飽和功率 50.5 dBm,增益 17 dB。標(biāo)簽:法蘭

2023-04-14 15:36:07

,DTS 在這個(gè)內(nèi)核上有點(diǎn)不同。比較這兩個(gè)內(nèi)核時(shí),特別是與上述錯(cuò)誤“phy init failed”相關(guān)的部分,存在重大差異。具體代碼在phy-driver中,文件phy-fsl-imx8m-pcie

2023-04-14 08:12:05

;●支持 PCIe 3.0 X8 接口,支持與 PC 的高速數(shù)據(jù)交互功能;●支持單獨(dú) 12V 供電(脫離 PC 機(jī));●標(biāo)準(zhǔn) PCIe 全高半長 167.5 *111 mm。三、產(chǎn)品應(yīng)用 ● AD采集

2023-04-13 15:56:21

PCIe接口從2001年發(fā)展至今,在協(xié)議的完整性上已經(jīng)建立足夠高的"護(hù)城河",重新定義一個(gè)接口協(xié)議在性能上超越PCIe,短期內(nèi)一方面沒有企業(yè)會有這個(gè)動力,另一方面技術(shù)的維度,也沒有可預(yù)期的雛形創(chuàng)新。

2023-04-13 11:10:00 2899

2899 IC CLOCK GENERATOR PCIE 42TQFN

2023-04-06 15:33:36

ICMUX/DEMUX2:1PCIE42TQFN

2023-04-06 15:33:30

ICMUX/DEMUX2:1PCIE42TQFN

2023-04-06 15:33:25

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:34:28

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:34:28

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:33:53

我對第 3 代存儲進(jìn)行了測試。但是 LS1046A RDB 指示此存儲是 Gen2。那么,我的問題是:LS1046ARDB 是否支持 PCIE 3.0?

2023-04-06 06:30:54

M31 PCIe 5.0 PHY IP,用于存儲和高帶寬連接 M31 PCIe 5.0 PHY IP為高帶寬應(yīng)用提供高性能、多通道功能和低功耗架構(gòu)。PCIe 5.0 IP支持一系列PCIe

2023-04-03 19:57:12

用于存儲和高帶寬連接的M31 PCIe 4.0 PHY IP–具有16GT/s的最高速度PCIe 4.0 PHY IP M31 PCIe 4.0 PHY IP為高帶寬應(yīng)用提供高性能、多通道

2023-04-03 19:54:58

M31 PCIe 3.1 PHY IP M31 PCIe 3.1 PHY IP為高帶寬應(yīng)用提供高性能、多通道功能和低功耗架構(gòu)。PCIe 3.1 IP支持一系列完整的PCIe 3.1基本應(yīng)

2023-04-03 19:50:56

M31 PCIe 2.1 PHY IP M31 PCIe 2.1收發(fā)器IP提供了一系列完整的PCIe 2.1基本應(yīng)用程序。它符合PIPE 3.0規(guī)范。該IP集成了高速混合信號電路,以支持

2023-04-03 19:47:28

硬件:S32R45 評估板 Crucial 英睿達(dá) P3 1TB PCIe M.2 2280 固態(tài)硬盤我通過一根M.2轉(zhuǎn)PCIE線將SSD連接到EVB的PCI接口,如下圖:EVB板啟動后,在shell界面輸入如下命令:

2023-04-03 08:56:25

PI3PCIE2415EVALBOARD

2023-03-30 11:41:37

PI2PCIE2412-EVALUATIONBOARD1

2023-03-30 11:41:15

PCIE-52P90H

2023-03-29 22:43:17

PCIe 3.0,2 通道(4 通道),差分 2:1 Mux/DeMux。3.3V

2023-03-28 12:41:12

交換機(jī)采用16端口類型配置。它為用戶提供了擴(kuò)展或根據(jù)應(yīng)用程序需求將PCI Express通道扇出。在PCI Express體系結(jié)構(gòu)中,PCIE交換機(jī)轉(zhuǎn)發(fā)已發(fā)布和未發(fā)布的請求以及完成數(shù)據(jù)包同時(shí)在下行或上行方向上,就好像每個(gè)端口上都有一個(gè)虛擬PCI橋在運(yùn)行一樣將端口可視化為虛擬網(wǎng)橋,交換機(jī)在邏輯上可以被視

2023-03-27 10:54:11 1

1 我想為我們的項(xiàng)目使用 LX2080A 處理器,它只有 2 個(gè) USB 3.0 控制器。我的項(xiàng)目需要五個(gè) USB 端口。我想知道我是否可以在其中一個(gè) USB 控制器中使用 USB 集線器 IC(具有

2023-03-27 08:54:43

電子發(fā)燒友App

電子發(fā)燒友App

評論