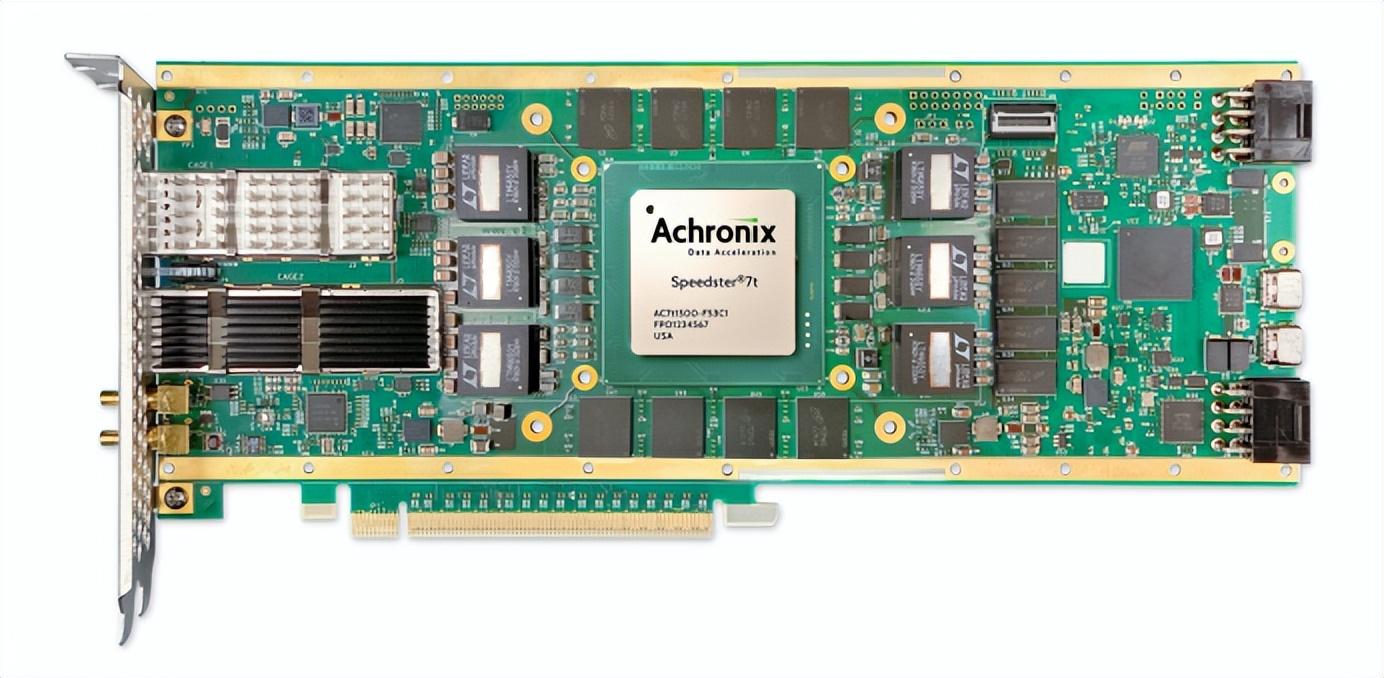

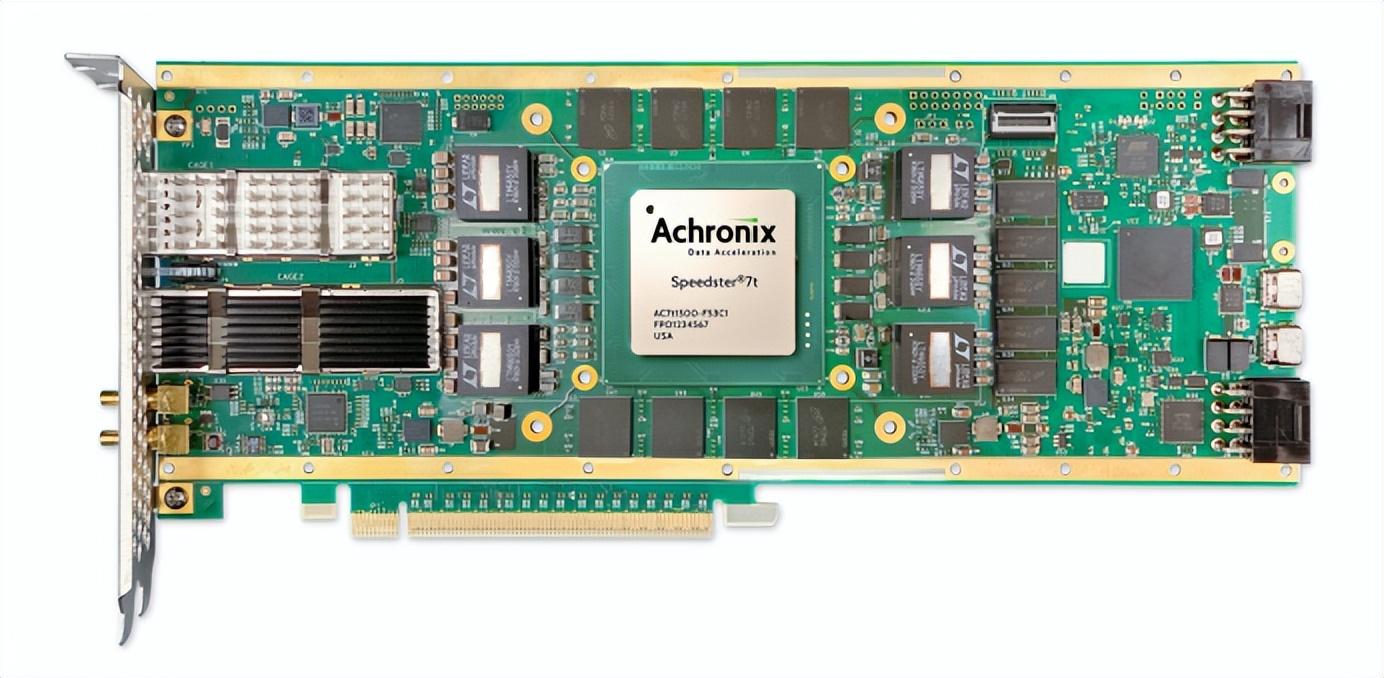

Achronix的Speedster7t支持PCIe Gen5和112G Serdes,而AMD的高端系列Virtex Ultrascale+也僅僅支持到PCIe Gen4,也只在最高端的FPGA中支持到58Gb的GTM,大多數Virtex Ultrascale+僅僅支持32.75Gb的GTY。

2024-03-18 10:55:34 34

34

TINYFPGA AX2

2024-03-14 22:18:36

全球領先的高性能現場可編程門陣列(FPGA)和嵌入式FPGA(eFPGA)半導體知識產權(IP)提供商Achronix Semiconductor公司宣布,該公司將參加由私募股權和風

2024-03-01 10:38:44 585

585 端口例化 問題:如圖上圖所示,計算出圖像數據需要的時鐘為147M而IP核設置的為70M時鐘,計算出數據速率也與IP核配置的不一樣,為什么?產品實際的圖像顯示好像還好。所以實際的視頻1數據輸出所算出的速率與時鐘頻率與lvds_rx輸入的關系速率與時鐘頻率是?

2024-02-26 09:35:47

目前項目需要實現正交解碼功能,但是GPT12用于正交解碼的引腳都沒有連接,所以只能是另辟蹊徑。目前看TC377的用戶手冊中的TIM模塊是可以(28.13.1.3 )External capture

2024-02-04 06:03:31

#2024,為FPGA生態加油,為FPGA社區點贊#...使用IP核時如何進行modelsim仿真

2024-02-02 20:22:37

長期以來,Achronix為不同行業的數據密集型和高帶寬應用提供了創新性的FPGA產品和技術,并幫助客戶不斷打破性能極限。

2023-12-26 18:14:38 591

591

最近在使用貴公司的AD9826芯片,用FPGA進行驅動,目前AD端輸入模擬直流電壓,未來要接光電裝換的輸入裝置。現在用FPGA驅動時,在2-SHA模式下,電平轉換側的值時鐘為FF,驅動AD的方法

2023-12-18 06:28:12

目前,我在設計中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D轉換器AD9683轉換完成后的數據。但是JESD204 IP核的端口很多,我不知道應該如何將AD9683

2023-12-15 07:14:52

本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協議是一種高速串行通信協議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關SRIO協議的詳細介紹網上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結構。

2023-12-12 09:19:08 855

855

我在使用AD9625芯片時,使用4lane 1Gsps時能正常工作。但是用8lane 2.4Gsps時,FPGA內部的IP核會提示無法鎖定,問下各位大神遇到過類似的問題嗎?有什么解決措施嗎?

2023-12-12 08:16:05

星邏智能CEO王海濱表示:“無人機的未來,關鍵在自動化;而無人機能否實現自動化,關鍵在續航和操控。與其花費巨額資金優化電池性能,不如另辟蹊徑在充電硬件和調度軟件上做文章。”星邏智能的三大主力產品就是地面自動化、飛采自動化和數據自動化。

2023-12-08 09:58:12 180

180

我們需要 XILINX FPGA 給 AD9240 提供 8MHz CLK,AD9240 給 FPGA 提供采樣數據和溢出標志,但 FPGA 提供的 CLK 最高 3.3V,請問如何輸入給 AD9240 呢?

2023-12-08 06:54:46

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317 IP5316 2.4A 充電、2.4 A 放電、集成 DCP 功能移動電源 SOC

簡介:

IP5316 是一款集成升壓轉換器、鋰電池充電管理、電池電量指示的多功能電源管理 SOC,為移動電源提供

2023-12-05 09:28:42

的AD9162-FMX-EBZ板子,看到的現象是SYSREF信號一直為高,CGS測試信號不完全拉高,每次重新配置時拉高的lane通道數還不一樣。其界面設置如下圖所示。FPGA的使用是條用的xilinx的JESD204 IP核。

FPGA抓到的SYNC信號與SYSREF信號如下圖所示:

2023-12-05 08:23:30

請問AD9625的寄存器需要如何設置才能打開時間戳的功能?

按照數據手冊我將寄存器0x072設置為0x8B,將0x08A設置為0x22.數據經過Xilinx FPGA的JESD204B IP核,但

2023-12-05 07:33:36

的情況時,總會遇到一些以前未曾接觸過的新內容,這些新內容會讓我們感到陌生和恐懼,不知道該如何下手。

那么今天以xilinx vivado 為例分享學習FPGA 新IP核的正確打開方式。

一、常規

2023-11-17 11:09:22

為你的FPGA設計加加速,NIC、Router、Switch任意實現

優秀的IC/FPGA開源項目(二)-NetFPGA

《優秀的IC/FPGA開源項目》是新開的系列,旨在介紹單一項目,會比《優秀

2023-11-01 16:27:44

開發和驗證 FPGA IP 不僅僅是編寫 HDL,而是需要更多的思考。讓我們來看看如何做吧!

2023-10-17 09:57:19 529

529

開發和驗證 FPGA IP 不僅僅是編寫 HDL,而是需要更多的思考。讓我們來看看如何做吧!

2023-10-16 18:24:42 373

373

本文開源一個FPGA高速串行通信項目:Aurora 8b10b光通信。7 Series FPGAs Transceivers Wizard IP是Xilinx官方7系列FPGA的高速串行收發器,本工程主要是圍繞該IP核采用Vivado提供的例程創建。

2023-10-01 09:48:00 2599

2599

請教一下,我在HLS里面要將以下程序生成IP核,C Synthesis已經做好了,但是在export RTL的時候一直在運行

int sum_single(int A int B

2023-09-28 06:03:53

以下主題概述了Altera的外部內存接口解決方案。

Altera提供最快、最高效、延遲最低的內存接口IP核。Altera的外部存儲器接口IP設計用于方便地與當今更高速的存儲器設備接口。

Altera

2023-09-26 07:38:12

最近出現的 FPGA設計工具和 IP有效減少了計算占用的資源,大大簡化了浮點數據通路的實現。而且,與數字信號處理器不同

2023-09-25 14:42:14 374

374

電子發燒友網站提供《UltraScale FPGA收發器向導v1.7 LogiCORE IP產品指南.pdf》資料免費下載

2023-09-15 10:04:16 0

0 電子發燒友網站提供《基于超大規模架構的FPGA存儲器IP.pdf》資料免費下載

2023-09-13 17:31:54 0

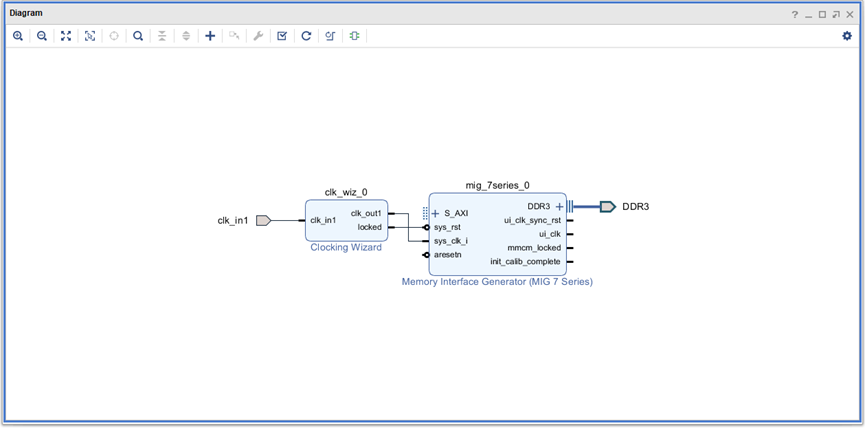

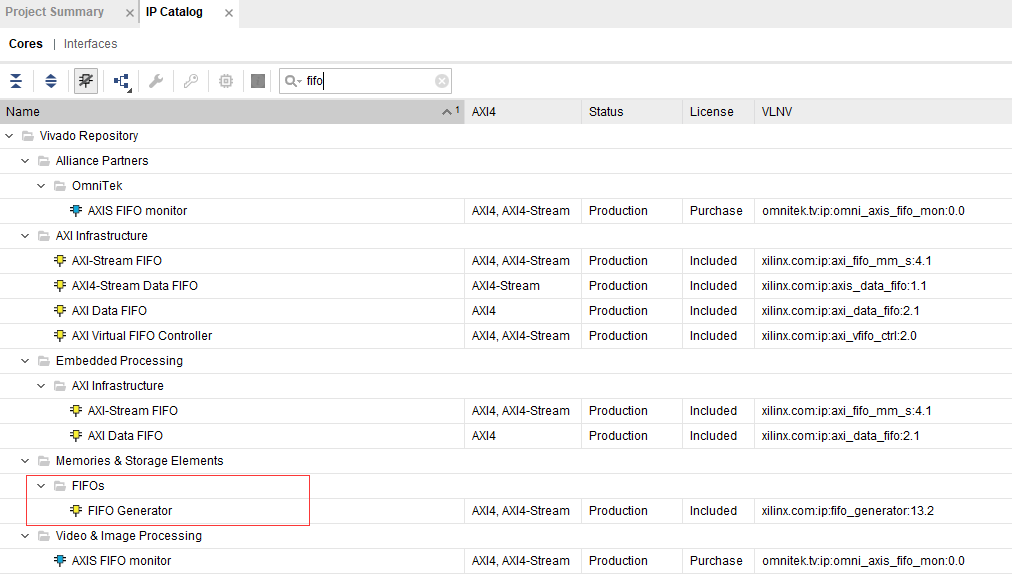

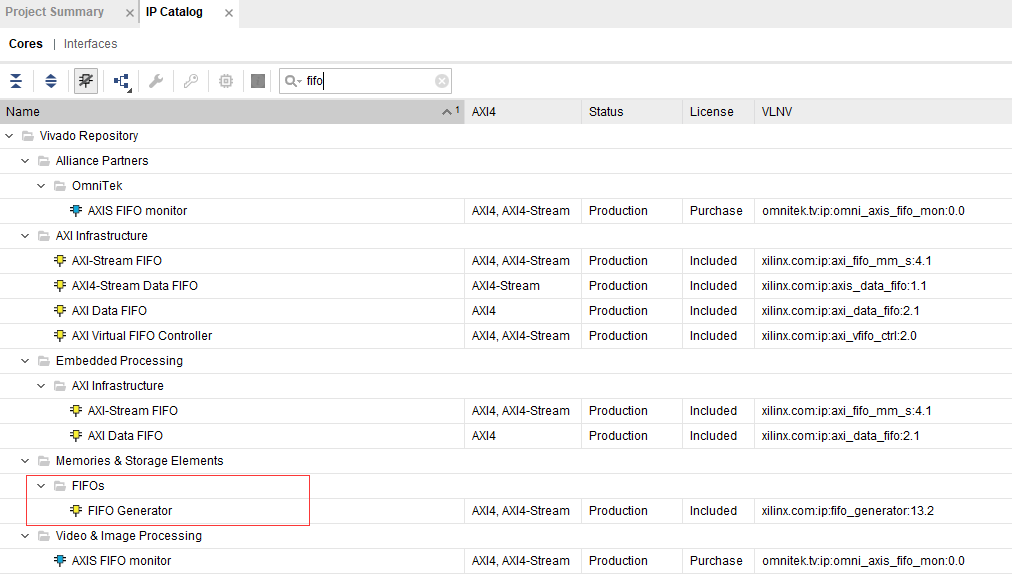

0 上文XILINX FPGA IP之FIFO對XILINX FIFO Generator IP的特性和內部處理流程進行了簡要的說明,本文通過實際例子對該IP的使用進行進一步的說明。本例子例化一個讀數據位寬是寫數據位寬兩倍的FIFO,然后使用讀時鐘頻率:寫時鐘頻率=2:3,進行簡單的FIFO跨時鐘域操作。

2023-09-07 18:31:35 758

758

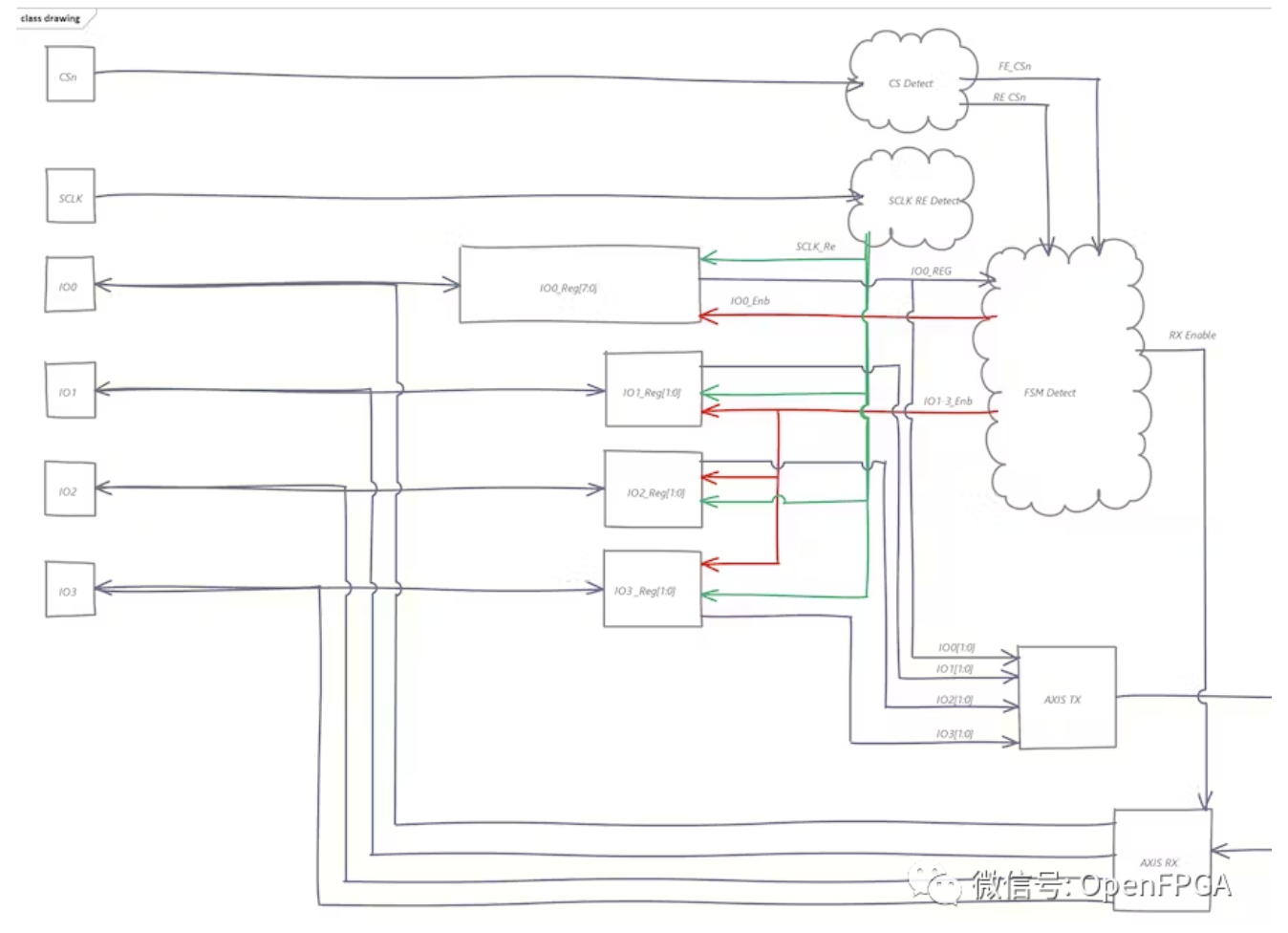

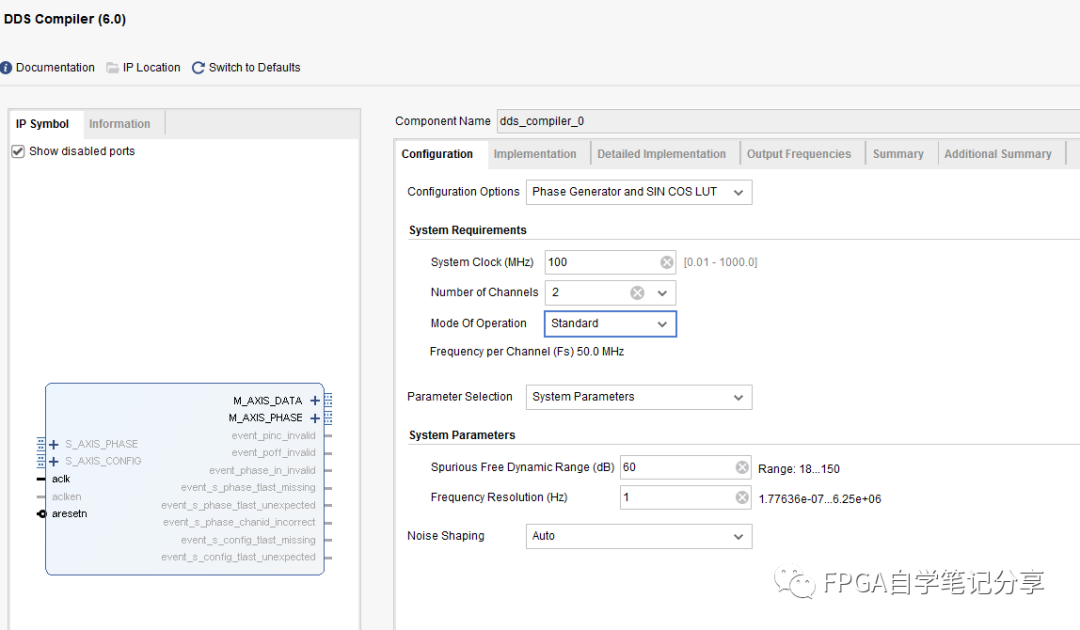

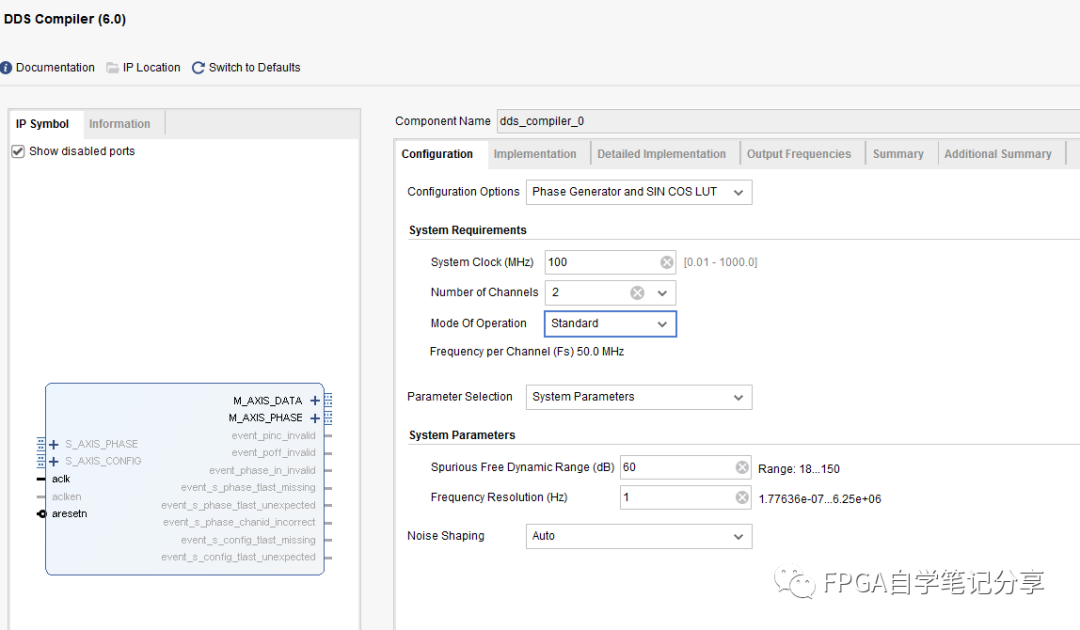

之前的文章對dds ip 的結構、精度、參數、接口進行了詳細的說明,本文通過例化仿真對該IP的實際使用進行演示。本文例化固定模式和可配置模式兩種模式分別例化ip并仿真,說明該IP的應用。

2023-09-07 18:31:06 769

769

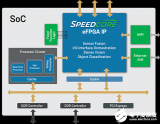

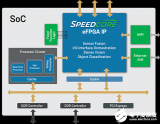

尋求最高集成度的設計人員可以選擇去開發一款包含Speedcore eFPGA IP的單芯片ASIC。然而,在某些應用中,單芯片集成無法實現某些產品靈活性,而這在使用基于chiplet的方案中就有更多靈活性。

2023-09-06 15:12:11 234

234

Xilinx的官方PCIE 2.0 IP核或0 IP核,用來實現PCIE 硬核IP的例化;

使用DMA控制器,實現PCIE DMA操作,并將接口轉換成方便易用的FIFO接口和RAM接口

2023-09-05 14:39:57

本文介紹一個FPGA 開源項目:Micro Blaze最小系統。MicroBlaze是Xilinx提供的一個軟核IP,該軟核是由FPGA片內邏輯資源組成,其功能相當于一個CPU。利用Micro Blaze,設計師可以輕松實現一些FPGA難以實現的復雜算法。

2023-09-01 16:16:21 797

797

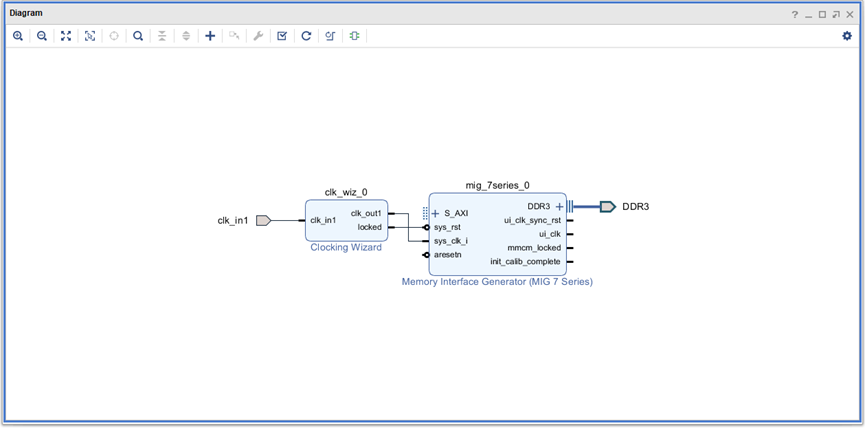

外部存儲器接口( EMIF )通信常用于FPGA和DSP之間的數據傳輸,即將FPGA作為DSP的外部SRAM、或者協同處理器等。Xilinx提供了AXI-EMC IP核,將其掛載到AXI總線用于

2023-08-31 11:25:41 2348

2348

FPGA開發中使用頻率非常高的兩個IP就是FIFO和BRAM,上一篇文章中已經詳細介紹了Vivado FIFO IP,今天我們來聊一聊BRAM IP。

2023-08-29 16:41:49 2602

2602

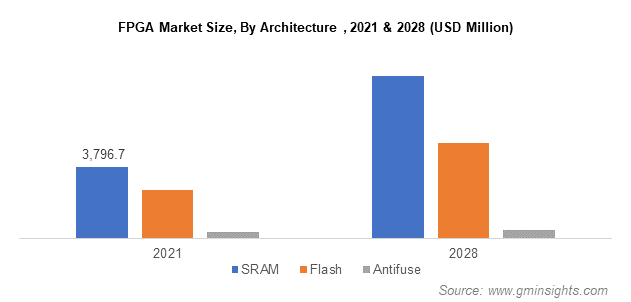

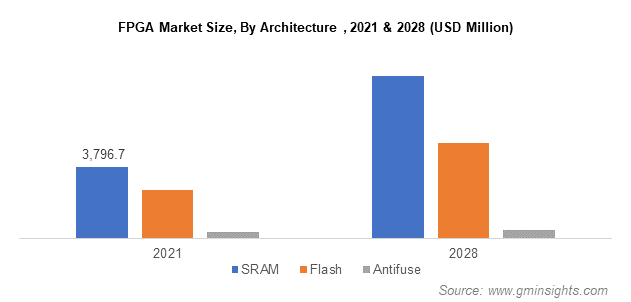

FPGA作為一種邏輯芯片,硬件架構獨特,具有并行性、低延時性和靈活性等特性,應用領域廣泛。FPGA市場主要玩家是英特爾、AMD、萊迪思、Microchip、Achronix等;國內廠商包括復旦

2023-08-25 16:48:48 952

952

,一旦寫入不能再修改或刪除,斷電不丟失。我們知道FPGA只有RAM,因此事實上在 FPGA 中通過 IP 核生成的 ROM 或 RAM掉電內容都會丟失。用 IP 核生成的 ROM 模塊只是提前添加

2023-08-22 15:06:38 1644

1644

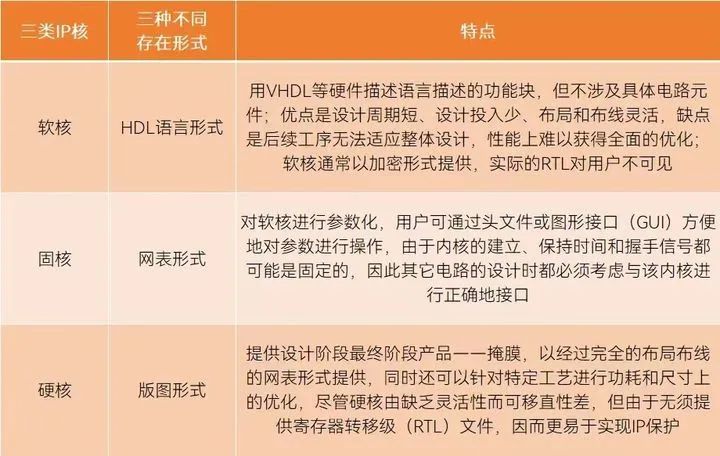

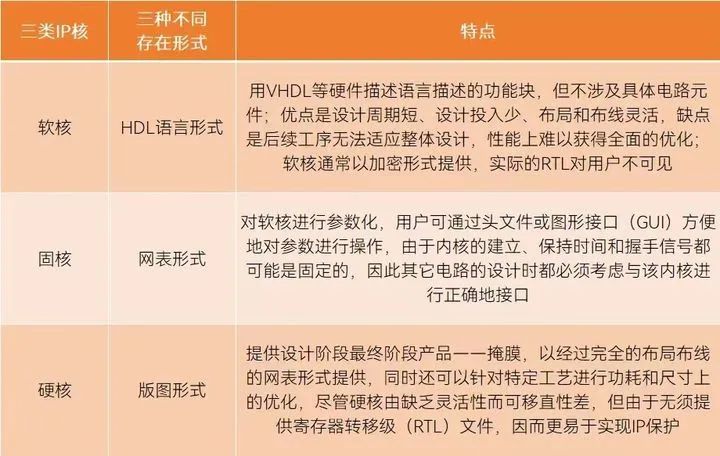

IP(Intellectual Property)是知識產權的意思,半導體行業的IP是“用于ASIC或FPGA中的預先設計好的電路功能模塊”。一些常用的復雜的功能模塊(如FIFO、RAM、FIR

2023-08-22 15:04:43 1523

1523

所搭的IP軟核的通訊協議與總線支持的通訊協議(ICB)不同怎么轉換?

2023-08-17 07:05:35

VIVADO 的官方IP核最少分頻出4MHz多,而32.768KHz太小了,難道只能自己寫分頻器嗎?

謝謝。

2023-08-12 07:03:06

軟核與fpga如何共用一塊flash?

目前fpga開發板上只有一個flash,用nuclei 向軟核中下載程序掉電就不跑了,請問怎么解決?

2023-08-12 06:05:26

CAN IP 可以應用于汽車控制單元和工業網絡等汽車和工業領域,并且 CAN IP 提供多個可配置選項來增加 IP 的靈活性,用戶可以使用此 IP 簡化設計,快速建立起基于 FPGA 的 CAN 通信系統。

2023-08-09 07:18:34

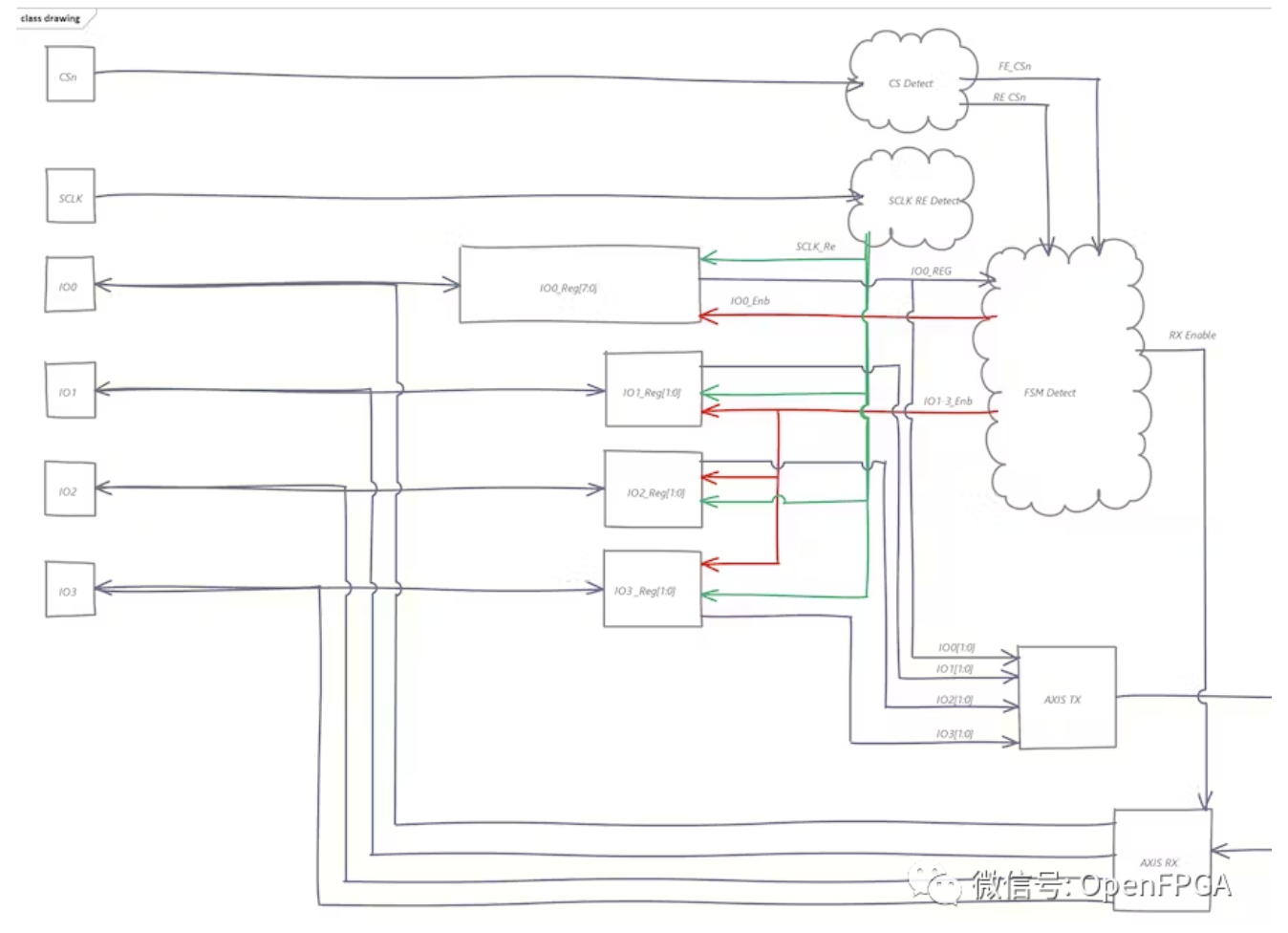

的協議版本。安路的 SPI IP 核具有極高的靈活性,用戶可通過配置 SPIIP 核的主/從類型,時鐘極性,時鐘相位,數據寬度,數據傳輸順序,從設備數量以及部分接收閾值等,使 SPI IP 核兼容市場上常見的 SPI 接口。

2023-08-09 06:19:48

FPGA開發過程中,利用各種IP核,可以快速完成功能開發,不需要花費大量時間重復造輪子。

2023-08-07 15:43:19 440

440

以提供可適用于多種工藝的eFPGA IP解決方案的領先提供商,Achronix還給用戶提供統一的開發工具,既支持其高端FPGA芯片的開發設計,也支持eFPGA IP的開發設計。Achronix近日再次以其

2023-08-02 17:25:05 538

538

SEM IP是一種比較特殊的IP。它的基本工作就是不停地后臺掃描檢測FPGA配置RAM中的數據

2023-07-10 16:40:23 420

420 筆者在校的科研任務,需要用FPGA搭建OFDM通信系統,而OFDM的核心即是IFFT和FFT運算,因此本文通過Xilinx FFT IP核的使用總結給大家開個頭,詳細內容可查看官方文檔PG109。

2023-07-10 10:43:18 630

630

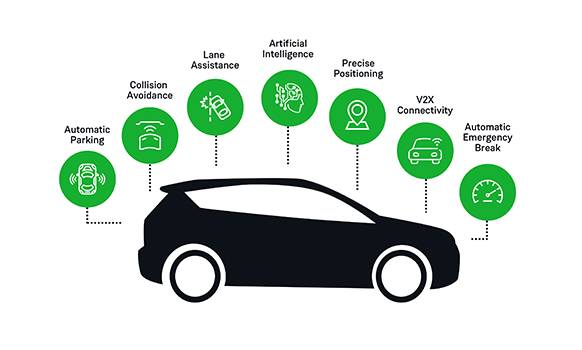

了解eFPGA IP的基礎知識,它的優點,以及為什么它將成為未來先進駕駛輔助系統(ADAS)技術的關鍵要素。

2023-07-10 10:26:38 237

237

FPGA IP核(Intellectual Property core)是指在可編程邏輯器件(Field-Programmable Gate Array,FPGA)中使用的可復用的設計模塊或功能片段。它們是預先編寫好的硬件設計代碼,可以在FPGA芯片上實現特定的功能。

2023-07-03 17:13:28 4086

4086 隨著晶體管尺寸不斷向原子尺度靠近,摩爾定律正在放緩,面對工藝技術持續微縮所增加的成本及復雜性,市場亟需另辟蹊徑以實現低成本前提下的芯片高性能,以TSV(Through Silicon Via,硅通孔)技術為代表的先進封裝成為芯片集成的重要途徑。

2023-06-30 16:39:34 512

512

隨著對高速數據處理的需求呈指數級增長,Achronix始終走在創新的前沿,提供尖端解決方案,以滿足網絡行業不斷演進的需求。通過集成400 GbE速度和PCIe Gen 5.0功能,Achronix

2023-06-29 16:30:13 319

319

1.安裝 IP 核

(1)打開工程,點擊菜單欄中【tools】 下的【IP Compiler】。

IP Compiler

(2)在彈出的 IP Compiler 界面中,選擇【File】下

2023-06-26 10:41:47

一.Xilinx FFT IP介紹

1.總體特性

?FFT IP核支持復數的正逆傅里葉變換,可以實時配置變換的長度

?變換的長度N=2 ^m^ ,m=3-16,即支持的點數范圍為8-65536

2023-06-19 18:34:22

說,上貨。

ROM使用教程

ROM的英文全稱為Read-Only Memory,即只讀存儲器。可以從任意地址上讀取數據,但是不能寫入。那么我們ROM中的數據,就需要我們提前存放進去,在IP核中

2023-06-15 16:57:22

上文XILINX FPGA IP之Clocking Wizard詳解說到時鐘IP的支持動態重配的,本節介紹通過DRP進行MMCM PLL的重新配置。

2023-06-12 18:24:03 5513

5513

鎖相環基本上是每一個fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時鐘資源對xilinx fpga的底層時鐘資源做過說明,但是對于fpga的應用來說,使用Clocking Wizard IP時十分方便的。

2023-06-12 17:42:03 2883

2883

用vivado2019.2建立工程,工程中調用cordic IP核進行atan求解,功能仿真時正常且滿足要求;綜合時正常;實現時報錯提示多重驅動。

如果經cordic計算后的輸出值不用于后續的操作

2023-06-06 17:17:37

S32G2 聚四氟乙烯

S32G2是ip核還是外設?

如果是ip核,是否可以集成到其他SoC中?

謝謝

2023-06-02 08:04:53

的集成電路芯核總稱,是經過反復驗證過的、具有特定功能的宏模塊,與芯片制造工藝無關,可以移植到不同的半導體工藝中。到了SOC階段,IP核設計已成為ASIC電路設計公司和FPGA提供商的重要任務,也是其實

2023-05-30 20:53:24

FPGA硬核與軟核處理器有什么區別和聯系?

2023-05-30 20:36:48

RecurrentGPT 則另辟蹊徑,是利用大語言模型進行交互式長文本生成的首個成功實踐。它利用 ChatGPT 等大語言模型理解自然語言指令的能力,通過自然語言模擬了循環神經網絡(RNNs)的循環計算機制。

2023-05-29 14:34:43 571

571

的移動通信組織3GPP(第三代合作伙伴計劃,3rdGenerationPartnershipProject)。一、不走尋常路的ITU-RITU-R另辟蹊徑,提出了一種

2023-05-29 06:00:00 672

672

A76,為工業控制、汽車、通信等泛工業領域提供CPU IP核;高性能核則基于第三代“香山”(昆明湖)性能提升,對標ARM N2,為數據中心和算力設施等領域提供高性能CPU IP核。

2023-05-28 08:41:37

本文是本系列的第三篇,本文主要介紹FPGA常用運算模塊-乘加器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:17:12 888

888

現今的FPGA設計規模越來越龐大,功能越來越復雜,因此FPGA設計的每個部分都從頭開始著手是不切實際的。

2023-05-22 14:35:00 1327

1327

Memory Access) IP核開發文檔為產品資料“6-開發參考資料\Xilinx官方參考文檔\”目錄下的《pg020_axi_vdma.pdf》。VDMA IP核寄存器列表如下,其中S2MM_xx將視頻

2023-05-03 22:38:12

作者:Pascal Ravillion,Achronix產品營銷高級經理 了解 eFPGA IP 的基礎知識,它的優點,以及為什么它將成為未來先進駕駛輔助系統( ADAS )技術的關鍵要素。 提高

2023-04-26 15:20:24 1302

1302

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

日益增長的數據加速需求對硬件平臺提出了越來越高的要求,FPGA作為一種可編程可定制化的高性能硬件發揮著越來越重要的作用。近年來,高端FPGA 芯片 采用了越來越多的Hard IP去提升FPGA外圍

2023-04-18 11:30:06 299

299 難以在全球化的先進制程中分一杯羹,手機、HPC等需要先進制程的芯片供應受到嚴重阻礙,亟需另辟蹊徑。而先進封裝/Chiplet等技術,能夠一定程度彌補先進制程的缺失,用面積和堆疊換取算力和性能。

2023-04-15 09:48:56 1949

1949 。設計原理FPGA內部沒有FIFO的電路,實現原理為利用FPGA內部的SRAM和可編程邏輯實現。ISE軟件中提供了FIFO的ip core,設計者不需要自己設計可編程邏輯和SRAM組成FIFO。設計者

2023-04-11 20:50:21

不多說,上貨。IP CORE 之 RAM 設計- ISE 操作工具本篇實現基于叁芯智能科技的SANXIN -B02 FPGA開發板,如有入手開發板,可以登錄官方淘寶店購買,還有配套的學習視頻

2023-04-10 16:43:04

不多說,上貨。IP CORE 之 ROM 設計- ISE 操作工具本篇實現基于叁芯智能科技的SANXIN -B02 FPGA開發板,如有入手開發板,可以登錄官方淘寶店購買,還有配套的學習視頻

2023-04-07 20:09:59

將此信號輸出到外部擴展針即可。架構設計和信號說明此模塊命名為pll_test。本設計共有兩個模塊構成:一個反相器和一個PLL模塊(my_pll)。pll_my設計實現本模塊為FPGA內部ip 模塊

2023-04-06 16:04:21

Opencores是一個開源的數字電路設計社區,它提供了免費的開源IP(知識產權)核心,讓工程師和愛好者們可以使用這些IP核心來構建自己的數字電路設計。Opencores的IP核心包括處理器、總線接口、視頻、音頻和其他數字電路組件

2023-04-03 10:39:53 1194

1194

電子發燒友App

電子發燒友App

評論