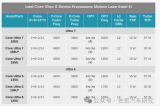

蘋果M3芯片和英特爾芯片在多個(gè)方面存在顯著差異。首先,M3芯片是蘋果自家研發(fā)的,采用了先進(jìn)的制程技術(shù)和架構(gòu)設(shè)計(jì),使其具有出色的計(jì)算性能和多任務(wù)處理能力。而英特爾芯片則以其廣泛的應(yīng)用領(lǐng)域和穩(wěn)定的性能著稱。

2024-03-11 18:21:03 1214

1214 m3芯片相當(dāng)于英特爾幾代cpu 關(guān)于m3芯片相當(dāng)于英特爾幾代cpu的問題,實(shí)際上并沒有一個(gè)準(zhǔn)確的答案,因?yàn)椴煌?b class="flag-6" style="color: red">芯片制造商與英特爾的CPU產(chǎn)品線在性能、架構(gòu)和用途等方面都存在一定的差異,因此很難進(jìn)行

2024-03-11 18:13:17 1783

1783 蘋果M3芯片的晶體管數(shù)量相當(dāng)可觀,相比前代產(chǎn)品有了顯著的提升。這款芯片搭載了高達(dá)250億個(gè)晶體管,比M2芯片多出50億個(gè),這樣的設(shè)計(jì)使得M3芯片在性能上有了質(zhì)的飛躍。

2024-03-11 16:45:37 257

257 蘋果M3芯片與英特爾芯片在多個(gè)方面存在顯著差異。首先,M3芯片是蘋果自家研發(fā)的,采用了先進(jìn)的制程技術(shù)和架構(gòu)設(shè)計(jì),具有出色的計(jì)算性能和多任務(wù)處理能力。而英特爾芯片則以其廣泛的應(yīng)用領(lǐng)域和穩(wěn)定的性能著稱。

2024-03-08 16:12:54 336

336 M3芯片的晶體管數(shù)量根據(jù)不同的版本有所差異。具體來說,標(biāo)準(zhǔn)版的M3芯片擁有250億個(gè)晶體管,這一數(shù)量相比前代產(chǎn)品M2有了顯著的提升,使得M3芯片在性能上有了更出色的表現(xiàn)。

2024-03-08 15:43:49 190

190 本帖最后由 jf_50240986 于 2024-3-8 22:51 編輯

串接NPN型晶體管的情況。晶體管基極要求注入電流,產(chǎn)生電流的電壓必須高于(Vo+Vbe),約為(Vo+1)。若基極

2024-03-06 20:49:11

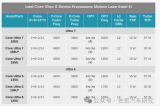

據(jù)悉,18A 制程是英特爾技術(shù)引領(lǐng)道路上的關(guān)鍵階段,雖非直接采用 1.8納米工藝,英特爾仍自豪宣稱其性能與晶體管密度媲美友商的 1.8 nm制程。

2024-02-29 15:13:29 139

139 微軟將使用英特爾的18A技術(shù)生產(chǎn)芯片 據(jù)外媒報(bào)道微軟公司計(jì)劃使用英特爾的18A制造技術(shù)生產(chǎn)自研芯片。但是目前沒有確切的消息表明微軟將生產(chǎn)什么芯片,但是業(yè)界多估計(jì)是人工智能加速器。

2024-02-22 17:35:11 356

356 雙極性晶體管是利用兩種離子導(dǎo)電,空穴和自由電子,但是對于一個(gè)實(shí)際存在的系統(tǒng),其整體上是呈現(xiàn)電中性的,當(dāng)其中的電子或者空穴移動(dòng)形成電流時(shí),與之對應(yīng)的空穴或者電子為什么不會(huì)一起隨著移動(dòng)?

這個(gè)問題困擾

2024-02-21 21:39:24

晶體管并聯(lián)時(shí),當(dāng)需要非常大的電流時(shí),可以將幾個(gè)晶體管并聯(lián)使用。因?yàn)榇嬖赩BE擴(kuò)散現(xiàn)象,有必要在每一個(gè)晶體管的發(fā)射極上串聯(lián)一個(gè)小電阻。電阻R用以保證流過每個(gè)晶體管的電流近似相同。電阻值R的選擇依據(jù)

2024-01-26 23:07:21

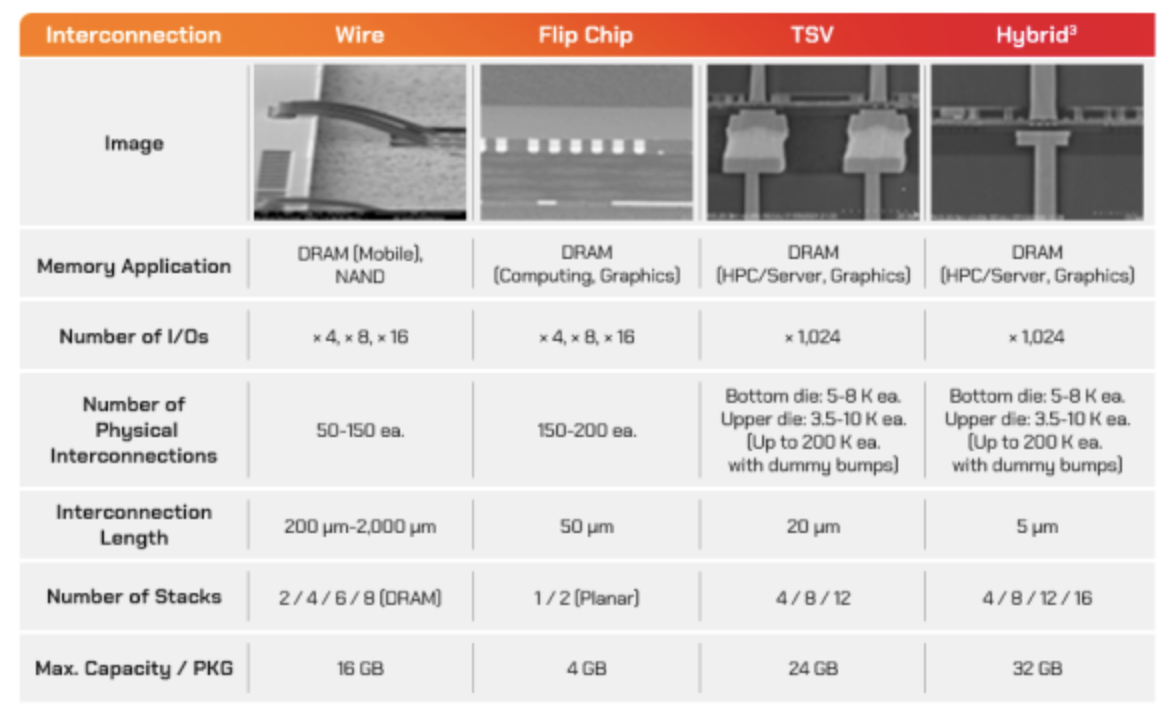

英特爾最近宣布,他們已經(jīng)實(shí)現(xiàn)了基于業(yè)界領(lǐng)先的半導(dǎo)體封裝解決方案的大規(guī)模生產(chǎn),其中包括具有劃時(shí)代意義的3D封裝技術(shù)Foveros。

2024-01-26 16:53:24 911

911 英特爾在封裝技術(shù)方面取得了重大突破,并已經(jīng)開始大規(guī)模生產(chǎn)基于3D Foveros技術(shù)的產(chǎn)品。這項(xiàng)技術(shù)使得英特爾能夠在單個(gè)封裝中整合多個(gè)小芯片(Chiplets),從而提高了芯片的性能、尺寸和設(shè)計(jì)靈活性。

2024-01-26 16:04:50 231

231 近日,英特爾(Intel)宣布,其已成功實(shí)現(xiàn)基于業(yè)界領(lǐng)先的半導(dǎo)體封裝解決方案的大規(guī)模生產(chǎn),其中包括突破性的3D封裝技術(shù)Foveros。這一技術(shù)在新墨西哥州Fab 9工廠中完成升級并投產(chǎn)。

2024-01-26 16:03:15 238

238 眾所周知,整個(gè)半導(dǎo)體領(lǐng)域正邁進(jìn)一個(gè)同時(shí)整合多個(gè)‘芯粒’(Chiplets,也被稱為‘小芯片’)在同一封裝中的多元時(shí)代。基于此,英特爾的 Foveros 及新型 EMIB(嵌入式多芯片互連橋接)等高級封裝解決方案被譽(yù)為能將一萬億個(gè)晶體管融于單一封裝之內(nèi)

2024-01-26 09:44:28 188

188 英特爾宣布已實(shí)現(xiàn)基于業(yè)界領(lǐng)先的半導(dǎo)體封裝解決方案的大規(guī)模生產(chǎn),其中包括英特爾突破性的3D封裝技術(shù)Foveros,該技術(shù)為多種芯片的組合提供了靈活的選擇,帶來更佳的功耗、性能和成本優(yōu)化。 這一

2024-01-25 14:24:34 118

118 放大,似于多路比較器的輸出,NPN型晶體管多發(fā)射極分別接到比較器的輸出端,集電極共用一路上拉電阻連接至電源,如果多路比較器有一路導(dǎo)通,則該多發(fā)射極晶體管集電極輸出導(dǎo)通拉低,電平為低電平。

不知是否是我理解的這樣?

2024-01-21 13:47:56

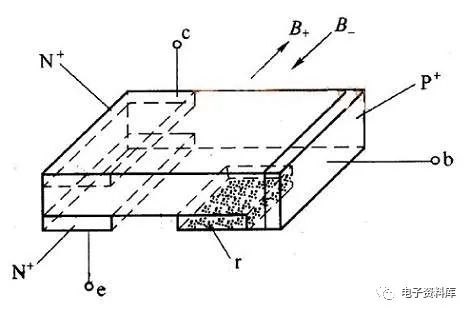

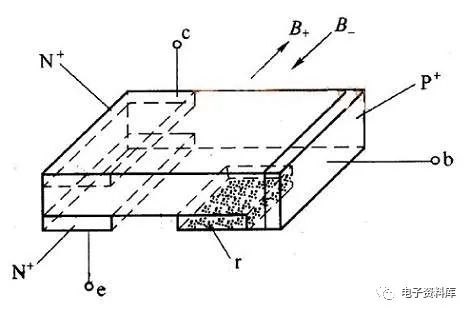

常用的半導(dǎo)體元件還有利用一個(gè)PN結(jié)構(gòu)成的具有負(fù)阻特性的器件一單結(jié)晶體管,請問這個(gè)單結(jié)晶體管是什么?能夠?qū)崿F(xiàn)負(fù)阻特性?

2024-01-21 13:25:27

晶體管在基極和集電極之間并聯(lián)電容有什么作用?是為了米勒電容嗎、?但是米勒電容對三極管的開通有害的時(shí)候,為什么還要并聯(lián)電容?電容不是越并越大,加大了等效米勒電容?

2024-01-19 22:39:57

三極管功率會(huì)先上升后下降,因?yàn)殡妷航翟谙陆刀娏髟谏仙9β首畲簏c(diǎn)在中間位置。

3、當(dāng)基射極電流增大到一定水平,集射極電壓降低到不能再降的程度時(shí),晶體管進(jìn)入飽和,此時(shí)無論基射極電流如何增大,集射極電流也

2024-01-18 16:34:45

英特爾在2024年CES上推出首款軟件定義汽車SoC芯片,也是全球首款采用Chiplet的車規(guī)級芯片。

2024-01-12 11:40:58 1607

1607

英特爾將發(fā)布推出了一系列AI軟件定義汽車系統(tǒng)芯片(SDV SoC),在車用芯片市場與高通和英偉達(dá)展開競爭。

2024-01-12 11:33:53 389

389 對于一個(gè)含有晶體管,場效應(yīng)管,運(yùn)放的電路,該如何求解他的輸入電阻和輸出電阻,舉例而言,在含有晶體管的電路射極跟隨器中,求解輸出電阻時(shí),為什么要考慮基極的電阻和偏置電路的電阻,此時(shí)不應(yīng)該在基極是二極管

2024-01-10 17:17:56

英特爾對此次活動(dòng)的定位如下: “誠摯邀請您傾聽英特爾高層精英、技術(shù)專才以及各方合作伙伴深度解讀我們的戰(zhàn)略布局、卓越工藝技術(shù)、尖端封裝技巧與生態(tài)建設(shè)。旨在讓您深入理解英特爾的代工廠服務(wù)如何助力貴司充分利用英特爾強(qiáng)大的彈性供應(yīng)實(shí)力構(gòu)筑芯片設(shè)計(jì)。”

2024-01-05 09:40:29 368

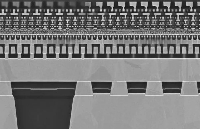

368 12月9日,英特爾在IEDM 2023(2023 IEEE 國際電子器件會(huì)議)上展示了使用背面電源觸點(diǎn)將晶體管縮小到1納米及以上范圍的關(guān)鍵技術(shù)。英特爾表示將在2030年前實(shí)現(xiàn)在單個(gè)封裝內(nèi)集成1萬億個(gè)晶體管。

2023-12-28 13:58:43 258

258 英特爾宣布將在以色列南部建造價(jià)值250億美元的芯片工廠,

2023-12-27 15:58:54 145

145

帕特·基辛格進(jìn)一步預(yù)測,盡管摩爾定律顯著放緩,到2030年英特爾依然可以生產(chǎn)出包含1萬億個(gè)晶體管的芯片。這將主要依靠新 RibbonFET晶體管、PowerVIA電源傳輸、下一代工藝節(jié)點(diǎn)以及3D芯片堆疊等技術(shù)實(shí)現(xiàn)。目前單個(gè)封裝的最大芯片含有約1000億個(gè)晶體管。

2023-12-26 15:07:37 312

312 摩爾定律概念最早由英特爾聯(lián)合創(chuàng)始人戈登·摩爾在1970年提出,明確指出芯片晶體管數(shù)量每兩年翻一番。得益于新節(jié)點(diǎn)密度提升及大規(guī)模生產(chǎn)芯片的能力。

2023-12-25 14:54:14 227

227 過去五年來,英特爾在先進(jìn)芯片制造方面一直落后于臺積電和三星。現(xiàn)在,為了重新奪回領(lǐng)先地位,該公司正在采取大膽且冒險(xiǎn)的舉措,在其臺式機(jī)和筆記本電腦Arrow Lake處理器中引入兩項(xiàng)新技術(shù),該處理器將于2024年末推出。英特爾希望憑借新的晶體管技術(shù)和首創(chuàng)的電力輸送系統(tǒng)超越競爭對手。

2023-12-25 14:50:38 317

317 近五年來,英特爾在高級芯片制造領(lǐng)域落后于臺積電和三星。如今,為重新贏得領(lǐng)先地位,英特爾正大膽而冒險(xiǎn)地引入兩項(xiàng)全新技術(shù),即新型晶體管技術(shù)和首創(chuàng)的電源交付系統(tǒng),這兩項(xiàng)技術(shù)將被應(yīng)用在計(jì)劃于2024年底發(fā)布的桌面和筆記本電腦的Arrow Lake處理器中。

2023-12-19 11:58:26 278

278

英特爾是三者中最早演示 CFET 的,早在 2020 年就在 IEDM 上推出了早期版本。這一次,英特爾報(bào)告了圍繞 CFET 制造的最簡單電路(inverter)的多項(xiàng)改進(jìn)。CMOS inverter 將相同的輸入電壓發(fā)送到堆棧中兩個(gè)器件的柵極,并產(chǎn)生與輸入邏輯相反的輸出。

2023-12-19 11:15:56 259

259

在最近的IEDM大會(huì)上,英特爾表示,已將 CMOS 硅晶體管與氮化鎵 (GaN) 功率晶體管集成,用于高度集成的48V設(shè)備。

2023-12-14 09:23:06 547

547

眾所周知,晶體管微縮和背面供電是英特爾滿足快速增長的算力市場需求的關(guān)鍵所在。雖然面臨著困境和挑戰(zhàn),例如成本壓力,但英特爾堅(jiān)定不移地推動(dòng)著自己的發(fā)展計(jì)劃,使自身在滿足此類市場需求時(shí)處于領(lǐng)先地位。

2023-12-12 15:00:53 219

219 在IEDM 2023上,英特爾展示了結(jié)合背面供電和直接背面觸點(diǎn)的3D堆疊CMOS晶體管,這些開創(chuàng)性的技術(shù)進(jìn)展將繼續(xù)推進(jìn)摩爾定律。

2023-12-11 16:31:05 342

342 英特爾在2023年國際電子設(shè)備制造大會(huì)上宣布,他們已經(jīng)成功完成了一項(xiàng)名為PowerVia的背面供電技術(shù)的開發(fā)。這個(gè)技術(shù)是基于英特爾的最新晶體管研究成果,它實(shí)現(xiàn)了互補(bǔ)金屬氧化物半導(dǎo)體場效應(yīng)晶體管

2023-12-11 16:10:42 501

501

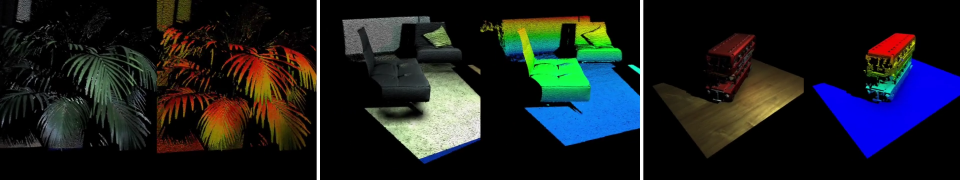

英特爾研究院將在NeurIPS 2023大會(huì)上展示一系列富有價(jià)值、業(yè)界領(lǐng)先的AI創(chuàng)新成果。面向廣大開發(fā)者、研究人員和學(xué)界人士,這一AI和計(jì)算機(jī)視覺領(lǐng)域的全球頂會(huì)將于12月10日至16日在美國新奧爾良

2023-12-08 19:15:04 334

334 英特爾研究院將重點(diǎn)展示31項(xiàng)研究成果,它們將推進(jìn)面向未來的AI創(chuàng)新。 ? ? ? ?英特爾研究院將在NeurIPS 2023大會(huì)上展示一系列富有價(jià)值、業(yè)界領(lǐng)先的AI創(chuàng)新成果。面向廣大開發(fā)者、研究人員

2023-12-08 09:17:21 379

379 來至網(wǎng)友的提問:如何選擇分立晶體管?

2023-11-24 08:16:54

我在進(jìn)行AD8138ARM的熱仿真,datasheet中只有結(jié)到環(huán)境的熱阻JA的數(shù)據(jù),我需要結(jié)到外殼的熱阻Jc的數(shù)據(jù),還有AD8138ARM放大器集成的晶體管數(shù)目是多少?

2023-11-21 06:54:43

英特爾聯(lián)合創(chuàng)始人戈登摩爾曾預(yù)言,芯片上的晶體管數(shù)量每隔一到兩年就會(huì)增加一倍。

2023-11-14 17:20:35 704

704

移動(dòng)式英特爾? GME965 和移動(dòng)式英特爾? GLE960 高速芯片組具備卓越的圖形處理功能、高 I/O 帶寬、資產(chǎn)管理功能以及領(lǐng)先的存儲速度和可靠性,為嵌入式開發(fā)人員提供更高靈活性。

2023-11-14 14:44:52 0

0 晶體管,作為現(xiàn)代電子設(shè)備的基石,其功能和工作原理一直是電子學(xué)和半導(dǎo)體物理領(lǐng)域研究的核心。芯片中的每個(gè)晶體管都是一個(gè)微型開關(guān),負(fù)責(zé)控制電流的流動(dòng)。隨著技術(shù)的不斷發(fā)展,現(xiàn)代芯片上可能集成了數(shù)十億甚至數(shù)百億的晶體管。本文將探討晶體管的基本工作原理,從其構(gòu)造開始,深入解析其操作機(jī)制。

2023-10-16 10:09:13 1239

1239

專業(yè)圖書47-《新概念模擬電路》t-I晶體管

2023-09-28 08:04:05

晶體管是通常用于放大器或電控開關(guān)的半導(dǎo)體器件。晶體管是調(diào)節(jié)計(jì)算機(jī)、移動(dòng)電話和所有其他現(xiàn)代電子電路運(yùn)行的基本構(gòu)件。

2023-09-27 10:59:40 2306

2306

強(qiáng)強(qiáng)聯(lián)手!英特爾于創(chuàng)新日上展示了世界第一個(gè)UCIe連接的Chiplet(小芯片)處理器。此芯片匯聚兩大晶圓代工廠尖端技術(shù),分別將使用Intel 3,以及TSMC N3E的Synopsys(新思科

2023-09-22 18:17:02 451

451 英特爾基于Chiplet的處理器,如Sapphire Rapids和新發(fā)布的Meteor Lake,目前使用專有接口和協(xié)議進(jìn)行Chiplet之間的通信,但英特爾已宣布將在其下一代Arrow Lake消費(fèi)級處理器之后使用UCIe接口。AMD和英偉達(dá)也在致力于自己的計(jì)劃,但還沒有展示可用的硅芯片。

2023-09-22 16:05:12 432

432

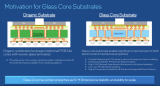

”,并稱這將重新定義芯片封裝的邊界,能夠?yàn)閿?shù)據(jù)中心、人工智能和圖形構(gòu)建提供改變游戲規(guī)則的解決方案,推動(dòng)摩爾定律進(jìn)步。該公司表示,將于本十年晚些時(shí)候使用玻璃基板進(jìn)行先進(jìn)封裝。 1971年,英特爾的第一款微處理器擁有2300個(gè)晶體管

2023-09-20 08:46:59 521

521

英特爾稱該基板材料是一項(xiàng)重大突破,可解決有機(jī)材質(zhì)基板用于芯片封裝產(chǎn)生的翹曲問題,突破了現(xiàn)有傳統(tǒng)基板的限制,讓半導(dǎo)體封裝晶體管數(shù)量極限最大化,同時(shí)更省電、更具散熱優(yōu)勢,將用于更高速、更先進(jìn)的數(shù)據(jù)中心、AI、繪圖處理等高端芯片封裝。

2023-09-19 17:36:19 757

757

的NMN910 5G SoC 芯片,也被稱為麒麟9000。 這款芯片集成了49億個(gè)晶體管,尺寸為 5 納米,成為了全球首個(gè)量產(chǎn)的5nm 5G SoC芯片。這是一個(gè)重要的里程碑,它意味著華為已經(jīng)成為了第一個(gè)推出5nm工藝技術(shù)的芯片制造商,并且在性能方面達(dá)到了全球領(lǐng)先的水平。 首先我們

2023-09-01 16:47:35 7012

7012 ? 先進(jìn)封裝則被視為延續(xù)摩爾定律壽命的重要技術(shù),英特爾(Intel)最新電腦處理器Meteor Lake將在9月發(fā)布,采用英特爾最先進(jìn)3D IC封裝技術(shù)「Foveros」,透過堆疊的封裝方式,增進(jìn)

2023-08-28 11:08:14 1860

1860 晶體管和芯片的關(guān)系介紹 晶體管和芯片是現(xiàn)代電子技術(shù)中最重要的兩個(gè)概念,二者有密不可分的關(guān)系。晶體管是一種半導(dǎo)體材料制造的電子器件,而芯片則是晶體管等電子器件及相關(guān)電路的集成體。 一、晶體管 晶體管

2023-08-25 15:29:37 2440

2440 晶體管和芯片的關(guān)系是什么? 晶體管和芯片是相互關(guān)聯(lián)的兩個(gè)概念,晶體管是芯片的核心組成部分之一。 晶體管是一種能夠控制電流的電子器件,由美國貝爾實(shí)驗(yàn)室的William Shockley、John

2023-08-25 15:21:05 1513

1513 英特爾的福爾瑟姆園區(qū)被用于固態(tài)硬盤(SSD)、圖形處理器、軟件甚至芯片的開發(fā),甚至芯片開發(fā)等多種研究開發(fā)。英特爾計(jì)劃在2021年出售3d nand和ssd事業(yè)部門后,將適當(dāng)?shù)膶<肄D(zhuǎn)移到solidm或使其退出。

2023-08-18 11:27:43 645

645 m3芯片相當(dāng)于英特爾什么水平? M3芯片是一種用于移動(dòng)設(shè)備的處理器芯片,由ARM架構(gòu)開發(fā),可以用于智能手機(jī)、平板電腦和其他移動(dòng)設(shè)備。它最初是由華為公司自主設(shè)計(jì)并制造的,后來被其他廠商采用。那么,M3

2023-08-16 11:33:31 6032

6032 安裝OpenVINO?工具套件英特爾 Distribution時(shí),出現(xiàn)錯(cuò)誤: Python 3.10.0.ECHO is off. Unsupported Python version.

2023-08-15 08:14:13

晶體管是現(xiàn)代電子設(shè)備中至關(guān)重要的組件,而芯片則是晶體管的集成。晶體管是一種用于控制電流的電子器件,它是由半導(dǎo)體材料制成的。晶體管的發(fā)明和發(fā)展對現(xiàn)代科技的進(jìn)步起到了重要的推動(dòng)作用。

2023-08-04 09:45:30 1074

1074 英特爾媒體加速器參考軟件是用于數(shù)字標(biāo)志、交互式白板(IWBs)和亭位使用模型的參考媒體播放器應(yīng)用軟件,它利用固定功能硬件加速來提高媒體流速、改進(jìn)工作量平衡和資源利用,以及定制的圖形處理股(GPU)管道解決方案。該用戶指南將介紹和解釋如何為Linux* 使用英特爾媒體加速器參考軟件。

2023-08-04 06:34:54

調(diào)節(jié)電流或電壓的設(shè)備,充當(dāng)電子信號的按鈕或門。

?

編輯

添加圖片注釋,不超過 140 字(可選)

晶體管的類型

晶體管由三層半導(dǎo)體器件組成,每層都能夠移動(dòng)電流。半導(dǎo)體是一種以“半熱敏”方式導(dǎo)電的材料

2023-08-02 12:26:53

紋理貼圖獲取2D曲面圖像并將其映射到3D多邊形上。

本指南涵蓋了幾種紋理優(yōu)化,可以幫助您的游戲運(yùn)行得更流暢、看起來更好。

在本指南的最后,您可以檢查您的知識。您將了解有關(guān)主題,包括紋理圖譜

2023-08-02 06:12:17

該2通道混音器電路基于2n3904晶體管,該晶體管形成2個(gè)前置放大器。2通道混音器電路的第一個(gè)前置放大器具有高增益,可用于麥克風(fēng)輸入,第二個(gè)前置放大器可用于控制音頻電平的輸入。

這種雙通道

2023-08-01 17:19:21

在半導(dǎo)體行業(yè)的最初幾十年里,新的工藝節(jié)點(diǎn)只需縮小晶體管的物理尺寸并將更多晶體管塞到芯片上即可實(shí)現(xiàn)性能、功耗和面積增益,這稱為經(jīng)典縮放。集成電路工作得更好,因?yàn)殡娦盘栐诿總€(gè)晶體管之間傳播的距離更短。

2023-07-16 15:47:43 413

413 英特爾表示,它是業(yè)內(nèi)第一個(gè)在類似產(chǎn)品的測試芯片上實(shí)現(xiàn)背面供電的公司,實(shí)現(xiàn)了推動(dòng)世界進(jìn)入下一個(gè)計(jì)算時(shí)代所需的性能。PowerVia 將于 2024 年上半年在英特爾 20A 工藝節(jié)點(diǎn)上推出,正是英特爾業(yè)界領(lǐng)先的背面供電解決方案。它通過將電源路由移動(dòng)到晶圓的背面,解決了面積縮放中日益嚴(yán)重的互連瓶頸問題。

2023-06-20 15:39:06 326

326 研發(fā)的最先進(jìn)的硅自旋量子比特芯片,利用了英特爾數(shù)十年來積累的晶體管設(shè)計(jì)和制造能力。 在英特爾的晶圓廠里,Tunnel Falls是在300毫米的硅晶圓上生產(chǎn)的,利用了英特爾領(lǐng)先的晶體管工業(yè)化制造能力,如極紫外光刻技術(shù)(EUV),以及柵極和接觸層加工技術(shù)。在硅自旋量子比特中,信息(0/1)被編碼

2023-06-17 10:15:03 416

416

將于2024年上半年在Intel 20A制程節(jié)點(diǎn)上推出。通過將電源線移至晶圓背面,PowerVia解決了芯片單位面積微縮中日益嚴(yán)重的互連瓶頸問題。 “ 英特爾正在積極推進(jìn)‘四年五個(gè)制程節(jié)點(diǎn)’計(jì)劃,并致力于在2030年實(shí)現(xiàn)在單個(gè)封裝中集成一萬億個(gè)晶體管,PowerVia對這兩大目標(biāo)而言都是重要里程

2023-06-09 20:10:03 193

193 的關(guān)鍵技術(shù),英特爾將PowerVia技術(shù)和RibbonFET晶體管的研發(fā)分開進(jìn)行,以確保PowerVia可以被妥善地用于Intel 20A和In

2023-06-07 16:56:20 701

701 英特爾率先在產(chǎn)品級芯片上實(shí)現(xiàn)背面供電技術(shù),使單元利用率超過90%,同時(shí)也在其它維度展現(xiàn)了業(yè)界領(lǐng)先的性能。 英特爾宣布在業(yè)內(nèi)率先在產(chǎn)品級測試芯片上實(shí)現(xiàn)背面供電(backside power

2023-06-06 16:22:00 314

314 在比利時(shí)安特衛(wèi)普舉行的ITF World 2023上,英特爾技術(shù)開發(fā)總經(jīng)理Ann Kelleher概述了英特爾在幾個(gè)關(guān)鍵領(lǐng)域的最新進(jìn)展,最有趣的是英特爾將在未來采用堆疊CFET晶體管。

2023-05-20 10:01:14 423

423

差分放大電路輸入共模信號時(shí)

為什么說RE對每個(gè)晶體管的共模信號有2RE的負(fù)反饋效果

這里說的每個(gè)晶體管的共模信號是指什么信號 是指輸入信號 還是指ie1 ie2 uoc ?

另外為什么是負(fù)的反饋

2023-04-25 16:15:31

英特爾和Arm達(dá)成了一項(xiàng)合作協(xié)議,英特爾代工服務(wù)(Intel Foundry Services)和Arm將會(huì)進(jìn)行設(shè)計(jì)技術(shù)協(xié)同優(yōu)化,這意味著讓芯片設(shè)計(jì)者能夠基于英特爾18A制程打造低功耗的SoC

2023-04-19 14:31:23 913

913 西門子S7-200電源怎么看是繼電器輸出還是晶體管輸出呢?

2023-04-18 10:08:03

為什么我在EDA上導(dǎo)入AD中的pcb時(shí),在EDA的3D顯示上板子上光禿禿的沒有器件?

2023-04-10 19:56:07

我使用 Unity Hub 和 android runtime 開發(fā)了一個(gè) 3D unity 游戲。我可以在基于 Android 的手機(jī)上玩這個(gè)游戲,但不能在 iMX8QM 上玩。而且好像沒有具體

2023-04-04 07:42:57

采用晶體管互補(bǔ)對稱輸出時(shí),兩管基極之間有電容相連,為什么?c2有什么用??

2023-03-31 14:02:55

有沒有負(fù)觸發(fā)導(dǎo)通正的晶體管呢?哪位大神知道請賜教。謝謝啦!

2023-03-31 11:47:46

芯片上那必然會(huì)引起新一輪的技術(shù)革命,但是目前光芯片量產(chǎn)使用的光刻方式特征尺寸也在130nm以上,而且光波長至少在1.1um以上,光器件注定不能縮小器件到晶體管那么小。現(xiàn)在比較有前景的方式為光電共封裝

2023-03-29 10:48:47

我在設(shè)計(jì) PCB 時(shí)犯了一個(gè)錯(cuò)誤,我的一些晶體管在原理圖上將集電極和發(fā)射極調(diào)換了。“正常”方式是有 1:基極,2:發(fā)射極,3:集電極,但我需要一個(gè)晶體管,1:基極,2:集電極,3:發(fā)射極。引腳號與此圖像相關(guān):你知道有這種封裝的晶體管嗎?我知道我可以將它倒置并旋轉(zhuǎn),但我想知道我是否可以正確使用一個(gè)。

2023-03-28 06:37:56

用于英特爾移動(dòng)CPU的2相高效DC/DC控制器

2023-03-23 08:54:16

電子發(fā)燒友App

電子發(fā)燒友App

評論