電器設備在關斷或沒有運行主要功能時,其耗電量被稱為待機功耗。一個設備一整年下來的耗電量可達約8600Wh,若待機功耗能減小1W,就相當于1美元/年的能源成本。盡管待機功耗看似微不足道,但如果考慮到家庭里所有電子設備的累積效應,這個數目就很可觀了。美國家庭在這方面的能源成本每年就高達30億美元左右,占美國住宅總用電量的近7%。

例如,從圖1所示的典型機頂盒(STB),我們可以看到整個系統里有許多子電路。其中,AC/DC適配器采用AC電力線輸入,然后輸出一個DC電壓,為紅色框里的STB供電。STB還包含了一個DC/DC 功率部件,可把AC/DC電源輸出的DC電壓轉換為眾多更低的電壓,供數字處理器和不同外設的連接所用。

圖1 機頂盒(STB)的典型模塊示意圖

機頂盒系統

機頂盒系統包含有大量不同的子電路,其中每一個都可在待機模式下被關斷,以降低總功耗。為了通過“能源之星”的認證,AC/DC適配器必須滿足最低滿載效率要求,而且空載功耗小于500mW。

STB要通過“能源之星”認證,必須確保睡眠模式下的功耗小于1W。

所有目標就是通過以下措施提高有功模式下的效率,降低待機功耗的。

1 關注架構級的改進,判斷系統何時處于低功耗狀態,采取措施提高效率。

2 提高元器件性能以優化最低功耗。

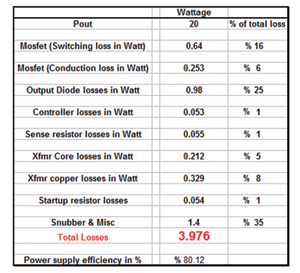

下面我們將從AC/DC部分開始分析,接下來是DC/DC和數字處理器部分。表1是一個采用普通輸入,輸出電壓為32V,總輸出功率為20W的典型反激式設計的損耗計算。該表表明,我們必須把關注焦點放在降低損耗上。

變壓器損耗

從表1可看出,人們很容易忽略掉變壓器損耗,而把注意力集中在緩沖電路、二極管以及MOSFET的損耗上。雖然所有這些損耗都非常重要,但緩沖電路損耗是由變壓器的初級和次級繞組之間的松耦合(loose coupling)引起的,要降低緩沖電路損耗,實際上應該從變壓器設計著手。通過優化繞組層的排列,可在初級和次級端之間形成更緊密的耦合,而且有效減少緩沖電路的能量泄漏,從而使互耦合 (mutual coupling)得以改進。

磁性元件是總電源損耗的主要原因,對于頻率很低的滿負載模式和PFM模式,采用損耗較低的材料,加之正確的繞組排列,可以同時降低磁芯損耗和AC損耗,最終提高電源效率。

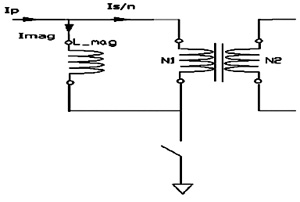

在任何AC/DC反激式適配器設計中,由于加載的VIN很大,為了降低開關損耗,設計人員不得不采用較低的工作頻率,這就給變壓器帶來了高壓使用的問題。因此初級線圈需要很大的匝數,以使磁通量密度保持在其飽和點以下的某個合理水平。在空載條件下,另一個造成大量功耗的額外損耗是變壓器的磁化電流。除了流入初級端的電流之外,不論連接負載與否,還有一個磁化電流或勵磁電流(Imag)流入初級端,造成輕載或空載條件下的銅損耗。

圖2 變壓器泄漏和繞組模式

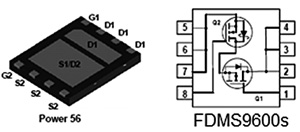

MOSFET損耗及封裝

一般而言,性能更高的轉換器設計可以推動MOSFET硅芯片及封裝技術,實現尺寸更小、效率更高的產品。

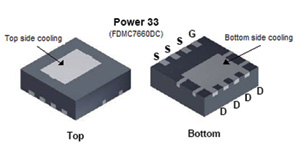

圖3 Power 33&56封裝

低導通阻抗Rds(on)是實現滿載條件下MOSFET傳導損耗最小化的一個關鍵因素。由于封裝鍵合引線與管腳的阻抗占據總阻抗的相當大部分,尤其是在Power56與Power33這樣的新MOSFET設計中尤其明顯,故需要特別關注使封裝阻抗最小化。

相比其他類型的封裝,采用Power 56/33這樣帶裸露銅引線框架技術和鋁圓線互連的增強型封裝,可以在占位面積更小的封裝內獲得出色的熱性能和最佳的電氣性能。比如,硅晶技術和封裝技術兩方面的進步(如雙面冷卻Power33封裝),催生了出色的熱性能,在電流高達20A的情況下,導通阻抗極低,僅僅為不到2mΩ,而尺寸僅3.3mm×3.3mm。

圖4 先進的雙面冷卻power33封裝

還有一點非常重要,就是不僅要考慮在滿載條件下以更低的Rds(on)來獲得更高的效率,還需考慮輕載條件下Rds(on)×QG(TOT)或品質因數(FOM)。

輕載條件下,Rds(on)沒有那么重要,大部分損耗是由柵極驅動損耗造成,其為柵極電壓平方的函數。

優化MOSFET的柵極電壓也十分重要,因為若柵極電壓增加,MOSFET的導通阻抗就會下降。不過,當柵極電壓增加時,所需的柵極電荷Qg也隨之增加。柵極驅動功率P=Qg·V·F,這里,Qg為柵極電荷,V為柵極電壓,F是頻率。

輸出二極管損耗

2A/500mV標準肖特基二極管的傳導損耗大約為1W。若正向電壓降(VF)減小200mV為300mV,損耗可降至600mW,即功耗減小約400mW。對于電流較大的低壓應用來說,用Rds(on)為10mΩ的同步MOSFET來代替肖特基二極管也是一種可選方案。

工作頻率控制

另外還有一些能夠減小控制器開關頻率的技術,可用來降低待機模式下的功率半導體開關損耗。

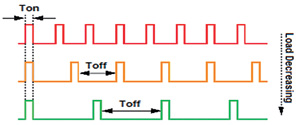

其中一種技術是通過降低電源的頻率來減小開關損耗,從而提高低功率工作模式下的效率。

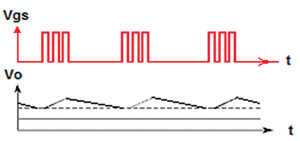

圖5 脈沖頻率調制

開關模式電源有兩種工作模式:脈寬調制(PWM)模式和脈沖頻率調制(PFM)模式。在PWM模式下,開關頻率是固定的。通過改變電源的占空比來控制輸出電壓。

在PFM模式下,通過隨線路和負載條件的變化而改變開關頻率來控制輸出電壓。這時,開關頻率與輸出功率成比例。在輸出功率很低時,開關頻率降低,開關損耗減小,效率提高。PFM控制器的靜態電流消耗只限于其基準電壓和誤差比較器的偏置所需的電流。不過,PWM控制器始終帶有一個有源振蕩器,即使在空載時,它也會持續從輸入源汲取電流。

許多PWM電源控制器都關斷大部分或部分PWM功能性,以求降低極輕載或空載條件下的損耗。在這種方案中,突發模式前后還有幾個相關的延時周期,會帶來可聽噪聲問題。

圖6 遲滯控制

當電源重新開啟,并從輕載向滿載變化時,這種延時還會造成輸出電壓下降,迫使電源設計人員不得不使用額外的并聯輸出電容,從而增加系統的成本和尺寸。

先進突發模式可把輕載條件下的開關損耗降至最小,缺點是會增加DC輸出紋波,延長控制周期。

啟動電阻損耗

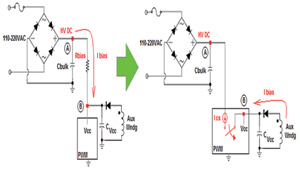

高壓半導體IC工藝的進步讓電源IC可以直接從AC整流高電壓啟動,不再像以往那樣需要啟動電阻來把高電壓降壓到低電壓,從而避免了這部分功耗。

圖7中,高壓內部電流源(Ics)為內部偏置電路供電,為Cvcc電容充電。而且,當Vcc達到閾值時,內部電流源被禁用,PWM的偏置電流來自于調節輔助繞組(Auxwndg)。本系統中,低靜態電流是關鍵的設計考慮因素。

圖7 通過Rbias或利用HV IC實現Vcc偏置

DC/DC功率部件

前面我們討論了運用于DC/DC的 PWM、PFM和突發模式,本節將著重討論設計和元件優化。

對于MOSFET,除了通常的傳導損耗和開關損耗之外,還有一些可能被忽略的其他損耗。下面我們將討論其中部分損耗,以及提高滿載和輕載效率的方法。

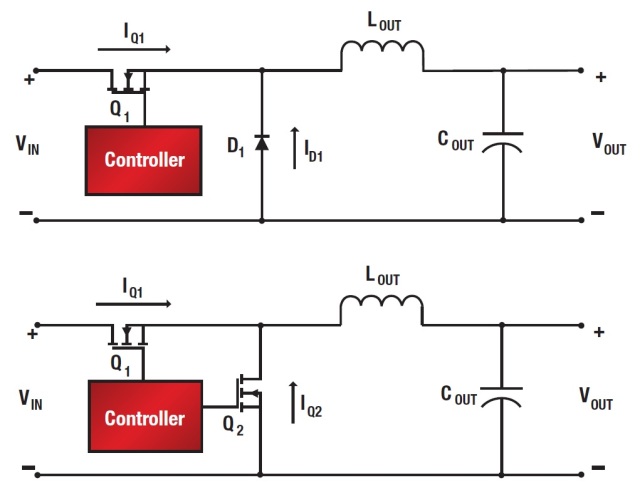

高邊和低邊同步MOSFET不同的電氣特性要求

當同步降壓轉換器的占空比在50%左右時,高邊和低邊MOSFET可以使用相同器件;但占空比較小時,必須根據不同的條件來分別選擇每個MOSFET。

圖8 Power 56的示意圖與封裝

占空比很小時,高邊MOSFET需要非常快速地導通和關斷,因此應該選擇具有極小柵極電荷的MOSFET。

對于低邊MOSFET,由于在開關周期內,它的傳導時間要長得多,故支持的RMS電流大得多,這時I2R損耗占主要部分,導通阻抗Rds(on)成為更重要的因子。通過為高邊MOSFET選擇小柵極電荷(Q1)器件,為低邊MOSFET選擇低導通阻抗(Q2)器件,而不是高低邊MOSFET采用相同的器件,可以獲得更高的效率。

直通損耗

當MOSFET的漏源電壓迅速上升時,感應產生的dv/dt會導致MOSFET導通。對于12V或更高的輸入電壓,這可能是一個問題。而且隨著MOSFET的漏源電壓急劇增加,dv/dt感應電壓尖峰可能經由Cgd柵漏電容(米勒電容)出現在相應的柵極信號上。

如果dv/dt感應電壓尖峰超過了給定閾值電壓,MOSFET就會在本應該關斷的時候暫時導通,對總體效率造成不良影響。必須確保所選的控制器使用了“固定死區時間”或“自適應柵極驅動”技術,或者二者兼備。

死區時間損耗

當一個同步整流器關斷時,存在一個死區時間,以確保高邊MOSFET等待低邊MOSFET關斷,從而避免交越傳導。在死區時間內,低邊MOSFET的內部體二極管由于反向恢復速度很慢,故需要一定的時間才能關斷,這就在該時間內產生額外的功耗。

利用集成有肖特基二極管、幾乎沒有反向恢復時間的MOSFET來代替常規體二極管,有助于降低死區時間內的體二極管損耗。

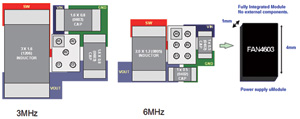

圖9 通過提高頻率,減少寄生效應來減小系統尺寸

寄生損耗

任何電路都會因元件封裝和電路布局而存在寄生電感。由于輸出功率等于輸入功率減去寄生功耗,故更高的頻率有助于減小器件的尺寸,把寄生電容和寄生電感效應降至最小。增加開關頻率可減少元件數目,提高集成度,增強對寄生效應的控制,從而減小總體電源系統的尺寸。

多個負載開關

在子電路進入待機模式時,負載開關可以利用使能管腳或通過I2C控制來關斷其電源。減小待機電流的一種解決方案是關斷系統中未使用的子電路或功能模塊。系統中的電路可劃分為許多子電路或功率島區,其中每一個都整合有一個負載開關。

在待機模式下,維持供電只是為了子電路保持稍后恢復工作狀態所必需的信息,圖10中的子電路#1就是這種情況。所有其他子電路則關斷以節電。

利用這種方法,盡管待機電流仍然大于關斷所有子電路的方法,但有可能實現一個可快速恢復的待機狀態。

這種方法可能帶來一個工程技術挑戰,即如何實現各模塊啟動/關斷的正確時序。通過打開或切斷與不同功能模塊連接的負載開關,可以使系統進入待機模式。一旦GPIO或I2C發出命令,低功耗DSP就退出待機模式,解碼接收到的信號,通過負載開關啟動整個系統。

圖10 負載開關關斷子電路

數字處理器

處理器芯片的關鍵在于使用低功耗技術,在待機期間減小內部工作電壓,把板上振蕩器頻率降至低速,并優化電路,降低功耗。對于任何處于有功或待機模式下的邏輯模塊,半導體行業都提供有一些相應的解決方案,可幫助降低這些損耗。

時鐘門控是一項可用于降低系統有功功耗的技術。它只在有未決任務時啟動特定邏輯模塊的時鐘。若沒有未決任務,特定邏輯模塊的時鐘可被關斷,故只減小該模塊的有功功率。

還有一種更好的時鐘門控解決方案,即切斷未在使用的那些邏輯模塊的供電。由于有功功率同時與電源電壓和頻率有關(V2),我們可以動態控制電源電壓,或根據計算任務的強度調節處理器的時鐘頻率,以此來控制有功功率。若性能要求不高,系統可以降低器件的頻率和供電電壓。

圖11 通過I2C控制實現Vout的動態電壓調節

結語

關于提高滿載條件下的效率,必須改變傳統的思考方式,轉而著眼于通過降低功耗來提高滿載與輕載條件下的效率。

系統工程師必須重點關注架構級和元件級優化的改進,以實現最高效的設計和最低的功耗。特別需要注意的是低磁化電流變壓器設計,通過降低輕載下銅損耗來提高效率。

此外,還需要通過頂層系統回顧,以找出給定系統中的所有損耗,然后利用帶PFM或突發模式的控制器來降低輕載功耗。最后,劃分功率島區,根據需要利用負載開關來啟動/關斷子電路,也可以降低待機功耗。

電子發燒友App

電子發燒友App

評論