信號(hào)鏈基礎(chǔ):時(shí)鐘抖動(dòng)解秘——高速鏈路時(shí)鐘抖動(dòng)規(guī)范基礎(chǔ)知識(shí)分享

用于在更遠(yuǎn)距離對(duì)日益增長(zhǎng)的海量數(shù)據(jù)進(jìn)行傳輸?shù)囊恍?biāo)準(zhǔn)不斷出現(xiàn)。來(lái)自各行業(yè)的工程師們組成了各種委員會(huì)和標(biāo)準(zhǔn)機(jī)構(gòu),根據(jù)其開發(fā)標(biāo)準(zhǔn)的目標(biāo)(數(shù)據(jù)吞吐量和通信距離)確定抖動(dòng)預(yù)算;同時(shí)還要考慮到組成通信鏈路的模塊的局限性。

?

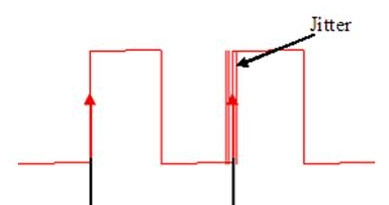

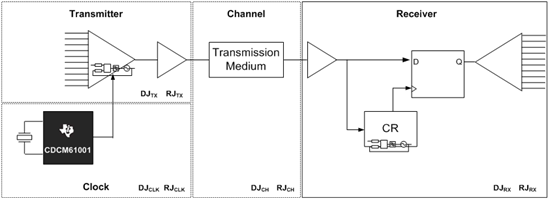

圖1通信鏈路—抖動(dòng)組件

?

圖1 顯示了集成有一個(gè)嵌入式時(shí)鐘的典型高速通信鏈路。每個(gè)子系統(tǒng)(時(shí)鐘、發(fā)送器、通道和接收機(jī))都會(huì)對(duì)整體抖動(dòng)預(yù)算的增加產(chǎn)生影響。子系統(tǒng)抖動(dòng)包括一個(gè)決定性 (DJ) 組件和一個(gè)隨機(jī)組件 (RJ),如圖1 所示。為了實(shí)現(xiàn)可接受的通信效果,必須滿足下列條件:

?

?

其中:TJSYS 是總抖動(dòng),而 1UI 為1個(gè)單位時(shí)間間隔(1 比特時(shí)間)

?

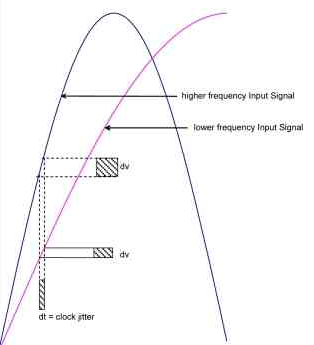

總抖動(dòng) (TJ) 包括每個(gè)子系統(tǒng)決定性抖動(dòng)和隨機(jī)抖動(dòng)的和。由于隨機(jī)抖動(dòng)自身的屬性,進(jìn)行這種求和時(shí)需要特別注意。隨機(jī)抖動(dòng)呈現(xiàn)高斯(隨機(jī))分布,并且無(wú)邊界。因此,隨機(jī)抖動(dòng)可表示為一個(gè) RMS 值,并且在規(guī)定測(cè)量/整合帶寬范圍內(nèi)對(duì)其進(jìn)行估算。例如,圖1 所示接收機(jī)的抖動(dòng)測(cè)量帶寬便為 f2 - f1(參見圖2)。這是因?yàn)榻邮諜C(jī)鎖相環(huán)路 (PLL) 追蹤 f1 以下的抖動(dòng)(從而排斥它),而發(fā)射 PLL 的頻率上限為 f2。從接收機(jī)的角度來(lái)看,使鏈路性能降低的隨機(jī)抖動(dòng)降至這些限制之間。

?

圖2高速通信鏈路—隨機(jī)抖動(dòng)測(cè)量帶寬

?

由于隨機(jī)抖動(dòng)是隨機(jī)過(guò)程產(chǎn)生的結(jié)果,系統(tǒng)總隨機(jī)抖動(dòng)的計(jì)算需要進(jìn)行方和根 (RSS) 計(jì)算,如方程式2所示:

?

?

決定性抖動(dòng)源和的計(jì)算很簡(jiǎn)單:

?

最后,可對(duì)系統(tǒng)總抖動(dòng)進(jìn)行估算,由此可以實(shí)現(xiàn)鏈路預(yù)算;但是,還需要做更多的工作。這種計(jì)算涉及統(tǒng)計(jì)數(shù)學(xué)。需要用到一種被稱之為 Q 因數(shù)的參數(shù)(參見表 1)。Q 因數(shù)的大小具體取決于誤碼率 (BER),同時(shí)還要根據(jù)鏈路性能/可靠性目標(biāo)來(lái)選擇。由于隨機(jī)抖動(dòng)的無(wú)邊界屬性,(最終)會(huì)出現(xiàn)誤碼。例如,10-8 的 BER 意味著,每發(fā)送 100,000,000 比特便會(huì)有一個(gè)比特被錯(cuò)誤解釋。現(xiàn)代的通信系統(tǒng)通常會(huì)要求一個(gè)達(dá)到或者超過(guò) 10-12 以上的 BER。

?

系統(tǒng)總抖動(dòng)(以及鏈路預(yù)算)可使用方程式 4 計(jì)算得到:

?

例如,10-14 的 BER 時(shí),總抖動(dòng)為:

?

表1Q 因數(shù)和誤碼率

?

本文討論了構(gòu)成總抖動(dòng)預(yù)算的一些參數(shù)。下一次,我們將探討時(shí)鐘,并研究隨機(jī)抖動(dòng)和相位噪聲之間的關(guān)系。

?

- 時(shí)鐘抖動(dòng)(15825)

- 高速鏈路(6752)

相關(guān)推薦

如何估算采樣時(shí)鐘抖動(dòng)

本文介紹了如何準(zhǔn)確地估算采樣時(shí)鐘抖動(dòng),以及如何計(jì)算正確的上下整合邊界。

2012-04-01 10:19:38 1665

1665

1665

1665

時(shí)域時(shí)鐘抖動(dòng)分析(上)

本系列文章共有三部分,第 1 部分重點(diǎn)介紹如何準(zhǔn)確地估算某個(gè)時(shí)鐘源的抖動(dòng),以及如何將其與 ADC 的孔徑抖動(dòng)組合。在第 2 部分中,該組合 抖動(dòng) 將用于計(jì)算 ADC 的 SRN,然后將其與實(shí)際

2012-05-07 11:37:30 2668

2668

2668

2668

正確理解時(shí)鐘器件的抖動(dòng)性能

為了正確理解時(shí)鐘相關(guān)器件的抖動(dòng)指標(biāo)規(guī)格,同時(shí)選擇抖動(dòng)性能適合系統(tǒng)應(yīng)用的時(shí)鐘解決方案,本文詳細(xì)介紹了如何理解兩種類型時(shí)鐘驅(qū)動(dòng)器的抖動(dòng)參數(shù),以及從鎖相環(huán)輸出噪聲特性理解時(shí)鐘器件作為合成器、抖動(dòng)濾除功能時(shí)的噪聲特性。

2013-06-21 15:40:41 14342

14342

14342

14342

時(shí)鐘抖動(dòng)和相噪及其測(cè)量方法

抖動(dòng)一般定義為信號(hào)在某特定時(shí)刻相對(duì)于其理想位置的短期偏移。這個(gè)短期偏移在時(shí)域的表現(xiàn)形式為抖動(dòng)(下文的抖動(dòng)專指時(shí)域抖動(dòng)),在頻域的表現(xiàn)形式為相噪。本文主要探討下時(shí)鐘抖動(dòng)和相噪以及其測(cè)量方法,以及兩者之間的關(guān)系。

2016-01-18 10:54:11 24276

24276

24276

24276

為什么時(shí)鐘抖動(dòng)技術(shù)可以降低EMI呢?

時(shí)鐘抖動(dòng)技術(shù)適合于各種周期性的脈沖信號(hào),典型的是電力電子設(shè)備中的PWM電壓和數(shù)字電路中的時(shí)鐘信號(hào)。

2023-09-11 10:55:34 503

503

503

503

IC設(shè)計(jì)必須關(guān)注的時(shí)鐘抖動(dòng)

時(shí)鐘抖動(dòng)是相對(duì)于理想時(shí)鐘沿實(shí)際時(shí)鐘存在不隨時(shí)間積累的、時(shí)而超前、時(shí)而滯后的偏移稱為時(shí)鐘抖動(dòng),簡(jiǎn)稱抖動(dòng)

2023-11-08 15:08:01 892

892

892

892

了解抖動(dòng)對(duì)高速鏈路的影響并將其降至最低

飛秒 (fs))以保持系統(tǒng)性能。盡管溫度和電壓會(huì)發(fā)生變化,但它們還必須隨著時(shí)間的推移保持其低抖動(dòng)規(guī)格。 一些抖動(dòng)是由信號(hào)路徑噪聲和失真引起的,使用時(shí)鐘恢復(fù)和重定時(shí)技術(shù)可以在一定程度上減少抖動(dòng)。然而,抖動(dòng)也由時(shí)鐘源產(chǎn)生,時(shí)鐘源通常是一個(gè)振蕩器。這

2024-01-01 13:55:00 265

265

265

265

信號(hào)鏈基礎(chǔ):Time-interleaving high-speed ADCs

我很高興為您帶來(lái)下一期TI信號(hào)鏈基礎(chǔ)知識(shí),由我曾經(jīng)工作過(guò)的最有才華的RF /高速系統(tǒng)公司之一 - 羅伯特·凱勒(Robert Keller)撰寫。請(qǐng)享用。隨著模數(shù)轉(zhuǎn)換器(ADC)的采樣率和輸入頻率

2017-04-26 12:04:25

抖動(dòng)的知識(shí)及測(cè)量方法

時(shí)間不確定。這種不確定就是抖動(dòng)。抖動(dòng)是對(duì)信號(hào)時(shí)域變化的測(cè)量結(jié)果,它從本質(zhì)上描述了信號(hào)周期距離其理想值偏離了多少。在絕大多數(shù)文獻(xiàn)和規(guī)范中,時(shí)間抖動(dòng)(jitter)被定義為高速串行信號(hào)邊沿到來(lái)時(shí)刻與理想時(shí)刻

2008-11-27 08:28:56

時(shí)鐘抖動(dòng)會(huì)對(duì)高速ADC的性能有什么影響?

對(duì)高速信號(hào)進(jìn)行高分辨率的數(shù)字化處理需審慎選擇時(shí)鐘,才不至于使其影響模數(shù)轉(zhuǎn)換器(ADC)的性能。那么時(shí)鐘抖動(dòng)會(huì)對(duì)高速ADC的性能有什么影響呢?

2021-04-08 06:00:04

時(shí)鐘抖動(dòng)傳遞及其性能

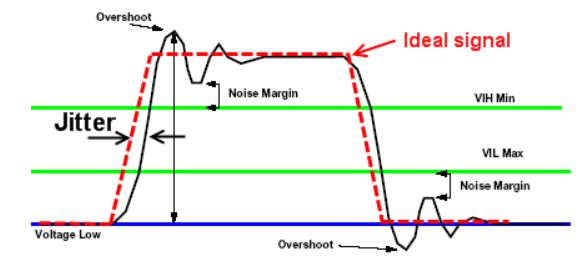

圖1強(qiáng)調(diào)了噪聲源而不是固有抖動(dòng)會(huì)引起定時(shí)抖動(dòng)錯(cuò)誤。更快的邊沿速率減少了時(shí)鐘信號(hào)上的電壓噪聲對(duì)時(shí)鐘抖動(dòng)性能的影響。這種現(xiàn)象并非是僅屬于時(shí)鐘信號(hào)的特點(diǎn)。在接收時(shí)鐘信號(hào)或測(cè)量抖動(dòng)性能的設(shè)備內(nèi),這種機(jī)理也表現(xiàn)得很明顯。…

2022-11-23 07:59:49

時(shí)鐘抖動(dòng)對(duì)高速鏈路性能的影響

作者:John Johnson,德州儀器 本文介紹時(shí)鐘抖動(dòng)對(duì)高速鏈路性能的影響。我們將重點(diǎn)介紹抖動(dòng)預(yù)算基礎(chǔ)。 用于在更遠(yuǎn)距離對(duì)日益增長(zhǎng)的海量數(shù)據(jù)進(jìn)行傳輸?shù)囊恍?biāo)準(zhǔn)不斷出現(xiàn)。來(lái)自各行業(yè)的工程師們組成

2018-09-19 14:23:47

時(shí)鐘抖動(dòng)對(duì)高速鏈路性能的影響

本文介紹時(shí)鐘抖動(dòng)對(duì)高速鏈路性能的影響。我們將重點(diǎn)介紹抖動(dòng)預(yù)算基礎(chǔ)。 用于在更遠(yuǎn)距離對(duì)日益增長(zhǎng)的海量數(shù)據(jù)進(jìn)行傳輸?shù)囊恍?biāo)準(zhǔn)不斷出現(xiàn)。來(lái)自各行業(yè)的工程師們組成了各種委員會(huì)和標(biāo)準(zhǔn)機(jī)構(gòu),根據(jù)其開發(fā)標(biāo)準(zhǔn)的目標(biāo)

2022-11-23 06:59:24

高速時(shí)鐘如何驅(qū)動(dòng)串行鏈路?

的時(shí)鐘)。高速時(shí)鐘如何驅(qū)動(dòng)串行鏈路?我應(yīng)該在哪里連接?以上來(lái)自于谷歌翻譯以下為原文Hi all, I want to connect twoFreeware ML605 boards

2019-02-13 06:22:28

高速串行鏈路系統(tǒng)對(duì)信號(hào)的影響是什么?

高速串行鏈路系統(tǒng)對(duì)信號(hào)的影響是什么?常用的補(bǔ)償技術(shù)有哪些?

2021-06-10 06:20:34

一個(gè)低抖動(dòng)時(shí)鐘源的參考設(shè)計(jì),不看肯定后悔

本文為高速數(shù)據(jù)轉(zhuǎn)換器提供了一個(gè)低抖動(dòng)時(shí)鐘源的參考設(shè)計(jì),目標(biāo)是在時(shí)鐘頻率高達(dá)2GHz時(shí),邊沿間抖動(dòng)《 100fs。對(duì)于1GHz模擬輸出頻率,所產(chǎn)生的抖動(dòng)信噪比SNR為:-20 × log(2 × π × f × tj) = -64dB。

2021-04-15 06:28:19

儀器基礎(chǔ)教程系列之時(shí)鐘信號(hào)、抖動(dòng)、遲滯和眼圖

了解時(shí)鐘信號(hào)的數(shù)字定時(shí)以及諸如抖動(dòng)、漂移、上升時(shí)間、下降時(shí)間、穩(wěn)定時(shí)間、遲滯和眼圖等常用術(shù)語(yǔ)。 本教程是儀器基礎(chǔ)教程系列的一部分。1. 時(shí)鐘信號(hào)發(fā)送數(shù)字信號(hào)其實(shí)發(fā)送的就是一串由0或1組成的數(shù)字序列

2019-06-12 08:00:00

各種抖動(dòng)技術(shù)規(guī)范是什么?抖動(dòng)的影響有哪些?

各種抖動(dòng)技術(shù)規(guī)范是什么抖動(dòng)的影響有哪些

2021-04-06 09:22:00

各種抖動(dòng)技術(shù)規(guī)范理解

,對(duì)各種抖動(dòng)技術(shù)規(guī)范的更深入理解現(xiàn)已變得非常重要。從 10Gb 以太網(wǎng)網(wǎng)絡(luò)到 PCIe 等高速互聯(lián)技術(shù),鏈路中所暗含的穩(wěn)健性都與降低定時(shí)裕度密切相關(guān)。簡(jiǎn)言之,抖動(dòng)就是信號(hào)邊沿與理想值或理想間隔的偏差

2018-09-13 14:29:18

基于TLK10081的千兆以太網(wǎng)多速率鏈路聚合器參考設(shè)計(jì)包括原理圖和BOM表

的外部抖動(dòng)消除時(shí)鐘每個(gè)通道的功耗最低(額定 800mW/通道)鏈路聚合將低速信號(hào)多路復(fù)用到單一的高速串行鏈路,從而有助于減少系統(tǒng)中的電纜或路由線跡使用 TLK10081 在系統(tǒng)的接收側(cè)進(jìn)行解聚

2018-08-03 08:32:03

基于級(jí)聯(lián)PLL的超低噪聲精密時(shí)鐘抖動(dòng)濾除技術(shù)仿真和研究設(shè)計(jì)

本文針對(duì)全方位的信號(hào)路徑系統(tǒng)中的高速全差分運(yùn)放及高頻寬14位模擬/數(shù)字轉(zhuǎn)換器的隨機(jī)及固定時(shí)鐘抖動(dòng),具體分析、研究了超低噪聲兼時(shí)鐘抖動(dòng)濾除技術(shù)。研究選用雙級(jí)聯(lián)PLLatinum架構(gòu),配置高性能壓控振蕩器(VCXO),很好地實(shí)現(xiàn)了降噪和時(shí)鐘抖動(dòng)濾除的作用。

2019-07-05 07:47:46

如何實(shí)現(xiàn)低抖動(dòng)采樣時(shí)鐘電路的設(shè)計(jì)?

采樣時(shí)鐘抖動(dòng)對(duì)ADC信噪比的性能有什么影響?如何實(shí)現(xiàn)低抖動(dòng)采樣時(shí)鐘電路的設(shè)計(jì)?

2021-04-14 06:49:20

如何更好地理解各種抖動(dòng)技術(shù)規(guī)范

今天,我將幫助您了解如何更好地理解各種抖動(dòng)技術(shù)規(guī)范。隨著高速應(yīng)用中的定時(shí)要求日趨嚴(yán)格,對(duì)各種抖動(dòng)技術(shù)規(guī)范的更深入理解現(xiàn)已變得非常重要。從 10Gb 以太網(wǎng)網(wǎng)絡(luò)到 PCIe 等高速互聯(lián)技術(shù),鏈路中所

2022-11-21 06:02:44

干貨 | 信號(hào)鏈基礎(chǔ)知識(shí)合輯 1-10

模擬信號(hào)鏈的基本構(gòu)建塊予以探討和研究。討論運(yùn)放的一些基本應(yīng)用,描述一些運(yùn)放性能的指標(biāo),包括模擬信號(hào)處理以及支持這些功能所必須的器件。歡迎多提保貴意見和建議。 早在推出這本信號(hào)鏈基礎(chǔ)知識(shí)合集之前,我們還推出

2019-01-05 09:45:19

微控制時(shí)鐘抖動(dòng)如何改善?

。這工作正常,直到我決定董事會(huì)所做的測(cè)量不夠準(zhǔn)確(在時(shí)間軸上)。因此,我將生成的時(shí)鐘使能信號(hào)(2MHz)輸出到IO-Pin,并使用示波器測(cè)量頻率抖動(dòng)。抖動(dòng)似乎具有高斯分布,標(biāo)準(zhǔn)偏差約為28ns。我還測(cè)量

2020-08-19 06:09:57

數(shù)字定時(shí): 時(shí)鐘信號(hào)、抖動(dòng)、遲滯和眼圖

了解時(shí)鐘信號(hào)的數(shù)字定時(shí)以及諸如抖動(dòng)、漂移、上升時(shí)間、下降時(shí)間、穩(wěn)定時(shí)間、遲滯和眼圖等常用術(shù)語(yǔ)。 本教程是儀器基礎(chǔ)教程系列的一部分。1. 時(shí)鐘信號(hào)發(fā)送數(shù)字信號(hào)其實(shí)發(fā)送的就是一串由0或1組成的數(shù)字序列

2016-01-18 15:31:09

時(shí)間抖動(dòng)的概念及其分析方法介紹

。不僅如此,它還會(huì)導(dǎo)致通信鏈路的誤碼率增大,甚至限制A/D轉(zhuǎn)換器的動(dòng)態(tài)范圍。有資料表明在3GHz以上的系統(tǒng)中,時(shí)間抖動(dòng)(jitter)會(huì)導(dǎo)致碼間干擾(ISI),造成傳輸誤碼率上升。在此趨勢(shì)下,高速數(shù)字設(shè)備

2019-06-04 07:16:09

構(gòu)建JESD204B鏈路的步驟

建立了所需的電氣連接,如圖 1 所示。請(qǐng)注意圖中箭頭表示信號(hào)方向。圖1 —JESD204B TX 至RX 鏈路的信號(hào)連接從 TX (tx_dataout) 到 RX 的信號(hào)是包含數(shù)據(jù)鏈路的串行解串器信道

2018-09-13 09:55:26

構(gòu)建JESD204B鏈路的步驟

連接,如圖 1 所示。請(qǐng)注意圖中箭頭表示信號(hào)方向。圖 1 — JESD204B TX 至 RX 鏈路的信號(hào)連接從 TX (tx_dataout) 到 RX 的信號(hào)是包含數(shù)據(jù)鏈路的串行解串器信道信號(hào)。這些

2022-11-21 07:18:42

測(cè)量時(shí)鐘緩沖器的附加抖動(dòng)

需求。作為該最新博客系列的開篇文章,我將幫助您了解如何正確測(cè)量時(shí)鐘緩沖器的附加抖動(dòng)。為什么抖動(dòng)很重要?在當(dāng)今數(shù)據(jù)通信、有線及無(wú)線基礎(chǔ)設(shè)施以及其它高速應(yīng)用等高級(jí)系統(tǒng)中,時(shí)鐘抖動(dòng)是整體系統(tǒng)性能的關(guān)鍵因素。要

2018-09-13 14:38:43

簡(jiǎn)談數(shù)字電路設(shè)計(jì)中的抖動(dòng)

中日益得到人們的重視。在高速系統(tǒng)中,時(shí)鐘或振蕩器波形的時(shí)序誤差會(huì)限制一個(gè)數(shù)字I/O接口的最大速率。不僅如此,它還會(huì)導(dǎo)致通信鏈路的誤碼率增大,甚至限制A/D轉(zhuǎn)換器的動(dòng)態(tài)范圍。在此趨勢(shì)下,高速數(shù)字設(shè)備

2018-02-25 12:23:44

系統(tǒng)同步多通道數(shù)字鏈路怎么設(shè)計(jì)

嗨,我有一個(gè)項(xiàng)目,我必須在發(fā)送器端序列化16位數(shù)字輸入數(shù)據(jù),然后在接收器端反序列化數(shù)據(jù)。這種數(shù)字鏈路的預(yù)期速度是100MHz-500MHz。這種實(shí)現(xiàn)必須是系統(tǒng)同步的,即沒有任何時(shí)鐘轉(zhuǎn)發(fā),我必須在Rx

2019-08-06 10:31:49

請(qǐng)問(wèn)時(shí)鐘抖動(dòng)如何處理?

一塊音視頻處理芯片輸出1080i的數(shù)據(jù)Data及其同步時(shí)鐘Clk,但是時(shí)鐘clk的抖動(dòng)很大,我該如何處理呢?另外,抖動(dòng)很大的時(shí)鐘源能否在后面接入一個(gè)模擬鎖相環(huán)降低時(shí)鐘的抖動(dòng)呢?

2018-11-12 09:12:43

請(qǐng)問(wèn)時(shí)鐘抖動(dòng)或結(jié)束時(shí)鐘抖動(dòng)的最佳方法是什么?

時(shí)鐘抖動(dòng)或結(jié)束時(shí)鐘抖動(dòng)的最佳方法是什么?

2021-03-17 07:04:07

超低抖動(dòng)時(shí)鐘發(fā)生器與串行鏈路系統(tǒng)性能的優(yōu)化

爬升到25GbE,并且允許的BER在1e-18時(shí)變?yōu)闃?biāo)準(zhǔn)值,高質(zhì)量、低抖動(dòng)基準(zhǔn)時(shí)鐘在保護(hù)信號(hào)完整性方面的重要性變得不可小覷。在用一個(gè)眼圖來(lái)解決鏈路無(wú)法正常運(yùn)行的問(wèn)題后,你現(xiàn)在需要確保你的設(shè)計(jì)是穩(wěn)健耐用

2018-09-05 16:07:30

超低抖動(dòng)時(shí)鐘發(fā)生器優(yōu)化串行鏈路系統(tǒng)性能的過(guò)程

程度!隨著數(shù)據(jù)速率的增加,鏈路抖動(dòng)允許量變得越來(lái)越嚴(yán)格。硬件工程師將主要精力放在如何使他們的整個(gè)線路卡能夠支持最大吞吐量,而為基準(zhǔn)時(shí)鐘產(chǎn)生的隨機(jī)抖動(dòng)分配盡可能小的允許量。針對(duì)基準(zhǔn)時(shí)鐘,對(duì)于一條25GbE

2022-11-18 07:31:24

利用頻域時(shí)鐘抖動(dòng)分析加快設(shè)計(jì)驗(yàn)證過(guò)程

隨著數(shù)據(jù)速率的提高,時(shí)鐘抖動(dòng)分析的需求也在與日俱增。在高速串行數(shù)據(jù)鏈路中,時(shí)鐘抖動(dòng)會(huì)影響發(fā)射機(jī)、傳輸線和接收機(jī)的數(shù)據(jù)抖動(dòng)。保證時(shí)鐘質(zhì)量的測(cè)量也在不斷發(fā)展

2008-12-27 12:24:05 6

6

6

6利用頻域時(shí)鐘抖動(dòng)分析加快設(shè)計(jì)驗(yàn)證過(guò)程

隨著數(shù)據(jù)速率的提高,時(shí)鐘抖動(dòng)分析的需求也在與日俱增。在高速串行數(shù)據(jù)鏈路中,時(shí)鐘抖動(dòng)會(huì)影響發(fā)射機(jī)、傳輸線和接收機(jī)的數(shù)據(jù)抖動(dòng)。保證時(shí)鐘質(zhì)量的測(cè)量也在不斷發(fā)展。目前

2009-07-07 14:01:21 20

20

20

20用于高速AD的低抖動(dòng)時(shí)鐘穩(wěn)定電路

介紹了一種用于高速ADC 的低抖動(dòng)時(shí)鐘穩(wěn)定電路。這個(gè)電路由延遲鎖相環(huán)(DLL)來(lái)實(shí)現(xiàn)。這個(gè)DLL 有兩個(gè)功能:一是通過(guò)把一個(gè)時(shí)鐘沿固定精確延遲半個(gè)周期,再與另一個(gè)沿組成一個(gè)新

2009-11-26 15:55:15 28

28

28

28高速ADC的低抖動(dòng)時(shí)鐘設(shè)計(jì)

本文主要討論采樣時(shí)鐘抖動(dòng)對(duì)ADC 信噪比性能的影響以及低抖動(dòng)采樣時(shí)鐘電路的設(shè)計(jì)。

2009-11-27 11:24:07 15

15

15

15高速互聯(lián)鏈路中參考時(shí)鐘的抖動(dòng)分析與測(cè)量

高速互聯(lián)鏈路中參考時(shí)鐘的抖動(dòng)分析與測(cè)量

在高速互聯(lián)鏈路中,發(fā)送器的參考工作時(shí)鐘的抖動(dòng)是影響整個(gè)

2010-04-15 14:01:39 19

19

19

19超低抖動(dòng)時(shí)鐘合成器的設(shè)計(jì)挑戰(zhàn)

該應(yīng)用筆記提出了超低抖動(dòng)時(shí)鐘合成器的一種設(shè)計(jì)思路,其目標(biāo)是產(chǎn)生2GHz時(shí)鐘時(shí),邊沿之間的抖動(dòng)< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動(dòng)指標(biāo),設(shè)計(jì)難度遠(yuǎn)遠(yuǎn)高于預(yù)期。關(guān)

2009-04-21 23:14:05 723

723

723

723

超低抖動(dòng)時(shí)鐘合成器的設(shè)計(jì)挑戰(zhàn)

摘要:該應(yīng)用筆記提出了超低抖動(dòng)時(shí)鐘合成器的一種設(shè)計(jì)思路,其目標(biāo)是產(chǎn)生2GHz時(shí)鐘時(shí),邊沿之間的抖動(dòng)< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動(dòng)指標(biāo),設(shè)計(jì)難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-04-22 09:35:13 296

296

296

296

時(shí)鐘抖動(dòng)(CLK)和相位噪聲之間的轉(zhuǎn)換

摘要:這是一篇關(guān)于時(shí)鐘(CLK)信號(hào)質(zhì)量的應(yīng)用筆記,介紹如何測(cè)量抖動(dòng)和相位噪聲,包括周期抖動(dòng)、逐周期抖動(dòng)和累加抖動(dòng)。本文還描述了周期抖動(dòng)和相位噪聲譜之間的關(guān)系,并介紹

2009-04-22 10:16:50 3736

3736

3736

3736

超低抖動(dòng)時(shí)鐘合成器的設(shè)計(jì)挑戰(zhàn)

摘要:該應(yīng)用筆記提出了超低抖動(dòng)時(shí)鐘合成器的一種設(shè)計(jì)思路,其目標(biāo)是產(chǎn)生2GHz時(shí)鐘時(shí),邊沿之間的抖動(dòng)< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動(dòng)指標(biāo),設(shè)計(jì)難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-04-25 09:54:26 482

482

482

482

超低抖動(dòng)時(shí)鐘合成器的設(shè)計(jì)挑戰(zhàn)

摘要:該應(yīng)用筆記提出了超低抖動(dòng)時(shí)鐘合成器的一種設(shè)計(jì)思路,其目標(biāo)是產(chǎn)生2GHz時(shí)鐘時(shí),邊沿之間的抖動(dòng)< 100fs。分析和仿真結(jié)果表明,要達(dá)到這一抖動(dòng)指標(biāo),設(shè)計(jì)難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-05-08 10:19:03 431

431

431

431

理解不同類型的時(shí)鐘抖動(dòng)

理解不同類型的時(shí)鐘抖動(dòng)

抖動(dòng)定義為信號(hào)距離其理想位置的偏離。本文將重點(diǎn)研究時(shí)鐘抖動(dòng),并探討下面幾種類型的時(shí)鐘抖動(dòng):相鄰周期抖動(dòng)、周期抖動(dòng)、時(shí)間間隔誤

2010-01-06 11:48:11 1608

1608

1608

1608

時(shí)鐘抖動(dòng)和相位噪聲對(duì)采樣系統(tǒng)的影響

如果明智地選擇時(shí)鐘,一份簡(jiǎn)單的抖動(dòng)規(guī)范幾乎是不夠的。而重要的是,你要知道時(shí)鐘噪聲的帶寬和頻譜形狀,才能在采樣過(guò)程中適當(dāng)?shù)貙⑺鼈兛紤]進(jìn)去。很多系統(tǒng)設(shè)計(jì)師對(duì)數(shù)據(jù)轉(zhuǎn)換器

2012-05-08 15:29:00 47

47

47

47時(shí)鐘抖動(dòng)的基礎(chǔ)

介紹 此應(yīng)用筆記側(cè)重于不同類型的時(shí)鐘抖動(dòng)。時(shí)鐘抖動(dòng)是從它的時(shí)鐘邊沿偏差理想的位置。了解時(shí)鐘抖動(dòng)非常重要在應(yīng)用中,因?yàn)樗鹬P(guān)鍵作用,在時(shí)間預(yù)算一個(gè)系統(tǒng)。 隨著系統(tǒng)數(shù)據(jù)速率的增加,定時(shí)抖動(dòng)成為關(guān)鍵

2017-04-01 16:13:18 6

6

6

6高速ADC時(shí)鐘抖動(dòng)的影響的了解

了解高速ADC時(shí)鐘抖動(dòng)的影響將高速信號(hào)數(shù)字化到高分辨率要求仔細(xì)選擇一個(gè)時(shí)鐘,不會(huì)妥協(xié)模數(shù)轉(zhuǎn)換器的采樣性能(ADC)。 在這篇文章中,我們希望給讀者一個(gè)更好的了解時(shí)鐘抖動(dòng)及其影響高速模數(shù)轉(zhuǎn)換器的性能

2017-05-15 15:20:59 13

13

13

13時(shí)鐘抖動(dòng)時(shí)域分析

級(jí),從而降低成本和功耗。在欠采樣接收機(jī)設(shè)計(jì)中必須要特別注意采樣時(shí)鐘,因?yàn)樵谝恍└咻斎腩l率下時(shí)鐘抖動(dòng)會(huì)成為限制信噪比(SNR) 的主要原因。 本系列文章共有三部分,第1 部分重點(diǎn)介紹如何準(zhǔn)確地估算某個(gè)時(shí)鐘源的抖動(dòng),以及如何將其與AD

2017-05-18 09:47:38 1

1

1

1基于改進(jìn)延遲鎖相環(huán)的高速低抖動(dòng)時(shí)鐘電路的開發(fā)與設(shè)計(jì)

時(shí)鐘產(chǎn)生抖動(dòng)(jitter)會(huì)使發(fā)生抖動(dòng)的時(shí)鐘信號(hào)與未發(fā)生抖動(dòng)的時(shí)鐘信號(hào)在時(shí)域上存在偏差,從而使模數(shù)轉(zhuǎn)換器的采樣頻率發(fā)生紊亂,最終導(dǎo)致模數(shù)轉(zhuǎn)換器采樣的不穩(wěn)定性,使輸出信號(hào)存在頻譜毛刺,導(dǎo)致誤碼率上升

2017-11-11 18:22:26 9

9

9

9高速ADC在低抖動(dòng)采樣時(shí)鐘電路設(shè)計(jì)中的應(yīng)用

本文主要討論采樣時(shí)鐘抖動(dòng)對(duì) ADC 信噪比性能的影響以及低抖動(dòng)采樣時(shí)鐘電路的設(shè)計(jì)。 ADC 是現(xiàn)代數(shù)字解調(diào)器和軟件無(wú)線電接收機(jī)中連接模擬信號(hào)處理部分和數(shù)字信號(hào)處理部分的橋梁,其性能在很大程度上決定

2017-11-27 14:59:20 17

17

17

17時(shí)鐘抖動(dòng)的4大根本原因及3種查看途徑

時(shí)鐘接口閾值區(qū)間附近的抖動(dòng)會(huì)破壞ADC的時(shí)序。例如,抖動(dòng)會(huì)導(dǎo)致確定性抖動(dòng)由干擾引起,會(huì)通過(guò)某些方式使閾值發(fā)生偏移,通常受器件本身特性限制。查看時(shí)鐘信號(hào)噪聲通常有三種途徑:時(shí)域、頻域、相位域。

2018-03-12 13:39:33 21583

21583

21583

21583三分鐘教會(huì)你,級(jí)聯(lián)PLL超低噪聲精密時(shí)鐘抖動(dòng)濾除技術(shù)研究

本文針對(duì)全方位的信號(hào)路徑系統(tǒng)中的高速全差分運(yùn)放及高頻寬14位模擬/數(shù)字轉(zhuǎn)換器的隨機(jī)及固定時(shí)鐘抖動(dòng),具體分析、研究了超低噪聲兼時(shí)鐘抖動(dòng)濾除技術(shù)。

2018-05-30 09:00:00 5165

5165

5165

5165

關(guān)于時(shí)鐘抖動(dòng)的原因及查看途徑分析

時(shí)鐘設(shè)計(jì)人員通常會(huì)提供一個(gè)相位噪聲,但不提供抖動(dòng)規(guī)格。相位噪聲規(guī)格可以轉(zhuǎn)換為抖動(dòng),首先確定時(shí)鐘噪聲,然后通過(guò)小角度計(jì)算將噪聲與主時(shí)鐘噪聲成分進(jìn)行比較。相位噪聲功率通過(guò)計(jì)算圖9中的灰色區(qū)域積分得出。

2019-08-20 11:06:53 7787

7787

7787

7787

時(shí)鐘抖動(dòng)性能和相位噪聲測(cè)量

時(shí)鐘抖動(dòng)性能主題似乎是時(shí)鐘,ADC和電源的當(dāng)前焦點(diǎn)供應(yīng)廠家。理由很清楚;時(shí)鐘抖動(dòng)會(huì)干擾包括高速ADC在內(nèi)的數(shù)字電路的性能。高速時(shí)鐘可以對(duì)它們所接收的功率的“清潔度”非常敏感,盡管量化關(guān)系需要一些努力。

2019-09-14 11:24:00 7712

7712

7712

7712

級(jí)聯(lián)式PLL時(shí)鐘抖動(dòng)濾除技術(shù)實(shí)現(xiàn)的設(shè)計(jì)說(shuō)明

本文針對(duì)全方位的信號(hào)路徑系統(tǒng)中的高速全差分運(yùn)放及高頻寬14位模擬/數(shù)字轉(zhuǎn)換器的隨機(jī)及固定時(shí)鐘抖動(dòng),具體分析、研究了超低噪聲兼時(shí)鐘抖動(dòng)濾除技術(shù)。研究選用雙級(jí)聯(lián)PLLatinum架構(gòu),配置高性能壓控振蕩器(VCXO),很好地實(shí)現(xiàn)了降噪和時(shí)鐘抖動(dòng)濾除的作用。

2020-09-23 10:45:00 2

2

2

2高速模數(shù)轉(zhuǎn)換器的性能分析及時(shí)鐘抖動(dòng)會(huì)對(duì)其造成什么影響

對(duì)高速信號(hào)進(jìn)行高分辨率的數(shù)字化處理需審慎選擇時(shí)鐘,才不至于使其影響模數(shù)轉(zhuǎn)換器(ADC)的性能。借助本文,我們將使讀者更好地理解時(shí)鐘抖動(dòng)問(wèn)題及其對(duì)高速ADC性能的影響。

2020-08-20 14:25:16 791

791

791

791

AD9524:帶6路差分或13路LVCMOS輸出的抖動(dòng)凈化器和時(shí)鐘發(fā)

AD9524:帶6路差分或13路LVCMOS輸出的抖動(dòng)凈化器和時(shí)鐘發(fā)

2021-03-19 07:03:02 10

10

10

10AD9525: 8路LVPECL輸出低抖動(dòng)時(shí)鐘發(fā)生器

AD9525: 8路LVPECL輸出低抖動(dòng)時(shí)鐘發(fā)生器

2021-03-21 15:00:20 0

0

0

0如何去正確理解采樣時(shí)鐘抖動(dòng)(Jitter)對(duì)ADC信噪比SNR的影響

高速ADC使用外部輸入時(shí)鐘對(duì)模擬輸入信號(hào)進(jìn)行采樣,如圖1所示。圖中顯示了輸入采樣時(shí)鐘抖動(dòng)示意圖。 圖1、ADC采樣 輸入模擬信號(hào)的頻率越高,由于時(shí)鐘抖動(dòng)導(dǎo)致的采樣信號(hào)幅度變化越大,這點(diǎn)在圖2中顯示的非常明顯。輸入信號(hào)頻率為F2=100MHz時(shí),采樣幅度變化如圖紅色虛

2021-04-07 16:43:45 7378

7378

7378

7378

高速鏈路時(shí)鐘抖動(dòng)規(guī)范基礎(chǔ)知識(shí)

作者:John Johnson,德州儀器?

?

本文介紹時(shí)鐘抖動(dòng)對(duì)高速鏈路性能的影響。我們將重點(diǎn)介紹抖動(dòng)預(yù)算基礎(chǔ)。

?

用于在更遠(yuǎn)距離對(duì)日益增長(zhǎng)的海量數(shù)據(jù)進(jìn)行傳輸?shù)囊恍?biāo)準(zhǔn)不斷出現(xiàn)。來(lái)自

2021-11-22 15:52:21 1284

1284

1284

1284

比較和對(duì)比PCIe和以太網(wǎng)時(shí)鐘抖動(dòng)規(guī)范

PCIe 和網(wǎng)絡(luò)時(shí)鐘抖動(dòng)測(cè)量之間的另一個(gè)顯著差異在圖 2 中并不明顯。數(shù)字采樣示波器 (DSO) 用于獲取時(shí)鐘周期或波形文件以計(jì)算 PCIe 時(shí)鐘抖動(dòng),而不是 PNA。造成這種情況的主要原因是 PCIe 時(shí)鐘支持?jǐn)U頻,而網(wǎng)絡(luò)時(shí)鐘不支持,而且從歷史上看,PNA 一直無(wú)法使用正在擴(kuò)頻的時(shí)鐘。

2022-05-05 15:50:44 4513

4513

4513

4513

時(shí)鐘抖動(dòng)解秘—高速鏈路時(shí)鐘抖動(dòng)規(guī)范基礎(chǔ)知識(shí)

時(shí)鐘抖動(dòng)解秘—高速鏈路時(shí)鐘抖動(dòng)規(guī)范基礎(chǔ)知識(shí)

2022-11-07 08:07:30 1

1

1

1最大信噪比與時(shí)鐘抖動(dòng)的關(guān)系

對(duì)于頻率成分相對(duì)較低的輸入信號(hào),例如在1MHz以下,時(shí)鐘抖動(dòng)變得不那么重要,但是當(dāng)輸入信號(hào)的頻率為幾百兆赫茲時(shí),時(shí)鐘上的抖動(dòng)將成為誤差的主要來(lái)源,并且將成為SNR的限制因素。

2023-01-03 14:35:04 823

823

823

823

為高速數(shù)據(jù)轉(zhuǎn)換器設(shè)計(jì)低抖動(dòng)時(shí)鐘

在設(shè)計(jì)中使用超快速數(shù)據(jù)轉(zhuǎn)換器的高速應(yīng)用通常需要非常干凈的時(shí)鐘信號(hào),以確保外部時(shí)鐘源不會(huì)對(duì)系統(tǒng)的整體動(dòng)態(tài)性能產(chǎn)生不需要的噪聲。因此,選擇合適的系統(tǒng)組件至關(guān)重要,這有助于產(chǎn)生低相位抖動(dòng)時(shí)鐘。以下應(yīng)用筆記可作為選擇合適的元件的寶貴指南,以設(shè)計(jì)適用于超快速數(shù)據(jù)轉(zhuǎn)換器的基于PLL的低相位噪聲時(shí)鐘發(fā)生器。

2023-02-25 10:50:48 2307

2307

2307

2307

時(shí)鐘抖動(dòng)的影響

1.1.1.??抖動(dòng)定義和分類 ITU-T G.701對(duì)抖動(dòng)的定義為:“抖動(dòng)是指數(shù)字信號(hào)在短期內(nèi)相對(duì)于理想位置發(fā)生的偏移重大影響的短時(shí)變化”。 對(duì)于真實(shí)物理世界中的時(shí)鐘源,比如晶振、DLL、PLL,它們的時(shí)鐘輸出周期都不可能是一個(gè)單點(diǎn)的固定值,而是隨時(shí)間而變化的

2023-03-10 14:54:32 657

657

657

657

時(shí)鐘抖動(dòng)的影響

抖動(dòng)和相位噪聲是晶振的非常重要指標(biāo),本文主要從抖動(dòng)和相位噪聲定義及原理出發(fā),闡述其在不同場(chǎng)景下對(duì)數(shù)字系統(tǒng)、高速串行接口、數(shù)據(jù)轉(zhuǎn)換器和射頻系統(tǒng)的影響。

2023-03-26 09:09:11 693

693

693

693

時(shí)鐘抖動(dòng)和時(shí)鐘偏斜講解

系統(tǒng)時(shí)序設(shè)計(jì)中對(duì)時(shí)鐘信號(hào)的要求是非常嚴(yán)格的,因?yàn)槲覀兯械臅r(shí)序計(jì)算都是以恒定的時(shí)鐘信號(hào)為基準(zhǔn)。但實(shí)際中時(shí)鐘信號(hào)往往不可能總是那么完美,會(huì)出現(xiàn)抖動(dòng)(Jitter)和偏移(Skew)問(wèn)題。

2023-04-04 09:20:56 1637

1637

1637

1637時(shí)鐘抖動(dòng)會(huì)影響建立時(shí)間和保持時(shí)間違例嗎?

首先,我們需要理解什么是時(shí)鐘抖動(dòng)。簡(jiǎn)而言之,時(shí)鐘抖動(dòng)(Jitter)反映的是時(shí)鐘源在時(shí)鐘邊沿的不確定性(Clock Uncertainty)。

2023-06-02 09:09:06 1025

1025

1025

1025

時(shí)鐘抖動(dòng)的幾種類型

理想值附近的一個(gè)范圍內(nèi),從而造成相鄰的時(shí)鐘邊沿存在偏差。在時(shí)序分析時(shí),時(shí)鐘抖動(dòng)是一個(gè)重要的因素。多種因素會(huì)導(dǎo)致時(shí)鐘抖動(dòng),包括PLL回路噪聲、電源紋波、熱噪聲以及信號(hào)之間的串?dāng)_等。

2023-06-09 09:40:50 1128

1128

1128

1128

時(shí)鐘抖動(dòng)對(duì)ADC性能有什么影響

電子發(fā)燒友網(wǎng)站提供《時(shí)鐘抖動(dòng)對(duì)ADC性能有什么影響.pdf》資料免費(fèi)下載

2023-11-28 10:24:10 1

1

1

1示波器測(cè)量之抖動(dòng)的四個(gè)維度

,包括時(shí)鐘抖動(dòng)、噪聲抖動(dòng)、跳變抖動(dòng)和漂移抖動(dòng)。 時(shí)鐘抖動(dòng)是指時(shí)鐘信號(hào)在頻率和相位上的變化。時(shí)鐘信號(hào)是大多數(shù)電子系統(tǒng)中用于同步和定時(shí)的關(guān)鍵信號(hào),其穩(wěn)定性對(duì)系統(tǒng)的性能有著重要影響。時(shí)鐘抖動(dòng)會(huì)導(dǎo)致測(cè)量結(jié)果的不確定性

2024-01-19 15:01:31 254

254

254

254相位抖動(dòng)是從哪來(lái)的?通信中有哪些抖動(dòng)?

相位抖動(dòng)是從哪來(lái)的?通信中有哪些抖動(dòng)? 相位抖動(dòng)是指信號(hào)在傳輸過(guò)程中產(chǎn)生的相位變化,導(dǎo)致信號(hào)的相位偏離理想值的現(xiàn)象。它是由多種因素引起的,包括時(shí)鐘不準(zhǔn)確、傳輸介質(zhì)不穩(wěn)定、信號(hào)傳輸路徑不確定等。 時(shí)鐘

2024-01-25 15:29:28 171

171

171

171了解并盡量減少抖動(dòng)對(duì)高速鏈路的影響

,通常低于 100 飛秒 (fs),以保持系統(tǒng)性能。這些時(shí)鐘還必須長(zhǎng)期保持低抖動(dòng)規(guī)格,且不受溫度和電壓的影響。 某些抖動(dòng)是由信號(hào)路徑噪聲和失真引起的,使用重復(fù)時(shí)鐘和重定時(shí)技術(shù)可以在一定程度上減少抖動(dòng)。不過(guò),抖動(dòng)也是由時(shí)鐘源產(chǎn)生的,時(shí)鐘源通常是振蕩器。這是由于各

2024-02-13 17:47:00 621

621

621

621

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論