。在測量與控制電路中,寬帶放大器是調理傳感器輸出信號的重要環節。傳感器輸出的電平信號通常不是規則的正弦信號,且輸出電壓范圍往往變化很大,這就需要后級放大

2010-09-01 16:52:35 2654

2654

03電賽題目B寬帶放大器

2012-08-01 12:13:44

AN098用于電視調諧器應用的寬帶放大器MMIC。使用BGA616設計用于50 MHz和1 GHz頻段的通用寬帶放大器

2020-06-03 10:30:34

請各位高人指點:如何設計一個可編程放大器,最好附有電路圖,即硬件部分,謝謝啦

2012-10-17 19:38:14

包括可獨立應用的運放被專門設計成PGA、ASIC、集成有可編程濾波器的PGA、儀表放大器PGA、用于運放的數字電位器前端、PGA用數字可編程分壓器、ADC驅動器。有時把PGA和DAC集成在同一芯片上

2019-05-21 05:00:12

想通過調節可編程電阻的阻值來調整運算放大器的放大倍數,當可編程電阻不接在運算放大器上時可以正常的調節,一旦接到運算放大器上時就工作不正常,運算放大器為INA128,信號頻率為200KHZ,求大神幫助!!

2014-02-26 09:30:13

增益可調簡介ATA-1050是一款理想的可放大交、直流信號的單通道寬帶放大器。最大輸出33Vp-p (±16.5V)電壓,輸出電流 800mA,可與主流的信號發生器配套使用,實現信號的完美放大。并且具有

2017-08-31 16:17:59

寬帶放大器程序求助,用TM4C123GH6PM 寫的程序

2015-07-25 17:08:38

{:4:}寬帶放大器?求解,初次參加電子大賽,不懂

2013-08-31 17:04:41

最近在做09年電子設計大賽寬大放大器題 想請教到了一個問題:壓控放大器AD603可以其他那類放大器代替呢?還有與OPA642 OPA620 用能相似的寬帶放大器有哪些呢?感謝回帖~~

2013-08-13 00:03:14

寬帶放大器和預分頻器模塊可覆蓋直流至20 GHz

2019-05-06 13:12:46

:ATA-1372A寬帶放大器指標參數 ATA-1372A是一款可放大交直流信號的單通道寬帶放大器。其最大輸出電壓70Vp-p(±35Vp),最大輸出電流2Ap(>50Hz)。電壓增益數控可調,一鍵保存設置,提供了方便簡潔的操作選擇,可與主流的信號發生器配套使用,實現信號的放大。

2024-02-28 16:01:52

ATA-1000寬帶放大器簡介: ATA-1000 系列是一款理想的可放大交、直流信號的單通道寬帶放大器。最大輸出 33Vp-p(±16.5V)電壓,輸出電流 800mA,可與主流的信號發生器配套

2016-11-14 16:03:31

情況。

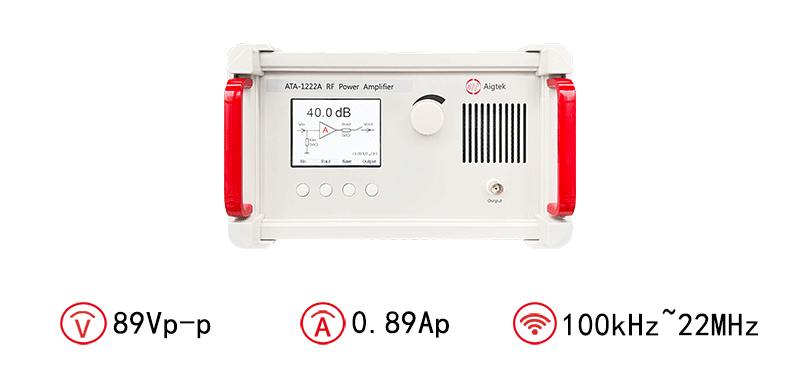

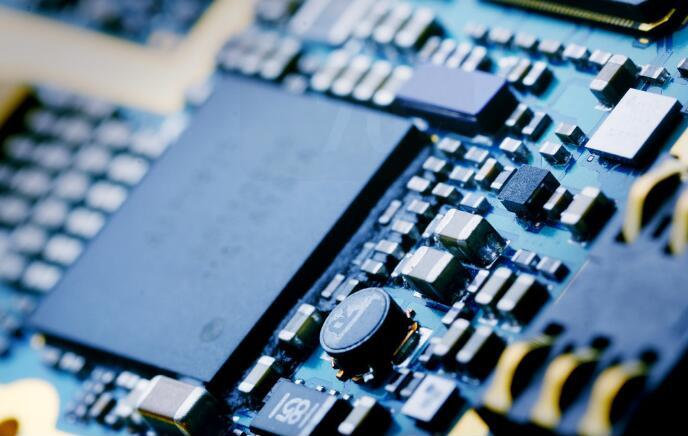

寬帶放大器推薦:ATA-1222A

圖:ATA-1222A寬帶放大器指標參數 ATA-1222A是一款寬帶放大器。其飽和輸出功率40W,增益P1dB壓縮點輸出功率20W。增益數控可調

2024-02-28 16:04:24

項目需求,需要用到 PGA可編程增益放大器,放大遞歸規律要為指數。需求參數:輸入信號為100KHz正弦波,程控增益倍數 Gain=1~256。于是帶寬積GBP >= 30MHz,壓擺率

2021-08-09 08:02:07

TI公司運算放大器做200M寬帶放大器的芯片

2017-04-19 10:24:41

描述使用 TI OPA2683 低功耗雙通道電流反饋放大器的低功耗全差動可編程增益放大器的參考設計。此設計指南回顧了創建這類電路所需的一些設計中的挑戰。設計指南回顧了結果并針對使用/設計低功耗

2018-07-23 07:18:17

描述 使用 TI OPA2683低功耗雙通道電流反饋放大器的低功耗全差動可編程增益放大器的參考設計。此設計指南回顧了創建這類電路所需的一些設計中的挑戰。設計指南回顧了結果并針對使用/設計低功耗

2022-09-27 07:34:51

全國大學生電子設計大賽收集整理的高頻類題目資料(射頻寬帶放大器),分享給有用的朋友!

2016-02-04 18:40:59

因為需要一個關于射頻寬帶放大器的設計,在網上查閱資料,發現大部分電子元器件的型號,具體參數以及一些電路都不知道。再次希望有人能幫下忙,叫我如何下手去設計一款射頻寬帶放大器。具體要求如下:設計要求

2014-04-18 12:52:58

本文提出了一種基于I2C總線的新型可編程增益放大器的設計方法,可根據輸入的模擬信號大小,自動選擇量程進行放大/衰減。

2021-04-21 06:01:39

設計說明該子系統演示了如何在可編程增益放大器 (PGA) 配置中設置 MSPM0 內部運算放大器,動態更改增益,輸出放大的信號以及使用 ADC 讀取結果。該配置使用戶能夠使用具有高增益的小輸入電壓

2023-04-12 15:01:32

ADG1611為四路單刀單擲開關,AD620是電阻可編程增益的放大器,請問這種放大器采用四通道的原因是什么?是那四個電阻嗎?

2019-01-08 16:43:14

請教在使用寬帶放大器放大時,如何減少放大信號的反向過沖?

2023-11-21 07:01:45

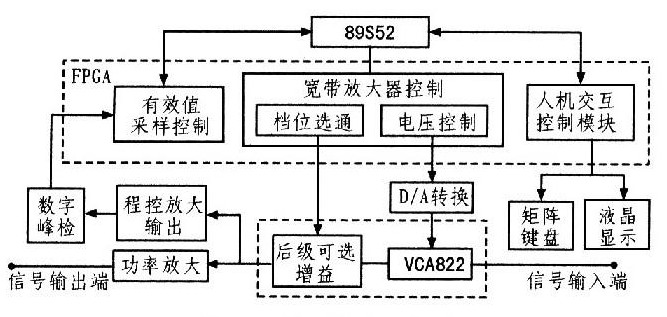

提出了一種采用數控方式的高增益、寬帶寬放大器。采用多個放大器直接耦合級聯的方式,有效改善了放大器的低頻特性,提高了放大增益范圍;數控增益自動穩定技術,有效帶寬內提高了增益穩定性;多個放大器增益統一

2010-05-04 08:05:33

求一款基于VCA822的可編程增益放大器設計方案

2021-04-09 06:54:23

什么是DPGA(數字可編程增益放大器)?如何設計一種采用發散指數曲線理念的新型DPGA?

2021-04-23 07:05:37

想請教大神射頻寬帶放大器設計的時候按照典型電路來為什么不能實現功能 有什么需要注意的地方?

2015-08-13 11:11:23

比賽結束了,選了D題的射頻寬帶放大器,菜鳥做的太差,有木有大神都做出來的,求教方法,想有空自己再接著做一下看看~~~~~~

2013-09-10 00:34:01

沒有要求步進,那么發揮余地比較大,用一片30dB的數控衰減器就行,類似產品HMC759一類,或者利用繼電器與電阻自己搭一個派型衰減網絡(此方法的誤差較大,而且帶寬會受繼電器與電阻影響),寬帶放大器盡量

2018-11-09 09:36:34

數字可編程增益放大器(DPGA)放大或減弱模擬信號,可最大限度地擴大模數轉換器(ADC)的動態范圍。大多數單片DPGA都在運算放大器的反饋環路中使用了多路復用乘法數模轉換器(DAC),如Maxim

2019-07-17 07:28:50

利用AD603和AD811制作一個0DB到60DB的數控增益寬帶放大器,RL=100歐,輸入信號10mV 1MHZ 該如何設計求原理圖 并注明器件參數

2013-08-01 08:47:15

武漢大學射頻寬帶放大器解析,很不錯,值得分享

2014-08-01 15:08:58

簡易夾具靜態測試可編程增益放大器的分析,看完你就懂了

2021-05-11 07:02:00

可編程增益放大器中的增益該怎樣理解?到具體編程中該如何操作?比如說增益選擇為1,2,4,8,16。如何在程序中進行操作?

2013-04-25 23:41:28

在使用CH32V307的時候,看到ADC初始化結構體中,有可編程放大器ADC_Pga參數,不知道它是否真實有用的?

2022-07-18 08:22:26

請教在使用寬帶放大器放大時,如何減少放大信號的反向過沖?

2018-08-24 11:38:53

怎么一種可編程寬帶運算放大器?如何實現可編程寬帶運算放大器的軟件設計?

2021-04-21 06:15:27

為什么要設計一種可編程放大器?怎樣去設計一種可編程放大器?可編程放大器有什么優點?

2021-04-22 07:06:51

購買RIGOL信號發生器DG5000系列贈送ATA1050寬帶放大器!購買RIGOL信號發生器DG5000系列贈送ATA1050寬帶放大器!如需采購請聯系當地代理商!

2016-12-20 16:51:15

采購AFG泰克信號發生器指定款,送ATA1050寬帶放大器!采購AFG泰克信號發生器指定款,送ATA1050寬帶放大器!如需采購請聯系當地代理商。

2016-12-20 16:48:37

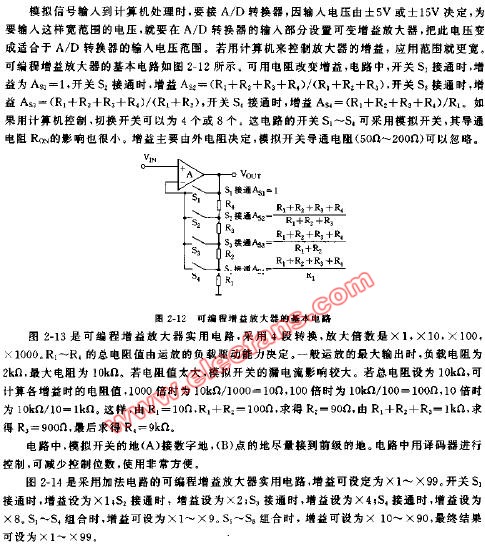

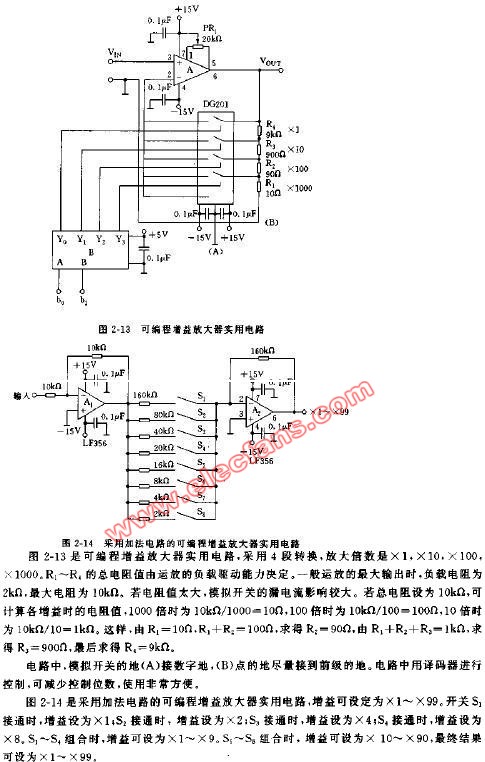

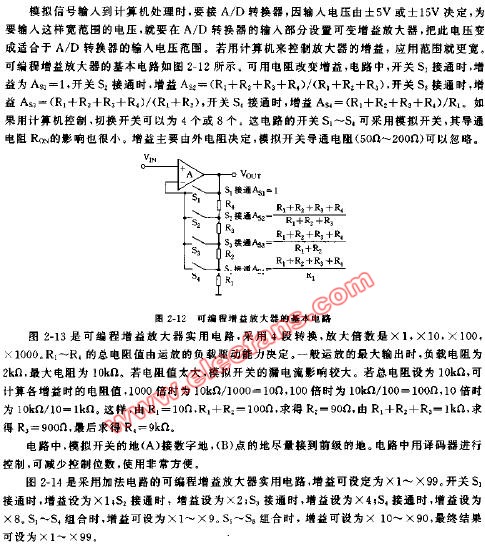

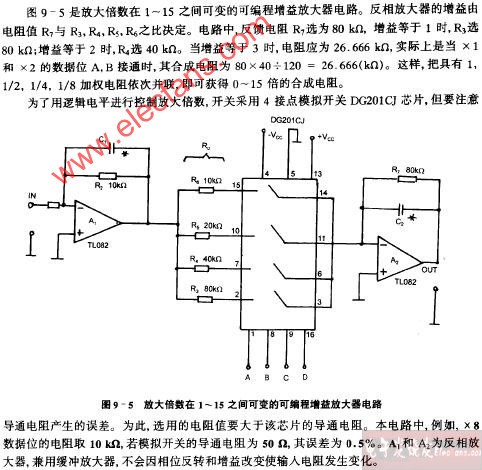

將CMOS D A轉換器和運算放大器組合設計可編程增益放大器:

2009-06-11 14:06:30 24

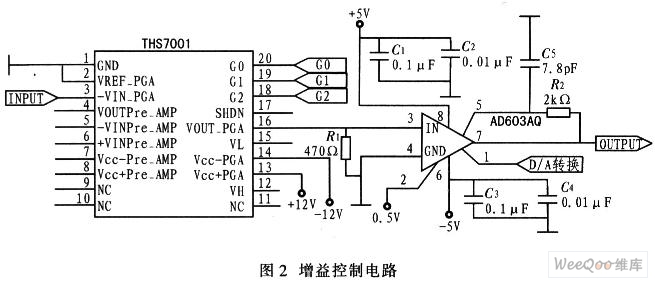

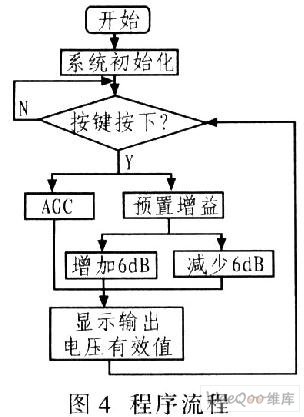

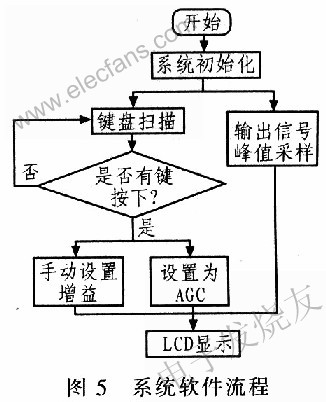

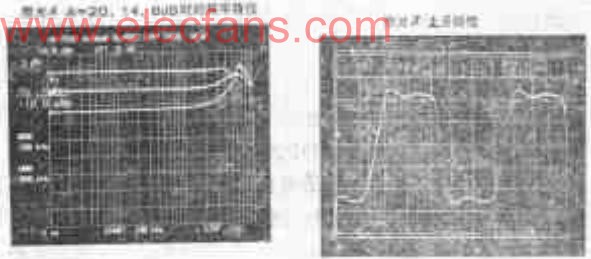

24 寬帶放大器:本設計利用可變增益寬帶放大器AD603 來提高增益和擴大AGC 控制范圍,通過軟件補償減小增益調節的步進間隔和提高準確度。輸入部分采用高速電壓反饋型運放OPA642作跟隨

2009-12-08 08:45:11 68

68 寬帶放大器用碲基摻鉺光纖結構參量的設計考慮

利用光波導理論及均勻展寬四能級模型,研究了寬帶放大器用階躍型折射率分布碲基摻鉺光纖的結構參量一

2010-02-22 17:34:57 20

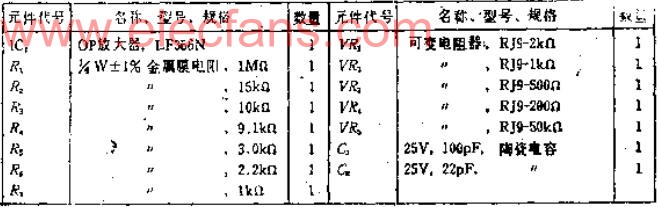

20 可編程放大器實驗18

一、演示內容1. 了解可編程放大電路的工作原理。 2. 演示輸出波形。

2010-05-23 15:59:03 22

22

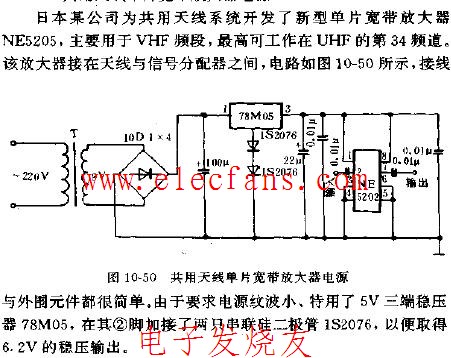

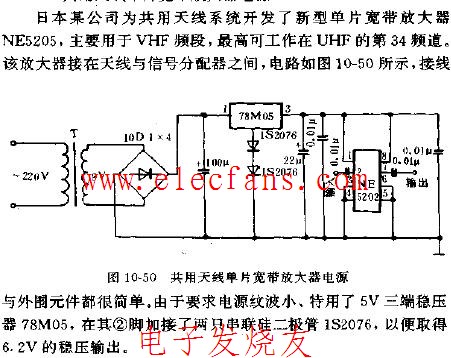

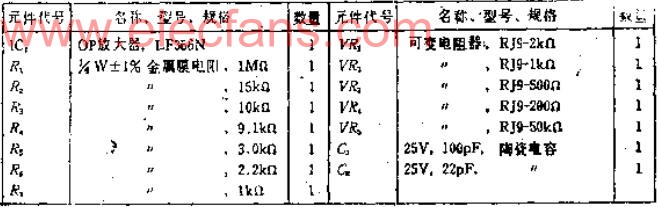

共用天線單片寬帶放大器電源電路

2008-08-23 23:54:43 656

656

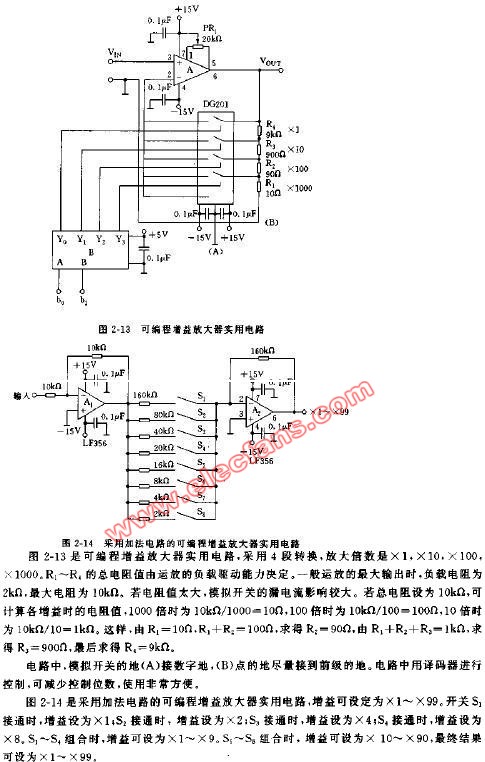

可編程增益放大器

2008-12-17 14:24:54 1103

1103

可編程增益放大器實用電路

2008-12-17 14:25:52 1396

1396

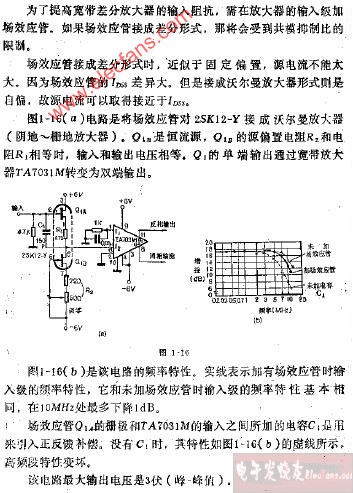

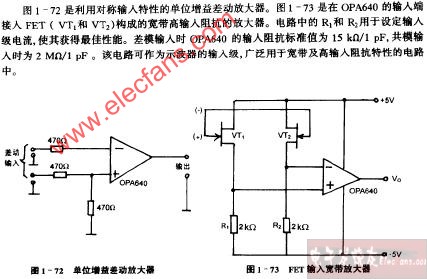

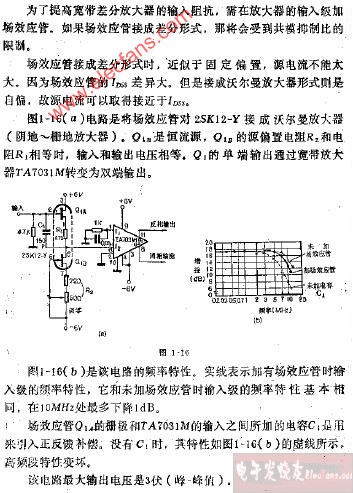

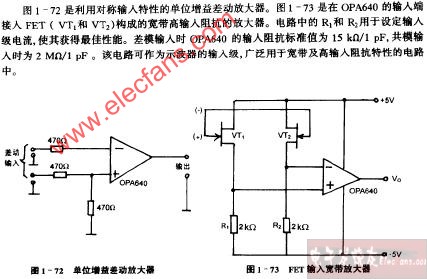

高輸入阻抗寬帶放大器

2009-03-20 10:39:35 548

548

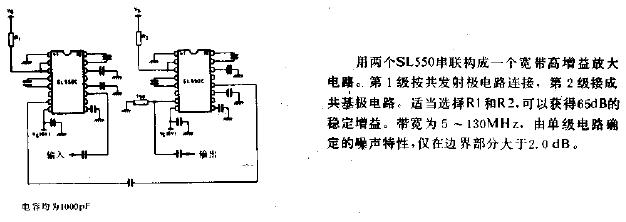

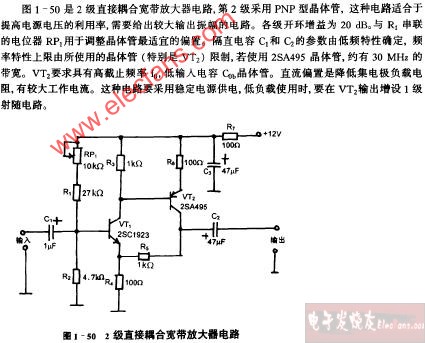

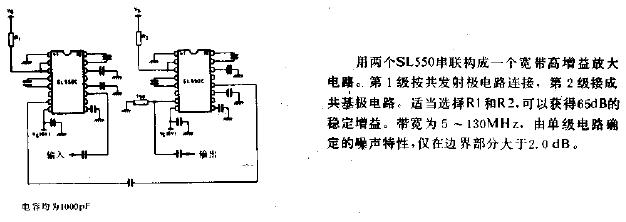

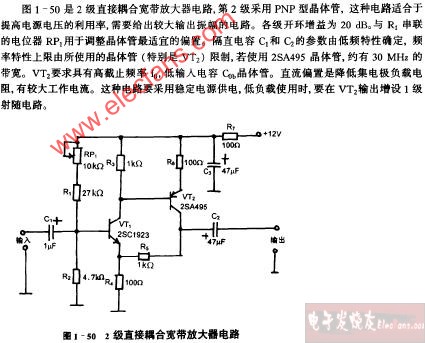

兩級寬帶放大器電路圖

2009-04-15 08:48:44 1500

1500

可編程增益放大器采用

2009-04-28 10:49:01 1020

1020

可編程增益放大器,采

2009-05-08 09:52:42 1246

1246

2級直接耦合寬帶放大器電路圖

2009-07-13 17:20:11 714

714

FET輸入寬帶放大器電路圖

2009-07-13 17:22:18 1197

1197

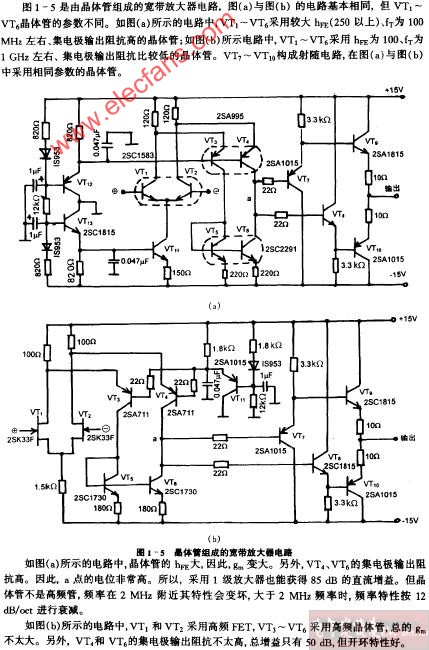

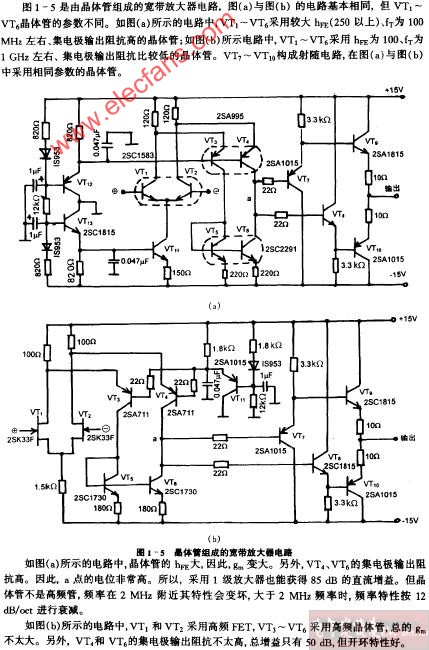

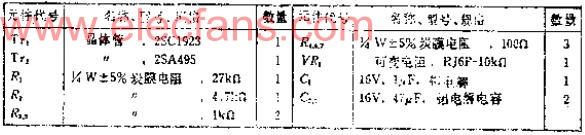

晶體管組成的寬帶放大器電路圖

2009-07-13 17:53:35 567

567

一種靈活的可編程三相開關功率放大器

摘要:分析了三相四橋臂開關功率放大器的原理及其在繼電保護測試中的應用

2009-07-15 08:43:11 510

510

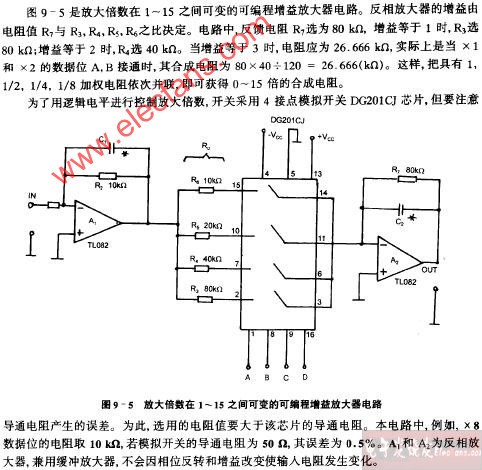

放大倍數在1~15之間可變的可編程增益放大器電路圖

2009-07-16 17:12:25 1995

1995

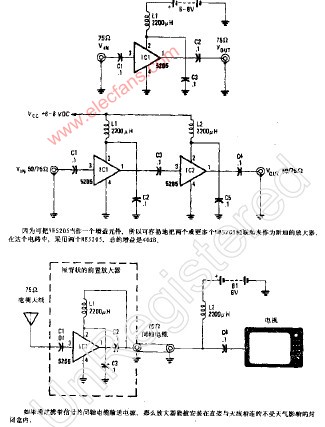

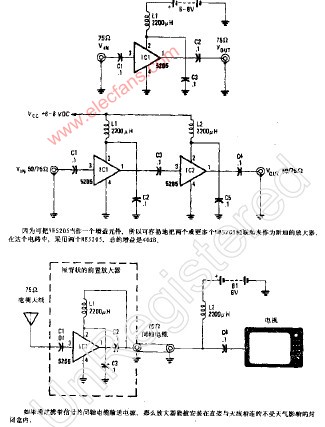

小型寬帶放大器

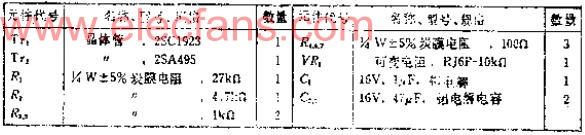

除去耦合及去耦合電容,

2009-10-06 14:45:01 872

872

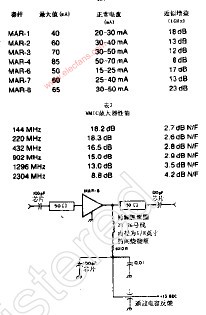

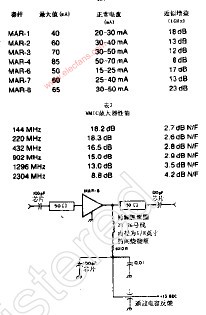

144-2304MHz的UHF寬帶放大器

該電路基于一個MAE-6前置

2009-10-06 15:39:38 1167

1167

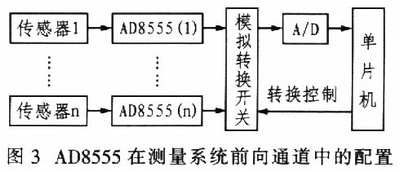

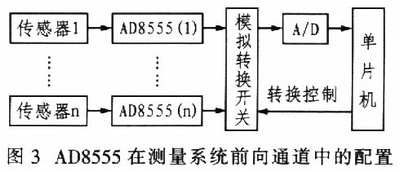

AD8555型數字可編程放大器的原理及應用

AD8555是ADI推出的一款增益及輸出失調,可數字編程的零漂移橋式傳感放大器,工作電壓為2.7 V~5.5 V,工作溫度范圍為-40℃~125℃

2009-10-30 12:37:50 1187

1187

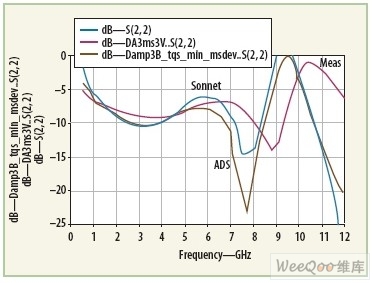

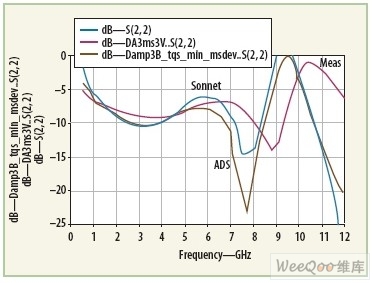

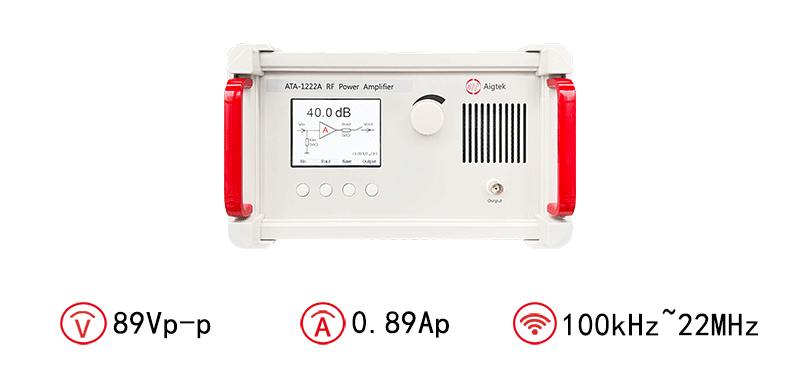

寬帶放大器的設計方法以及仿真和實測

分布式放大器能提供很寬的頻率范圍和較高的增益。有一段時間,其設計通常采用傳輸線作為

2010-04-28 09:32:20 2264

2264

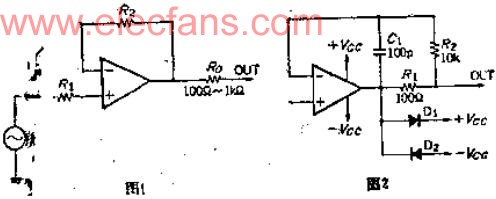

可以設定1、10、100、1000倍數放大倍數的可編程放大器

電路的功能

該電路是一種由CPU控制的

2010-04-28 16:01:16 11054

11054

可按1倍、2倍、5倍的順序切換8次(3位)的可編程放大器

電路的功能

2010-04-28 16:24:21 4281

4281

用于記錄儀接口的可編程放大器

電路的功能

記錄儀內含有增益放大器時,若選定最大輸入

2010-04-28 17:15:55 597

597

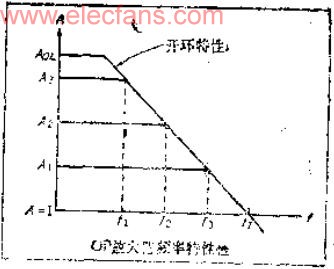

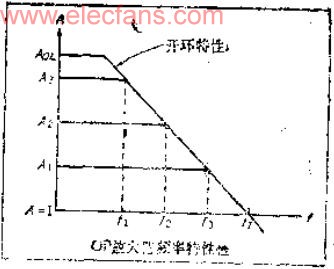

設計自由度很大的二級直耦寬帶放大器

電路的功能

雖然很多單片IC也被稱為寬帶放大器,

2010-04-29 18:24:08 1063

1063

使用UPC1663的寬帶放大器

電路的功能

UPC1663的電路與作為視頻放大而廣泛應用的UA733相同,

2010-04-30 14:36:40 2449

2449

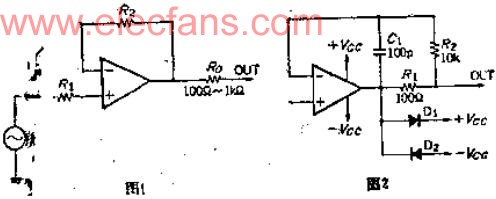

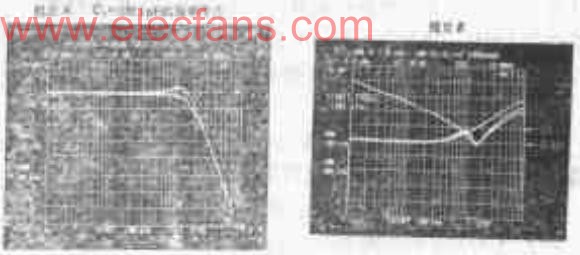

帶寬為50MHZ的寬帶放大器

電路的功能

寬帶OP放大器是一種調整脈沖電路或視頻電路、高頻

2010-04-30 14:57:57 2607

2607

本設計實現了一個5 V單電源供電的寬帶放大器基本功能,整個系統結構簡單,而且綜合應用了電容去耦、濾波等抗干擾措施以減少放大器噪聲并抑制高頻自激。經驗證,本方案完成了設

2011-04-23 10:43:02 4862

4862

設計了一種 寬帶放大器 , 采用高速運算放大器OPA820 和低失真電流反饋運算放大器T HS3091 構成兩級放大電路,在6 H z~ 20 MHz 的通頻帶中實現放大增益為43 dB, 具有帶內波動小, 輸出噪聲低的

2011-08-19 11:17:05 243

243 2013 年全國大學生電子設計競賽試題_射頻寬帶放大器(D 題) 【本科組】!

2015-12-08 11:00:58 11

11 利用寬帶放大器解決電信多頻段工作需求,ADI工程師介紹的在線研討會

2016-01-08 16:34:56 1

1 可編程增益放大器

2017-03-05 15:00:06 10

10 射頻寬帶放大器

2017-03-05 15:11:18 10

10 可編程增益放大器(PGA:),是一種通用性很強的放大器,其放大倍數可以根據需要用程序進行控制。

2017-09-18 09:09:18 7

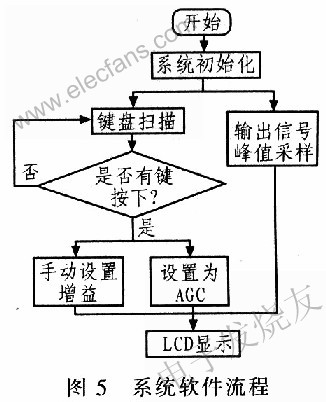

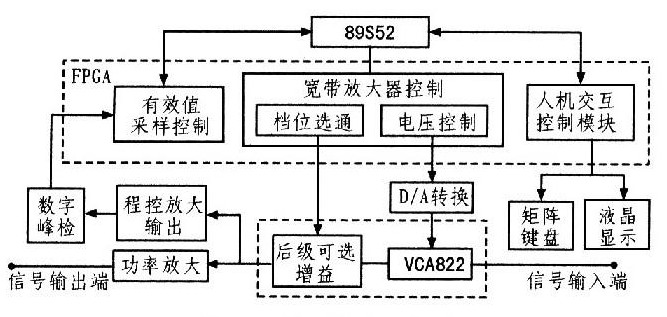

7 具有較高的頻帶寬度和靈活的電壓增益,因此,這里提出一種以壓控增益放大器VCA822為核心的可編程寬帶放大器,可實現通頻帶為100 Hz~15 MHz,放大器增益為10~58 dB,6 dB步進可調。該設計可通過矩陣式鍵盤設置放大器增益,液晶顯示器顯示輸出電壓,人機界面友好。

2018-12-18 07:54:00 5529

5529

寬帶微波放大器主要運用于電子監控與對抗、雷達、光纖和儀表系統等寬帶通信系統,它們都需要多倍頻程的放大器。設計一個相對帶寬大于50%的放大器是一項重大挑戰[1]。傳統的寬帶放大器技術包括電抗/電阻性網絡結構、并聯電阻性反饋結構、平衡結構、分布式結構。

2020-01-22 16:59:00 4595

4595

AN-320A:CMOS乘法DAC和運算放大器相結合構成可編程增益放大器(上)

2021-04-27 10:11:48 10

10 AN-320B:CMOS乘法DAC和運算放大器相結合構成可編程增益放大器(下)

2021-05-21 08:22:39 12

12 AN-137:一種數字可編程增益和衰減放大器的設計

2021-05-25 14:56:30 13

13 電子發燒友網站提供《低功耗全差動可編程增益放大器參考設計.zip》資料免費下載

2022-09-07 09:29:46 1

1 功率放大,以滿足需要發送功率的要求,然后經過天線將其輻射到空間,保證在一定區域內的接收機可以接收到滿意的信號電平的同時不干擾相鄰信道的通信。 ????寬帶放大器是指上限工作頻率與下限工作頻率之比甚大于1的放大電路,通常我

2021-10-10 18:00:00 1646

1646

寬帶放大器是一種電子設備,用于增加信號的幅度和功率,以便在電子通信和無線傳輸中提供更好的性能和覆蓋范圍。寬帶放大器可以根據其工作方式和應用領域的不同,分為幾種類型。

2023-07-20 09:45:15 497

497 寬帶放大器芯片是一種關鍵的電子器件,用于增強信號的幅度和功率。在現代通信和電子領域中,寬帶放大器芯片的應用十分廣泛。本文將對寬帶放大器芯片的結構進行分析。

2023-07-27 10:00:47 424

424 ATA-1222A寬帶放大器選型手冊ATA-1222A是一款寬帶放大器。其飽和輸出功率40W,增益P1dB壓縮點輸出功率20W。增益數控可調,一鍵保存設置,提供了方便簡潔的操作選擇,可與主流的信號發生器配套使用,實現信號的放大。寬范圍供電電源,可兼容全球不同地區的電源標準要求。

2023-08-09 15:27:35 0

0 ATA-1372A寬帶放大器ATA-1372A是一款可放大交直流信號的單通道寬帶放大器。其最大輸出電壓70Vp-p(±35Vp),最大輸出電流2Ap(>50Hz)。電壓增益數控可調,一鍵保存設置,提供了方便簡潔的操作選擇,可與主流的信號發生器配套使用,實現信號的放大。

2023-08-09 15:22:50 0

0 近日某院校送修羅德與施瓦茨寬帶放大器 BBA150,客戶反饋寬帶放大器 寬帶放大器 出現報錯,對儀器進行初步檢測,確定與客戶描述故障一致。本期將為大家分享本維修案例。 下面就是

2023-10-07 17:49:39 239

239

寬帶放大器是一種用于放大高頻信號的電子設備,它在二極管測試中有多種應用。下面安泰電子將介紹寬帶放大器在二極管測試中的幾種常見應用。 寬帶放大器可以用于二極管參數測試。二極管是一種常見的半導體器件

2024-01-17 17:11:05 201

201

射頻寬帶放大器在多個領域都有廣泛的應用,包括但不限于通信系統(如手機、衛星通信、無線電廣播等)、醫療診斷(如醫學成像和其他醫療設備)和軍事應用(如軍事雷達和通信系統)。

2024-03-21 15:59:51 180

180

正在加载...

電子發燒友App

電子發燒友App

評論