目前,在多數保密通信沒備中,主要采用通用CPU和專用硬件電路控制密碼專用芯片來實現兩種方式的密碼運算。采用前者控制密碼專用芯片時,需要選用一種具有靈活性高、維護容易、升級方便等特點的性能優良的通用微處理器GPP(General Purpose Processor),但由于通用微處理器指令的局限性,使密碼專用芯片達不到其最佳性能,嚴重影晌了保密通信的速度;采用專用硬件電路直接控制密碼專用芯片,雖然可使密碼專用芯片的性能達到最高,但由于其功能只依賴于密碼專用芯片及其外圍器件,使得靈活性差、開發周期比較長。

由此可見,無論采用上面哪種方式,由于密碼專用芯片的運算處理與控制分離,限制了密碼數據處理性能,制約了系統整體速度。針對上述問題,通過分析多種密碼算法,本文提出一種基于處理器設計思想的顯式并行指令計算結構(EPIC的可編程密碼處理器架構,實現了速度與靈活性的折衷。

1 密碼算法分析

1.1 典型的密碼算法及其應用

現針對七種分組密碼算法和兩種雜湊函數即DES、IDEA、Rijndael、RC6、Serpent、Twofish、Mars、MD5和SHA進行分析。

分組密碼算法是一個將比特明文映射成n比特密文的雙射函數,n為其分組長度,它的加密與解密過程具有相同的密鑰,因此又稱為對稱密碼算法。而雜湊函數是一種將任意長度的消息壓縮為某一固定長度的消息摘要的函數,它主要用十數字簽名、消息的完整性檢測和消息的起源認證檢測等方面。

DES算法(數據加密標準)是第一代公開的完全說明實現細節的被世界公認的分組密碼算法。其最初設計者是IBM公司,并取得了它的專利權。在隨后的二十多年中,DES算法作為一種典型的分組密碼算法,被廣泛地應用于保護商業數據的安全(如銀行系統等)。

IDEA算法(國際數據加密算法)公布于1992年,足IPES標準,因廣泛應用于email加密認證軟件(PGP)中而聞名。

Riindael是1998年公布的,并于2000年在由NIST(美國國家標準技術研究所)主持的AES評選中獲勝,此后Rijndael算法也稱為AES算法,成為逐漸代替DES的新的加密標準。

RC6、Serpent、Twofish和Mars算法是與Rijndael算法一起參評的AES候選算法,它們都不同程度地體現了分組密碼算法的設計原則,對應用密碼學的發展產生了相當大的影響。

MD5消息摘要函數是由RSA算法的設計者之一Rivest提出的一種單向散列函數,它不基于任何假設和密碼體制,采用了直接構造的方法,處理速度非常快。

SHA是1993年公布的聯邦信息處理標準(FIPS-180)的安全散列標準,由NIST提出并于1995年推出了其修訂版,通稱為SHA-1。

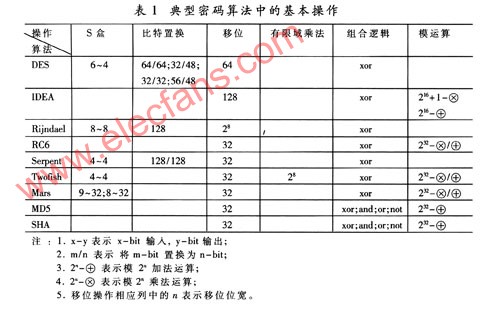

1.2 密碼算法中的基本操作

在分析上述算法的基礎上,提取出各個算法的核心操作類型,并總結出它們的基本操作分別為以下六類:S盒操作、比特置換操作、算術運算、邏輯運算、移位操作和有限域乘法運算。其中算術運算包括模加/減和模乘運算,邏輯運算則由‘與 i、‘或 i、‘非 i和‘異或 i組成,表1詳細列出了它們在各種算法中的具體應用,如DES算法中主要使用了S盒操作、比特置換、異或和移位操作。

2 可編程密碼處理器體系結構設計

在典型的可編程密碼處理器結構(AFPC)中,EPIC結構開發的是標量操作之間的隨機并發性,并且增加了功能部件的個數。不相關的指令由編譯顯式地編入到一個超長的機器指令字中,并發射到流水線,在各個功能部件中并發執行,指令級并行度為4~8。這種結構的硬件控制相對簡單,在計算密集型應用時內在并行性很明顯。且不需要很多轉移預測。在這種結構上運行指令能夠達到較高的實際指令級并行度。正是由于以上特點,EPIC結構在很大程度上符合了密碼算法的需求,即計算密集且順序執行。

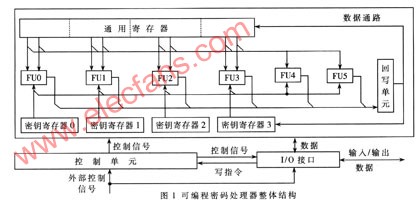

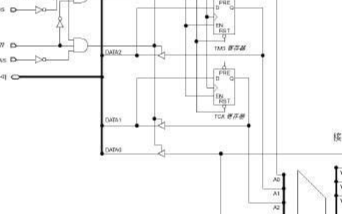

可編程密碼處理器體系結構的硬什結構如圖1所示,整個處理器包括三部分:數據通路、控制單元和輸入/輸出接口電路。

?

數據通路是處理器的關鍵部件之一,包含FUO~FU5共6個可并行執行的功能單元、32個32bit通用寄存器、4×32個32bit密鑰寄存器和回寫單元。

功能單元是處理器執行指令運算的核心,由若干個密碼運算模塊組成。其中,FUO~FU3內部運算模塊的組成與結構完全相同,輸入為3個32bit運算數據,其中2個來自通用寄存器堆、1個來自密鑰寄存器堆,輸出的運算結果亦為32bit。FUO~FU3內部分別設置了7個運算模塊,分別為S盒運算模塊、模加,減運算模塊、模乘運算模塊、32bit移位運算模塊、有限域乘法運算模塊、二輸入邏輯運算模塊、三輸入邏輯運算模塊。FU4內部設置了1個128bit,置換運算模塊,輸入為12個32bit運算數據,其中8個來自通用寄存器堆,4個來自密鑰寄存器堆。FU5內部設置了1個128bit移位運算模塊,輸入也為12個32bit運算數據,其中8個來自通用寄存器堆,4個來自密鑰寄存器堆。

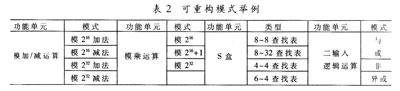

上述這些運算模塊功能不是單一的,而是可重構的。表2中給出了4個可重構運算模塊所支持的模式。

?

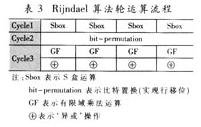

除了上述運算模式可重構外,各運算模塊根據具體情況還支持運算前增加‘異或 i操作、運算后增加‘異或 i操作或者運算前后都增加‘異或 i操作。由于‘異或 i操作延時很小,它的加入并不影響運算的關鍵路徑,這就使得密碼運算時減少了單一‘異或 i操作的時鐘,從而減少了整個運算的時鐘數,并且不影響整體性能。表3中給出了Rijndael算法輪運算流程,采用有限域乘法運算后加入‘異或 i操作,時鐘周期數由4減為3,10輪運算將減少10個時鐘周期。

?

控制單元完成指令存取、指令譯碼、指令存儲器地址生成等工作,協調處理器內部指令與外部用戶命令正確執行。

輸入/輸出接口電路包括16個32bit輸入寄存器、16個32bit輸出寄存器、4個數據 長度計數器、1個32bit命令寄存器等,完成指令、運算數據從32bit數據總線裝載到指令存 儲器和輸人寄存器以及運算結果從內部通用寄存器寫入輸出寄存器等操作。

3 指令系統設計

指令系統是算法要素和密碼處理器體系結構特性的集中體現,指令系統的設計必須支 持硬件的并行執行,即開發指令級并行性(ILP),指令級并行性的開發程度對發揮密碼微處理器的硬件特性,提高程序運行性能至為關鍵。ILP技術實際上是指一套完整的處理器設計和編譯技術,這些技術通過并行地執行獨立的機器操作(如存儲器讀寫、邏輯運算、算術運算等)來加速程序的執行。ILP的大小可以采用每周期平均執行的指令數(IPC)朱衡量,或者采用整個程序的每條指令平均執行的周期數CPI(CPT=l/IPC)來衡量。在可編程密碼處理器體系結構中采用了顯式并行指令計算結構,指令級并行數達到5。

3.1 指令分類

可編程密碼處理器體系結構中的指令分為以下幾類:

(1)靜態配置指令。它是在密鑰生成及加/解密過程中保持不變或者改變次數很少的控制信息配置指令,算法確定后,其S盒查找表信息、有限域乘數矩陣和不可約多項式、若干個置換的控制信息等就確定了,它們不會因為操作模式不同而改變。在加/解密過程中采用將配置指令分離出來的方法,可以大大減少執行密碼運算時指令的冗余編碼,從而縮短了指令字的長度,增加了運算指令字中包含有效操作的個數,有效地提高了加/解密速度并減少了密碼程序的代碼量。

(2)短指令。它執行除置換與128bit移位運算外的各種密碼運算和內部寄存器問的數據傳輸操作。

(3)長指令。它執行置換與128bit移位運算。

(4)超長指令。它執行立即數操作和多分支判斷操作。

(5)控制指令。它執行程序跳轉、子程序調用及返回、單分支判斷等控制操作。

3.2 指令形態

在硬件上,多個功能單元的設置為多條指令的并行執行提供了支持,而哪些指令可以并行執行,哪些指令不能并行執行以及如何將多條指令組裝成一條指令的原則,即稱為指令的拼裝規則。在此設計中有以下幾種指令形態:

(1) 靜態配置指令。

(2) 超長指令。

(3) 短指令Ⅱ短指令Ⅱ短指令Ⅱ短指令ll控制指令。

(4) 長指令Ⅱ控制指令。

其中短指令長度為37bit,控制指令長度為32bit,長指令長度為148bit。無論上述哪種形態,最終的指令字長度都為192bit(包括指令拼裝標識),如四個短指令可以與控制指令拼裝成一條指令,長指令也可以與控制指令拼裝成一條指令,但靜態配置指令與超長指令不能與其他指令拼裝,自身組成一個192bit的指令字。

4 性能分析

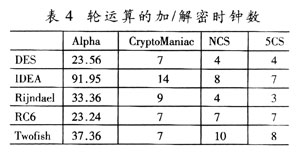

由于可編程密碼處理器體系結構支持5條指令綁定并行執行,因此其數據路徑定義為5CS(5Combining-Strands),假設不采用綁定的數據路徑定義為NCS(No-Combining-Strands),將這兩種情況與Alpha處理器、Cryp-toManiac密碼處理器[9]路程進行比較,四種數據路徑下加/解密所需時鐘數如表4所示。分析比較表明可編程密碼處理器執行時鐘大量減少,尤其與通用處理器Al-pha相比,加/解時鐘數DES算法減少83%,IDEA算法減少92%,Rijndael算法減少9l%,RC6算法減少69%,Twofish算法減少78%。

?

為了驗證可編程密碼處理器體系結構實現數據通路和控制通路的正確性,使用Altera StraTIxlIEP2S180F1508C4器件作為FPCA目標芯片,使用AlteraQuartusII 5.0工具進行綜合,在綜合前和綜合后使用Mentor公司的ModelSim 5.8c分別進行功能仿真和時序仿真,結果均正確。其具體資源占用情況如表5所示。

?

密碼處理的靈活性和高效性一直是密碼算法使用中的制約因素,采用通用微處理器雖然能獲得較好的靈活性,但卻使一些算法的性能達不到要求;采用專用算法芯片,在獲得很高性能的同時喪失了靈活性。本文針對這一矛盾以EPIC結構微處理器構架為出發點,系統地研究了通用的并行分組密碼處理器模型、各種密碼運算單元、指令集等關鍵技術,并最終得以實現,達到了實現性能與靈活性之間的良好折衷。

電子發燒友App

電子發燒友App

評論