針對(duì)嵌入式應(yīng)用系統(tǒng)片外Flash存儲(chǔ)器IAP無現(xiàn)成方案的問題,介紹一種基于代碼重入思想的片外存儲(chǔ)器IAP解決方案。

2011-11-30 11:58:39 1810

1810

Altera公司近日發(fā)布其面向FPGA的OpenCL (開放計(jì)算語言)早期使用計(jì)劃(EAP),支持客戶提前了解Altera面向FPGA的OpenCL解決方案。采用這一開放標(biāo)準(zhǔn),設(shè)計(jì)團(tuán)隊(duì)可以在高級(jí)C語言框架中面向

2012-09-04 08:47:41 750

750 Altera公司今天宣布,眾志和達(dá)公司采用Altera FPGA解決方案構(gòu)建8Gbps光纖通道協(xié)議存儲(chǔ),正式進(jìn)軍8GFC存儲(chǔ)市場(chǎng)。

2012-12-12 14:26:01 1098

1098 Altera公司今天在2013年安博會(huì)上宣布動(dòng)視元采用Altera基于FPGA的最新視頻分析成功推出首個(gè)基于FPGA的智能交通視頻分析解決方案,較之傳統(tǒng)工控機(jī)或DSP的解決方案,基于FPGA的視頻分析可極大提高偵測(cè)率和節(jié)省成本...

2013-10-29 18:13:44 1140

1140 異步SRAM存儲(chǔ)器接口電路設(shè)計(jì)(Altera FPGA開發(fā)板)如圖所示:FLASH存儲(chǔ)器接口電路圖(Altera FPGA開發(fā)板)高速SDRAM存儲(chǔ)器接口電路設(shè)計(jì)(Altera FPGA開發(fā)板)如下

2012-08-16 18:49:43

描述PMP9357 參考設(shè)計(jì)是 Altera Arria V 系列 FPGA 的完整電源解決方案。此設(shè)計(jì)使用多個(gè) TPS54620 同步降壓轉(zhuǎn)換器、多個(gè) LDO 和一個(gè) DDR 終端穩(wěn)壓器提供為

2018-09-12 09:08:24

描述 PMP9353 參考設(shè)計(jì)是 Altera Cyclone V SoC 器件的完整電源解決方案。此設(shè)計(jì)使用多個(gè) LMZ3 系列模塊、兩個(gè) LDO 和一個(gè) DDR 終端穩(wěn)壓器提供為 SoC 芯片

2022-09-26 07:58:34

描述PMP9353 參考設(shè)計(jì)是 Altera Cyclone V SoC 器件的完整電源解決方案。此設(shè)計(jì)使用多個(gè) LMZ3 系列模塊、兩個(gè) LDO 和一個(gè) DDR 終端穩(wěn)壓器提供為 SoC 芯片供電

2018-09-06 09:07:37

處理器、存儲(chǔ)器、I/O口、LVDS、CDR等系統(tǒng)設(shè)計(jì)需要的功能模塊集成到一個(gè)可編程器件上,構(gòu)成一個(gè)可編程的片上系統(tǒng)。1.1 SOPC及其技術(shù)現(xiàn)今,可將SOPC視為是基于FPGA解決方案的SOC

2019-02-21 04:38:54

描述PMP9353 參考設(shè)計(jì)是 Altera Cyclone V SoC 器件的完整電源解決方案。此設(shè)計(jì)使用多個(gè) LMZ3 系列模塊、兩個(gè) LDO 和一個(gè) DDR 終端穩(wěn)壓器提供為 SoC 芯片供電

2015-05-11 16:45:44

設(shè)計(jì)解決方案43-Altera低壓FPGA的高性能開關(guān)模式電源解決方案

2019-08-09 07:04:51

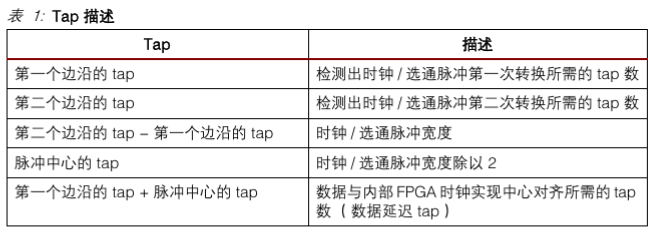

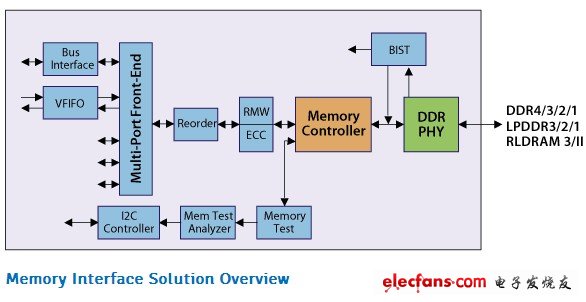

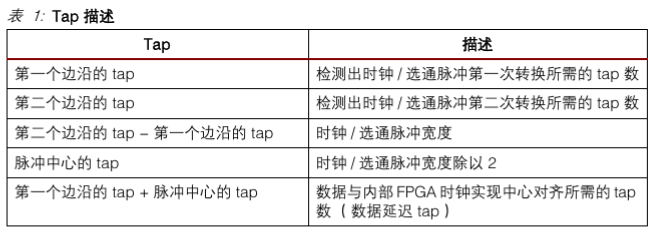

以下主題概述了Altera的外部內(nèi)存接口解決方案。

Altera提供最快、最高效、延遲最低的內(nèi)存接口IP核。Altera的外部存儲(chǔ)器接口IP設(shè)計(jì)用于方便地與當(dāng)今更高速的存儲(chǔ)器設(shè)備接口。

Altera

2023-09-26 07:38:12

28-Gbps收發(fā)器FPGA的公司。開發(fā)高性能系統(tǒng)的客戶,包括世界上頂級(jí)通信、廣播、軍事、測(cè)試和醫(yī)療公司,都在下一代系統(tǒng)中選擇了Altera高端FPGA,這是因?yàn)槠骷哂械男阅軆?yōu)勢(shì)和公司積極的生產(chǎn)計(jì)劃

2012-05-14 12:38:53

Altera_Stratix_V_FPGA提供RLDRAM_3存儲(chǔ)器支持

2012-08-13 22:17:28

的核。最新技術(shù)為20nm工藝。5、Intel的arria 10 fpga 系列也很出名,大家可以關(guān)注關(guān)注。支持DDR4存儲(chǔ)器接口的FPGA。 Altera的Arria 10 FPGA和SoC是目前業(yè)界

2018-01-29 11:05:29

多家客戶已在大量應(yīng)用中采用Cyclone III FPGA進(jìn)行設(shè)計(jì),應(yīng)用領(lǐng)域涵蓋在消費(fèi)類、汽車、軍事、工業(yè)和無線通信等。Cyclone III提供豐富的邏輯、存儲(chǔ)器和DSP功能,它含有5K至120K邏輯

2013-12-25 19:37:36

,其中也包括和第三方EDA工具的接口。QuartusII設(shè)計(jì)軟件根據(jù)設(shè)計(jì)者需要提供了一個(gè)完整的多平臺(tái)開發(fā)環(huán)境,它包含整個(gè)FPGA和CPLD設(shè)計(jì)階段的解決方案。圖1說明了QuartusII軟件的開發(fā)流程。在

2018-12-18 09:51:38

Flash存儲(chǔ)器來存儲(chǔ)配置碼流,并利用JTAG接口完成配置碼流下載的FPGA多配置解決方案。與System ACE方案相比,該方案不僅能快速完成多個(gè)配置碼流的下載,還具有更高的配置速度和更低的實(shí)現(xiàn)

2019-06-10 05:00:08

存儲(chǔ)器接口生成器(MIG)解決方案---Virtex-4 存儲(chǔ)器接口和Virtex-II Pro存儲(chǔ)器解決方案 Virtex-4? FPGAs solve

2009-10-24 12:02:14

描述該參考設(shè)計(jì)采用多種 TPS54325 和其他 TI 電源器件,是適用于 Xilinx Zynq FPGA 的全套電源解決方案。輸入電壓達(dá)到 12V 后,該參考解決方案可提供 Zynq FPGA

2015-04-14 09:46:41

本帖最后由 eehome 于 2013-1-5 09:53 編輯

用于Xilinx和Altera_FPGA的電源管理解決方案

2012-08-13 22:31:30

功能,如多隊(duì)列和可選的存儲(chǔ)器架構(gòu),可以幫助開發(fā)人員設(shè)計(jì)更快、更有效率,從而使其適應(yīng)廣泛的應(yīng)用。它已經(jīng)是一個(gè)成熟的解決方案,可以加速推向市場(chǎng)的時(shí)間,同時(shí)減少相關(guān)設(shè)計(jì)工作。該器件還可提供很寬的擴(kuò)展選擇,可以

2011-07-15 09:18:00

庫的慢-慢工藝點(diǎn)對(duì)塊進(jìn)行合成,以200 MHz的目標(biāo)速度確認(rèn)時(shí)序特性。

接口存儲(chǔ)器端口上的信號(hào)符合RAM編譯器為TSMC CL013G工藝技術(shù)生產(chǎn)的單端口同步存儲(chǔ)器組件所要求的時(shí)序要求

2023-08-21 06:55:33

? ALTMEMPHY宏功能來構(gòu)建所有的 DDR2或者 DDR SDRAM外部存儲(chǔ)器。通過將 Altera DDR2 或者 DDR SDRAM 存儲(chǔ)控制器、第三方控制器或者定制控制器用于特定的應(yīng)用需要,可以實(shí)現(xiàn)控制器功能

2017-11-14 10:12:11

指令。此外,萊迪思ECP3為帶有SERDES和高速接口,如DDR3存儲(chǔ)器控制器的應(yīng)用提供最低功耗的可編程解決方案。設(shè)計(jì)和驗(yàn)證流程 DDR3存儲(chǔ)器控制器IP核必須易于配置、生成并應(yīng)用到一個(gè)目標(biāo)設(shè)計(jì)中

2019-05-24 05:00:34

存儲(chǔ)器件開關(guān)穩(wěn)壓器和 LDO 的最優(yōu)組合可提供最佳的電源分配樹該設(shè)計(jì)已經(jīng)過測(cè)試,可用于為 Zynq FPGA 加電

2018-09-11 09:14:38

為什么推出Virtex-5LXT FPGA平臺(tái)和IP解決方案?如何打造一個(gè)適用于星形系統(tǒng)和網(wǎng)狀系統(tǒng)的串行背板結(jié)構(gòu)接口FPGA?

2021-04-29 06:18:31

服務(wù)器 a. 同類最佳的串行數(shù)字接口(SDI)解決方案; b. 通過用戶友好的部分重新配置功能,支持多個(gè)CODEC; c. 自然支持10位,實(shí)現(xiàn)最佳存儲(chǔ)器設(shè)計(jì); d. 更高的乘法器和存儲(chǔ)器邏輯比

2012-09-21 13:49:05

關(guān)于數(shù)Gpbs高速存儲(chǔ)器接口設(shè)計(jì)的分析,看完你就懂了

2021-05-19 06:38:12

大家好!xilinx軟錯(cuò)誤緩解控制器IPcore V4.1用于配置內(nèi)存以避免SEU。我想知道,有關(guān)塊存儲(chǔ)器,分布式存儲(chǔ)器和觸發(fā)器的一些解決方案是否有關(guān)于SEU的解決方案?非常感謝你!

2020-08-05 07:40:29

FPGA是基于RAM結(jié)構(gòu)的,當(dāng)然了,也有基于FLASH結(jié)構(gòu)的,但RAM結(jié)構(gòu)的是主流,也是我們討論的重點(diǎn)。而RAM是易失存儲(chǔ)器,在掉電后保存在上面的數(shù)據(jù)就丟失了,重新上電后需要再下載一次才可以。因此

2018-03-04 22:12:49

到接收器。接收器接口內(nèi)部利用時(shí)鐘來鎖存數(shù)據(jù),此舉可消除接口控制問題(例如在存儲(chǔ)器和FPGA間的信號(hào)傳遞時(shí)間),但也為設(shè)計(jì)師帶來了必須解決的新挑戰(zhàn)。 關(guān)鍵問題之一就是如何滿足各種讀取數(shù)據(jù)捕捉需求以實(shí)現(xiàn)高速

2019-04-29 07:00:06

摘要:文中詳細(xì)地分析了Altera公司Cyclone VFPGA器件的硬核存儲(chǔ)控制器底層架構(gòu)和外部接口,并在此基礎(chǔ)上對(duì)Controller和PHY進(jìn)行了功能仿真。仿真結(jié)果表明硬核存儲(chǔ)控制器和PHY

2019-06-13 05:00:06

DSP的地址線A00接在SRAM的A0上。 5 小結(jié) 本文主要介紹了如何根據(jù)實(shí)際需要來自動(dòng)地調(diào)節(jié)存儲(chǔ)器接口寬度。由于C32可以非常靈活地調(diào)整其存儲(chǔ)器接口寬度,使得存儲(chǔ)器接口電路的設(shè)計(jì)更加的靈活,因此非常適用于電機(jī)或電力系統(tǒng)等實(shí)時(shí)系統(tǒng)的數(shù)據(jù)采集與處理。

2019-06-14 05:00:08

強(qiáng)大的硬件支持。SOPC是Ahera公司提出的一種靈活、高效的片上系統(tǒng)(SOC)解決方案,它將處理器、存儲(chǔ)器、I/O口等系統(tǒng)設(shè)計(jì)所需要的功能模塊集成到一個(gè)可編程器件上,從而構(gòu)成一個(gè)可編程的片上系統(tǒng)

2018-12-07 10:27:46

基于Xilinx FPGA的DDR2 SDRAM存儲(chǔ)器接口

2012-08-20 18:55:15

電路設(shè)計(jì)(如何掛載到NIOSII的總線上),最終解決了不同數(shù)據(jù)位寬的多種存儲(chǔ)器的同平臺(tái)測(cè)試解決方案,并詳細(xì)地設(shè)計(jì)了各結(jié)口的硬件實(shí)現(xiàn)方法。

2019-07-26 06:53:39

如何利用Xilinx FPGA和存儲(chǔ)器接口生成器簡化存儲(chǔ)器接口?

2021-05-06 07:23:59

本文介紹了一種0.13微米CMOS T藝下FPGA中嵌入式存儲(chǔ)器模塊的設(shè)計(jì)與實(shí)現(xiàn)。

2021-04-09 06:02:09

的工作時(shí)鐘頻率。然而,設(shè)計(jì)至DDR3的接口也變得更具挑戰(zhàn)性。在FPGA中實(shí)現(xiàn)高速、高效率的DDR3控制器是一項(xiàng)艱巨的任務(wù)。直到最近,只有少數(shù)高端(昂貴)的FPGA有支持與高速的DDR3存儲(chǔ)器可靠接口的塊

2019-08-09 07:42:01

如何用低成本FPGA解決高速存儲(chǔ)器接口挑戰(zhàn)?

2021-04-29 06:59:22

本文提出了一個(gè)網(wǎng)絡(luò)存儲(chǔ)器的基本解決方案,實(shí)現(xiàn)了網(wǎng)絡(luò)存儲(chǔ)器的基本功能。

2021-04-26 06:50:19

客戶提供Altera FPGA技術(shù)支持,包括支持客戶方案選型,提供現(xiàn)場(chǎng)技術(shù)支持。4.掌握Altera最新產(chǎn)品技術(shù),開拓市場(chǎng)新興應(yīng)用電子技術(shù)方面,配合銷售主動(dòng)推廣技術(shù)解決方案任職資格: 1.具備3年

2017-06-05 10:45:35

的,在上電之際就可使用,可以立即使用AED功能。 由于非易失性FPGA是單芯片器件,可以省去與SRAM FPGA配置單元相關(guān)的附加電路。除了一個(gè)引導(dǎo)ROM和一個(gè)用于存儲(chǔ)未加密配置代碼的附加系統(tǒng)存儲(chǔ)器

2012-12-07 16:26:14

如何滿足各種讀取數(shù)據(jù)捕捉需求以實(shí)現(xiàn)高速接口?怎么縮短高端存儲(chǔ)器接口設(shè)計(jì)?

2021-04-29 07:00:08

為什么要開發(fā)和測(cè)試存儲(chǔ)器件?怎樣去測(cè)試存儲(chǔ)器的基本功能?如何去擴(kuò)展存儲(chǔ)器的測(cè)試能力?

2021-04-15 06:44:19

:Arria 10 SoC 開發(fā)套件板針對(duì)內(nèi)核、系統(tǒng)和 I/O 的電源管理謹(jǐn)慎地選擇高端 FPGA (包括 Arria 10) 的電源管理解決方案應(yīng)謹(jǐn)慎地選擇。經(jīng)過審慎考慮的電源管理設(shè)計(jì)可縮減 PCB

2018-10-29 17:01:56

自行設(shè)計(jì)的基于FPGA芯片的解決方案DDS技術(shù)的實(shí)現(xiàn)依賴于高速、高性能的數(shù)字器件。可編程邏輯器件以其速度高、規(guī)模在、可編程,以及有強(qiáng)大EDA軟件支持等特性,十分適合實(shí)現(xiàn)DDS技術(shù)。Altera是著名

2011-07-13 14:13:56

FLASH+SRAM+EEPROM 實(shí)現(xiàn)有困難,或功耗,速度,成本三者難以協(xié)調(diào)的應(yīng)用。本文介紹的多功能雙接口存儲(chǔ)器方案,除了實(shí)現(xiàn)低功耗快速存儲(chǔ)的功能外,還包括RTC,硬件看門狗,AES 數(shù)據(jù)加/解密,接口擴(kuò)展等功能。2

2019-06-12 05:00:08

開發(fā)周期、長期供貨和最先進(jìn)技術(shù)。從便攜式電子產(chǎn)品到網(wǎng)絡(luò)設(shè)備,賽普拉斯的存儲(chǔ)器系列產(chǎn)品總能提供相應(yīng)的存儲(chǔ)器方案:低功耗、異步、同步與非易失性 SRAM,以及多端口 SRAM、FIFO 等。賽普拉斯提供完整

2020-09-01 19:40:50

`描述該 Artix 7 電源管理參考設(shè)計(jì)板使用電源模塊、線性穩(wěn)壓器和兼容 PMBus 的系統(tǒng)控制器來提供 FPGA(包括 DDR 存儲(chǔ)器終端)所需的所有內(nèi)核和輔助電壓。數(shù)字電源圖形用戶界面用于監(jiān)控

2015-05-07 17:36:13

構(gòu)件、選擇 DC/DC 穩(wěn)壓器器件型號(hào)并驗(yàn)證定制解決方案。 LTpowerPlanner 用來產(chǎn)生滿足 Arria 10 開發(fā)套件中 FPGA 要求及系統(tǒng)要求的電源樹 (圖 3),是用途更廣

2018-10-15 10:30:31

對(duì)七路溫度的實(shí)時(shí)監(jiān)控。二、溫度存儲(chǔ)模塊該模塊的主要構(gòu)成部分是一個(gè) 14*8位存儲(chǔ)器,用于存儲(chǔ)七路溫度數(shù)值,每一路數(shù)值需要2個(gè)8位寄存器存放。存儲(chǔ)完畢后,等待DSP讀取。 (3)DSP接口模塊該模塊主要用于

2020-08-19 09:29:48

DSP的地址線A00接在SRAM的A0上。 5 小結(jié) 本文主要介紹了如何根據(jù)實(shí)際需要來自動(dòng)地調(diào)節(jié)存儲(chǔ)器接口寬度。由于C32可以非常靈活地調(diào)整其存儲(chǔ)器接口寬度,使得存儲(chǔ)器接口電路的設(shè)計(jì)更加的靈活,因此非常適用于電機(jī)或電力系統(tǒng)等實(shí)時(shí)系統(tǒng)的數(shù)據(jù)采集與處理。

2019-06-12 05:00:08

描述該 Cyclone III 電源管理設(shè)計(jì)是一套完整的非隔離式電源解決方案,可提供為 FPGA 供電所需的全部 5 種電源軌。該設(shè)計(jì)還包括適用于 DDR 存儲(chǔ)器 VTT 和 VDDQ 電壓軌以及

2018-07-23 08:59:18

利用XILINX解決方案快速創(chuàng)建存儲(chǔ)器接口設(shè)計(jì)

2010-01-08 23:05:26 39

39 利用Virtex-5 FPGA迎接存儲(chǔ)器接口設(shè)計(jì)挑戰(zhàn):在不支持新的接口協(xié)議時(shí),存儲(chǔ)器接口設(shè)計(jì)師總是試圖支持越來越快的接口總線速度。目前,源同步雙數(shù)據(jù)速率 (DDR)存儲(chǔ)器件,例如 DDR2 SDRAM

2010-04-25 10:28:16 57

57 延續(xù)其在高清晰(HD) 視頻監(jiān)控解決方案上的領(lǐng)先優(yōu)勢(shì),Altera公司 (NASDAQ: ALTR) 發(fā)布世界上第一款基于FPGA的全HD 1080p/(每秒30幀) 30fps視頻分析解決方案,它采用Cyclone? IV FPGA。Altera的單芯片解

2011-10-19 12:25:53 1010

1010 Altera和Eutecus的高性能、低成本和低功率消耗采用FPGA架構(gòu)的視訊分析解決方案,專門設(shè)計(jì)用于為視訊監(jiān)控系統(tǒng)開發(fā)人員提供靈活的平臺(tái),突出最終系統(tǒng)的優(yōu)勢(shì)。讓設(shè)計(jì)人員能快速方便的獲

2012-05-07 10:06:55 747

747 Altera 公司的Cyclone IV 系列 FPGA 包括兩個(gè)系列:Cyclone IV E和Cyclone IV GX,具有低成本、低功耗的FPGA 架構(gòu),6 K 到150 K 的邏輯單元,高達(dá)6.3 Mb 的嵌入式存儲(chǔ)器,小于1.5 W 的總功耗;Cyclone IV GX 器件提供

2012-05-31 09:08:54 8725

8725

本資料是TI(德州儀器)推出的用于Xilinx和Altera FPGA的電源管理解決方案介紹。其主要內(nèi)容包括:低失真調(diào)整器、步減控制器、集成FET轉(zhuǎn)換器、低功率集成FET轉(zhuǎn)換器等

2012-08-10 16:14:27 43

43 AS下載和調(diào)試接口電路(Altera FPGA開發(fā)板)如下圖所示:

2012-08-15 14:29:23 5576

5576

高速SDRAM存儲(chǔ)器接口電路設(shè)計(jì)(Altera FPGA開發(fā)板)如下圖所示:

2012-08-15 14:33:41 3326

3326

FLASH存儲(chǔ)器接口電路圖(Altera FPGA開發(fā)板)

2012-08-15 14:36:31 6269

6269

異步SRAM存儲(chǔ)器接口電路設(shè)計(jì)(Altera FPGA開發(fā)板)如圖所示:

2012-08-15 14:37:05 3862

3862

本資料是關(guān)于Altera FPGA的選型及開發(fā),內(nèi)容大綱是:Altera的 FPGA體系結(jié)構(gòu)簡介;Altera的 FPGA選型策略;嵌入式邏輯分析工具SignalTAPII的使用;基于CPLD的FPGA配制方法。

2012-08-15 14:48:34 103

103 面臨著提高性能、降低成本、功能安全三大挑戰(zhàn),Altera 公司致力于FPGA解決方案,加強(qiáng)其在工業(yè)垂直細(xì)分市場(chǎng)中的廣泛使用。

2012-12-18 12:49:07 779

779 使用功能強(qiáng)大的FPGA來實(shí)現(xiàn)一種DDR2 SDRAM存儲(chǔ)器的用戶接口。該用戶接口是基于XILINX公司出產(chǎn)的DDR2 SDRAM的存儲(chǔ)控制器,由于該公司出產(chǎn)的這種存儲(chǔ)控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 FPGA 設(shè)計(jì)人員在滿足關(guān)鍵時(shí)序余量的同時(shí)力爭(zhēng)實(shí)現(xiàn)更高性能,在這種情況下,存儲(chǔ)器接口的設(shè)計(jì)是一個(gè)一向構(gòu)成艱難而耗時(shí)的挑戰(zhàn)。Xilinx FPGA 提供 I/O 模塊和邏輯資源,從而使接口設(shè)計(jì)變

2013-03-14 15:16:07 71

71 Altera公司(Nasdaq: ALTR)今天宣布,在硅片中演示了DDR4存儲(chǔ)器接口,其工作速率是業(yè)界最高的2,666 Mbps。

2014-12-19 15:13:01 3812

3812 2015.11.2最新Altera 外部存儲(chǔ)器接口手冊(cè)External Memory Interface Handbook

2015-11-11 10:53:27 11

11 該參考設(shè)計(jì)采用多種 TPS54325 和其他 TI 電源器件,是適用于 Xilinx Zynq FPGA 的全套電源解決方案。輸入電壓達(dá)到 12V 后,該參考解決方案可提供 Zynq FPGA 所需的所有電源軌(包括 DDR3 存儲(chǔ)器)。

2017-02-11 09:39:37 2995

2995

接口,無所不包。 性能要求和 Xilinx 解決方案 20 世紀(jì) 90 年代后期,存儲(chǔ)器接口從單倍數(shù)據(jù)速率 SDRAM 發(fā)展為雙

2017-11-24 16:21:46 876

876 的功能安全領(lǐng)先供應(yīng)商YOGITECH聯(lián)合開發(fā)的鎖步解決方案采用了Altera FPGA、SoC,認(rèn)證工具流程,以及YOGITECH的知識(shí)產(chǎn)權(quán)(IP)內(nèi)核。這一解決方案幫助客戶在Altera FPGA中輕松實(shí)現(xiàn)SIL3安全設(shè)計(jì),包括低成本Cyclone V FPGA和MAX 10 FPGA系列。

2018-08-31 16:46:00 1329

1329 ,幫助系統(tǒng)設(shè)計(jì)人員開發(fā)完整的芯片系統(tǒng)(SoC)解決方案。這一系列產(chǎn)品同時(shí)實(shí)現(xiàn)了從 16K邏輯單元(LE)到530K LE的FPGA解決方案以及高達(dá)1150萬ASIC邏輯門的HardCopy ASIC解決方案。

2018-10-25 15:43:50 1393

1393 系統(tǒng)架構(gòu)師必須解決高性能系統(tǒng)應(yīng)用的一些復(fù)雜問題,包括體系結(jié)構(gòu)、算法和功能范圍。一般而言,這些應(yīng)用中一個(gè)基本的問題是存儲(chǔ)器,作為系統(tǒng)性能的瓶頸和挑戰(zhàn)經(jīng)常位于存儲(chǔ)器的體系結(jié)構(gòu)中。由于外部存儲(chǔ)器需要更快

2018-12-24 08:00:00 14

14 個(gè)高速收發(fā)器,以及 1,067 Mbps (533 MHz) DDR3存儲(chǔ)器接口)達(dá)到了前所未有的水平,并具有優(yōu)異的信號(hào)完整性, 非常適合無線通信,固網(wǎng),軍事,廣播等其他最終市場(chǎng)中的高端數(shù)字應(yīng)用。本文介紹了Stratixreg; IV FPGA主要特性, Stratix IV GT器

2019-02-16 09:51:01 495

495

事實(shí)上,除了這些傳統(tǒng)要求,在前兩代非易失FPGA產(chǎn)品的經(jīng)驗(yàn)基礎(chǔ)上,萊迪思半導(dǎo)體(Lattice Semiconductor)公司還認(rèn)識(shí)到需要靈活的片上非易失存儲(chǔ)器,以及作為非易失FPGA新要求的用于現(xiàn)場(chǎng)邏輯更新的全面解決方案。

2019-06-16 09:48:47 1340

1340 ,并與內(nèi)部 FPGA 時(shí)鐘實(shí)現(xiàn)中心對(duì)齊。在這個(gè)方案中,內(nèi)部 FPGA時(shí)鐘采集傳出的數(shù)據(jù)。存儲(chǔ)器傳出的時(shí)鐘/ 選通脈沖用于決定與數(shù)據(jù)位相關(guān)的延遲值。因此,與選通脈沖相關(guān)的數(shù)據(jù)位的數(shù)量不受限制。由于無需將選通脈沖分配給相關(guān)數(shù)據(jù)位,所以不需要其他時(shí)鐘資源。

2020-04-11 09:55:08 743

743

、Cyclone IV GX或Stratixe IV GX FPGA、內(nèi)部存儲(chǔ)器和系統(tǒng)之間傳輸數(shù)據(jù)記憶參考設(shè)計(jì)包括一個(gè)基于Windows XP的軟件應(yīng)用程序,用于設(shè)置DMA轉(zhuǎn)移軟件應(yīng)用程序還測(cè)量和顯示轉(zhuǎn)移。

2020-05-14 17:51:24 58

58 在FPGA開發(fā)板上都有幾種不同的存儲(chǔ)器,比如SDRAM,F(xiàn)LASH,EPCS,還有內(nèi)部

2020-10-09 11:41:41 2921

2921 本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用Verilog設(shè)計(jì)Altera的DE2板上SDRAM存儲(chǔ)器。

2021-01-22 15:34:09 10

10 串行接口存儲(chǔ)器廣泛應(yīng)用于消費(fèi)類、汽車、電信、醫(yī)療、工業(yè)和 PC 相關(guān)市場(chǎng)。串行存儲(chǔ)器主要用于存儲(chǔ)個(gè)人偏好數(shù)據(jù)和配置/設(shè)置數(shù)據(jù),是當(dāng)今使用的最為靈活的非易失性存儲(chǔ)器(Nonvolatile

2021-03-31 11:14:47 7

7 Altera氣旋V系列FPGA的電源解決方案

2021-04-22 20:30:25 7

7 Altera Arria V系列FPGA的電源解決方案

2021-04-29 08:58:06 9

9 Altera Stratix V FPGA的電源解決方案

2021-04-29 09:41:47 5

5 設(shè)計(jì)解決方案43-Altera低壓FPGA的高性能開關(guān)模式電源解決方案

2021-04-30 11:55:18 7

7 FPGA各存儲(chǔ)器之間的關(guān)系(嵌入式開發(fā)工作怎么樣)-該文檔為FPGA各存儲(chǔ)器之間的關(guān)系總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 16:35:09 6

6 FPGA中嵌入式塊存儲(chǔ)器的設(shè)計(jì)(嵌入式開發(fā)平臺(tái))-該文檔為FPGA中嵌入式塊存儲(chǔ)器的設(shè)計(jì)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-08-04 10:14:40 6

6 在第三屆硬核中國芯領(lǐng)袖峰會(huì)上,芯動(dòng)科技憑借全球頂尖的全系高端DDR存儲(chǔ)接口解決方案,成功斬獲“硬核中國芯”2021年度最佳IP產(chǎn)品。

2022-01-05 09:17:04 2748

2748 中國上海—2022年8月5日——一站式定制芯片及IP供應(yīng)商——燦芯半導(dǎo)體日前宣布推出xSPI/Hyperbus/Xcella存儲(chǔ)器(閃存、PSRAM、MRAM 等)的控制器和PHY解決方案,適用于

2022-08-05 10:17:43 588

588 電源設(shè)計(jì)挑戰(zhàn)的方法,并解釋了成本、尺寸和效率之間的權(quán)衡。此外,還介紹了Maxim的Altera? FPGA解決方案。

2023-01-17 11:25:39 1729

1729

PLC的主機(jī)部分由中央處理器、輸入/輸出接口(I/0接口)通信、擴(kuò)展接口、儲(chǔ)存器、設(shè)備接口和電源等部分構(gòu)成。其中,基于京微齊力FPGA HME-M7和舜銘存儲(chǔ)鐵電存儲(chǔ)器PB85RS2MC的PLC系統(tǒng)已成為最佳解決方案。

2023-05-06 14:32:44 893

893

電子發(fā)燒友網(wǎng)站提供《集成電源解決方案-Altera FPGA應(yīng)用介紹.pdf》資料免費(fèi)下載

2023-11-28 09:21:50 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論