2G信號放大器:提升通信質量的利器?|深圳市特信電子有限公司2G信號放大器是一種用于增強2G網絡信號的設備,能夠有效提升手機信號覆蓋范圍和通話質量。在如今普遍普及的移動通信時代,信號放大器的作用愈發

2024-03-22 09:06:38

電子發燒友網站提供《完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表.pdf》資料免費下載

2024-03-13 13:58:12 0

0 電子發燒友網站提供《適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩壓器數據表.pdf》資料免費下載

2024-03-13 13:53:03 0

0 該內存速度高達5600MT/s,并可同時兼容5200和4800 MT/s。據詳情頁介紹,其工作電壓僅為1.1V,相較于DDR4 3200內存,性能提升幅度為1.5倍,且將于本月底開始出貨。

2024-03-13 11:43:05 89

89 電子發燒友網站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數據表.pdf》資料免費下載

2024-03-13 11:24:34 0

0 電子發燒友網站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內存電源解決方案數據表.pdf》資料免費下載

2024-03-13 11:13:44 0

0 電子發燒友網站提供《完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-03-13 10:16:45 0

0 此代碼示例說明如何使用 UART 將 TRAVEOTM T 2G 設備從深度睡眠中喚醒。 在活動模式下,TRAVEOTM T 2G 設備通過 UART 接收數據并回顯接收到的數據。 MCU 在接收

2024-01-31 06:08:32

和2個FTC310核,其中FTC664核主頻可達1.8GHz,FTC310核主頻可達1.5GHz。主板板載64位 DDR4內存,分2G和4G兩個版本,支持SD或者eMMC外部存儲。主板板載WiFi藍牙

2024-01-22 00:47:47

四大特點。

根據飛騰公布的參數顯示,飛騰派的CPU采用的是飛騰四核處理器,兼容ARM v8指令集,兩顆1.8GHz的FTC664和兩顆1.5GHz的FTC310,64位DDR內存,且分為2G版本和4G

2024-01-22 00:34:27

,其中 FTC664 核主頻可達 1.8GHz,FTC310 核主頻可達 1.5GHz。主板板載 64 位 DDR4 內存,有 2G 和 4G 兩個版本,支持 SD 或者 eMMC 外部存儲。主板板載

2024-01-13 22:02:08

DDR6和DDR5內存的區別有多大?怎么選擇更好? DDR6和DDR5是兩種不同的內存技術,它們各自在性能、功耗、帶寬等方面都有不同的特點。下面將詳細比較這兩種內存技術,以幫助你選擇更適合

2024-01-12 16:43:05 2848

2848 硬件世界拉斯維加斯現場報道:CES 2024大展期間,雷克沙帶來了豐富的存儲方案,涵蓋SSD、內存、存儲卡等,包括頂級的PCIe 5.0 SSD、DDR5高頻內存。

2024-01-12 10:32:27 282

282

DDR2 內存空間,中間要是錯了一個 Bytes,進異常了問題都不好找,不知道有沒有大佬遇見過類似的問題

以下是 G2D 初始化代碼:

2024-01-04 21:56:29

關于2023年第三季度毛利率增長原因,瀾起科技指出,主要是因為 DDR5內存接口芯片出貨量占比提升,特別是 DDR5 第二子代 RCD 芯片出貨量及其占比顯著提升。

2024-01-03 13:52:11 270

270 國產高性能、低功耗通用計算微處理器的設計研發和產業化推廣。飛騰派是一款面向行業工程師、學生和愛好者的開源硬件,采用飛騰嵌入式四核處理器,兼容ARM V8架構,板載64位 DDR4內存,分為2G和4G兩個版本

2024-01-02 22:43:09

FTC310核,其中FTC664核主頻可達1.8GHz,FTC310核主頻可達1.5GHz。主板板載64位 DDR4內存,分2G和4G兩個版本,支持SD或者eMMC外部存儲。主板板載WiFi藍牙,陶瓷天線

2024-01-02 22:23:36

在最為重要的內存顆粒上,根據軟件檢測,這款內存采用了編號為“H5CG48AEBDX018”的SK海力士A-die顆粒,與市面上大部分DDR5 7600、DDR5 8000等高速率內存使用的顆粒相同,這也意味著該內存可能具備優秀的超頻潛力。

2024-01-02 14:37:01 192

192

在DDR4年代,芝奇與阿斯加特成功完成逆襲,從原先的落落無名轉變為如今受到廣大DIY玩家追捧的內存廠商。

2023-12-29 10:41:00 247

247

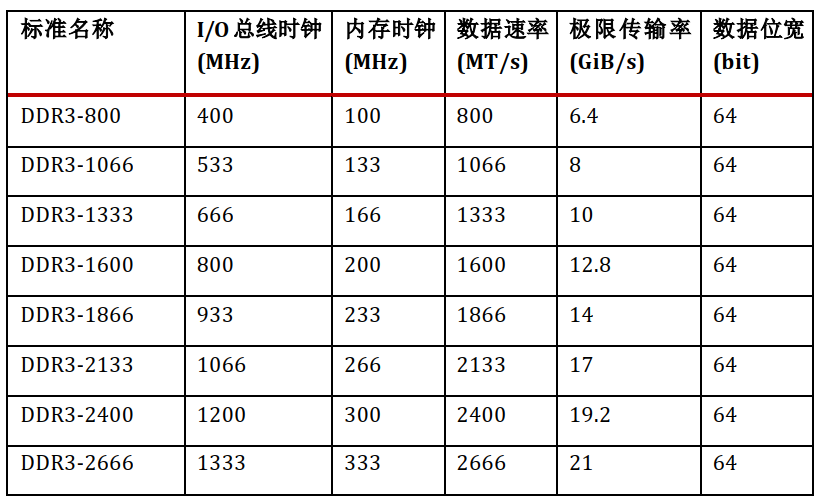

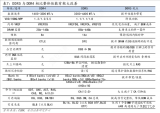

時鐘頻率:可通過倍頻技術升級的核心頻率。時鐘頻率可以理解為IO Buffer的實際工作頻率,DDR2中時鐘頻率為核心頻率的2倍,DDR3 DDR4中時鐘頻率為核心頻率的4倍。

2023-12-25 18:18:47 1188

1188

的引腳介紹

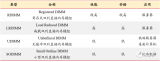

DDR內存條的引腳數,取決于內存條的類型和規格。以下是一些常見的 DDR內存條類型和它們的引腳數 :

DDR1內存條,184引腳(92針對每側)

DDR2內存條,240引腳(120針對每側

2023-12-25 14:02:58

的引腳介紹

DDR內存條的引腳數,取決于內存條的類型和規格。以下是一些常見的 DDR內存條類型和它們的引腳數 :

DDR1內存條,184引腳(92針對每側)

DDR2內存條,240引腳(120針對每側

2023-12-25 13:58:55

請問FM350-2可以帶8路增量式編碼器采集速度嗎? FM350-2是8 通道智能計數器模塊,我想用來采集8路增量式編碼器,采用速度測量模式來得到轉速信號,請問各位高手,可以實現嗎?

2023-12-20 08:19:17

通過在時鐘上升沿和下降沿的同時傳輸數據,實現了比傳統SDRAM更高的傳輸速率。目前,市場上主要有DDR、DDR2、DDR3、DDR4等幾代DDR內存。

2023-12-11 09:27:49 320

320 ,其中 FTC664 核主頻可達 1.8GHz,FTC310 核主頻可達 1.5GHz。

板載 64 位 DDR4 內存,有 2G 和 4G 兩個版本,支持 SD 或者 eMMC 外部存儲。主板板載

2023-12-10 21:27:03

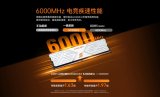

追風A60采用新一代DDR5內存規格,相較DDR4,性能提升接近1倍。高配6000MHz頻率實現DDR4 3200MHz的1.6倍傳輸速度和1.9倍傳輸帶寬,讓用戶在使用臺電內存條時獲得更快速、更流暢的電腦體驗。

2023-12-05 15:52:49 403

403

為滿足對高效內存性能日益增長的需求,DDR5相比其前身DDR4實現了性能的大幅提升,具體為傳輸速度更快、能耗更低、穩定性提高、內存密度更大和存取效率提高等。

2023-12-05 10:50:40 211

211

香蕉派BPI-R3 Mini路由器板開發板采用聯發科MT7986A(Filogic 830)四核ARM A53芯片設計,板載2G DDR 內存,8G eMMC和128MB SPI NAND存儲

2023-11-30 16:06:19

香蕉派 BPI-M4 Zero是BPI-M2 Zero的最新升級版本。它在性能上有很大的提高。主控芯片升級為全志科技H618 四核A53, CPU主頻提升25%。內存升級為2G

2023-11-30 15:46:09

DDR4和DDR3內存都有哪些區別? 隨著計算機的日益發展,內存也越來越重要。DDR3和DDR4是兩種用于計算機內存的標準。隨著DDR4內存的逐漸普及,更多的人開始對兩者有了更多的關注。 DDR

2023-10-30 09:22:00 3885

3885 飛騰派是由飛騰攜手中電港螢火工場研發的一款面向行業工程師、學生和愛好者的開源硬件,采用飛騰嵌入式四核處理器,兼容ARM V8架構,板載64位 DDR4內存,分為2G和4G兩個版本。主板板載WiFi

2023-10-25 11:44:22

。

關鍵特性

全志H618,四核ARM Cortex?-A53處理器

ARM Mali G31圖形處理器

WIFI & 藍牙

2G LPDDR4 RAM

8G eMMC閃存

1x

2023-10-08 15:25:13

摘要:本文將對DDR3和DDR4兩種內存技術進行詳細的比較,分析它們的技術特性、性能差異以及適用場景。通過對比這兩種內存技術,為讀者在購買和使用內存產品時提供參考依據。

2023-09-27 17:42:10 1088

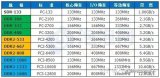

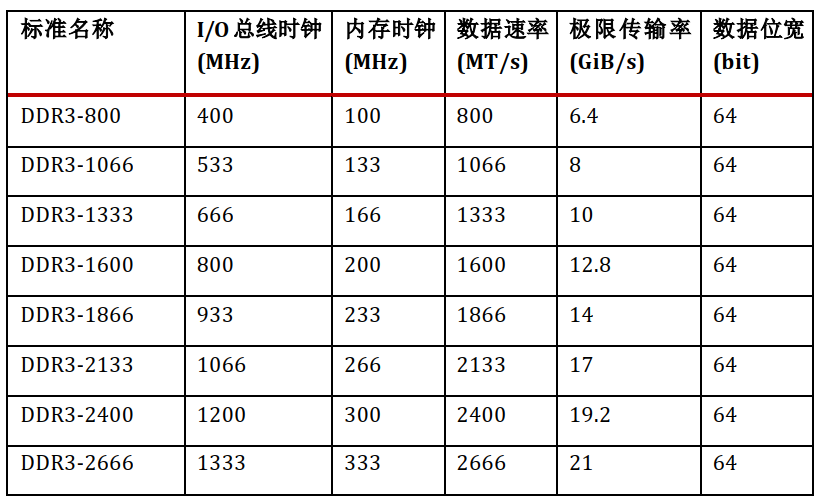

1088 我們在買DDR內存條的時候,經常會看到這樣的標簽DDR3-1066、DDR3-2400等,這些名稱都有什么含義嗎?請看下表。

2023-09-26 11:35:33 1922

1922

電子發燒友網站提供《具有最大1Gb DDR2 SDRAM的SAMA5D2 SIP MPU.pdf》資料免費下載

2023-09-25 10:11:12 0

0 相對于DDR3, DDR4首先在外表上就有一些變化,比如DDR4將內存下部設計為中間稍微突出,邊緣變矮的形狀,在中央的高點和兩端的低點以平滑曲線過渡,這樣的設計可以保證金手指和內存插槽有足夠的接觸面

2023-09-19 14:49:44 1478

1478

在全默認設置的情況下,影馳HOF OC Lab幻跡S DDR5 8000內存的工作速率為DDR5 4800,延遲設定為40-40-40-76,因此在這個設置下它的內存性能并不突出,與普通的DDR5 4800內存相當。

2023-09-15 10:40:42 750

750

:ArmSoM P2 Pro 物聯網開發板評測,支持PoE供電[]()

硬件說明

SoC 旁邊是 512 MB DDR3 內存。規格表明SoC的DDR接口支持DDR2、LPDDR2和DDR3內存

2023-09-13 12:21:21

PL341內存控制器是一款高性能、面積優化的DDR2 SDRAM內存控制器,兼容高級微控制器總線架構(AMBA)AXI協議。

有關AXI協議的詳細說明,請參閱AMBA AXI協議規范。

本節總結了周期模型的功能與硬件的功能,以及周期模型的性能和準確性。

2023-08-12 06:01:49

DDR5的主板不支持使用DDR4內存。DDR5(第五代雙倍數據率)和DDR4(第四代雙倍數據率)是兩種不同規格的內存技術,它們在電氣特性和引腳布局上存在明顯差異。因此,DDR5內存模塊無法插入DDR4主板插槽中,也不兼容DDR4內存控制器。

2023-08-09 15:36:25 12789

12789 CoreLink DDR2動態存儲器控制器(DMC-341)技術參考手冊

2023-08-02 15:28:28

隨著制程工藝的進步,DRAM內存芯片也面臨著CPU/GPU一樣的微縮難題,解決辦法就是上EUV光刻機,但是設備實在太貴,現在還要榨干DUV工藝最后一滴,DDR5內存有望實現單條1TB。

2023-07-31 17:37:07 875

875

/存儲:2 GB DDR4 SDRAM128MB SPI 閃存板載 8GB eMMC

連接性:2 個 2.5GbE 以太網端口Wi-Fi 6 4×4 2.4G Wi-Fi (MT7975N) + 4×4

2023-07-29 12:42:32

解一下米爾瑞薩RZ/G2L開發板的核心板:

MYC-YG2LX核心板采用高密度高速電路板設計,在大小為43mm*45mm的板卡上集成了RZ/G2L、DDR4、eMMC、E2PROM、PMIC電源管理等電路

2023-07-29 00:21:11

DDR是運行內存芯片,其運行頻率主要有100MHz、133MHz、166MHz三種,由于DDR內存具有雙倍速率傳輸數據的特性,因此在DDR內存的標識上采用了工作頻率×2的方法。 ? DDR芯片

2023-07-28 13:12:06 1877

1877

DDR是Double Data Rate的縮寫,即“雙倍速率同步動態隨機存儲器”。DDR是一種技術,中國大陸工程師習慣用DDR稱呼用了DDR技術的SDRAM,而在中國臺灣以及歐美,工程師習慣用DRAM來稱呼。

2023-07-16 15:27:10 3362

3362

今天我們測試的這款芝奇幻鋒戟Z5 RGB DDR5內存,在1.35V的電壓上就上到了7200MHz高頻,時序也控制在CL36-46-46-115 CR2,并且單條容量達到了24GB。

2023-06-26 10:39:41 869

869

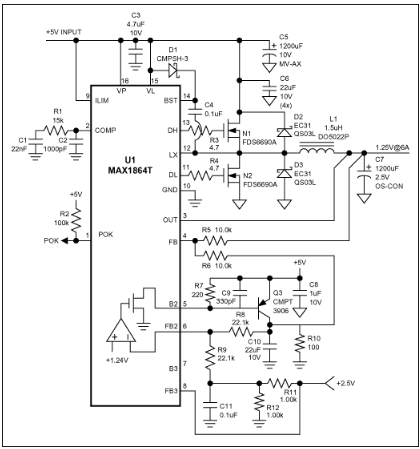

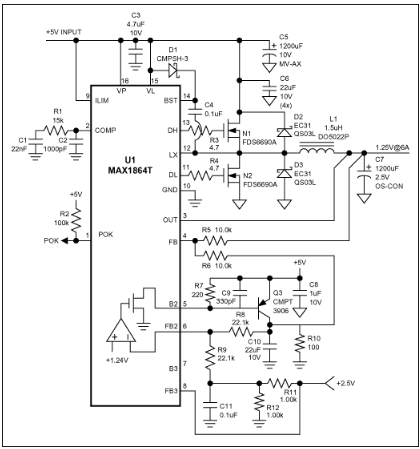

本設計筆記顯示了用于工作站和服務器的高速內存系統的雙倍數據速率 (DDR) 同步 DRAM (SDRAM)。使用MAX1864 xDSL/電纜調制解調器電源,電路產生等于并跟蹤VREF的終止電壓(VTT)。

2023-06-26 10:34:36 549

549

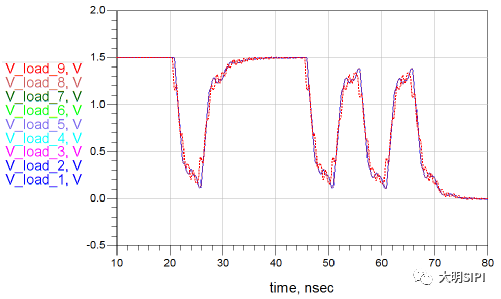

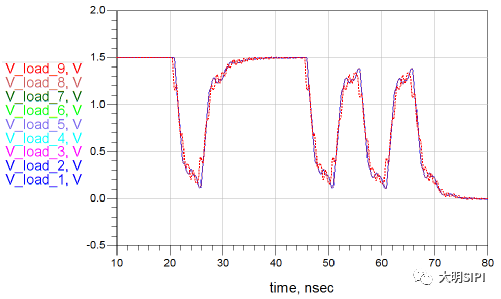

這里介紹兩種方式改善帶有ECC的奇數負載的DDR2信號質量。一種不需要改變拓撲結構,另一種需要對拓撲結構進行調整。

2023-06-15 17:39:34 474

474

★ DDR內存條治具六大特點 有哪些呢?

讓凱智通小編為你解答~

①通用性高:只需換顆粒限位框,即可測試尺寸不同的顆粒;

②操作省力方便:采用手動翻蓋滾軸式結構,相比同類產品減少磨損,達到更高的機械

2023-06-15 15:45:22

我嘗試使用S32DS 3.5的DDR驗證工具測試S32G274A-RDB2板,但顯示串行連接存在通信問題。

這些問題應該如何解決?

2023-06-05 07:16:27

和筆記本。內存模組的類型決定了所需的內存接口芯片和內存模組配套芯片。 ? ? ? 內存進入 DDR5 新世代,標準升級拉動相關芯片需求。與 DDR4 相比, DDR5 的優勢可簡單地概括為: ( 1)速度

2023-05-29 14:07:38 1359

1359

大家好,

請幫助我了解 S32G2 是否支持雙內存進行 OTA 更新。基本上在這里我們期待雙分區。

2023-05-29 08:51:39

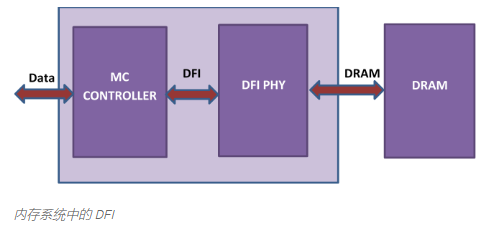

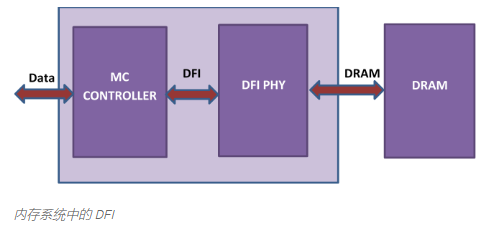

、時序和可編程參數。DFI 適用于所有 DRAM 協議,包括 DDR4、DDR3、DDR2、DDR、LPDDR4、LPDDR3、LPDDR2 和 LPDDR。

2023-05-26 15:27:31 4564

4564

S32G3開發板上使用的ddr芯片是micro MT53E1G32D2FW-046 AUT: B

但是我們的開發板使用的是三星的芯片(K4FBE3D4HM THCL)。

如何查看 S32G3 支持的 DDR 芯片?。以及如何支持新的DDR芯片?

2023-05-23 07:15:48

我對從 S32G274A 控制 Micron MT35XU512ABA QSPI 串行 NOR 閃存感到頭疼。

該板是定制板(不是 NXP RDB2 或 EVP 之一)。

我使用 NXP

2023-05-18 08:48:37

感謝

感謝電子發燒友論壇、感謝米爾電子,把米爾瑞薩RZ/G2L開發板試用話動的機會給了我。雖然周五就收到了開發板,但是由于復陽了,為了能及時的完成試用活動,所以今天努力的爬起來完成開箱報告。

開箱

2023-05-14 19:41:46

我嘗試將 MPC5748G(硅版本 1N81M)與 freemaster 版本 3.0.2.6 一起使用,并帶有選項“BDM 連接 Nexus2+ 內存訪問”。我使用 PE micro

2023-05-12 08:19:46

我正在尋找 S32G2 中內存映射系統計數器的地址。

Armv8 參考手冊(DDI 0487H.a,D7 章,尤其是 D7.1.2 節)提供了系統計數器的定義。引用其中的一點:

通用

2023-05-12 06:18:27

應用處理器

ARM Cortex的高級實現?-A8核心,針對最低功耗進行了優化。

i.MX53xD處理器采用ARM Cortex?-A8核心,其工作時鐘速度高達1.2千兆赫。

它提供DDR2

2023-05-11 11:04:19

錄像機 NVR/XVR 芯片方案

核心板: 提供連接器與郵票孔兩種,商業級2G、商業級4G、商業級8G工業級2G、工業級4G、國產化工業級2G多種核心板引腳兼容,適用于同一底板,產品升級自如,適用于各個

2023-05-10 10:58:28

DDR4內存模塊支持單個64位通道(如果考慮ECC,則為72位通道)。相比之下,DDR5內存模塊配備了兩個獨立的32位通道(40位ECC)。

2023-05-08 10:27:44 1330

1330 內存是數據中心、服務器以及個人計算機等技術發展的重要組成。目前內存的發展是由DDR技術路線引導,TE Connectivity(以下簡稱“TE”)經歷了DDR1、DDR2、DDR3、DDR4的迭代

2023-05-06 17:33:42 1392

1392

我有一塊使用基于 i.MX8QM MEK 板的 i.MX8QM 的板。我使用了 2 x MT53D512M32D2(總計 4GB DDR 內存)并且它可以正常工作。

現在我想把內存加倍到 8GB。我

2023-05-04 06:39:14

我正在嘗試從 Integration_Reference_Examples_S32G2_2023_01 編譯 Bootloader_S32G2XX_ASR_4.4_M7 項目。在 Eb Tresos

2023-04-11 09:02:06

ls1046a ddr 內存 8G 升級到 16G 硬件和軟件需要哪些改動 ..?

2023-04-10 06:21:57

社會:ls1043aDDR:MT40A2G8VA-062E:B,x5,4 個用于 8GB,1 個用于 ECC。我使用 CW 獲取配置文件: 我嘗試了兩個文件來生成 img他們都在 BL2 運行時遇到問題:使用 (0-2GB) DDR 數據顯示不正確:(寫入≠讀取) 我該如何解決?謝謝

2023-04-07 06:44:48

DDR內存1代已經淡出市場,直接學習DDR3 SDRAM感覺有點跳躍;如下是DDR1、DDR2以及DDR3之間的對比。

2023-04-04 17:08:47 2867

2867

]: 無法打開 pfe_ddr: 2 ERR[ hw/s32g/pfe_platform_master.c:1623]:無法獲取 BMU2 池內存ERR[src/pfe_drv.c:1456]:無法初始化

2023-04-03 08:23:52

我們使用 10*MT40A1G16 獲得 16GB 內存,一個 ddr 控制器連接 8GB。三個問題:1)在codewarrior ddr config上,我們應該選擇什么dram類型?NoDimm

2023-04-03 07:24:21

大家好,請問大家知道如何在SDK1.9中修改U-Boot for P2020的2G DRAM大小嗎?我嘗試更改p1_p2_rdb_pc.h,但是uboot 無法運行,見日志如下。還有一個

2023-04-03 06:40:26

IP CORE DDR2 SDRAM XO2

2023-03-30 12:02:09

SITE LICENSE DDR2 SDRAM ECP3

2023-03-30 12:01:46

SITE LICENSE DDR2 SDRAM ECP2

2023-03-30 12:01:46

SITE LICENSE DDR2 SDRAM ECP2M

2023-03-30 12:01:46

IP CORE DDR2 SDRAM XO2

2023-03-30 12:01:19

IP CORE DDR2 SDRAM CTLR ECP2M

2023-03-30 12:01:17

IP CORE DDR2 SDRAM CTLR ECP3

2023-03-30 12:01:16

IP CORE DDR2 SDRAM CTLR ECP2

2023-03-30 12:01:16

IP CORE DDR2 SDRAM CTLR SC/SCM

2023-03-30 12:01:16

的操作,但我仍然無法訪問內存區域。我是如何一步一步粗略地做到這一點的:初始化 DDR 控制器 1 和 2 -> 為每個控制器開啟 TZC 網守 -> 應用內存區域信息 -> 設置操作

2023-03-29 07:58:56

基于全志科技D1-H芯片定制的AIoT開發板,是全球首款支持64bit RISC-V指令集并支持Linux系統的可量產開發板

2023-03-28 12:58:34

我一直在研究 BL2 上的 DDR 驅動程序,并注意到 *** 設置了對內存區域的訪問,在研究 CW 腳本時也是如此。是否需要初始化 *** 才能訪問 DDR 內存?我知道它不需要 MMU,但它與 TZ 一樣嗎?

2023-03-27 07:13:46

你好 我們正在使用 4 * 2GB DDR4 芯片構建我們的定制 ls1046a 板。(我們參考LS1046AFRWY,容量翻倍,去掉ECC)首先我生成了 BL2 二進制文件制作 PLAT

2023-03-24 08:50:43

電子發燒友App

電子發燒友App

評論