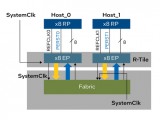

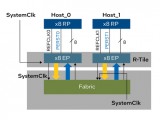

Arm Neoverse S3 是 Arm 專門(mén)面向基礎(chǔ)設(shè)施的第三代系統(tǒng) IP,應(yīng)用范圍涵蓋高性能計(jì)算 (HPC) 、機(jī)器學(xué)習(xí) (ML)、邊緣和顯示處理單元,是新一代基礎(chǔ)設(shè)施系統(tǒng)級(jí)芯片 (SoC) 的理想技術(shù)根基。

2024-03-22 11:30:01 202

202

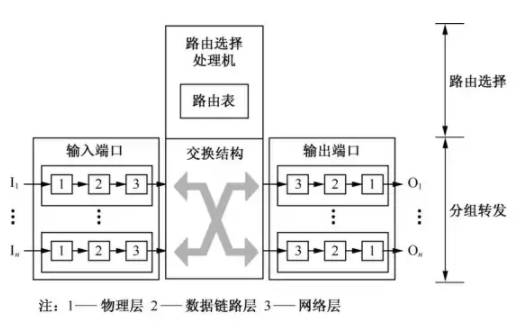

發(fā)現(xiàn)和識(shí)別故障實(shí)時(shí)數(shù)據(jù)分析數(shù)據(jù)包分析數(shù)據(jù)包快速捕獲和解碼隨著基礎(chǔ)設(shè)施環(huán)境的快速變化和技術(shù)的不斷進(jìn)步,用戶數(shù)量和IT基礎(chǔ)設(shè)施流量迅速增加,服務(wù)故障的數(shù)量也相應(yīng)增加。此時(shí),服務(wù)中斷不僅會(huì)帶來(lái)直接的不便

2024-03-05 08:05:08 227

227

IEEE 802.1Qbv作為一項(xiàng)針對(duì)實(shí)時(shí)流量時(shí)間敏感性進(jìn)行優(yōu)化的重要標(biāo)準(zhǔn),在網(wǎng)絡(luò)通信領(lǐng)域具有廣泛的應(yīng)用前景。通過(guò)引入時(shí)間感知調(diào)度機(jī)制和支持多個(gè)優(yōu)先級(jí),IEEE 802.1Qbv為實(shí)時(shí)應(yīng)用程序提供了可靠的網(wǎng)絡(luò)基礎(chǔ)設(shè)施,滿足了各種應(yīng)用場(chǎng)景對(duì)延遲和時(shí)序性的高要求。

2024-02-29 17:19:46 332

332

開(kāi)放式、虛擬化無(wú)線接入網(wǎng)絡(luò)(開(kāi)放式vRAN)正迎來(lái)商用設(shè)計(jì)和部署的強(qiáng)勁發(fā)展勢(shì)頭,智能計(jì)算創(chuàng)新和AI對(duì)5G基礎(chǔ)設(shè)施的重要性也在快速增加。作為通信和AI技術(shù)的領(lǐng)軍企業(yè),高通技術(shù)公司一直處于行業(yè)前沿推動(dòng)現(xiàn)代5G網(wǎng)絡(luò)的未來(lái)發(fā)展。

2024-02-21 09:11:47 227

227 隨著企業(yè)信息化程度的不斷提高,IT基礎(chǔ)設(shè)施的重要性日益凸顯。如何構(gòu)建高效、安全的IT基礎(chǔ)設(shè)施成為了企業(yè)面臨的重要挑戰(zhàn)。KVM矩陣系統(tǒng)作為一種先進(jìn)的遠(yuǎn)程管理解決方案,以其高效、靈活、安全的特點(diǎn),成為

2024-02-18 14:53:02 243

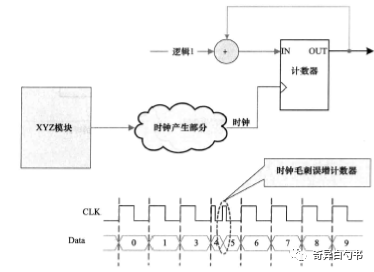

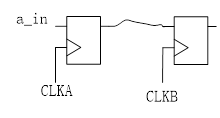

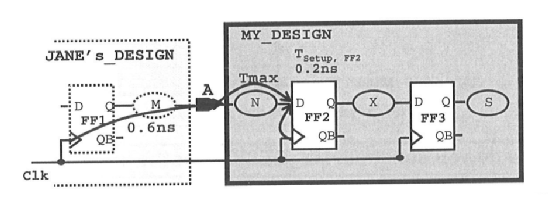

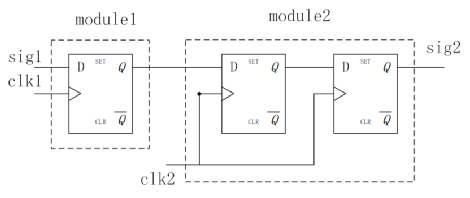

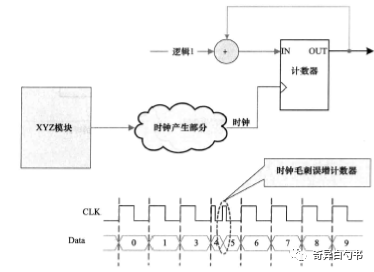

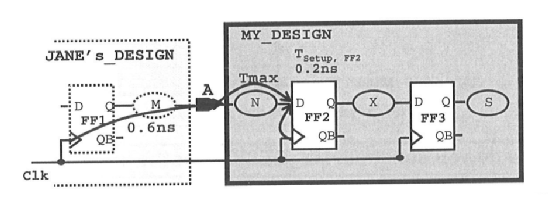

243 時(shí)序電路基本原理是指電路中的輸出信號(hào)與輸入信號(hào)的時(shí)間相關(guān)性。簡(jiǎn)單來(lái)說(shuō),就是電路的輸出信號(hào)要依賴于其輸入信號(hào)的順序和時(shí)間間隔。 時(shí)序電路由時(shí)鐘信號(hào)、觸發(fā)器和組合邏輯電路組成。時(shí)鐘信號(hào)是時(shí)序電路的重要

2024-02-06 11:30:00 344

344 時(shí)序電路是一種能夠按照特定的順序進(jìn)行操作的電路。它以時(shí)鐘信號(hào)為基準(zhǔn),根據(jù)輸入信號(hào)的狀態(tài)和過(guò)去的狀態(tài)來(lái)確定輸出信號(hào)的狀態(tài)。時(shí)序電路廣泛應(yīng)用于計(jì)算機(jī)、通信系統(tǒng)、數(shù)字信號(hào)處理等領(lǐng)域。根據(jù)不同的分類標(biāo)準(zhǔn)

2024-02-06 11:25:21 393

393 電路,并探討時(shí)序電路中可能存在的狀態(tài)循環(huán)。 首先,同步時(shí)序電路是指時(shí)序元件按照整個(gè)系統(tǒng)的時(shí)鐘信號(hào)進(jìn)行同步操作的時(shí)序電路。常見(jiàn)的同步時(shí)序元件有鎖存器和觸發(fā)器。鎖存器可以將輸入信號(hào)“鎖定”,在時(shí)鐘上升沿或下降沿將輸入信

2024-02-06 11:22:30 288

288 FPGA輸入的時(shí)鐘信號(hào)必須是方波么?正弦波會(huì)有影響么? FPGA是一種可編程邏輯器件,通常用于實(shí)現(xiàn)數(shù)字電路。輸入時(shí)鐘信號(hào)是FPGA中非常重要的時(shí)序信號(hào),對(duì)整個(gè)系統(tǒng)的穩(wěn)定性和性能都有很大

2024-01-31 11:31:42 1238

1238 芯片為什么要時(shí)鐘信號(hào) 時(shí)鐘芯片的作用是什么? 時(shí)鐘信號(hào)在芯片中起著非常重要的作用。它是芯片的“心臟”,相當(dāng)于人體的心臟,用于同步和控制芯片中的各個(gè)功能模塊之間的操作。時(shí)鐘信號(hào)可以提供一個(gè)穩(wěn)定的時(shí)間

2024-01-29 18:11:31 621

621 什么是時(shí)鐘信號(hào)?數(shù)字電路的時(shí)鐘信號(hào)是怎么產(chǎn)生呢? 時(shí)鐘信號(hào),也稱為時(shí)鐘脈沖,是用于同步數(shù)字電路中所有操作的基本信號(hào)。它提供了一個(gè)參考頻率,使得所有電路元件都能按照同樣的節(jié)奏進(jìn)行工作。時(shí)鐘信號(hào)

2024-01-25 15:40:52 894

894 將兩個(gè)支持相同協(xié)議的設(shè)備通過(guò)同步通信串口連接,怎么保證兩個(gè)通信串口的時(shí)鐘信號(hào)是同步啟動(dòng)的呢?這一步是靠軟件實(shí)現(xiàn)還是硬件實(shí)現(xiàn),如果在建立完成之前,兩臺(tái)設(shè)備的通信時(shí)鐘恰好是正交的,那么此時(shí)該讓主設(shè)備還是從設(shè)備等待這1/4/個(gè)周期呢,這1/4個(gè)周期會(huì)不會(huì)影響其它正常功能的運(yùn)行?

2024-01-19 14:55:15

關(guān)注計(jì)算能力的提升,通信基礎(chǔ)設(shè)施的提升跟不上,那么數(shù)據(jù)中心的整體系統(tǒng)性能依然受限,無(wú)法發(fā)揮出真正的潛力。DPU的提出背景就是應(yīng)對(duì)這些數(shù)據(jù)量和復(fù)雜性的指數(shù)級(jí)增長(zhǎng)。未來(lái),需要將計(jì)算移至接近數(shù)據(jù)的位置,這是

2023-12-21 10:47:01

作為集信息計(jì)算力、網(wǎng)絡(luò)運(yùn)載力、數(shù)據(jù)存儲(chǔ)力于一體的新型生產(chǎn)力,算力主要通過(guò)算力基礎(chǔ)設(shè)施向社會(huì)提供服務(wù)。因此,做強(qiáng)做優(yōu)做大我國(guó)數(shù)字經(jīng)濟(jì),促進(jìn)數(shù)字經(jīng)濟(jì)與實(shí)體經(jīng)濟(jì)融合發(fā)展,必須筑牢算力基礎(chǔ)設(shè)施的堅(jiān)實(shí)底座。

2023-12-20 16:26:23 270

270 我最近做一個(gè)CCD的項(xiàng)目,需要用到AD9945,因?yàn)樗念l率高,但是AD9945怎么與STM32F103外部引腳連接,他輸出的12位并行數(shù)據(jù)接到哪里?還有AD9945與STM32之間通過(guò)SPI通信,通信時(shí)序怎么寫(xiě)?時(shí)序圖如下:

2023-12-05 08:28:07

以上兩圖分別為AD2S1210并口配置模式下寫(xiě)時(shí)序和普通模式下讀時(shí)序

請(qǐng)問(wèn)這兩個(gè)圖中的CLKIN是什么時(shí)鐘?并口通訊的時(shí)候需要用時(shí)鐘嗎?

我的理解是,

并口配置模式下寫(xiě)寄存器,控制信號(hào)用nCS

2023-12-04 06:00:23

電子發(fā)燒友網(wǎng)站提供《磁隔離對(duì)延遲時(shí)序性能的改善.pdf》資料免費(fèi)下載

2023-11-27 09:44:05 0

0 差分探頭是一種常用的測(cè)量差分時(shí)鐘時(shí)延的工具。差分時(shí)鐘是指由兩個(gè)相互關(guān)聯(lián)的時(shí)鐘信號(hào)組成的時(shí)鐘系統(tǒng),其中一個(gè)時(shí)鐘信號(hào)被稱為主時(shí)鐘,另一個(gè)被稱為輔助時(shí)鐘。測(cè)量差分時(shí)鐘時(shí)延有助于了解時(shí)鐘信號(hào)的穩(wěn)定性和準(zhǔn)確性

2023-11-24 10:54:42 291

291 時(shí)鐘的時(shí)序特性主要分為抖動(dòng)(Jitter)、偏移(Skew)、占空比失真(Duty Cycle Distortion)3點(diǎn)。對(duì)于低速設(shè)計(jì),基本不用考慮這些特征;對(duì)于高速設(shè)計(jì),由于時(shí)鐘本身的原因造成的時(shí)序問(wèn)題很普遍,因此必須關(guān)注。

2023-11-22 09:29:16 350

350

和時(shí)鐘偏差組成的。

二、時(shí)序路徑

時(shí)序路徑是指從FPGA輸入到輸出的所有邏輯路徑組成的路徑。當(dāng)存在時(shí)序路徑時(shí),需要考慮時(shí)序約束以確保正確的邏輯功能和時(shí)序性能。

時(shí)序路徑中的關(guān)鍵元素包括:

(1) 路徑

2023-11-15 17:41:10

我連接了 8 個(gè) LTC6804 用兩線制通信都沒(méi)有問(wèn)題

但連接到第9 或 10 個(gè)時(shí) 讀取電池電壓偶爾就會(huì)發(fā)生 pec error 問(wèn)題

請(qǐng)問(wèn)這情況是什么問(wèn)題?

是超過(guò)了 isoSPI 菊鏈上限了嗎?

2023-11-10 07:45:35

的核心部分。主要包括以下幾個(gè)方面的指標(biāo): - 功耗測(cè)試:衡量芯片在不同工作狀態(tài)下的能耗。 - 時(shí)序測(cè)試:測(cè)試芯片內(nèi)部各個(gè)模塊之間的時(shí)序關(guān)系,確保信號(hào)的正確傳遞。 - 時(shí)鐘性能測(cè)試:評(píng)估芯片對(duì)外部時(shí)鐘源的輸入和輸出響應(yīng)速度。 - 噪聲測(cè)試:測(cè)

2023-11-09 09:24:20 421

421 同步通信的原理是發(fā)送端在發(fā)送串行數(shù)據(jù)的同時(shí),提供一個(gè)時(shí)鐘信號(hào),并按照一定的約定(例如:在時(shí)鐘信號(hào)的上升沿的時(shí)候,將數(shù)據(jù)發(fā)送出去)發(fā)送數(shù)據(jù)。接收端根據(jù)發(fā)送端提供的時(shí)鐘信號(hào),以及雙方的約定,接收數(shù)據(jù)

2023-11-07 08:07:32 1813

1813

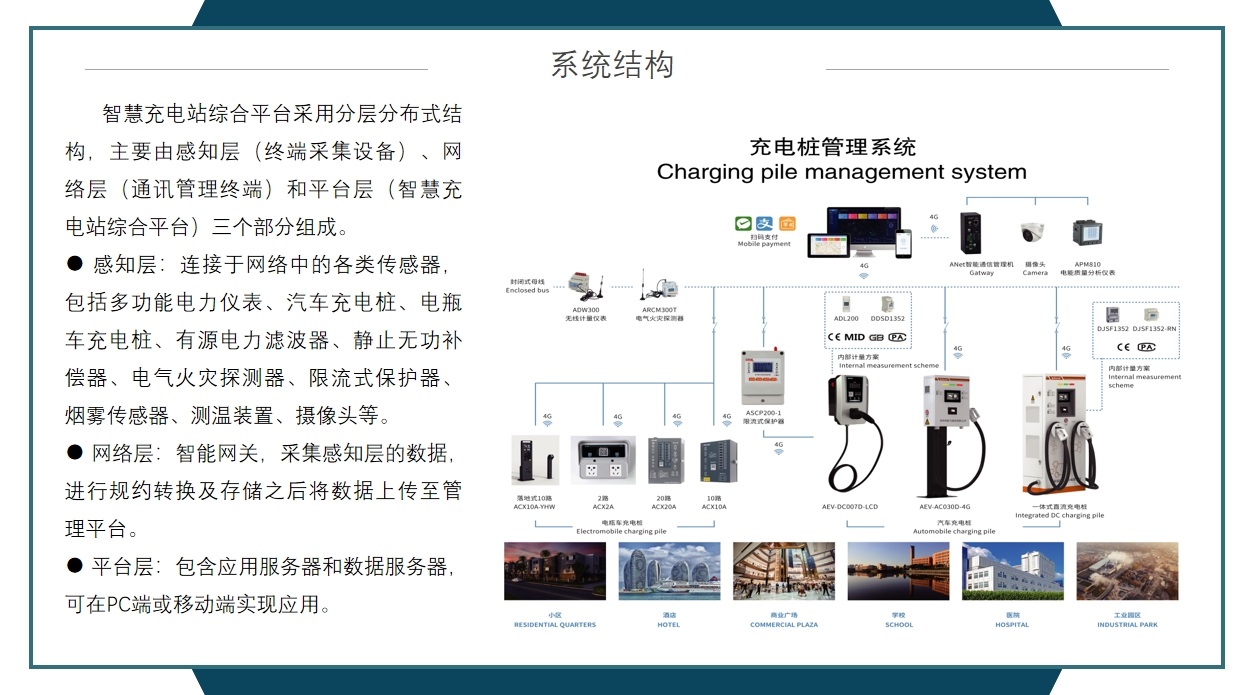

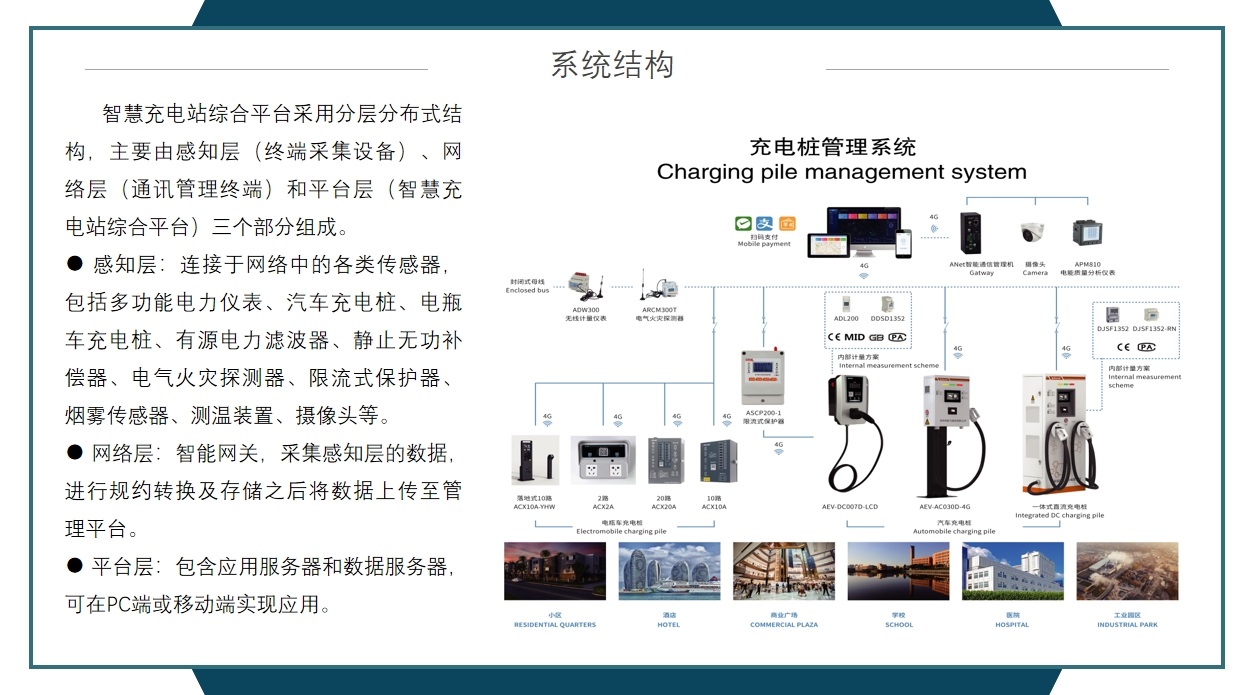

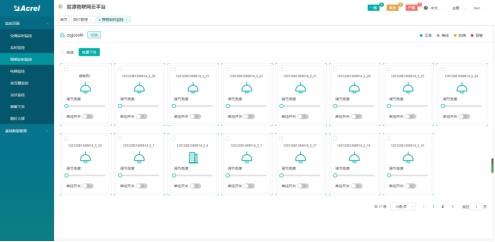

隨著新能源汽車的普及,充電基礎(chǔ)設(shè)施的建設(shè)和管理顯得尤為重要。為了滿足市場(chǎng)需求,提高充電設(shè)施的運(yùn)營(yíng)效率和服務(wù)質(zhì)量,公司推出了一款充電樁收費(fèi)運(yùn)營(yíng)云平臺(tái),為充電設(shè)施的智能化管理提供了解決方案。

2023-11-06 14:54:57 368

368

時(shí) , 將輸入 D 端的數(shù)據(jù)給到輸出 Q, 當(dāng)使能條件不滿足時(shí) , 輸入數(shù)據(jù) D 會(huì)暫存在觸發(fā)器當(dāng)中 , 直到觸發(fā)條件滿足才給到輸出 Q。 (2):D 觸發(fā)器工作時(shí)序 時(shí)鐘 clk: 周期性變化信號(hào) 。 時(shí)鐘極性 (CPOL): 時(shí)鐘初始值是 0, 時(shí)鐘極性為 0; 時(shí)鐘初始值是 1, 時(shí)鐘極性為 1。

2023-11-02 12:00:01 305

305

我們看到,今年的Forrester Wave超融合基礎(chǔ)設(shè)施圖,領(lǐng)導(dǎo)者(第一象限)是Nutanix和VMware,表現(xiàn)強(qiáng)勁者(第二象限)有HPE,微軟和深信服、Cisco。其他的都是競(jìng)爭(zhēng)者(第三象限),有浪潮信息,華為、IBM、Scale Computing、SmartX。

2023-10-29 17:01:19 511

511

電子發(fā)燒友網(wǎng)報(bào)道(文/周凱揚(yáng))從數(shù)智化轉(zhuǎn)型的角度來(lái)看,如何結(jié)合云邊端的基礎(chǔ)設(shè)施共建智慧園區(qū),已經(jīng)成了智慧城市建設(shè)中最關(guān)鍵的一環(huán)。尤其是在城市人口規(guī)模持續(xù)增長(zhǎng)的前提下,無(wú)縫結(jié)合關(guān)鍵基礎(chǔ)設(shè)施和數(shù)字技術(shù)

2023-10-26 09:01:20 1131

1131

如何用時(shí)鐘振蕩器產(chǎn)生穩(wěn)定的100hz或1hz的時(shí)鐘信號(hào)? 時(shí)鐘信號(hào)是電子系統(tǒng)中至關(guān)重要的組成部分,用于同步各種信號(hào)和操作。它需要穩(wěn)定、準(zhǔn)確、可靠地工作,以確保系統(tǒng)性能。時(shí)鐘信號(hào)的產(chǎn)生可以通過(guò)許多

2023-10-25 15:07:55 954

954 什么器件可以產(chǎn)生

時(shí)鐘信號(hào)?

時(shí)鐘信號(hào)是用來(lái)做什么用的?

時(shí)鐘信號(hào)起什么作用?

時(shí)鐘信號(hào)是一個(gè)精確的電

信號(hào),它可以通過(guò)電子器件來(lái)產(chǎn)生,并且具有一定的頻率和周期。

時(shí)鐘信號(hào)在電子系統(tǒng)中具有非常重要的作用,因?yàn)?/div>

2023-10-25 15:07:45 635

635 不夠標(biāo)準(zhǔn),這可能導(dǎo)致系統(tǒng)性能下降或故障。因此,我們需要對(duì)這種情況進(jìn)行適當(dāng)?shù)奶幚怼?對(duì)于波形和電平不標(biāo)準(zhǔn)的時(shí)鐘信號(hào),一般應(yīng)進(jìn)行以下處理: 1. 時(shí)鐘信號(hào)濾波 波形和電平不標(biāo)準(zhǔn)的時(shí)鐘信號(hào)往往會(huì)出現(xiàn)抖動(dòng)或噪聲,這會(huì)對(duì)數(shù)字系

2023-10-24 10:04:38 663

663 2023年IDC全球SD-WAN基礎(chǔ)設(shè)施市場(chǎng)報(bào)告發(fā)現(xiàn), SD-WAN 基礎(chǔ)設(shè)施市場(chǎng)在 2022 年激增 25%,預(yù)計(jì)到 2027 年將達(dá)到 75 億美元,復(fù)合年增長(zhǎng)率為 10.1% 。

2023-10-18 15:37:55 656

656

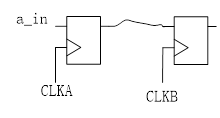

為什么異步fifo中讀地址同步在寫(xiě)時(shí)鐘域時(shí)序分析不通過(guò)? 異步FIFO中讀地址同步在寫(xiě)時(shí)鐘域時(shí)序分析不通過(guò)的原因可能有以下幾個(gè)方面: 1. 讀地址同步在寫(xiě)時(shí)鐘域時(shí)序分析未覆蓋完全 在時(shí)序分析時(shí),可能

2023-10-18 15:23:55 309

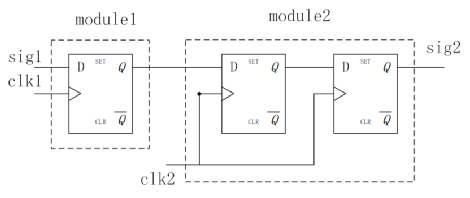

309 時(shí)鐘信號(hào)的同步 在數(shù)字電路里怎樣讓兩個(gè)不同步的時(shí)鐘信號(hào)同步? 在數(shù)字電路中,時(shí)鐘信號(hào)的同步是非常重要的問(wèn)題。因?yàn)樵?b class="flag-6" style="color: red">信號(hào)處理過(guò)程中,如果不同步,就會(huì)出現(xiàn)信號(hào)的混淆和錯(cuò)誤。因此,在數(shù)字電路中需要采取一些

2023-10-18 15:23:48 771

771 基礎(chǔ)設(shè)施,分為硬件基礎(chǔ)設(shè)施和軟件基礎(chǔ)設(shè)施。硬件基礎(chǔ)設(shè)施,包含常用器件庫(kù)、封裝庫(kù)、原理圖庫(kù)和硬件參考設(shè)計(jì)等等;而今天我們討論的重點(diǎn),主要在于軟件基礎(chǔ)設(shè)施。

2023-10-12 16:09:50 363

363 [中國(guó),上海,2023年9月20日] 在華為全聯(lián)接大會(huì)2023期間,華為數(shù)字能源舉辦新型數(shù)字產(chǎn)業(yè)能源基礎(chǔ)設(shè)施分論壇,全球200多位行業(yè)領(lǐng)袖、技術(shù)專家、生態(tài)伙伴齊聚上海,共同探討數(shù)據(jù)中心能源、行業(yè)關(guān)鍵

2023-09-20 19:40:09 388

388

[中國(guó),上海,2023年9月20日] 華為全聯(lián)接大會(huì)2023于9月20-22日在上海世博展覽館盛大舉辦。華為數(shù)字能源展示了綠色低碳的全場(chǎng)景數(shù)字能源解決方案及商業(yè)實(shí)踐,新型數(shù)字產(chǎn)業(yè)能源基礎(chǔ)設(shè)施、清潔

2023-09-20 19:40:05 353

353

是數(shù)據(jù)信號(hào)(SDA)。SCL信號(hào)是在IIC通信中非常重要的一個(gè)信號(hào),它確定了數(shù)據(jù)的傳輸速率以及同步時(shí)序。 IIC時(shí)鐘信號(hào)的產(chǎn)生需要硬件支持,一般通過(guò)外部晶振或者內(nèi)部時(shí)鐘源產(chǎn)生。在IIC總線使用過(guò)程中,時(shí)鐘信號(hào)的頻率很重要,必須要與所有設(shè)備的時(shí)鐘頻率保持一致。一般來(lái)說(shuō),為了保證

2023-09-19 17:16:02 735

735 我們?cè)O(shè)計(jì)時(shí)要盡可能避免在內(nèi)部產(chǎn)生時(shí)鐘,如果操作不當(dāng),會(huì)導(dǎo)致設(shè)計(jì)功能和時(shí)序問(wèn)題。總而言之,盡量在代碼中避免操作時(shí)鐘。

2023-09-19 09:26:42 424

424

,這篇文章將會(huì)詳細(xì)介紹它們之間的差異。 單脈沖時(shí)鐘信號(hào)是指在短時(shí)間內(nèi)以一定的速率發(fā)生較短、高速峰值的脈沖信號(hào)。它們通常用于時(shí)序控制,計(jì)數(shù)和精確時(shí)鐘測(cè)量系統(tǒng)中。一般而言,單脈沖信號(hào)所用的頻率比較高,可達(dá)數(shù)百M(fèi)Hz級(jí)別,這比其他

2023-09-15 16:28:23 994

994 的基礎(chǔ),因此,在電子學(xué)領(lǐng)域中,如何產(chǎn)生和控制時(shí)鐘信號(hào)是一項(xiàng)至關(guān)重要的技術(shù)。 時(shí)鐘信號(hào)是指一個(gè)周期性的方波信號(hào),其周期性能和穩(wěn)定性非常重要。為了使時(shí)鐘信號(hào)精確可靠地產(chǎn)生,需要考慮多種因素的影響,包括設(shè)備的穩(wěn)定性、

2023-09-15 16:28:22 1490

1490 時(shí)鐘脈沖的主要作用 時(shí)鐘脈沖是指一個(gè)定時(shí)器發(fā)出的一系列電脈沖信號(hào),這些脈沖信號(hào)在計(jì)算機(jī)系統(tǒng)中被廣泛應(yīng)用。時(shí)鐘脈沖的主要作用是為計(jì)算機(jī)內(nèi)部的所有操作提供精準(zhǔn)的時(shí)間基準(zhǔn),包括支持CPU時(shí)序、同步數(shù)據(jù)

2023-09-15 16:28:17 1359

1359 芯片為什么需要時(shí)鐘信號(hào)? 在我們?nèi)粘I钪校覀兯褂玫母鞣N電子設(shè)備都需要一個(gè)時(shí)鐘信號(hào)來(lái)進(jìn)行計(jì)時(shí)和同步,例如:手機(jī)、電腦、電視、汽車、機(jī)器人、智能家居等設(shè)備都需要時(shí)鐘信號(hào)。對(duì)于各種這些電子設(shè)備

2023-09-15 16:28:14 1366

1366 件、計(jì)算機(jī)、數(shù)字電路和通訊協(xié)議等設(shè)備的信號(hào)。它的主要作用是進(jìn)行時(shí)序控制,使數(shù)據(jù)傳輸和處理的時(shí)序保持一致。時(shí)鐘信號(hào)一般由計(jì)時(shí)器產(chǎn)生,其具有一定的周期性、穩(wěn)定性和精度。 時(shí)鐘信號(hào)的主要信號(hào)參數(shù)包括周期、頻率、精度和占空比等,

2023-09-15 16:28:12 1763

1763 電子發(fā)燒友網(wǎng)站提供《云基礎(chǔ)設(shè)施速度下的安全控制.pdf》資料免費(fèi)下載

2023-09-08 09:47:55 0

0 需要時(shí)鐘信號(hào)來(lái)控制內(nèi)部元件的工作節(jié)奏,以確保芯片的正常運(yùn)轉(zhuǎn)。 時(shí)鐘信號(hào)是指一種周期性的信號(hào),在芯片內(nèi)部被用于同步元件的工作狀態(tài)。時(shí)鐘信號(hào)的基本作用是為芯片內(nèi)部提供準(zhǔn)確、穩(wěn)定的時(shí)序信號(hào),從而協(xié)調(diào)芯片內(nèi)部各個(gè)部

2023-09-01 15:38:11 1373

1373 業(yè)界高端FPGA的卓越性能和高口碑聲譽(yù)都有哪些因素了?其中很重要的一個(gè)因素就是FPGA內(nèi)部豐富的時(shí)鐘資源使得FPGA在處理復(fù)雜時(shí)鐘結(jié)構(gòu)和時(shí)序要求的設(shè)計(jì)中具有很大優(yōu)勢(shì)。設(shè)計(jì)師可以更好地控制和管理時(shí)鐘信號(hào),提高時(shí)序性能、減少時(shí)鐘相關(guān)問(wèn)題,并滿足設(shè)計(jì)的高性能和穩(wěn)定性要求。

2023-08-31 10:44:01 530

530 時(shí)鐘電路的原理基于振蕩器和時(shí)序控制邏輯。振蕩器負(fù)責(zé)產(chǎn)生穩(wěn)定的周期性信號(hào),而時(shí)序控制邏輯用于控制和同步各個(gè)電子組件的操作和通信。

常用的振蕩器包括晶體振蕩器、RC振蕩器和串?dāng)_鎖相環(huán)(PLL

2023-08-24 15:40:10 8076

8076 AMBA?2 AHB?至AMBA 3 AXI?橋使AHB主機(jī)能夠與AXI從機(jī)或互連進(jìn)行通信(如果時(shí)鐘和重置信號(hào)是公共的)。

該網(wǎng)橋有三種變種,可支持以下接口:

·ARM11 AHB-Lite主控器

2023-08-21 06:43:35

今日,全球著名技術(shù)分析機(jī)構(gòu)DCIG(Data Center Intelligence Group)發(fā)布報(bào)告《DCIG 2023-24企業(yè)超融合基礎(chǔ)設(shè)施TOP5》(以下簡(jiǎn)稱“報(bào)告”),華為

2023-08-18 17:15:03 347

347 ? ? 城市地下市政基礎(chǔ)設(shè)施建設(shè)是城市安全有序運(yùn)行的的重要基礎(chǔ)。隨著城市地下空間大面積的開(kāi)發(fā)利用,各類地下空間安全事故呈多發(fā)趨勢(shì),城市內(nèi)澇、地面塌陷、燃?xì)獗ā⒋竺娣e停水停電等事故都對(duì)城市地下空間

2023-08-17 16:39:17 1686

1686 單位寬(Single bit)信號(hào)即該信號(hào)的位寬為1,通常控制信號(hào)居多。對(duì)于此類信號(hào),如需跨時(shí)鐘域可直接使用xpm_cdc_single,如下圖代碼所示。參數(shù)DEST_SYNC_FF決定了級(jí)聯(lián)觸發(fā)器

2023-08-16 09:53:23 462

462

,每個(gè)處理器集群都為每個(gè)處理器核心包含一個(gè)交叉觸發(fā)接口(CTI)組件。CTI和處理器核心之間的連接包括:?告知處理器核心停止調(diào)試活動(dòng)的信號(hào)?指示處理器核心正在停止的信號(hào)每個(gè)CTI還連接到交叉觸發(fā)矩陣

2023-08-10 07:01:18

正如“聚合”的意思(字典)“兩個(gè)或多個(gè)事物聚集在一起的發(fā)生”。所以我們可以假設(shè)它也與 2 個(gè)時(shí)鐘路徑聚集在一起有關(guān)。 (了解時(shí)鐘路徑請(qǐng)參考另一篇博客-靜態(tài)時(shí)序分析基礎(chǔ):第1部分“時(shí)序路徑”)

2023-08-08 10:31:44 524

524

而 Arm 以優(yōu)異的每瓦性能表現(xiàn)和更出色的吞吐率帶來(lái)了成本優(yōu)勢(shì),通過(guò)提供總擁有成本(TCO)優(yōu)勢(shì)及出色的能效表現(xiàn),成為了 5G 網(wǎng)絡(luò)基礎(chǔ)設(shè)施能效考量中的絕佳之選。

2023-08-04 16:14:01 527

527

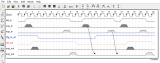

輕松繪制各種時(shí)序圖,同時(shí)支持快捷鍵操作功能,操作簡(jiǎn)單便捷。TimeGen還可以自由設(shè)置各個(gè)文本框的屬性字體樣式、字體大小和顏色、可以標(biāo)注信號(hào)之間的關(guān)系,調(diào)整信號(hào)周期的寬度,還能設(shè)置信號(hào)的背景圖案。如下圖1是小編自己畫(huà)的一個(gè)時(shí)序圖。

2023-08-04 10:42:15 6581

6581

FPGA設(shè)計(jì)中的絕大部分電路為同步時(shí)序電路,其基本模型為“寄存器+組合邏輯+寄存器”。同步意味著時(shí)序路徑上的所有寄存器在時(shí)鐘信號(hào)的驅(qū)動(dòng)下步調(diào)一致地運(yùn)作。

2023-08-03 09:27:25 912

912

可能無(wú)法滿足時(shí)序要求。 跨時(shí)鐘域信號(hào)的約束寫(xiě)法 問(wèn)題一: 沒(méi)有對(duì)設(shè)計(jì)進(jìn)行全面的約束導(dǎo)致綜合結(jié)果異常,比如沒(méi)有設(shè)置異步時(shí)鐘分組,綜合器對(duì)異步時(shí)鐘路徑進(jìn)行靜態(tài)時(shí)序分析導(dǎo)致誤報(bào)時(shí)序違例。 ??約束文件包括三類,建議用戶應(yīng)該將這三類約束

2023-08-01 09:18:34 1041

1041

隨著每個(gè) OSAT 和代工廠提供自己的技術(shù),支持小芯片和異構(gòu)結(jié)構(gòu)的 IC 封裝選項(xiàng)也不斷傳播。結(jié)果,術(shù)語(yǔ)變得相當(dāng)混亂。值得慶幸的是,這些封裝結(jié)構(gòu)比目前行業(yè)中存在的術(shù)語(yǔ)簡(jiǎn)單得多。

2023-07-29 14:25:28 880

880

時(shí)序:字面意思,時(shí)序就是時(shí)間順序,實(shí)際上在通信中時(shí)序就是通信線上按照時(shí)間順序發(fā)生的電平變化,以及這些變化對(duì)通信的意義就叫時(shí)序。

2023-07-26 10:06:03 1639

1639 “全局時(shí)鐘和第二全局時(shí)鐘資源”是FPGA同步設(shè)計(jì)的一個(gè)重要概念。合理利用該資源可以改善設(shè)計(jì)的綜合和實(shí)現(xiàn)效果;如果使用不當(dāng),不但會(huì)影響設(shè)計(jì)的工作頻率和穩(wěn)定性等,甚至?xí)?dǎo)致設(shè)計(jì)的綜合、實(shí)現(xiàn)過(guò)程出錯(cuò)

2023-07-24 11:07:04 655

655

世界越來(lái)越依賴太空基礎(chǔ)設(shè)施。這導(dǎo)致人們?cè)絹?lái)越意識(shí)到,它需要受到保護(hù),免受網(wǎng)絡(luò)攻擊,而網(wǎng)絡(luò)攻擊可能會(huì)破壞關(guān)鍵的基礎(chǔ)設(shè)施,造成巨大破壞。衛(wèi)星在支持物流系統(tǒng)、自動(dòng)取款機(jī)、航空公司等方面發(fā)揮

2023-07-20 16:28:56 414

414 今天我們要介紹的時(shí)序分析概念是clock gate。 clock gate cell是用data signal控制clock信號(hào)的cell,它被頻繁地用在多周期的時(shí)鐘path,可以節(jié)省功耗。

2023-07-03 15:06:03 1479

1479

引言 在同步電路設(shè)計(jì)中,時(shí)序是一個(gè)非常重要的因素,它決定了電路能否以預(yù)期的時(shí)鐘速率運(yùn)行。為了驗(yàn)證電路的時(shí)序性能,我們需要進(jìn)行 靜態(tài)時(shí)序分析 ,即 在最壞情況下檢查所有可能的時(shí)序違規(guī)路徑,而不需要測(cè)試

2023-06-28 09:38:57 713

713

跨時(shí)鐘域是如何產(chǎn)生的呢?現(xiàn)在的芯片(比如SOC,片上系統(tǒng))集成度和復(fù)雜度越來(lái)越高,通常一顆芯片上會(huì)有許多不同的信號(hào)工作在不同的時(shí)鐘頻率下。

2023-06-27 11:39:41 894

894

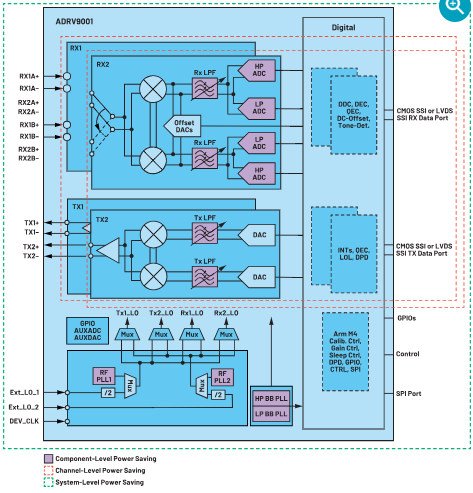

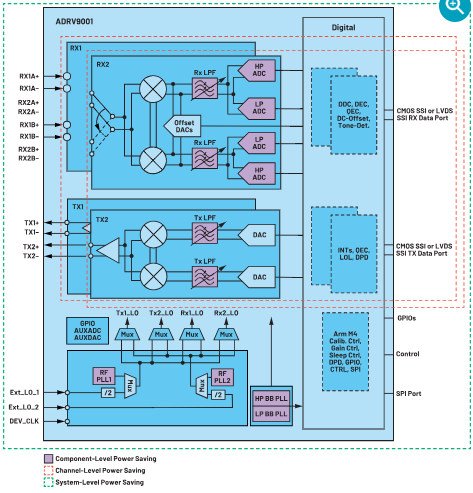

本文探討了ADRV9001,這是ADI公司最新一代軟件定義無(wú)線電(SDR)收發(fā)器單片集成電路(IC),旨在為衛(wèi)星、軍事、陸地移動(dòng)、公用事業(yè)基礎(chǔ)設(shè)施和蜂窩網(wǎng)絡(luò)的眾多關(guān)鍵任務(wù)型通信應(yīng)用提供可擴(kuò)展的功率和性能。它首先從組件級(jí)別、通道級(jí)別和IC系統(tǒng)級(jí)別介紹ADRV9001中的三個(gè)用戶定義節(jié)能選項(xiàng)。

2023-06-14 16:22:37 618

618

前面幾篇FPGA時(shí)序約束進(jìn)階篇,介紹了常用主時(shí)鐘約束、衍生時(shí)鐘約束、時(shí)鐘分組約束的設(shè)置,接下來(lái)介紹一下常用的另外兩個(gè)時(shí)序約束語(yǔ)法“偽路徑”和“多周期路徑”。

2023-06-12 17:33:53 861

861 在FPGA設(shè)計(jì)中,時(shí)序約束對(duì)于電路性能和可靠性非常重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的主時(shí)鐘約束。

2023-06-12 17:29:21 1226

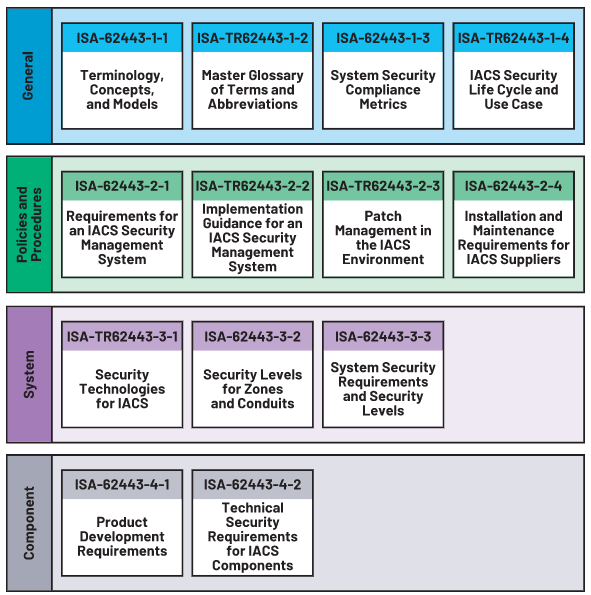

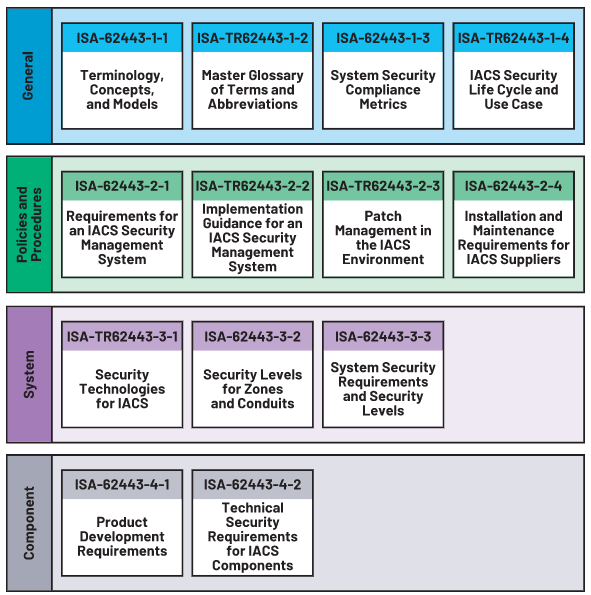

1226 本文探討了IEC 62443系列標(biāo)準(zhǔn)的基本推理和優(yōu)勢(shì),這是一組旨在確保網(wǎng)絡(luò)安全彈性的協(xié)議 保護(hù)關(guān)鍵基礎(chǔ)設(shè)施和數(shù)字化工廠。這一領(lǐng)先的標(biāo)準(zhǔn)提供了廣泛的安全層;然而,它給那些尋求認(rèn)證的人帶來(lái)了一些挑戰(zhàn)。我們將解釋安全IC如何為努力實(shí)現(xiàn)工業(yè)自動(dòng)化控制系統(tǒng)(IACS)組件認(rèn)證目標(biāo)的組織提供必要的幫助。

2023-06-08 11:34:58 1250

1250

在FPGA設(shè)計(jì)中,時(shí)序約束的設(shè)置對(duì)于電路性能和可靠性都至關(guān)重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的基礎(chǔ)知識(shí)。

2023-06-06 18:27:13 6194

6194

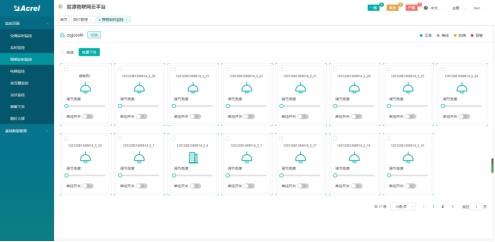

部等8部門(mén)共同印發(fā)《物聯(lián)網(wǎng)新型基礎(chǔ)設(shè)施建設(shè)三年行動(dòng)計(jì)劃(2021-2023年)》。 ? ? Acrel-EIoT能源物聯(lián)網(wǎng)平臺(tái)加速電網(wǎng)基礎(chǔ)設(shè)施智能化改造和智能微電網(wǎng)建設(shè),部署區(qū)域能源管理、智能計(jì)量體系、綜合能源服務(wù)等典型應(yīng)用系統(tǒng)。結(jié)合5G等通信設(shè)施的部署,搭建能

2023-06-05 09:59:22 607

607

自動(dòng)駕駛對(duì)公路基礎(chǔ)設(shè)施的影響主要包括物理基礎(chǔ)設(shè)施、交通控制設(shè)備(TCD)和其它路邊基礎(chǔ)設(shè)施、運(yùn)輸管理和運(yùn)營(yíng)系統(tǒng)(TSMO)及其基礎(chǔ)設(shè)施、多

式聯(lián)運(yùn)基礎(chǔ)設(shè)施。

2023-06-01 14:25:57 0

0 隨著城市科技現(xiàn)代化發(fā)展、綜合管廊巡檢是城市基礎(chǔ)設(shè)施建設(shè)中重要的一環(huán),承擔(dān)著電力、通信、供水、排水等關(guān)鍵網(wǎng)絡(luò)的運(yùn)輸和分發(fā)任務(wù)。為了保障城市運(yùn)行的安全和順暢必須不定時(shí)地對(duì)綜合管廊巡檢保養(yǎng)。然而,傳統(tǒng)

2023-05-31 16:47:29 434

434

我們的團(tuán)隊(duì)可以幫助您選擇正確的平臺(tái),并遷移您的服務(wù)器、數(shù)據(jù)庫(kù)和應(yīng)用程序。基于云解決方案的基礎(chǔ)設(shè)施有助于最大的企業(yè)和增長(zhǎng)最快的初創(chuàng)企業(yè)變得更加敏捷,并降低成本。

2023-05-30 09:13:44 243

243 設(shè)備旨在滿足數(shù)據(jù)中心基礎(chǔ)設(shè)施、云服務(wù)提供商 (CSP)、5G 通信服務(wù)提供商 (CoSP) 當(dāng)前和未來(lái)的多種需求。

2023-05-29 15:14:48 1010

1010

算力基礎(chǔ)設(shè)施是算力網(wǎng)絡(luò)的核心,以構(gòu)建高效、靈活、敏捷的算力基礎(chǔ)設(shè)施為目標(biāo),積極引入云原生、無(wú)服務(wù)器計(jì)算、異構(gòu)計(jì)算、算力卸載等技術(shù),探索算力原生、存算一體等新方向, 持續(xù)增強(qiáng)算力能力,釋放算力價(jià)值

2023-05-24 16:38:58 7

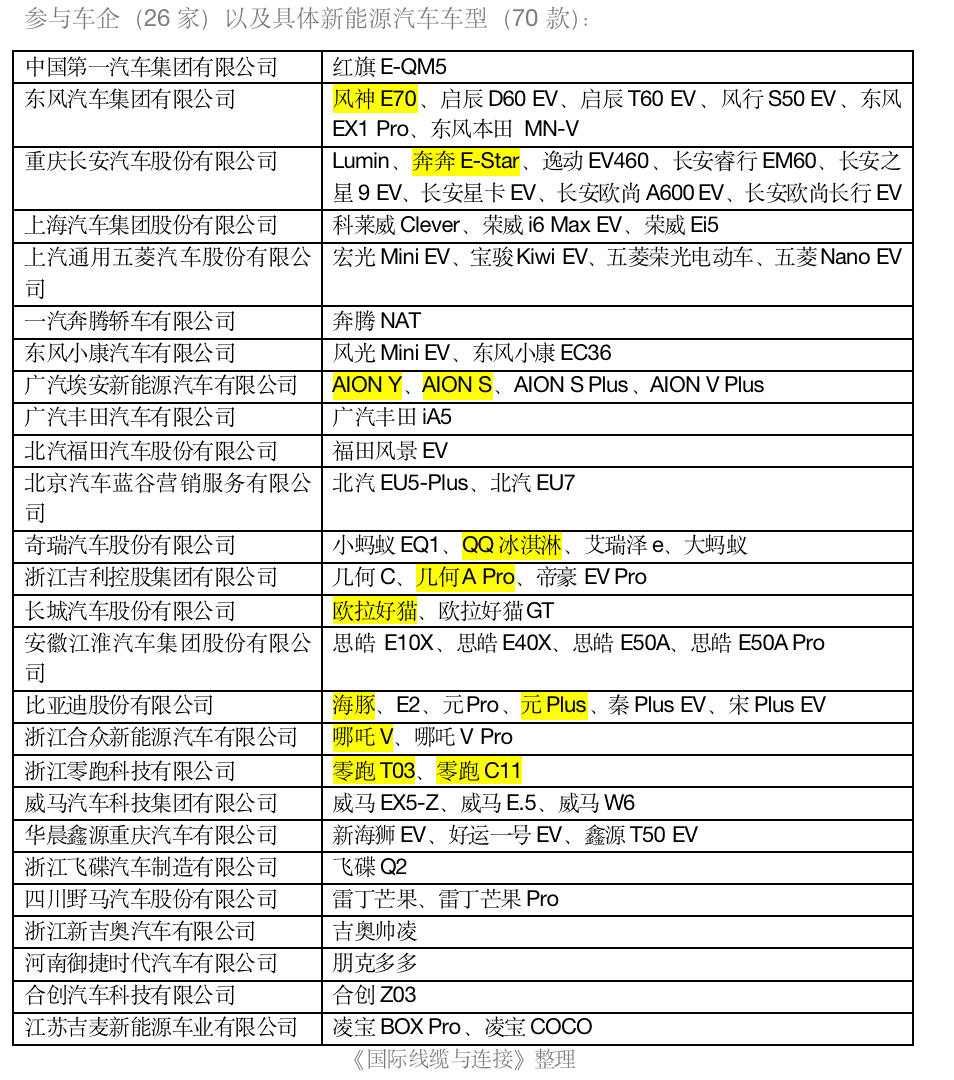

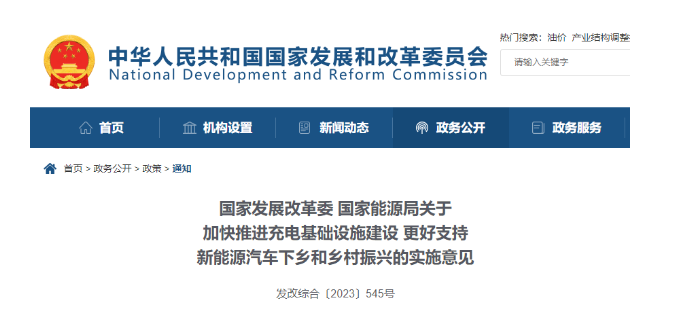

7 5月17日,國(guó)家發(fā)改委、國(guó)家能源局兩部門(mén)聯(lián)合發(fā)布《關(guān)于加快推進(jìn)充電基礎(chǔ)設(shè)施建設(shè) 更好支持新能源汽車下鄉(xiāng)和鄉(xiāng)村振興的實(shí)施意見(jiàn)》。

2023-05-19 16:03:02 672

672

在無(wú)線通信方便快捷的背后,是一個(gè)又一個(gè)穩(wěn)定可靠的通信節(jié)點(diǎn),它們編織在一起,便是全時(shí)空?qǐng)鼍跋碌母咚僖苿?dòng)互聯(lián)。在每一個(gè)通信節(jié)點(diǎn)下,光纖、路由器、電源設(shè)備等高效協(xié)同,為無(wú)線通信提供穩(wěn)定可靠的支持。而今天我們要談?wù)摰脑骷t是幫助那些無(wú)線通信基礎(chǔ)設(shè)施滿足網(wǎng)速、EMI等指標(biāo)的連接器——有線連接與接插件。

2023-05-19 10:57:58 717

717

5月5日,國(guó)常會(huì)提出,要聚焦制約新能源汽車下鄉(xiāng)的突出瓶頸,適度超前建設(shè)充電基礎(chǔ)設(shè)施,創(chuàng)新充電基礎(chǔ)設(shè)施建設(shè)、運(yùn)營(yíng)、維護(hù)模式。

2023-05-08 15:45:19 747

747

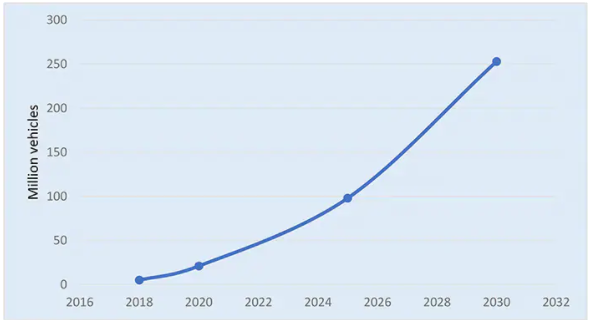

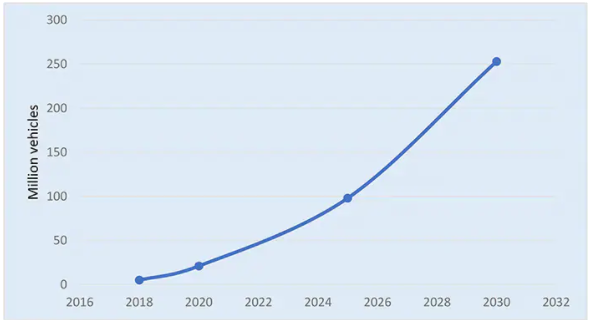

目前世界各地在爭(zhēng)相將燃油汽車替換為電動(dòng)汽車,預(yù)計(jì)電動(dòng)汽車的普及率將迅速攀升。與目前部署的充電樁數(shù)量相比,預(yù)計(jì)電動(dòng)車 (EV) 的迅速采用將會(huì)對(duì)可用的充電樁數(shù)量帶來(lái)重大改變。在本文中,我們將研究電動(dòng)車采用率的增加將對(duì)配電基礎(chǔ)設(shè)施提出怎樣的要求,以及在規(guī)劃電動(dòng)車充電基礎(chǔ)設(shè)施時(shí)必須考慮的一些因素。

2023-05-08 10:29:03 326

326

時(shí)鐘周期約束:用戶需要將設(shè)計(jì)中的所有時(shí)鐘進(jìn)行約束后,綜合器才能進(jìn)行合理的靜態(tài)時(shí)序分析。一個(gè)設(shè)計(jì)中的時(shí)鐘主要分為兩類:主時(shí)鐘和生成時(shí)鐘。主時(shí)鐘包括由全局時(shí)鐘引腳接入的時(shí)鐘、高速收發(fā)器的輸出時(shí)鐘。

2023-05-06 09:31:34 1253

1253

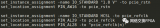

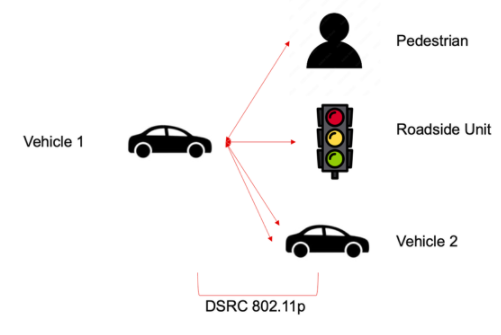

車輛到基礎(chǔ)設(shè)施 (V2I) 是一種通信模型,允許車輛與支持一個(gè)國(guó)家高速公路系統(tǒng)的組件共享信息,例如交通信號(hào)燈、車道標(biāo)記、路燈、標(biāo)牌、架空 RFID 閱讀器、攝像頭和停車計(jì)時(shí)器。幾乎任何物體,從建筑物到燈柱再到住宅區(qū),都可以配備此功能。

2023-05-04 09:52:55 337

337

我正在嘗試使用 i.MX8MP EVK 輸出 LVDS,但我無(wú)法調(diào)整 LVDS 輸出時(shí)鐘頻率和時(shí)序。我需要修改哪些源碼,應(yīng)該怎么修改?需要的時(shí)序參數(shù)如下:像素時(shí)鐘 = 54.13 MHz有效分辨率

2023-04-18 09:46:58

BMS 使用 ADI 的 LTC6820 連接到 MC33772C,具有菊花鏈喚醒功能,但沒(méi)有喚醒功能。MC33772C上電后進(jìn)入INIT,等待60S后進(jìn)入IDLE狀態(tài)。 通信正常,喚醒時(shí)序為6820的CS下拉、上拉、下拉、上拉操作,但沒(méi)有喚醒。關(guān)于在菊花鏈喚醒中尋找什么的任何建議?

2023-04-17 07:49:25

展頻IC在4M時(shí)鐘上的應(yīng)用

2023-04-14 10:12:27 0

0 單位寬(Single bit)信號(hào)即該信號(hào)的位寬為1,通常控制信號(hào)居多。對(duì)于此類信號(hào),如需跨時(shí)鐘域可直接使用xpm_cdc_single

2023-04-13 09:11:37 911

911 當(dāng)設(shè)計(jì)存在多個(gè)時(shí)鐘時(shí),根據(jù)時(shí)鐘的相位和頻率關(guān)系,分為同步時(shí)鐘和異步時(shí)鐘,這兩類要分別討論其約束

2023-04-06 14:34:28 886

886

我們?cè)贏SIC或FPGA系統(tǒng)設(shè)計(jì)中,常常會(huì)遇到需要在多個(gè)時(shí)鐘域下交互傳輸?shù)膯?wèn)題,時(shí)序問(wèn)題也隨著系統(tǒng)越復(fù)雜而變得更為嚴(yán)重。

2023-04-06 10:56:35 413

413 形式。儲(chǔ)能市場(chǎng)在過(guò)去幾年里的火爆程度大家也項(xiàng)目共睹。 ? “光伏+儲(chǔ)能”模式里,光伏逆變器和儲(chǔ)能變流器是兩大核心基礎(chǔ)設(shè)施。經(jīng)由這兩大核心基礎(chǔ)設(shè)施如何把大量組件的電量匯集在一起,都依賴于電纜和連接器。光伏連接器和儲(chǔ)

2023-04-06 00:32:00 2092

2092

系統(tǒng)時(shí)序設(shè)計(jì)中對(duì)時(shí)鐘信號(hào)的要求是非常嚴(yán)格的,因?yàn)槲覀兯械?b class="flag-6" style="color: red">時(shí)序計(jì)算都是以恒定的時(shí)鐘信號(hào)為基準(zhǔn)。但實(shí)際中時(shí)鐘信號(hào)往往不可能總是那么完美,會(huì)出現(xiàn)抖動(dòng)(Jitter)和偏移(Skew)問(wèn)題。

2023-04-04 09:20:56 1633

1633 信號(hào)完整性仿真重點(diǎn)分析有關(guān)高速信號(hào)的3個(gè)主要問(wèn)題:信號(hào)質(zhì)量、串?dāng)_和時(shí)序。對(duì)于信號(hào)質(zhì)量,目標(biāo)是獲取具有明確的邊緣,且沒(méi)有過(guò)度過(guò)沖和下沖的信號(hào)。

2023-04-03 10:40:07 887

887 設(shè)置 Input-to-Reg 時(shí)序路徑的約束時(shí),不僅需要?jiǎng)?chuàng)建時(shí)鐘模型,還需要設(shè)置輸入延時(shí) (input delay)。設(shè)置 input delay 時(shí),需要假設(shè)輸入 port 信號(hào)是與時(shí)鐘

2023-03-31 16:39:14 1044

1044

理論上講,快時(shí)鐘域的信號(hào)總會(huì)采集到慢時(shí)鐘域傳輸來(lái)的信號(hào),如果存在異步可能會(huì)導(dǎo)致出現(xiàn)時(shí)序問(wèn)題,所以需要進(jìn)行同步處理。此類同步處理相對(duì)簡(jiǎn)單,一般采用為延遲打拍法,或延遲采樣法。

2023-03-28 13:50:29 1386

1386

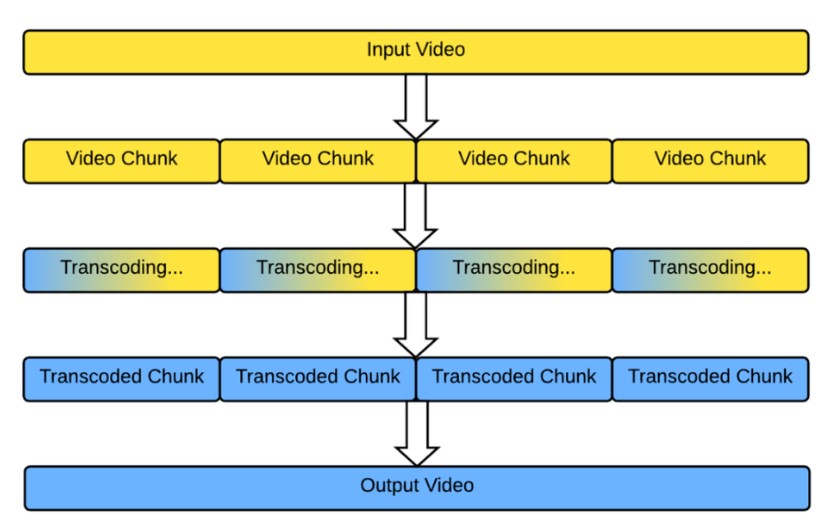

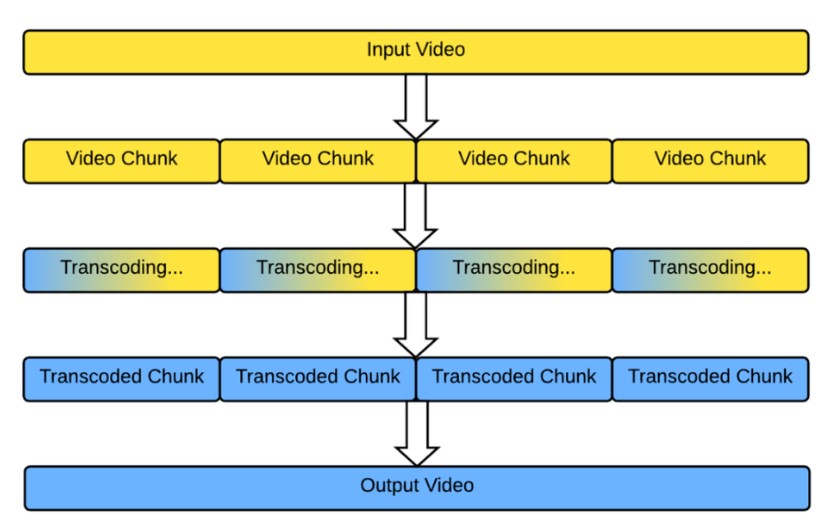

Vimeo發(fā)布新轉(zhuǎn)碼基礎(chǔ)設(shè)施Falkor——降低成本的同時(shí)將速度推向極限。

2023-03-28 10:55:30 445

445

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論