描述

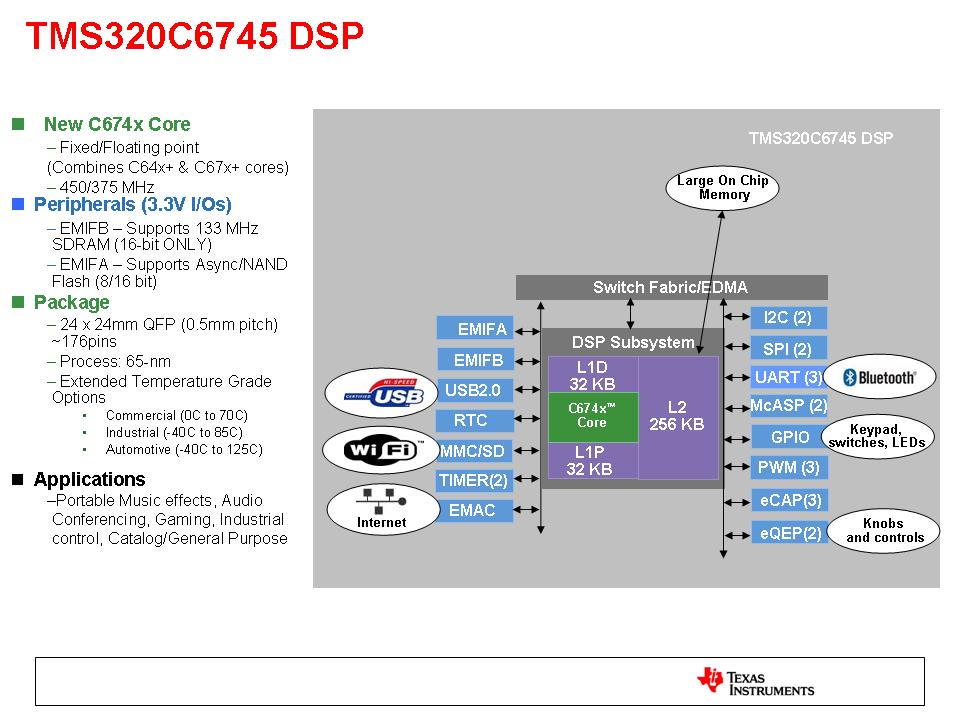

TMS320C6745 /6747器件是一款基于TMS320C674x DSP內核的低功耗數字信號處理器。它的功耗顯著低于TMS320C6000 DSP平臺的其他成員。

TMS320C6745 /6747器件使原始設備制造商(OEM)和原始設計制造商(ODM)能夠快速推出市場上的設備。高處理性能。

TMS320C6745 /6747 DSP內核采用基于緩存的兩級架構。 1級程序高速緩存(L1P)是32 KB直接映射高速緩存,1級數據高速緩存(L1D)是32 KB雙向組關聯高速緩存。 2級程序高速緩存(L2P)由256 KB內存空間組成,在程序和數據空間之間共享。 L2內存可以配置為映射內存,緩存或兩者的組合。雖然系統中的其他主機可以訪問DSP L2,但是其他主機可以使用額外的128KB RAM共享內存(僅限TMS320C6747),而不會影響DSP性能。

外設集包括:帶管理數據輸入/輸出(MDIO)模塊的10/100 Mbps以太網MAC(EMAC);兩個I 2 C總線接口; 3個多通道音頻串行端口(McASP),帶有16/9串行器和FIFO緩沖器;兩個64位通用定時器,每個都可配置(一個可配置為看門狗);可配置的16位主機端口接口(HPI)[僅限TMS320C6747];多達8個16引腳的通用輸入/輸出(GPIO),具有可編程中斷/事件生成模式,與其他外設復用; 3個UART接口(一個具有 RTS 和 CTS );三個增強型高分辨率脈沖寬度調制器(eHRPWM)外設;三個32位增強型捕獲(eCAP)模塊外設,可配置為3個捕獲輸入或3個輔助脈沖寬度調制器(APWM)輸出;兩個32位增強型正交編碼脈沖(eQEP)外設;和2個外部存儲器接口:用于較慢存儲器或外設的異步和SDRAM外部存儲器接口(EMIFA),以及用于SDRAM的高速存儲器接口(EMIFB)。

以太網媒體訪問控制器(EMAC)提供TMS320C6745 /6747器件與網絡之間的高效接口。 EMAC支持10Base-T和100Base-TX,或半雙工或全雙工模式下的10 Mbps和100 Mbps。此外,MDIO接口可用于PHY配置。

豐富的外設集可以控制外部外圍設備并與外部處理器通信。有關每個外圍設備的詳細信息,請參閱本文檔后面的相關章節以及相關的外圍設備參考指南。

特性

-

Software Support

-

TI DSP/BIOS

-

Chip Support Library and DSP Library

-

375- and 456-MHz TMS320C674x VLIW DSP

-

C674x Instruction Set Features

-

Superset of the C67x+ and C64x+ ISAs

-

Up to 3648 MIPS and 2736 MFLOPS C674x

-

Byte-Addressable (8-, 16-, 32-, and 64-Bit Data)

-

8-Bit Overflow Protection

-

Bit-Field Extract, Set, Clear

-

Normalization, Saturation, Bit-Counting

-

Compact 16-Bit Instructions

-

C674x Two-Level Cache Memory Architecture

-

32KB of L1P Program RAM/Cache

-

32KB of L1D Data RAM/Cache

-

256KB of L2 Unified Mapped RAM/Cache

-

Flexible RAM/Cache Partition (L1 and L2)

-

Enhanced Direct Memory Access Controller 3 (EDMA3):

-

2 Transfer Controllers

-

32 Independent DMA Channels

-

8 Quick DMA Channels

-

Programmable Transfer Burst Size

-

TMS320C674x Fixed- and Floating-Point VLIW DSP Core

-

Load-Store Architecture with Nonaligned Support

-

64 General-Purpose Registers (32-Bit)

-

Six ALU (32- and 40-Bit) Functional Units

-

Supports 32-Bit Integer, SP (IEEE Single Precision/32-Bit) and DP (IEEE Double Precision/64-Bit) Floating Point

-

Supports up to Four SP Additions Per Clock, Four DP Additions Every 2 Clocks

-

Supports up to Two Floating-Point (SP or DP) Reciprocal Approximation (RCPxP) and Square-Root Reciprocal Approximation (RSQRxP) Operations Per Cycle

-

Two Multiply Functional Units

-

Mixed-Precision IEEE Floating Point Multiply Supported up to:

-

2 SP x SP -> SP Per Clock

-

2 SP x SP -> DP Every Two Clocks

-

2 SP x DP -> DP Every Three Clocks

-

2 DP x DP -> DP Every Four Clocks

-

Fixed-Point Multiply Supports Two 32 x 32-Bit Multiplies, Four 16 x 16-Bit Multiplies, or Eight 8 x 8-Bit Multiplies per Clock Cycle, and Complex Multiples

-

Instruction Packing Reduces Code Size

-

All Instructions Conditional

-

Hardware Support for Modulo Loop

Operation

-

Protected Mode Operation

-

Exceptions Support for Error Detection and Program Redirection

-

128KB of RAM Shared Memory (TMS320C6747 Only)

-

3.3-V LVCMOS I/Os (Except for USB Interfaces)

-

Two External Memory Interfaces:

-

EMIFA

-

NOR (8- or 16-Bit-Wide Data)

-

NAND (8- or 16-Bit-Wide Data)

-

16-Bit SDRAM with 128-MB Address Space (TMS320C6747 Only)

-

EMIFB

-

32-Bit or 16-Bit SDRAM with 256-MB Address Space (TMS320C6747)

-

16-Bit SDRAM with 128-MB Address Space (TMS320C6745)

-

Three Configurable 16550-Type UART Modules:

-

UART0 with Modem Control Signals

-

Autoflow Control Signals (CTS, RTS) on UART0 Only

-

16-Byte FIFO

-

16x or 13x Oversampling Option

-

LCD Controller (TMS320C6747 Only)

-

Two Serial Peripheral Interfaces (SPIs) Each with One Chip Select

-

Multimedia Card (MMC)/Secure Digital (SD) Card Interface with Secure Data I/O (SDIO)

-

Two Master and Slave Inter-Integrated Circuit (I2C Bus™)

-

One Host-Port Interface (HPI) with 16-Bit-Wide Muxed Address/Data Bus for High Bandwidth (TMS320C6747 Only)

-

Programmable Real-Time Unit Subsystem (PRUSS)

-

Two Independent Programmable Realtime Unit (PRU) Cores

-

32-Bit Load and Store RISC Architecture

-

4KB of Instruction RAM per Core

-

512 Bytes of Data RAM per Core

-

PRUSS can be Disabled via Software to Save Power

-

Standard Power-Management Mechanism

-

Clock Gating

-

Entire Subsystem Under a Single PSC Clock Gating Domain

-

Dedicated Interrupt Controller

-

Dedicated Switched Central Resource

-

USB 1.1 OHCI (Host) with Integrated PHY (USB1) (TMS320C6747 Only)

-

USB 2.0 OTG Port with Integrated PHY (USB0)

-

USB 2.0 High- and Full-Speed Client (TMS320C6747)

-

USB 2.0 Full-Speed Client (TMS320C6745)

-

USB 2.0 High-, Full-, and Low-Speed Host (TMS320C6747)

-

USB 2.0 Full- and Low-Speed Host (TMS320C6745)

-

High-Speed Functionality Available on TMS320C6747 Device Only

-

End Point 0 (Control)

-

End Points 1,2,3,4 (Control, Bulk, Interrupt or ISOC) RX and TX

-

Three Multichannel Audio Serial Ports (McASPs):

-

TMS320C6747 Supports 3 McASPs

-

TMS320C6745 Supports 2 McASPs

-

Six Clock Zones and 28 Serial Data Pins

-

Supports TDM, I2S, and Similar Formats

-

DIT-Capable (McASP2)

-

FIFO Buffers for Transmit and Receive

-

10/100 Mbps Ethernet MAC (EMAC):

-

IEEE 802.3 Compliant (3.3-V I/O Only)

-

RMII Media-Independent Interface

-

Management Data I/O (MDIO) Module

-

Real-Time Clock with 32-kHz Oscillator and Separate Power Rail (TMS320C6747 Only)

-

One 64-Bit General-Purpose Timer (Configurable as Two 32-Bit Timers)

-

One 64-Bit General-Purpose Watchdog Timer (Configurable as Two 32-Bit General-Purpose Timers)

-

Three Enhanced Pulse Width Modulators (eHRPWMs):

-

Dedicated 16-Bit Time-Base Counter with Period and Frequency Control

-

6 Single Edge, 6 Dual Edge Symmetric, or 3 Dual Edge Asymmetric Outputs

-

Dead-Band Generation

-

PWM Chopping by High-Frequency Carrier

-

Trip Zone Input

-

Three 32-Bit Enhanced Capture (eCAP) Modules:

-

Configurable as 3 Capture Inputs or 3 Auxiliary Pulse Width Modulator (APWM) Outputs

-

Single-Shot Capture of up to Four Event Time-Stamps

-

Two 32-Bit Enhanced Quadrature Encoder Pulse (eQEP) Modules

-

TMS320C6747 Device:

-

256-Ball Pb-Free Plastic Ball Grid Array (PBGA) [ZKB Suffix], 1.0-mm Ball Pitch

-

TMS320C6745 Device:

-

176-pin PowerPAD Plastic Quad Flat Pack [PTP suffix], 0.5-mm Pin Pitch

-

Commercial, Industrial, Extended, or Automotive Temperature

參數 與其它產品相比 音頻處理器

|

|

|

DSP |

|

DSP MHz (Max) |

|

Arm CPU |

|

Operating Systems |

|

DRAM |

|

On-Chip L2 Cache/RAM |

|

Approx. Price (US$) |

|

McASP |

|

McBSP |

|

USB |

|

EMAC |

|

Package Group |

|

PCI/PCIe |

|

I2C |

|

UART (SCI) |

|

DSP MMACS |

|

Other Hardware Acceleration |

|

|

|

TMS320C6745 |

TMS320C6747 |

|

1 C674x |

1 C674x |

375

456 |

375

456 |

|

N/A |

|

|

TI RTOS |

SYS/BIOS |

|

SDRAM |

SDRAM |

|

256 KB |

256 KB |

|

10.17 | 1ku |

11.73 | 1ku |

|

2 |

3 |

|

0 |

0 |

|

1 |

2 |

|

10/100 |

10/100 |

|

HLQFP |

BGA |

|

N/A |

|

|

2 |

2 |

|

3 |

3 |

|

3648 |

|

|

PRU-ICSS |

|

|

|

|