完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

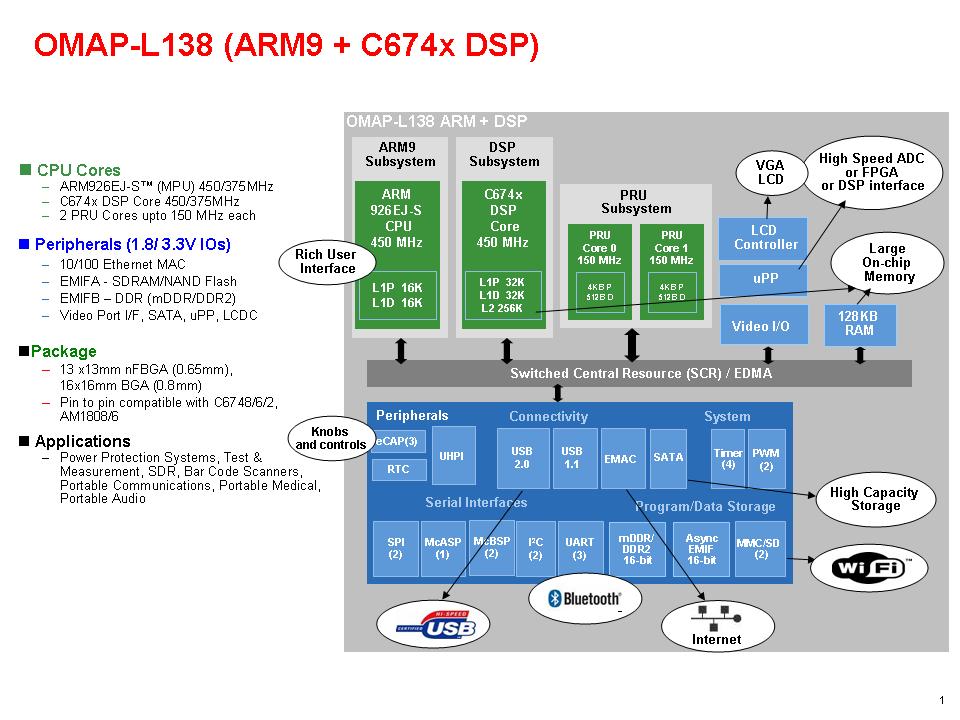

OMAP-L138 C6000 DSP+ARM 處理器 是一款低功耗 應用 處理器,該處理器基于 ARM926EJ-S 和 C674x DSP 內核。該處理器 與其他 TMS320C6000™ 平臺 DSP 相比,功耗要小很多。

憑借這款器件,原始設備制造商 (OEM) 和原始設計制造商 (ODM) 能夠充分利用全集成混合處理器解決方案的靈活性,迅速將兼具穩健操作系統、豐富用戶接口和高處理器性能的器件推向市場。

此器件采用雙內核架構(包括一個高性能的 TMS320C674x DSP 內核和一個 ARM926EJ-S 內核),實現了 DSP 與精簡指令集計算機 (RISC) 技術二者優勢的完美融合。

ARM926EJ-S 是一款 32 位 RISC 處理器內核,可執行 32 位或 16 位指令和處理 32 位、16 位或 8 位數據。該內核采用流水線結構,因此處理器和存儲器系統的所有部件能夠連續運行。

ARM9 內核配有協處理器 15 (CP15)、保護模塊以及具有頁表緩沖區的數據和程序存儲器管理單元 (MMU)。ARM9 內核配有獨立的 16KB 指令緩存和 16KB 數據緩存。這兩個緩存均與虛擬索引虛擬標簽 (VIVT) 4 路相連。ARM9 內核還配有 8KB 的 RAM(向量表)和 64KB 的 ROM。

該器件的 DSP 內核采用基于 2 級緩存的架構。第 1 級程序緩存 (L1P) 是一個 32KB 的直接映射緩存,第 1 級數據緩存 (L1D) 是一個 32KB 的 2 路組相連緩存。第 2 級程序緩存 (L2P) 包含 256KB 的存儲空間,由程序空間和數據空間共享。L2 存儲器可配置為映射存儲器、緩存或二者的組合。盡管 ARM9 和系統內的其他主機均可訪問 DSP L2,但還是額外提供了一個 128KB 的 RAM 共享存儲器給其他主機使用,從而避免對 DSP 性能產生影響。

對于支持安全功能的器件,TI 的基本安全啟動可為用戶保護自主知識產權并防止外部實體修改用戶開發的算法。該安全啟動流程從一個基于硬件的“信任根”開始,確保代碼從一個已知安全的位置開始執行。默認情況下會鎖定 JTAG 端口以防止仿真和調試攻擊;不過,在應用開發期間的安全啟動過程中可以使能 JTAG 端口。啟動模塊存儲在外部非易失性存儲器(例如,閃存或 EEPROM)中時處于加密狀態,在安全啟動期間被裝載時會進行解密和驗證。加密和解密程序會保護用戶 IP,使用戶能夠安全地設置系統并使器件采用已知可信任的代碼開始運行。

基本安全啟動使用 SHA-1 或 SHA-256 以及 AES-128 來驗證啟動映像。另外,基本安全啟動使用 AES-128 進行啟動映像加密。安全啟動流程采用多層加密機制,不但可以保護啟動過程,而且能夠安全地升級啟動和應用軟件代碼。該器件使用 1 個 128 位的器件專用密鑰來保護用戶密鑰,該 128 位密鑰由經過 NIST-800-22 認證的隨機數發生器生成,并且僅對該器件是已知的。當需要更新時,客戶可使用密鑰創建一個新的加密映像。之后,器件可通過外部接口(例如,以太網)來獲取該映像并覆蓋現有代碼。有關支持的安全 特性 或 TI 基本安全啟動的更多詳細信息,請參見《TMS320C674x/OMAP-L1x 理器安全用戶指南》。

外設集包括:1 個具有管理數據輸入/輸出模塊 (MDIO) 的 10Mbps/100Mbps 以太網介質訪問控制器 (EMAC);1 個 USB2.0 OTG 接口;1 個 USB1.1 OHCI 接口;2 個 I2C 總線接口;1 個具有 16 個串行器和 FIFO 緩沖器的多通道音頻串行端口 (McASP);2 個具有 FIFO 緩沖器的多通道緩沖串行端口 (McBSP);2 個支持多片選的串行外設接口 (SPI);1 個可配置的 16 位主機端口接口 (HPI);多達 9 組通用輸入/輸出 (GPIO) 引腳(每組包含 16 個引腳,每個引腳均支持可編程的中斷和事件生成模式,并且支持與其他外設復用);3 個 UART 接口(均支持 RTS 和 CTS);2 個增強型高分辨率脈寬調制器 (eHRPWM) 外設;3 個 32 位增強型捕捉 (eCAP) 模塊外設(可配置為 3 個捕捉輸入或 3 個 APWM 輸出);2 個外部存儲器接口(一個是用于慢速存儲器或外設的異步 SDRAM 外部存儲器接口 (EMIFA),另一個是高速 DDR2/移動 DDR 控制器)。

EMAC 為器件和網絡之間提供了一個高效接口。無論是在半雙工模式還是全雙工模式下,EMAC 都支持 10Base-T 和 100Base-TX 或者 10Mbps 和 100Mbps。此外,該器件還提供了一個針對 PHY 配置的 MDIO 接口。EMAC 支持 MII 和 RMII 接口。

串行 ATA (SATA) 控制器提供了一個連接至海量數據存儲器件的高速接口。SATA 控制器支持 SATA I (1.5Gbps) 和 SATA II (3.0Gbps)。

通用并行端口 (uPP) 提供了一個連接至多種類型的數據轉換器、FPGA 或其他并行器件的高速接口。uPP 的兩個通道均支持可編程的數據寬度,可編程范圍為 8 位至 16 位。另外,還支持單倍數據速率或雙倍數據速率傳輸以及 START、ENABLE 和 WAIT 信號,用以控制各類數據轉換器。

視頻端口接口 (VPIF) 提供了靈活的視頻 I/O 端口。

豐富的外設集提供了控制外設以及與外部處理器進行通信的功能。如需了解每個外設的詳細信息,請參見本文檔中的有關章節以及相關外設參考指南。

該器件配有一套完整的 ARM9 和 DSP 開發工具。這套工具包括 C 語言編譯器,用于簡化編程和調度過程的 DSP 匯編優化器以及用于查看源代碼執行的 Windows®調試器接口。

All trademarks are the property of their respective owners.

| Applications |

| Operating Systems |

| Arm CPU |

| Arm MHz (Max.) |

| DSP |

| DSP MHz (Max) |

| EMAC |

| Display Options |

| Video Port (Configurable) |

| DRAM |

| Operating Temperature Range (C) |

| USB |

| SPI |

| I2C |

| UART (SCI) |

| On-Chip L2 Cache/RAM |

| Other On-Chip Memory |

| SATA |

| Package Size: mm2:W x L (PKG) |

| OMAP-L138 | OMAP-L132 |

|---|---|

|

Communications and Telecom Consumer Electronics Energy Industrial Medical |

Communications and Telecom Consumer Electronics Energy Industrial Medical |

|

Linux SYS/BIOS |

Linux SYS/BIOS |

| 1 ARM9 | 1 ARM9 |

| 456 | 200 |

| 1 C674x | 1 C674x |

| 456 | 200 |

| 10/100 | 10/100 |

| 1 | 0 |

| 1 | 0 |

|

DDR2 LPDDR |

DDR2 LPDDR |

|

-40 to 105 -40 to 90 0 to 90 |

-40 to 105 0 to 90 |

| 2 | 1 |

| 2 | 2 |

| 2 | 2 |

| 3 | 3 |

| 256 KB (DSP) | 256 KB (DSP) |

| 128 KB | 128 KB |

| 1 | 0 |

|

361NFBGA: 169 mm2: 13 x 13(NFBGA) 361NFBGA: 256 mm2: 16 x 16(NFBGA) |

361NFBGA: 256 mm2: 16 x 16(NFBGA) |