優勢和特點

- 雙 DPLL 可同步 1 Hz 到 500 MHz 物理層時鐘,可在提供頻率轉換的同時去除噪聲基準電壓源的信號抖動

- 符合 ITU-T G.8262 和 Telcordia GR-253 標準

- 支持 Telcordia GR-1244、ITU-T G.812、G.813、G.823、G.824、G.825 和 G.8273.2

- 針對低至 50 ppb 的頻率偏移可進行持續頻率監控和基準電壓源驗證

- 兩個 DPLL 都配有帶有 24 位可編程模塊的 24 位小數分頻器

- 可編程數字環路濾波器帶寬:10-4 至 1850 Hz

- 兩個獨立的可編程輔助 NCO(1 Hz 至 65,535 Hz,分辨率 < 1.4 × 10?12 Hz),適合 PTP 應用中的 IEEE-1588 第 2 版伺服反饋

- 自動和手動保持和基準電壓源切換,實現零延遲、無中斷或相位增建

- 基于可編程優先級的基準電壓源切換,支持手動、自動可逆和自動不可逆模式

- 5 對時鐘輸出引腳,每對都可用作差分 LVDS/HCSL/CML 或者兩個單端輸出(1 Hz 至 500 MHz)

- 2 個差分或 4 個單端輸入基準電壓源

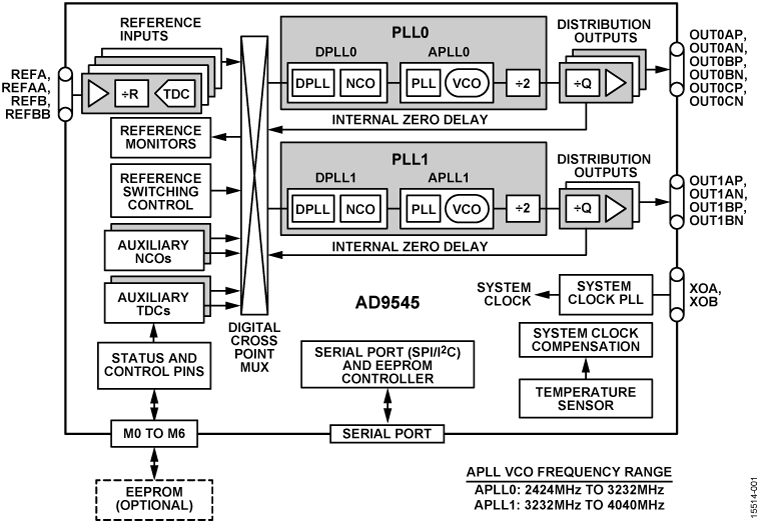

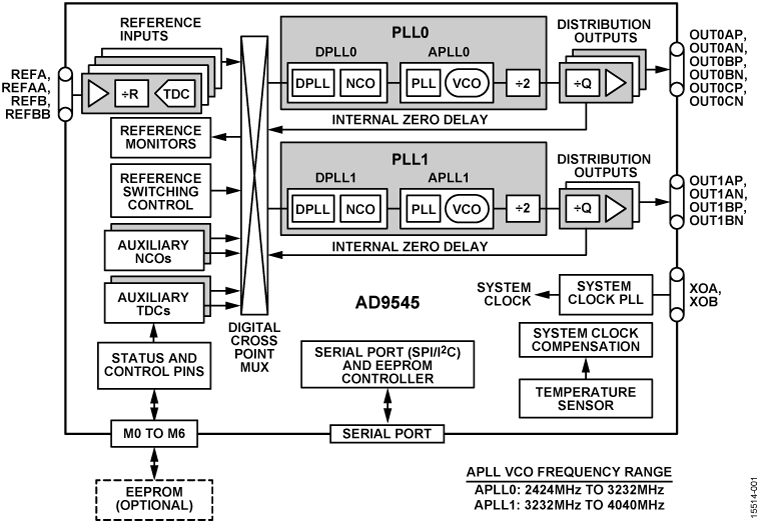

- 交叉點多路復用器將基準輸入與 PLL 互連

- 支持嵌入(模塊化)輸入/輸出時鐘信號

- 快速 DPLL 時鐘模式

- 支持 25 MHz 至 52 MHz 晶體諧振器、TCXO 或 OCXO 作為系統時鐘,提供系統時鐘頻率穩定性補償

- 自動初始化的外部 EEPROM 支持

- 1.8 V 單電源供電,帶有內部調節功能

- 內置溫度監控器/警報和溫度補償,可增強零延遲性能

產品詳情

AD9545 支持針對在服務提供商包交換網絡上提供頻率、相位和當日時間的現有和新興 ITU 標準。

將 AD9545 的 10 個時鐘輸出同步為多達四個輸入基準電壓源中的任意一個。數字鎖相環 (PLL) 可減少與外部基準電壓源相關的定時抖動。數字控制的環和保持電路即使在所有基準輸入失敗時仍可持續產生低抖動輸出信號。

AD9545 提供 48 引腳 LFCSP (7 mm × 7 mm) 封裝,可在 ?40°C 至 +85°C 的溫度范圍內工作。

應用

- GPS、PTP (IEEE-1588) 以及 SyncE 去除信號抖動和同步

- 光傳送網絡 (OTN)、SDH、運營商級以太網以及宏和小蜂窩基站。

- 帶有去除信號抖動功能的 OTN 映射/解映射

- 小基站時鐘,包括基帶和無線電

- Stratum 2、Stratum 3e 和 Stratum 3 保持、去除信號抖動和相位瞬態控制

- JESD204B 支持模數轉換器 (ADC) 和數模轉換器 (DAC) 時鐘

- 線纜基礎設施

- 運營商級以太網

方框圖