ADRF6603 1,100 MHz至3,200 MHz接收混頻器,集成小數(shù)N分頻PLL和VCO

數(shù)據(jù):

ADRF6603產(chǎn)品技術英文資料手冊

優(yōu)勢和特點

- 集成小數(shù)N分頻PLL的Rx混頻器

- RF輸入頻率范圍:1100 MHz至3200 MHz

- 內部LO頻率范圍:2100 MHz至2600 MHz

- 輸入P1dB:14.6 dBm

- 輸入IP3:27 dBm

- 通過外部引腳優(yōu)化輸入IP3

- SSB 噪聲系數(shù)

- IP3SET引腳開路:14.2 dB

- IP3SET引腳3.3 V:15.2 dB

- 電壓轉換增益:6.9 dB

- 200 Ω IF輸出匹配阻抗

- IF 3 dB 帶寬:500 MHz

- 可通過三線式SPI接口進行編程

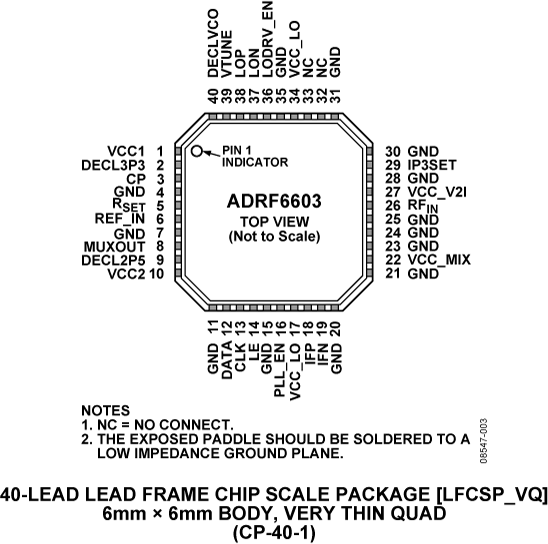

- 40引腳、6 mm × 6 mm LFCSP封裝

產(chǎn)品詳情

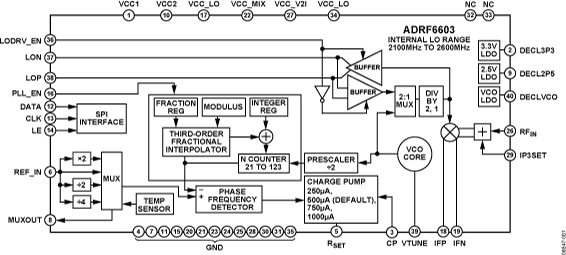

ADRF6603是一款高動態(tài)范圍有源混頻器,集成小數(shù)N分頻鎖相環(huán)(PLL)和壓控振蕩器(VCO),用于內部混頻器LO的產(chǎn)生。

ADRF6603與ADRF6602共同構成了一個集成PLL/混頻器系列,涵蓋2100 MHz至2600 MHz頻率范圍。

PLL基準輸入支持12 MHz至160 MHz范圍內的輸入頻率。PFD輸出控制一個電荷泵,其輸出驅動一個片外環(huán)路濾波器。

環(huán)路濾波器輸出再施加于一個集成式VCO。VCO輸出(2× fLO)施加于一個LO分頻器和一個可編程PLL分頻器。可編程PLL分頻器由一個Σ-Δ調制器(SDM)進行控制。SDM的模數(shù)可以在1至2047范圍內編程。

有源混頻器可將單端50 Ω RF輸入轉換為200 Ω差分IF輸出。IF輸出的工作頻率最高可達500 MHz。

ADRF6603采用先進的硅-鍺BiCMOS工藝制造,提供40引腳、裸露焊盤、6 mm × 6 mm、符合RoHS標準的LFCSP封裝,額定溫度范圍為?40°C至+85°C。

應用

方框圖