| DSP | 1 C674x |

| DSP MHz (Max) | 1000 |

| CPU | 32-/64-bit |

| Operating system | Android, DSP/BIOS, Linux |

| Ethernet MAC | 2x 10/100/1000 |

| PCIe | 1 |

| Rating | Catalog |

| Operating temperature range (C) | -40 to 105, 0 to 95 |

- 高性能 DaVinci? 視頻處理器

- ARM? Cortex-A8 RISC 處理器 高達 1.35GHz

- C674x 超長命令字 (VLIW) 數字信號處理器 (DSP)高達 1.125GHz高達 9000 每秒處理百萬條指令 (MIPS) 和 6750 每秒百萬個浮點運算 (MFLOPS)與 C67x+? 和 C64x+

- ARM Cortex?-A8 內核

- ARMv7 架構 順序、雙發射、超標量體系結構處理器內核 NEON 多介質架構

- 支持整數和浮點(符合 VFPv3-IEEE754 標準)Jazelle 運行時間編譯器目標 (RCT) 執行環境

- ARM? Cortex?-A8 存儲器架構

- 32K 字節指令和數據高速緩存

- 256K 字節 L2 高速緩存

- 64K 字節 RAM,48K 字節啟動 ROM

- TMS320C674x 浮點 VLIW DSP

- 64 個通用寄存器(32 位)

- 六個 ALU(32 位和 40 位)功能單元 支持 32 位整數,SP(IEEE 單精度,32位)和 DP(IEEE 雙精度,64位)浮點 每時鐘周期支持高達 4個單精度 (SP) 加法和每 2 個時鐘周期支持高達 4 個雙精度 (DP) 加法 每周期支持多達 2 個浮點(SP 或者 DP)近似倒數或者平方根運算

- 2 個乘法功能單元 混合精度 IEEE 浮點乘法支持高達: 每時鐘 2 SP x SP → SP 每 2 個時鐘 2 SP x SP → DP 每 3 個時鐘 2 SP x DP → DP 每 4 個時鐘 2 DP x DP → DP 定點乘法支持 2 個 32 x 32 位乘法,4 個包括復數乘法的 16 x 16 位乘法,或者 8 個 8 x 8 位乘法

- C674x 2 級存儲器架構

- 32K 字節一級程序 (L1P) 和一級數據 (L1D) RAM 和高速緩存

- 256K 字節 L2 統一映射 RAM 和高速緩存

- 系統內存管理單元(系統 MMU)

- 將 C674x DSP 和 EMDA 任務控制塊 (TCB) 內存存取映射到系統地址

- 512k 字節片上內存控制器 (OCMC) RAM

- 介質控制器

- 管理 HDVPSS 和 HDVICP2 模塊

- 多達 3 個可編程高清視頻圖像協處理 (HDVICP2) 引擎

- 編碼、解碼、轉碼操作

- H.264,MPEG2,VC1,MPEG4 SP 和 ASP

- SGX530 3D 圖形引擎(只在 DM8168 和 DM8166 器件上提供)

- 每秒提供多達 30 MTriangle

- 通用型可擴縮渲染引擎

- Direct3D 移動, OpenGL ES 1.1 和 2.0, OpenVG 1.1, OpenMax API 支持

- 高級幾何 DMA 驅動型操作

- 可編程 HQ 圖像抗混疊處理

- 字節序

- ARM,DSP指令和數據–小端序

- HD 視頻處理子系統 (HDVPSS)

- 2 個 165MHz HD 視頻捕捉通道 1 個 16 位或 24 位和 1 個 16 位通道 每個通道可被分成雙 8 位捕捉通道

- 2 個 165MHz HD 視頻顯示通道 一個 16 位,24 位,30 位 通道和一個 16 位通道

- 同步安全數碼卡 (SD) 和 HD 模擬輸出

- 具有物理層 (PHY)(具有高達 165MHz 像素時鐘的 HDCP)的數字高清數字多媒體接口 (HDMI) 1.3 發射器

- 三個圖形層

- 雙 32 位 DDR2 和 DDR3 SDRAM 接口

- 支持高達 DDR2-800 和 DR3-1600 的內存

- 總共最多 8 個 x8 器件

- 2GB 總地址空間

- 動態內存管理器 (DMM) 可編程多區域內存映射和交錯 實現了高效 2D 成組存取 支持 0°,90°,180°,或者 270° 取向的平鋪對象和鏡像 優化了交錯存取

- 1 個 PCI Express 具有集成 PHY 的 (PCIe?) 2.0 端口

- 具有 1 條或者 2 條 5.0GT/s 線道的單一端口

- 可配置為根聯合體或者端點

- 具有集成 PHY 的 穿行 ATA (SATA) 3.0 Gbps 控制器

- 至 2 個硬盤驅動的直接接口

- 來自多達 32 個入口的硬件輔助本機命令隊列 (NCQ)

- 支持端口乘法器和基于命令的交換

- 兩個 10Mbps,100Mbps 和 1000Mbps 以太網 MAC (EMAC)

- 與 IEEE 802.3 標準兼容(只適用于 3.3V IO)

- MII 和 GMII 媒介獨立接口

- 管理數據 IO (MDIO) 模塊

- 具有集成型 PHY 的雙 USB 2.0 端口

- USB 2.0 高度和全速客戶端

- USB 2.0 高速、全速和低速主機

- 支持端點 0-15

- 通用內存控制器 (GPMC)

- 8 位和 16 位復用地址和數據總線

- 多達 6 種芯片選擇(每個芯片選擇引腳具有高達 256M 字節的地址空間)

- 到 NOR 閃存、NAND 閃存(具有 BCH 和漢明錯誤碼檢測功能)、SRAM 和 偽 SRAM 的無縫接口

- 位于 GPMC 外部的錯誤定位器模塊 (ELM) 負責提供用于 NAND 的高達 16 位和 512 字節的硬件 ECC

- 針對到 FPAG,CPLD,ASIC 等接口的靈活異步協議控制

- 增強型直接內存存取 (EDMA)控制器

- 4 個傳輸控制器

- 64 個獨立的 DMA 通道和 8 個 QDMA 通道

- 7 個32 位通用定時器

- 1 個系統安全裝置定時器

- 3 個可配置的 UART,IrDA 和 CIR 模塊

- 具有調制解調器 (Modem) 控制信號的 UART0

- 支持高達 3.6864Mbps 的 UART

- SIR,MIR,FIR (4.0 MBAUD),和 CIR

- 1 個具有 4 種芯片選擇的 40MHz 串行外設接口 (SPI)

- SD 和 SDIO 串行接口(1 位和 4 位)

- 雙集成電路間(I2C 總線) 端口

- 3 個多通道音頻串口

- 一個六串化器發送和接收端口

- 2 個雙串化器發送和接收端口

- 針對 SDIF 和 PDIF 的 DIT 功能(所有端口)

- 多通道緩沖串行端口 (McBSP)

- 發送和接收時鐘高達 48MHz

- 2 個時鐘區和 2 個串行數據引腳

- 支持時分復用 (TDM),I2S,和相似格式

- 實時時鐘 (RTC)

- 一次或者周期性中斷生成

- 多達 64 個通用 IO (GPIO) 引腳

- 片上 ARM? ROM 引導加載程序 (RBL)

- 電源、復位、和時鐘管理

- SmartReflex 技術(二級)

- 7 個獨立內核電源域

- 針對子系統和外設的時鐘啟用和禁用控制

- 可兼容 IEEE-1149.1 (JTAG) 和 IEEE-1149.7 (cJTAG)

- 1031 引腳無鉛型 BGA 封裝 (CYG 后綴),0.65mm 焊球間距

- Via Channell? 技術使得能夠采用 0.8mm 設計規則

- 40nm CMOS 工藝技術

- 3.3V 單端 LVCMOS I/O(除了 1.5V 上的 DDR3,1.8V 上的 DDR2,1.8V 上的 DEV_CLKIN)

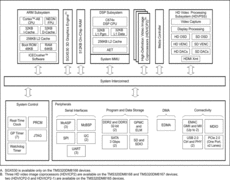

DM816x DaVinci? 視頻處理器是高度集成的、可編程平臺,它利用 TI 的DaVinci?技術來滿足下列應用的處理需求: 視頻編碼、解碼、轉碼和速率轉換、視頻安全、視頻會議、視頻基礎設施、媒體服務器、和數字標牌。

憑借全集成化混合處理器解決方案所具有的極大靈活性,該器件使得 OEM 和 ODM 制造商能夠將擁有穩健的操作系統支持、豐富的用戶界面以及高處理性能的設備迅速投放市場。 此器件將可編程視頻及音頻處理與1 個高度集成的外設集組合在一起。

該器件的關鍵之處在于多達 3 個高分辨率視頻和成像協處理器 (HDVICP2)。 每個協處理器能夠執行一個單個 1080p60 H.264 編碼或解碼、或者多個較低分辨率或幀速率的編碼和解碼。 另外,也可完成多通道 HD 至 HD 或 HD 至 SD 代碼轉換以及多重編碼。 憑借可同時處理 1080p60 數據流的能力,TMS320DM816x 器件成為了一款適合當今苛刻的 HD 視頻應用要求的強大解決方案。

可編程性由一個具有 NEON? 擴展的 ARM? Cortex? -A8 RISC CPU,TI C674x VLIW 浮點 DSP 內核,以及高分辨率視頻和成像協處理器提供。 ARM?使得開發人員能夠將控制功能與在 DSP 和協處理器上進行編程的音頻和視頻算法分離開來,從而降低了系統軟件的復雜程度。 支持 NEON? 浮點擴展的 ARM?Cortex?-A8 32 位 RISC 處理器包括:32K 字節 (KB) 指令高速緩存;32KB 數據高速緩存;256KB L2 高速緩存; 48KB 公共 ROM和 64KB RAM。

豐富的外設集提供了控制外圍設備以及與外部處理器進行通信的功能。 如需了解每個外設的詳細信息,請參見本文件中的有關章節以及相關聯的外設參考指南。 此外設集包括:HD 視頻處理子系統 (HDVPSS),此子系統提供同步 HD 和 SD 模擬視頻的輸出和雙 HD 視頻輸入;多達 2 個具有 GMII 和 MDIO 接口的千兆位以太網 MAC (10Mbps,100Mbps,1000 Mbps);2 個具有集成 2.0 PHY 的 USB 端口; PCIe 端口 x2 線道 GEN2 兼容型接口,它使得器件能夠充當一個 PCIe?根聯合體(root complex) 或設備端點;一個 6 通道 McASP 音頻串行端口(具有DIT 模式);兩個雙通道 McASP 音頻串行端口(具有DIT 模式);一個 McBSP 多通道緩沖串行端口;3 個可支持 IrDA 和 CIR 的 UART;SPI 串行接口;SD 和 SDIO 串行接口;兩個 I2C 主控和受控接口;多達 64 個通用 I/O (GPIO);7 個32 位定時器;系統安全裝置定時器;雙 DDR2 和 DDR3 SDRAM 接口;靈活的 8 位和 16 位異步存儲器接口;以及多達兩個用于兩個(或更多,通過采用一個端口乘法器來實現)磁盤驅動器上的外部存儲器的 SATA 接口。

此器件還包括一個 SGX530 3D 圖形引擎(只在 DM8168 和 DM8166 器件上提供)來實現精細復雜的用戶圖形接口 (GUI) 和富有吸引力的用戶接口和交互。 此外,它還有一個針對 包括 ARM 和 DSP 在內的完整開發工具集,這個工具集包括 C語言編譯器、一個用于簡化程序設計和調度的DSP 匯編優化器、 以及旨在將可視性引入源代碼執行的 Microsoft WIndows 調試程序界面。

C674x DSP 內核是 TMS320C6000 DSP 平臺上的高性能浮點 DSP 系列產品。 C674x 浮點 DSP 處理器采用 32KB 的 L1 程序內存和 32KB 的 L1 數據內存。 多達 32KB 的 L1P 可被配置為程序高速緩存。 剩余的是不可高速緩存的無等待狀態程序內存。 多達 32KB 的 L1D 可被配置為數據高速緩存。 剩余的是不可高速緩存的無等待狀態數據內存。 DSP 具有 256KB 的 L2 RAM,它可被規定為 SRAM、L2 高速緩存或此二者的某種組合。 所有的 C674x L3 及片外存儲器訪問均通過一個系統 MMU 來選定路由。

該器件的封裝采用 Via Channel? 技術進行了特別設計。 此項技術允許在這種 0.65mm 焊球間距封裝中使用 0.8mm 間距的 PCB 特征尺寸,并大幅度地降低了 PCB 的成本。 由于 Via Channel? BGA 技術的分層效率有所提升,因而還允許只在兩個信號層中進行 PCB 布線。