FPGA 如何進行浮點運算

2015-09-26 09:31:37

請問:

FPGA可以用來做數字電源嗎?有參考設計案例嗎?

FPGA和DSP做數字電源的優缺點是什么?

2024-01-08 22:24:13

技術完成對單個設計的測試,可以提高晶圓良率,大幅降低總成本,且無需額外的客戶工程設計工作或再認證。 EasyPath-6 FPGA提供世界級的故障覆蓋率,幾乎達100%,并且客戶在生產過程中可以在

2012-08-11 18:17:16

通常無法在一個時鐘周期內完成。因此FPGA實現除法運算并不是一個“/”號可以解決的。 好在此類基本運算均有免費的IP核使用,本人使用的VIVADO 2016.4開發環境提供的divider gen

2018-08-13 09:27:32

的FPGA,始終引領先進的工藝。 fpga的優勢 1)通信高速接口設計。FPGA可以用來做高速信號處理,一般如果AD采樣率高,數據速率高,這時就需要FPGA對數據進行處理,比如對數據進行抽取濾波

2020-10-26 14:35:32

)如何減少這些挑戰的影響,同時仍然提供系統電源集成的好處。FPGA因其可重編程性而廣受歡迎:設計人員可以為許多不同的應用配置相同的FPGA,并且FPGA允許在設計周期的后期進行設計更改 - 即使在產品發布

2018-07-24 17:27:53

=-*/在fpga中占用資源太大,怎么通過位運算實現這些,謝謝

2013-07-14 20:36:48

的 pyOCD 目標。

1. NXP 是否提供 pyOCD 支持?

2.我們可以為pyOCD創建支持文件嗎?

3. Zephyr 或社區是否提供對 pyOCD 的腳本支持?

2023-05-08 07:09:34

浮點型變量可以存儲實數字符型變量可以存儲單個字符,其值是該字符的ASCII 碼算術運算符提供運算功能,包括+、-、*、/、%、++、--printf() 和 scanf() 函數屬于格式輸入輸出函數getchar() 和 putchar() 函數用來輸入輸出單個字符的函數

2010-06-20 16:40:42

使用XINTF總線進行通訊進行數據傳輸,DSP,FPGAIO全部引出 這樣就可以很容易的將主控板融入到嵌入式系統中,需要什么外設可以直接裝在主控板上,可以用來控制電機,可以用來做數據采集系統。將外部

2016-07-18 16:59:22

了很多問題,從原理圖設計,方案驗證,制板,焊接,調試解決了很多為題,收貨還是蠻多的,DSP28335和FPGA使用XINTF總線進行通訊進行數據傳輸,DSP,FPGAIO全部引出 這樣就可以很容易的將

2016-07-18 16:53:28

了很多問題,從原理圖設計,方案驗證,制板,焊接,調試解決了很多為題,收貨還是蠻多的,DSP28335和FPGA使用XINTF總線進行通訊進行數據傳輸,DSP,FPGAIO全部引出 這樣就可以很容易的將

2016-07-18 17:13:01

可以用來控制電機,可以用來做數采系統。最小系統圖,將外部接口全部印出來,自己可以隨便做計,電機控制,數據采集,串口,can,485,AD,應有盡有設。DSP28335+FPGA外掛AD760616位

2016-07-16 14:32:23

SPICE雖然最初是用來做IC設計,但是由于低成本運算以及穩定設計的推動,越來越多的電路和系統設計人員已經意識到了模擬電路仿真的優點。但是SPICE可以用來驗證電路設計以預測電路功能嗎?

2021-04-07 06:34:07

SPWM調制載波可以為方波嗎?為什么bbs.21dianyuan.com/23402.html#buttom中的載波可為方波

2013-05-21 20:33:11

你好呀,我正在查看 STM32G031Kxxx(32 引腳 LQFP),想知道是否可以為該 μC 提供外部高速時鐘源?數據表顯示此封裝中 OSC32_IN 和 OUT 可用,但對于 HSE,只有 OSC_IN。因此,不能使用晶體,但應該可以使用外部時鐘——如果需要的話。我的假設對嗎?

2022-12-01 07:15:25

的邏輯運算符如表 2-6 所示。2.關系運算符關系運算符兩邊必須為相同的類型,其結果為 boolean 類型。等號(=)和不等號(/=)兩邊可以為任意類型的運算對象。其他關系運算符的運算對象必須為標量類型

2018-09-12 09:51:50

立即學習>>夢翼師兄FPGA培訓(視頻加板卡),手把手帶你入門FPGA寫在前面的話移位運算符是雙目運算符,將運算符左邊的操作數左移或右移指定的位數,用0來補充空閑位。如果右邊操作數的值

2019-12-17 10:45:17

“,”隔開。位拼運算符是夢翼師兄特別喜歡的一種運算符,它聰慧靈秀,不但可以進行簡單的數據拼接,更是可以用來執行移位操作,而且數據永遠是循環的,不會丟失,用途非常廣泛。代碼實例[table][tr][td

2019-12-19 09:38:25

為什么FPGA可以用來實現組合邏輯電路和時序邏輯電路呢?

2023-04-23 11:53:26

處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。但多數FPGA不支持浮點運算,這使FPGA在數值計算、數據分析和信號

2019-07-05 06:21:42

少需要這些功能。串行實現千赫級音頻算法使用的資源與三位數兆赫級信號處理所需完全相同。因此,像PLD和FPGA這類可編程邏輯元件很少用來處理低頻信號。畢竟與基于傳統DSP的實現相比,在硬件中并行處理數學運算

2011-03-06 19:15:48

的提升。運算速度或者數據路徑寬度都可以進一步提高,另外,時序操作可以在結構上增加一些并行度。這些措施中,每一種都可以提高一定的性能。在利用了目標FPGA器件靈活性的結構中實現算法,會獲得比較大的好處

2021-12-15 06:30:00

與閉運算:形態學開運算就是先對圖像進行腐蝕然后在膨脹,表達式即:形態學閉運算就是先對圖像進行膨脹然后在腐蝕,表達式即:圖1 開運算和閉運算演示(原圖由美國國家標準和技術研究所提供)如圖1所示,a為

2018-08-10 09:12:22

基于FPGA的實時互相關運算器對無源雷達的直通信號和反射信號進行互相關運算可以檢測目標是否存在。本文介紹了基于FPGA流水線操作的陣列運算器,該運算器有32個并行乘加運算單元時分,完成256個探測

2009-09-19 09:25:42

Sobel就完事了。希望讀者能自己去做去調試搞定。腐蝕算法腐蝕是一種消除邊界點,使邊界向內部收縮的過程。可以用來消除小且無意義的物體。用3X3的結構元素,掃描圖像的每一個像素,用結構元素與其覆蓋的二值

2017-09-22 13:20:55

。有時候,只需要用四層電路板上的一個電源層和一個地層,就可以解決大多數電源完整性問題。除了電源層以外,還可以為每只IC去耦,以解決設計中繁瑣的電源問題。不過,現在的PCB空間(還有成本與你的日程)都很緊...

2021-12-28 08:08:01

數組下標可以為負數嗎

2023-09-26 06:45:57

是否可以為 STM32WL 系列提供 SVD 文件?當芯片廣泛可用時,能夠已經準備好一些工作將非常有用。

2023-01-31 08:00:06

是否可以為Virtex系列(XCV400)提供無鉛部件?什么是Leadfree部件號,如果有的話?

2020-05-29 13:00:33

啟動模式。關于設備編程和啟動模式的正確配置,我有幾個問題:1) 任何 UART 端口都可以用于編程,還是只能使用 UART0 (U0RXD/U0TXD)?意思是,是否可以為板載主控MCU和板外提供單獨

2023-03-01 08:22:46

請問一下有什么方法可以為WiMAX應用提供上變頻轉換嗎?

2021-04-23 06:34:51

中提供的簡單接口所取代。此外,整個控制電路的尺寸也會顯著減小。有幾種方法可以為三相逆變器應用生成RPWM。此應用筆記中,我們介紹了一種合適的RPWM技術,它可以使用現成的GreenPAK CMIC資源來

2020-12-18 06:16:17

濾波器的尺寸,或完全避免在某些應用中使用濾波器。那么有哪些方法可以為三相逆變器應用生成RPWM?能否進行介紹

2019-09-10 09:22:51

有沒有人知道FPGA一般在哪買?預算在四萬左右,主要用來做控制算法的,要求運算速度得快。請各位高手指點一下,最好能給賣的公司的網址。謝謝!!

2015-11-11 13:19:33

電導可以為負數嗎?如果可以是需要專門的設計,還是說會有某種特殊的材料可以造成此電阻內有些地方為負的,有些地方不是負的,還有就是此類應用一般用在什么地方?

2013-03-02 15:33:33

盤古PGX-Mini 4K開發板,目前來說是一款性價比比較高的開發板,他用來入門FPGA怎么樣?

2024-03-16 07:17:45

注意蔡勒公式的結果是可以為負數的,如-1代表周6,-2代表周五,很多實現忽略了這點,出現錯誤。int gettheweek(int year,int month,int day){ int week

2021-07-14 06:09:40

FPGA如何實現32位減法運算

2019-02-28 04:59:09

運算放大器一般是用來做反向放大用嗎?除了做這個放大之外,它做加法與減法、積分運算的場合多不多?

2019-05-16 06:08:44

請問怎樣去實現一種基于FPGA的矩陣運算?

2021-06-22 07:00:19

你好,我目前正在設計一個LVDS接收器和DAC ASIC。DAC是12位。我需要使用來自FPGA / Eval板的LVDS信號進行測試。任何人都可以推薦Xilinx的評估板或FPGA,我可以使用它來測試我的ASIC嗎?謝謝。問候,尼基爾

2019-08-28 07:03:41

我正在開發一個涉及I2C(使用Spartan 3E FPGA)與EEPROM通信的項目。我對如何開始感到很困惑。有人可以為I2C主模式建議vhdl代碼嗎?我非常感謝你的幫助。謝謝以上來自于谷歌翻譯

2019-06-13 09:50:43

自動白平衡的FPGA實現采用FPGA對自動白平衡進行運算有什么優點?

2021-04-13 06:20:46

本文采用ALTERA 公司FPGA 作為算法處理器件,實現了互相關算法,取得了很好的效果。本文根據相關算法的運算原理并考慮了模塊與外部的交互性,在FPGA 中配置設計了互相關運算模塊

2009-09-01 09:48:25 13

13 本文采用ALTERA公司FPGA作為算法處理器件,實現了互相關算法,取得了很好的效果。本文根據相關算法的運算原理并考慮了模塊與外部的交互性,在FPGA中配置設計了互相關運算模塊、并串

2010-07-21 09:35:40 19

19 高精度的乘除法和開方等數學運算在FPGA實現中往往要消耗大量專用乘法器和邏輯資源。在資源敏感而計算時延要求較低的應用中,以處理時間換取資源的串行運算方法具有廣泛的應

2010-07-28 18:05:14 37

37 MP3不僅是用來聽的,也可以用來玩的

以VX系列MP3為例,將固件及其升級所帶來的好處做一些案例性的介紹,可以將MP3與手機的使用做

2010-02-02 11:42:15 615

615 提出一種基2FFT的FPGA方法,完成了基于FPGA高精度浮點運算器的FFT的設計。利用VHDL語言描述了蝶形運算過程及地址產生單元,其仿真波形基本能正確的表示輸出結果。

2011-12-23 14:24:08 46

46 基于FPGA的開方運算實現 ,的技術論文

2015-10-30 10:59:01 5

5 這是一個基于FPGA設計的四則運算簡易計算器。可以實現定點小數運算和負數運算。

2016-08-23 16:23:32 30

30 結構復雜,采用DSP實現會增加系統負擔,降低系統速度。在某些對速度要求較高的情況,必須采用專門的浮點運算處理器。 EDA/FPGA技術不斷發展,其高速、應用靈活、低成本的優點使其廣泛應用數字信號處理領域。在FPCA技術應用的初期,

2018-04-10 14:25:53 17

17 ,且通常無法在一個時鐘周期內完成。因此FPGA實現除法運算并不是一個“/”號可以解決的。 好在此類基本運算均有免費的IP核使用,本人使用的VIVADO 2016.4開發環境提供的divider gen IP核均采用AXI總線接口,已經不再支持native接口。

2018-05-18 01:15:00 4150

4150 關鍵詞:USB , 充電 , 墻插板 如果你想重新裝修,并且向購入比普通墻插板更貴的插座,那么你就應該選擇這款RCA USB墻插板。 有了它,你可以為三款設備充電,這款墻插板提供兩個USB接口

2018-12-25 20:45:01 238

238 TEEX 測試網是 TEEX 推出的測試版本,實現了 TEEX 系統的基礎架構和主體功能,為早期開發者和用戶提供了一個可用的測試環境。測試網搭載了真實的可信執行環境,開發者和用戶可以在測試網中部署和使用真實的安全服務 (Secure Service)。

2019-02-18 09:31:21 1399

1399

本文檔的主要內容詳細介紹的是使用FPGA實現三輸入的多數判決器的實驗詳細資料說明。

2019-04-28 08:00:00 2

2 多數表決器常見于信號處理。例如,在自動控制中,對三個針對同一事物的信號使用多數表決器進行運算,并按照其中兩個一致的結果執行。這樣既可以提高信號的可靠性(信號不止一個),又避免信號源錯誤(出錯的信號在表決中被排除)造成不必要的損失。

2019-12-04 07:02:00 2675

2675

Chainlink是全球首個可以為智能合約提供鏈外數據的分布式預言機,可訪問任何外部API,可以對市場、熱度、進度表或任何其他公共數據的變化做出自動響應,通過與aelf的攜手,Chainlink將確保aelf區塊鏈系統內所有輸入輸出數據的安全性和可靠性,并加強在區塊鏈落地應用時的數據安全性鏈接。

2019-09-11 10:51:26 518

518 云計算確實無處不在,各種供應商都為越來越多的客戶提供云計算解決方案。

2019-09-25 14:26:25 2847

2847 在萊迪思看來,隨著智能功能從云端引入到網絡邊緣領域,移動FPGA對多個市場都產生了影響。

2019-12-12 15:33:54 407

407 為了進一步營造一個連網的患者和護理人員社區,支持物聯網的智能藥丸和膠囊以及移動應用可以提供劑量和評估提醒,還可以訪問“操作指南”視頻、綜合日記和調查模塊。

2020-03-09 15:12:55 492

492 當今汽車行業最受關注的話題之一是先進的駕駛輔助系統(ADAS),該系統可以多種方式幫助駕駛員處理潛在問題。它們可以為駕駛員提供視覺和聽覺警告,也可以控制制動器、加速器和轉向裝置,使汽車遠離危險。

2020-05-09 08:00:00 1

1 開方運算作為數字信號處理(DSP)領域內的一種基本運算,其基于現場可編程門列(FPGA)的工程實現具有較高的難度。本文分析比較了實現開方運算的牛頓-萊福森算法,逐次逼近算法,非冗余開方算法3種算法

2020-08-06 17:58:15 6

6 我們知道,FPGA的頻率一般只有幾百MHz,而CPU的頻率卻高達數GHz。那么,有不少網友心中就有一個疑問:為什么FPGA主頻比CPU慢,但卻可以用來幫CPU做加速?。 今天,EDN就和大家

2020-11-20 09:56:16 3582

3582 Google提供了許多應用程序,可以為日常問題提供解決方案。它具有基本的辦公,電信和娛樂應用程序,并會不時為其提供新聞。這次,該輪到Google Photos接收新聞了,這是該公司的圖像存儲和管理應用程序。

2020-12-16 14:56:27 1352

1352 的,一種解決辦法就是采用定標。 數的定標就是將要運算的浮點數擴大很多倍,然后取整,再用這個數進行運算,運算得到的結果再縮小相應的倍數就可以了。在設計中,一定不要忘記小數點。在FPGA 中是體現不出來小數點的,小數點的位置只有程序員知道。

2021-08-12 09:53:39 4504

4504 FPGA中的硬件邏輯與軟件程序的區別,相信大家在做除法運算時會有深入體會。若其中一個操作數為常數,可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運算會占用較多的資源,電路結構復雜,且通常無法在一個時鐘周期內完成。因此FPGA實現除法運算并不是一個“/”號可以解決的。

2022-04-27 09:16:03 6098

6098 FPGA 在采用先進數字波束形成技術的雷達系統中提供了優于 CPU 和 GPU 選項的巨大優勢,因為它們可以降低成本、復雜性、功耗和上市時間。由于其在自適應波束成形應用中處理高度并行浮點運算的卓越能力,FPGA 可以提高算法性能,同時顯著降低功耗。

2022-06-14 09:19:13 1082

1082 這本書研究了加速EDA算法的硬件平臺,如ASIC,FPGA和GPU。覆蓋范圍包括討論在何種條件下使用一個平臺優于另一個平臺,例如,當EDA問題具有高度的數據并行性時,GPU通常是首選平臺,而當問題具有更多的控制因素時,FPGA可能是首選的。

2022-09-02 11:51:15 568

568 隨著 機器學習 (Machine Learning)領域越來越多地使用現場可 編程 門陣列( FPGA )來進行推理(inference)加速,而傳統FPGA只支持定點運算的瓶頸越發凸顯

2023-03-11 13:05:07 351

351 虛擬數字人是指利用人工智能技術和計算機圖形學生成的高度逼真的虛擬人形象,它可以模擬人類的語言、情感、行為和外貌,從而成為一種強大的營銷工具,可以為企業帶來多種商業價值。 廣州華銳互動作為一家15

2023-04-19 14:48:39 998

998 由于FPGA可以對算法進行并行化,所以FPGA 非常適合在可編程邏輯中實現數學運算。

2023-05-15 11:29:15 2057

2057

本文是本系列的第三篇,本文主要介紹FPGA常用運算模塊-乘加器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:17:12 888

888

本文是本系列的第四篇,本文主要介紹FPGA常用運算模塊-除法器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:20:45 1840

1840

本文是本系列的第五篇,本文主要介紹FPGA常用運算模塊-復數乘法器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:23:28 1204

1204

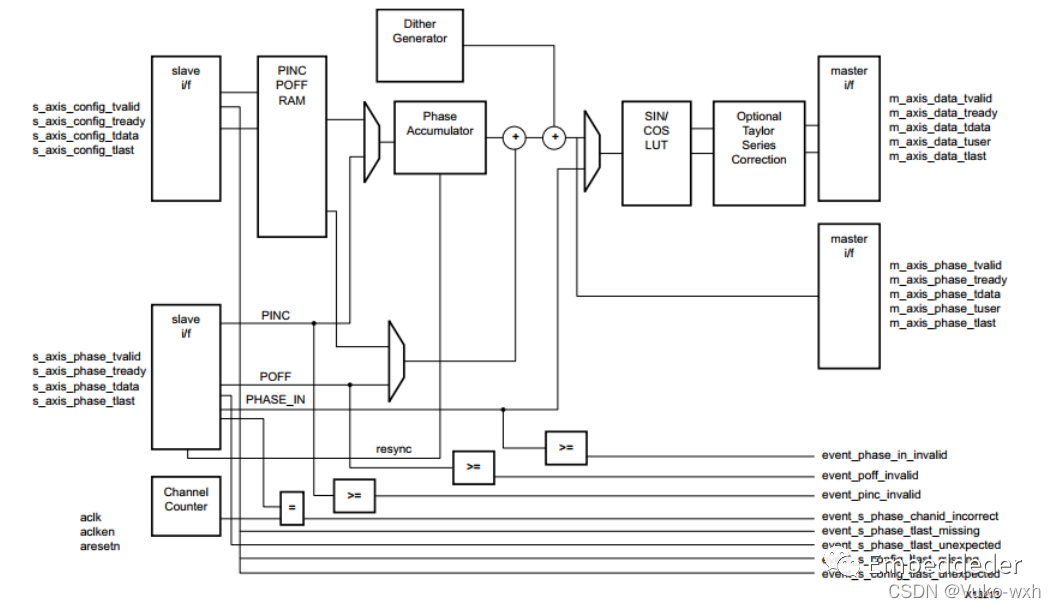

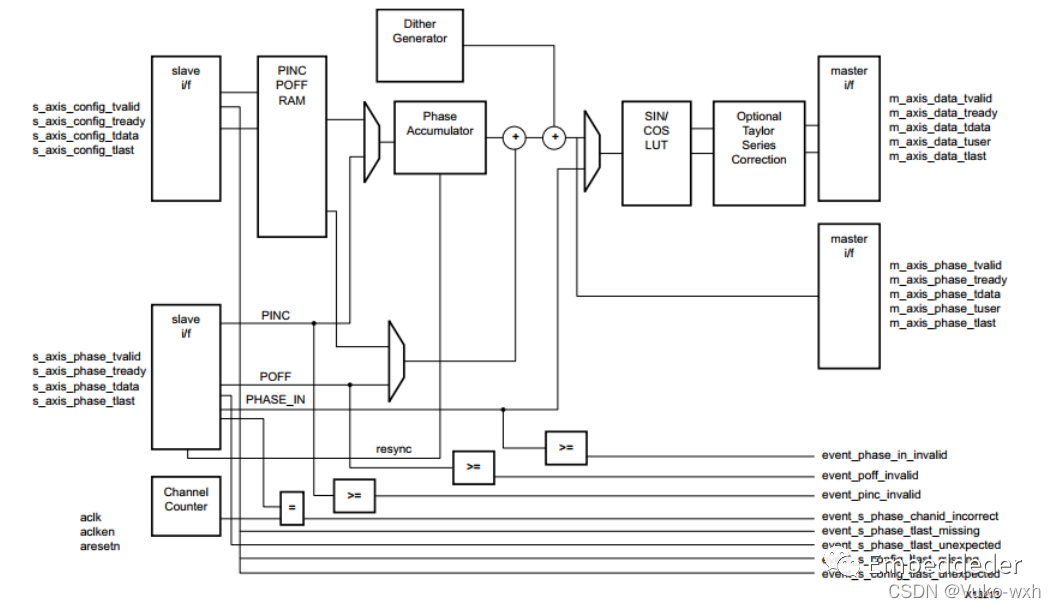

本文是本系列的第六篇,本文主要介紹FPGA常用運算模塊-DDS信號發生器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-24 10:37:18 3733

3733

點擊上方 藍字 關注我們 一、前言 FPGA以擅長高速并行數據處理而聞名,從有線/無線通信到圖像處理中各種DSP算法,再到現今火爆的AI應用,都離不開卷積、濾波、變換等基本的數學運算。但由于FPGA

2023-07-19 14:25:02 794

794

,通過集中式的控制器來管理和配置局域網設備,從而實現更靈活、智能和高效的局域網連接。

而SDWAN在跨境電商方面有許多有益的應用,可以為跨境電商提供以下幾方面的支持和優勢:

2023-08-01 12:03:09 368

368 FPGA實現加法和減法運算非常簡單,實現乘法和除法可以用IP,那實現對數和指數運算該用什么呢?

2023-08-05 09:37:05 810

810

不友好. 二、FPGA中的加減乘除 1.硬件資源 Xilinx 7系列的FPGA中有DSP Slice ,叫做“DSP48E1”這一專用硬件資源,這是一個功能強大的計算單元,單就用于基本運算的部分有加減單元和乘法器。詳見參考文獻1. 因此可以直接用HDL語言中的加、減、乘符號實現變

2023-09-05 11:45:02 267

267 ,浮點加法器是現代信號處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。 但多數FPGA不支持浮點運算,這使FPGA在數值計算、數據分析和信號處理等方

2023-09-22 10:40:03 394

394

電子發燒友App

電子發燒友App

評論