0 引言

目前已經(jīng)有多種成熟的數(shù)據(jù)采集系統(tǒng),主要用于工業(yè)生產(chǎn)、環(huán)境監(jiān)測(cè)、航空航天和科學(xué)研究領(lǐng)域中。大部分實(shí)時(shí)數(shù)據(jù)采集系統(tǒng)選用DSP(Digital Signal Processing)控制器和微控制器作為控制核心,比較容易實(shí)現(xiàn)復(fù)雜的算法[1],但是它們受到信息吞吐量和帶寬的限制,不能實(shí)現(xiàn)并行化處理,在高速大批量數(shù)據(jù)采集時(shí)有些乏力。而有極強(qiáng)并行處理數(shù)據(jù)能力的現(xiàn)場(chǎng)可編程門陣列器件(Field Programmable Gate Array,FPGA)備受青睞,以FPGA為控制核心的數(shù)據(jù)采集系統(tǒng)也日漸興盛。FPGA具有靈活性高、可擴(kuò)展性強(qiáng)和資源豐富的特點(diǎn)[2-3],而且能夠應(yīng)對(duì)各種形式的接口協(xié)議,使其在數(shù)據(jù)采集系統(tǒng)中得到廣泛應(yīng)用。有些FPGA是反熔絲的,可靠性能和穩(wěn)定性能非常高,這類FPGA在特定宇航應(yīng)用中是必選項(xiàng)。

地球臨近空間低溫、低壓、高輻射,環(huán)境極端惡劣,數(shù)據(jù)采集系統(tǒng)的傳感器和控制部件很容易受到影響而工作異常,甚至出現(xiàn)系統(tǒng)崩潰的現(xiàn)象。此環(huán)境下設(shè)計(jì)數(shù)據(jù)采集系統(tǒng)需要考慮穩(wěn)定性。FPGA能夠?qū)崿F(xiàn)復(fù)雜電路,能減小電路板上因布線產(chǎn)生的電磁干擾。與DSP控制器和其他CPU微控制器相比,F(xiàn)PGA生成硬件電路的特性更具有抗干擾性。前人進(jìn)行可靠性處理的方法有冗余結(jié)構(gòu)設(shè)計(jì)和配置存儲(chǔ)器的回讀校驗(yàn)與重配置[4]。同時(shí)數(shù)據(jù)采集系統(tǒng)可靠性也有合理的評(píng)估指標(biāo),例如運(yùn)行環(huán)境、系統(tǒng)集成、人機(jī)耦合、方案成熟性及安全性[5]。

需設(shè)計(jì)一個(gè)數(shù)據(jù)采集系統(tǒng),使其運(yùn)行在臨空的特定環(huán)境下,不僅實(shí)現(xiàn)數(shù)據(jù)采集任務(wù),還需要實(shí)時(shí)將數(shù)據(jù)傳回地面,并能完成部分控制功能。從運(yùn)行成本和環(huán)境考慮,需提高系統(tǒng)的可靠性和穩(wěn)定性。從硬件和軟件兩方面入手進(jìn)行設(shè)計(jì),在硬件方面,F(xiàn)PGA抗干擾性能強(qiáng),所以選取FPGA作為本系統(tǒng)的主控制器。采用冗余策略,設(shè)計(jì)兩路連接主控制器的傳感器電路,使得數(shù)據(jù)采集系統(tǒng)可靠性提高。對(duì)軟件部分,進(jìn)行模塊化編程,利用有限狀態(tài)機(jī)和看門狗策略來提高系統(tǒng)穩(wěn)健性。

1 系統(tǒng)硬件設(shè)計(jì)

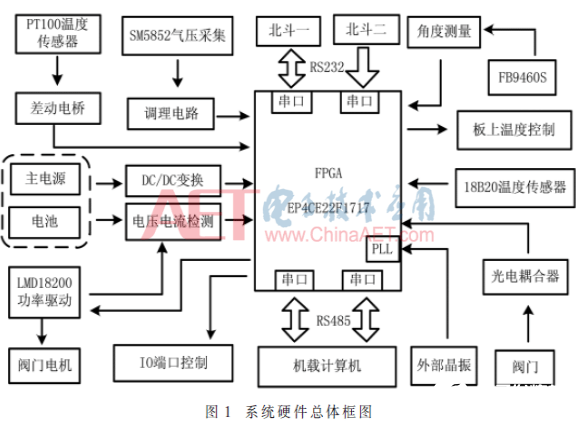

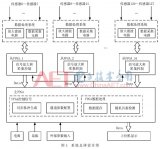

臨空數(shù)據(jù)采集系統(tǒng)主要包括了以FPGA為控制器的最小系統(tǒng)模塊、傳感器模塊、UART串口通信模塊和控制模塊。如圖1所示,最小系統(tǒng)是維持FPGA控制器正常運(yùn)行的外圍電路;傳感器模塊涉及溫度、角度、電流電壓等信號(hào)的采集與調(diào)理,因?yàn)橛布娜哂啵盘?hào)被分為主板信號(hào)和從板信號(hào);UART串口通信模塊包括2個(gè)RS232串口(與北斗模塊相連)、2個(gè)RS422串口(與臨空機(jī)載計(jì)算機(jī)連接);控制模塊主要包括閥門控制模塊和溫度控制模塊,溫度控制模塊用于控制加熱電阻,來維持電路板上的元器件正常運(yùn)行。

1.1 最小系統(tǒng)模塊

本設(shè)計(jì)選用Altera公司的Cyclone IV E系列的EP4CE22F1717作為采集系統(tǒng)的控制器。它有22 320個(gè)邏輯單元、154個(gè)用戶輸出輸出口、132個(gè)乘法器、4個(gè)PLL(“Phase Locked Loop”鎖相環(huán))。芯片的外部提供晶振頻率為50 MHz。

1.2 溫度采集模塊

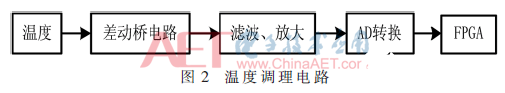

數(shù)據(jù)系統(tǒng)采用PT100溫度傳感器來測(cè)量10路溫度。PT100溫度傳感器將溫度變量轉(zhuǎn)換成可以傳送的標(biāo)準(zhǔn)化電信號(hào)。此傳感器精度高,穩(wěn)定性好,測(cè)溫范圍在-200 ℃~650 ℃之間,符合臨空測(cè)溫范圍要求。如圖2所示,將PT100傳感器連接到差動(dòng)電路中,測(cè)量差分電壓,將此電壓信號(hào)進(jìn)行整形調(diào)理,經(jīng)過模數(shù)轉(zhuǎn)換芯片得到數(shù)字值暫存到FPGA中的內(nèi)存中。濾波電路采用阻容濾波。儀表放大器采用TI公司的儀表放大器INA333,該放大器具有低功耗、高精度的特性。AD轉(zhuǎn)換芯片應(yīng)用5 V供電電壓的TLC2543IN,允許11路外部模擬信號(hào)并行輸入,串口輸出轉(zhuǎn)換數(shù)據(jù),具有12位的分辨率。

1.3 氣壓采集模塊

本設(shè)計(jì)選用SMI公司的SM5852系列氣壓傳感器來采集氣壓信號(hào)。SM5852傳感器的工作溫度為-40 ℃~125 ℃,能夠滿足臨空的惡劣環(huán)境,芯片內(nèi)部有溫度補(bǔ)償算法,實(shí)現(xiàn)氣壓的精準(zhǔn)測(cè)量。本文選用SM5852-003傳感器,其可測(cè)壓力范圍是0~0.3 PSI(Pounds per Square Inch)。氣壓傳感器既可以輸出數(shù)字信號(hào),又可以輸出模擬信號(hào)。為了使系統(tǒng)設(shè)計(jì)簡(jiǎn)單而且信號(hào)獲取精確高,這里直接采集傳感器的數(shù)字信號(hào)。數(shù)字信號(hào)是通過IIC協(xié)議傳輸?shù)模⒗?4LVC4245電平轉(zhuǎn)換芯片將電壓的控制器與傳感器連接在一起,將5 V的數(shù)字信號(hào)轉(zhuǎn)換為3.3 V數(shù)字信號(hào),同時(shí)對(duì)控制模塊起到保護(hù)作用。

1.4 通信模塊

這一模塊在本系統(tǒng)中非常關(guān)鍵,它是連接采集器與地面監(jiān)控系統(tǒng)的紐帶。它負(fù)責(zé)將臨空采集平臺(tái)上獲取的信息實(shí)時(shí)地傳送給機(jī)載計(jì)算機(jī)或者北斗模塊,同時(shí)實(shí)時(shí)接收來自兩個(gè)模塊的指令。采集平臺(tái)上的重要數(shù)據(jù)信息通過事先擬定的協(xié)議被組合成不同長(zhǎng)度的幀發(fā)送給地面指揮站。為了保證數(shù)據(jù)的安全性和準(zhǔn)確性,增加數(shù)據(jù)幀校驗(yàn)環(huán)節(jié),將求異或和作為幀校驗(yàn)的方法。

本系統(tǒng)的FPGA控制板放置在數(shù)據(jù)采集系統(tǒng)的平臺(tái)上,與地面指揮站通信交互信息主要有兩類:一類是下發(fā)采集器收集到的數(shù)據(jù)信息,另一類接收地面指揮系統(tǒng)的指令信息。為了保證數(shù)據(jù)安全和采集系統(tǒng)的可靠性,對(duì)通信模塊冗余設(shè)計(jì)。通過兩個(gè)RS422接口與機(jī)載計(jì)算機(jī)相連,機(jī)載計(jì)算機(jī)再通過無線通信與地面指揮站交互信息。另外,還通過兩個(gè)RS232接口與機(jī)載北斗相連,通過北斗衛(wèi)星服務(wù)與地面指揮站聯(lián)系。同時(shí),采集器的定位信息一同下發(fā)到地面。RS422接口芯片選用ADI公司ADM2587E,RS232接口芯片采用ADI公司的ADM3251E。兩個(gè)RS422接口分為主板串口、從板串口,主板串口處理的是與主板相關(guān)的數(shù)據(jù)信息,從板串口處理與從板相關(guān)的數(shù)據(jù)信息。

2 系統(tǒng)軟件設(shè)計(jì)

軟件代碼開發(fā)基于Altera公司的Quartus II 13.0平臺(tái),利用Verilog HDL語言實(shí)現(xiàn)代碼塊的設(shè)計(jì)與仿真。臨空數(shù)據(jù)采集系統(tǒng)中,F(xiàn)PGA控制器內(nèi)信號(hào)的性質(zhì)和來源各式各樣,有直接來自傳感器的數(shù)字信號(hào),有模擬信號(hào)轉(zhuǎn)換后的數(shù)字信號(hào),有程序內(nèi)部的標(biāo)志信號(hào),有來自機(jī)載計(jì)算機(jī)的控制信號(hào),有來自北斗模塊發(fā)來的控制信號(hào)和定位信號(hào),有FPGA控制器發(fā)出的數(shù)據(jù)信號(hào)、電機(jī)控制信號(hào)、電路板控溫信號(hào)等。為了提高有效數(shù)據(jù)穩(wěn)定地接收、存儲(chǔ)和發(fā)送,需要對(duì)全體信號(hào)細(xì)致分類,這對(duì)程序代碼模塊劃分有指導(dǎo)作用。系統(tǒng)軟件設(shè)計(jì)要求代碼可讀性高、可靠性高、易維護(hù)、有可擴(kuò)展的余地。系統(tǒng)設(shè)計(jì)的思路是先做總體架構(gòu),再逐個(gè)完成子模塊的編寫,最后在頂層模塊完成信號(hào)連接。模塊化的設(shè)計(jì)思路使得系統(tǒng)仿真測(cè)試更容易,代碼維護(hù)性更強(qiáng)。

2.1 程序頂層架構(gòu)

程序頂層模塊的設(shè)計(jì)影響全局,關(guān)系到系統(tǒng)的穩(wěn)定性和可靠性。系統(tǒng)結(jié)構(gòu)的設(shè)計(jì)是根據(jù)模塊的功能劃分,每一個(gè)模塊實(shí)現(xiàn)一個(gè)具體的功能,數(shù)據(jù)信息的交互通過各模塊的輸入輸出接口連接。

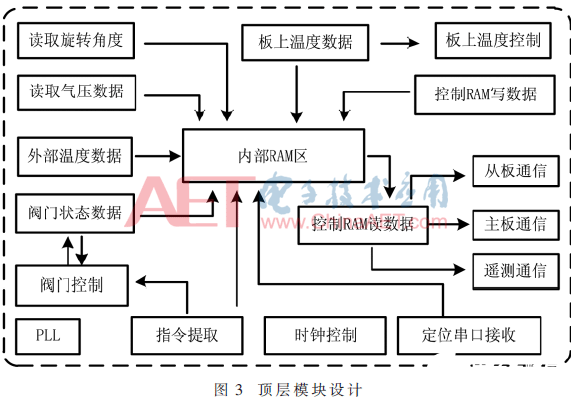

數(shù)據(jù)采集系統(tǒng)信號(hào)比較多,而且FPGA與機(jī)載計(jì)算機(jī)、北斗模塊的通信按照既定協(xié)議交互數(shù)據(jù),即定時(shí)發(fā)送采集系統(tǒng)的數(shù)據(jù),不定時(shí)接收外部指令和狀態(tài)信息,為了便于管理數(shù)據(jù),在FPGA內(nèi)開辟一塊隨機(jī)存儲(chǔ)器(Random Access Memory,RAM),專門針對(duì)各種信號(hào)存儲(chǔ)和讀取,這種數(shù)據(jù)結(jié)構(gòu)使FPGA內(nèi)部數(shù)據(jù)共享更容易,也不易產(chǎn)生讀寫數(shù)據(jù)紊亂現(xiàn)象[6-7]。引用Altera公司提供的IP核配置RAM,經(jīng)過事先估計(jì)并留有足夠的余地,將RAM大小設(shè)置為512 B,讀寫地址線各9根,并設(shè)置讀寫使能控制端口。圖3為系統(tǒng)的頂層模塊架構(gòu),核心模塊是RAM區(qū)的讀寫模塊,溫度、壓力、電壓、電流信號(hào),以及來自機(jī)載計(jì)算機(jī)或北斗的指令、位置和狀態(tài)等信號(hào)流入RAM區(qū),而存儲(chǔ)的數(shù)據(jù)需要從RAM區(qū)被讀取,通過UART串口模塊發(fā)送給機(jī)載計(jì)算機(jī)和北斗模塊。

2.2 通信模塊程序設(shè)計(jì)

通信模塊借助UART串口實(shí)現(xiàn)雙向通信。FPGA控制器向機(jī)載計(jì)算機(jī)和北斗模塊發(fā)送數(shù)據(jù)幀,同時(shí)實(shí)時(shí)接收它們的指令與狀態(tài)數(shù)據(jù)。控制器向兩個(gè)RS422串口發(fā)送定位、主從板信息、狀態(tài)等數(shù)據(jù)幀,定位數(shù)據(jù)幀包含來自北斗模塊的定位信息,主從板數(shù)據(jù)幀囊括采集系統(tǒng)采集到的各類信息,狀態(tài)數(shù)據(jù)幀含有北斗模塊的狀態(tài)信息。此外,控制器向兩個(gè)RS232串口發(fā)送遙測(cè)數(shù)據(jù)幀和自檢數(shù)據(jù)幀,遙測(cè)數(shù)據(jù)幀由遙測(cè)幀頭、定位信息、主板或從板信息和遙測(cè)數(shù)據(jù)幀尾組成,自檢數(shù)據(jù)幀包括自檢信息的請(qǐng)求。同時(shí),有3個(gè)UART串口實(shí)時(shí)接收來自機(jī)載計(jì)算機(jī)和北斗模塊的指令和狀態(tài)信息。程序運(yùn)行時(shí)需要對(duì)各種數(shù)據(jù)幀頻繁讀寫操作,如果程序設(shè)計(jì)不合理,很容易造成程序死鎖或崩潰。鑒于串口數(shù)據(jù)的接收和發(fā)送沒有緊密地耦合,程序內(nèi)部將數(shù)據(jù)接收和發(fā)送分成兩個(gè)子模塊來設(shè)計(jì),然后在頂層模塊通過wire型變量連接。為了有效解決數(shù)據(jù)讀寫不紊亂的問題,設(shè)計(jì)狀態(tài)機(jī)來合理使用RAM區(qū)資源,增強(qiáng)程序的穩(wěn)定性。狀態(tài)機(jī)的空閑任務(wù)會(huì)出現(xiàn)連接兩個(gè)always塊的使能信號(hào),設(shè)計(jì)watchdog程序增強(qiáng)程序的魯棒性。

2.2.1 RAM數(shù)據(jù)段劃分

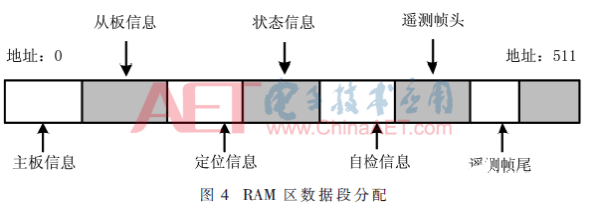

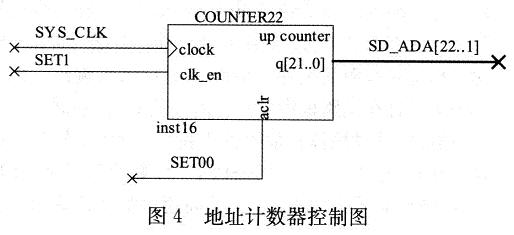

本文設(shè)計(jì)了雙端口RAM數(shù)據(jù)結(jié)構(gòu),承載采集控制系統(tǒng)的重要數(shù)據(jù)。依據(jù)通信協(xié)議,針對(duì)512 B的RAM區(qū),細(xì)致地進(jìn)行了數(shù)據(jù)段的劃分,如圖4所示。按照發(fā)送頻次以及組幀要求,合理分配數(shù)據(jù)幀的存儲(chǔ)順序。這樣設(shè)計(jì)會(huì)使控制器讀寫更可靠安全,也使代碼編寫調(diào)試更簡(jiǎn)捷。

2.2.2 數(shù)據(jù)發(fā)送狀態(tài)機(jī)設(shè)計(jì)

信息傳送模塊是連接地面指揮系統(tǒng)和數(shù)據(jù)采集系統(tǒng)的紐帶。在臨空惡劣環(huán)境下,為了將采集到的數(shù)據(jù)和系統(tǒng)狀況相關(guān)信息實(shí)時(shí)準(zhǔn)確地傳送到地面指揮站,在軟件上進(jìn)行了可靠性研究和處理。

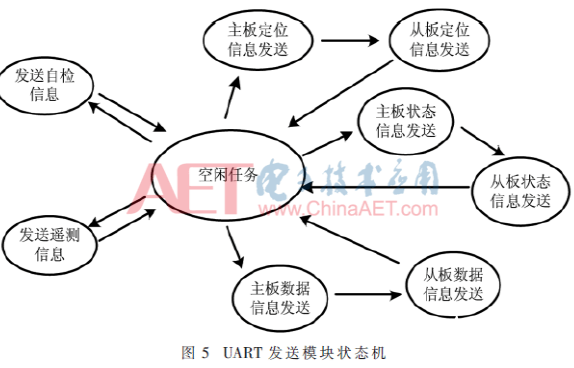

首先對(duì)傳送的數(shù)據(jù)做了校驗(yàn)處理,可通過上位機(jī)軟件測(cè)試傳輸數(shù)據(jù)幀是否正確,如果校驗(yàn)失敗,可丟棄此幀。本系統(tǒng)的發(fā)送模塊既要發(fā)送主板信息又要發(fā)送從板信息,既要傳送給機(jī)載計(jì)算機(jī)又要傳送給北斗衛(wèi)星,發(fā)送幀的類型也有差異,因此,設(shè)計(jì)三段式狀態(tài)機(jī)穩(wěn)定地傳送數(shù)據(jù),以免數(shù)據(jù)發(fā)送紊亂。在狀態(tài)機(jī)的空閑任務(wù)中,F(xiàn)PGA等待各種數(shù)據(jù)類型幀的觸發(fā)信號(hào),一旦接收到啟動(dòng)發(fā)送信號(hào),進(jìn)入到相應(yīng)的發(fā)送狀態(tài)中,將對(duì)應(yīng)的數(shù)據(jù)幀發(fā)送到UART串口上,串口的觸發(fā)信號(hào)也因數(shù)據(jù)信息的差異而不同。在空閑任務(wù)中,接收到觸發(fā)信號(hào)后,需要實(shí)時(shí)對(duì)RAM區(qū)執(zhí)行寫操作,寫操作完成后再進(jìn)入發(fā)送狀態(tài),不免會(huì)引起程序死鎖。為了解決這個(gè)問題,提高程序的魯棒性,在等待寫操作的部分加入看門狗程序,一旦死鎖,可以強(qiáng)行將程序拉回到原始等待狀態(tài)。圖5為UART串口發(fā)送模塊的狀態(tài)機(jī)示意圖。

3 系統(tǒng)仿真與調(diào)試

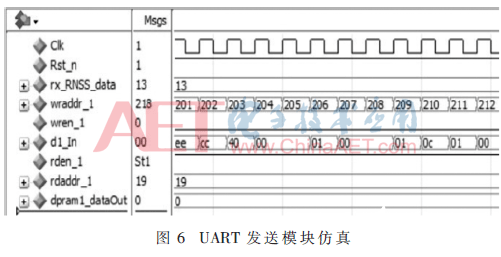

數(shù)據(jù)系統(tǒng)的測(cè)試主要通過兩種手段:軟件仿真和借助上位機(jī)聯(lián)調(diào)。本系統(tǒng)用到的仿真工具有Quartus II開發(fā)環(huán)境提供的在線邏輯分析儀、信號(hào)探針、邏輯分析儀接口等,還有外部安裝性能強(qiáng)大的Modelsim仿真工具。例如,在調(diào)試具有讀寫應(yīng)答的IIC通信的傳感器和基于SPI通信的傳感器時(shí),使用在線邏輯分析儀直接觀察數(shù)據(jù)波形特征,能夠快速診斷并排查錯(cuò)誤。利用Modelsim仿真工具時(shí),需要先編寫對(duì)應(yīng)模塊的testbench代碼,并添加到仿真工具中,運(yùn)行仿真軟件。圖6為調(diào)試UART通信模塊波形圖,可觀察RAM的讀寫地址值與數(shù)據(jù)值的對(duì)應(yīng)關(guān)系,驗(yàn)證代碼的邏輯。尤其在調(diào)試狀態(tài)機(jī)的運(yùn)行情況時(shí),能夠很直觀地查看狀態(tài)時(shí)序邏輯的正確性。

當(dāng)集中測(cè)試所有的模塊時(shí),為了提高調(diào)試效率,利用了基于UART通信的上位機(jī)軟件。該軟件運(yùn)行在Windows 10 系統(tǒng)上,它通過USB接口接收FPGA發(fā)送的數(shù)據(jù)信息,并把信息可視化在面板上,直觀明了地看到FPGA采集到的數(shù)據(jù)。

4 結(jié)論

臨空環(huán)境有低溫、低壓、高輻射的特點(diǎn),因此對(duì)運(yùn)行在環(huán)境下數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)要求極為嚴(yán)格。本文從軟硬件兩方面著手進(jìn)行可靠性研究,設(shè)計(jì)了應(yīng)對(duì)這種復(fù)雜環(huán)境的數(shù)據(jù)采集系統(tǒng),取得了良好的效果。該系統(tǒng)能夠可靠穩(wěn)定地采集到傳感器數(shù)據(jù),并能長(zhǎng)時(shí)間穩(wěn)定地與北斗模塊和機(jī)載計(jì)算機(jī)通信,能夠通過地面控制系統(tǒng)發(fā)送指令控制數(shù)據(jù)采集系統(tǒng)。

參考文獻(xiàn)

[1] MONMASSON E,IDKHAJINE L,CIRSTEA M N,et al.FPGAs in industrial control applications[J].IEEE Transactions on Industrial Informatics,2011,7(2):224-243.

[2] KANDADAI V,SRIDHARAN M,PARVATHY S M,et al.A comprehensive embedded solution for data acquisition and communication using FPGA[J].Journal of Applied Research & Technology,2017,15(1):45-53.

[3] 周珊,楊雅雯,王金波。航天高可靠FPGA測(cè)試技術(shù)研究[J]。計(jì)算機(jī)技術(shù)與發(fā)展,2017,27(3):1-5.

[4] 宋克非.FPGA在航天遙感器中的應(yīng)用[J]。光機(jī)電信息,2010,27(12):49-55.

[5] 陳柯勛,王曉毅,薛輝。基于FPGA的數(shù)據(jù)采集器設(shè)計(jì)及可靠性分析[J]。科技資訊,2017,15(24):7-8.

[6] 王敬美,楊春玲。基于FPGA和UART的數(shù)據(jù)采集器設(shè)計(jì)[J]。電子器件,2009,32(2):386-389.

[7] NING Y,GUO Z,SHEN S,et al.Design of data acquisition and storage system based on the FPGA[J].Procedia Engineering,2012,29:2927-2931.

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論