0 引言

隨著現代信息技術的快速發展,數字信號處理技術在軍用和民用市場都得到了廣泛的應用,同時日趨復雜的信號處理需求也對處理平臺提出了更高的要求,特別是在無線通信、人工智能、航空航天等高科技領域信號處理實時性高,數據量大,數據交互及處理算法復雜度高,依靠單個處理器的傳統解決方案已經無法滿足這些需求,高度集成的多處理器嵌入式系統逐步成為高速信號處理平臺的主流方案,基于“DSP+FPGA”的協同處理架構憑借其超強的處理能力和廣泛的工程化應用優勢,已經成為通用信號處理平臺的首選。采用“DSP+FPGA”的信號處理系統顯著提升了運算速度和數據處理能力,但同時不可避免地引入了處理器之間的數據交換問題,隨著交互頻率和數據量的急劇增加,對芯片間的高速數據傳輸要求越來越高,傳統的共享總線已無法滿足高性能嵌入式系統的數據交互需求,成為了處理平臺性能進一步提升的瓶頸。因此,需要高性能互聯體系結構來解決嵌入式處理器之間的數據交互問題,高速串行Rapid IO總線正是基于該需求設計的新型高性能互連總線技術,該總線以其高帶寬、低延時、低功耗及高可靠性等優勢為嵌入式系統內部互連提供了良好的解決方案。本文設計一種基于SRIO總線的DSP與FPGA通信互連架構,其中多核DSP TMS320C6678的SRIO接口模塊采用4x接口模式配置,每路接口傳輸速率為3.125 Gb/s,理論傳輸速率達到10 Gb/s,同時使用DSP片上DDR3控制器模塊擴展2 GB高速緩存進行數據讀寫,從而實現系統內部數據高速傳輸及共享存儲。

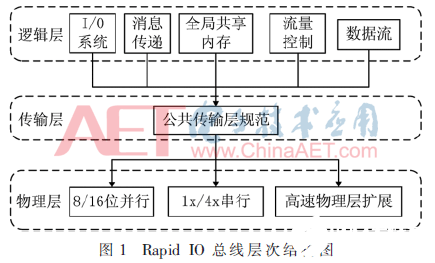

1 Rapid IO協議架構介紹

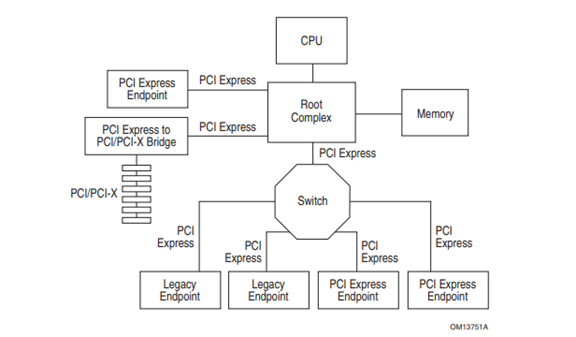

Rapid IO體系架構是為了滿足高性能嵌入式系統互連需求而設計的一種系統級互連技術,它支持芯片間以及板間的互連與通信,廣泛應用于多處理器、多存儲器及通用信號處理平臺等的交互連接。Rapid IO的數據傳輸操作基于數據包的請求與響應,數據包是點對點通信設備的消息載體,通信過程首先由主控器件發出一個請求事務,并將該請求事務以包的形式傳輸給目標器件,目標器件收到請求事務后執行相應操作并產生響應事務返回給通信的發起方,發起方接收到響應包后一次通信操作完成。Rapid IO互連體系結構共分為三層,分別為邏輯層、傳輸層和物理層。邏輯層為協議最高層,定義了全部操作協議和包格式,為端點器件發起和完成事務提供必要的信息;傳輸層處于協議中間層,定義了Rapid IO的地址空間、尋址機制和用于包交換的路由信息;物理層處于協議最底層,主要定義電氣特性、包傳輸機制、流量控制及低級錯誤管理等器件級接口細節,Rapid IO協議層次結構如圖1所示。

2 基于SRIO的互連系統設計

2.1 TMS320C6678的SRIO模塊特性

TMS320C6678 DSP外圍接口豐富,片內集成了基于1x/4x LP-Serial規范的串行Rapid IO外設接口模塊,即SRIO。該模塊支持4通道的Rapid IO高速傳輸,也可配置成1x、2x和4x等多種接口模式,單個通道的傳輸速度最大可達5 Gb/s,在實際工程化應用中也可靈活配置到1.25 Gb/s、2.5 Gb/s和3.125 Gb/s使用。

基于Rapid IO的高速傳輸操作協議由邏輯層定義,SRIO接口邏輯層支持I/O邏輯操作(Direct I/O)和消息傳遞(Message Passing)兩種數據傳輸機制,其中I/O邏輯操作包含NREAD、NWRITE、NWRITE_R、SWRITE、Atomic和MAINTENANCE共6種基本I/O操作,消息傳遞主要包括DOORBELL和MESSAGE兩種,具體如表1所示。

直接I/O模式是最簡單實用的傳輸方式,主設備可以直接讀寫從設備的存儲器,可通過多種請求和響應事務直接完成對應存儲空間的數據讀寫,其中SWRITE事務是高效的傳輸格式,接口實現簡單,通信開銷小,適用于點對點的大數據直接傳輸;消息傳遞模式使用信箱和信件的方式傳遞信息,類似以太網的傳輸方式,接收方根據內部地址與信箱的映射關系對數據進行讀寫,適用于包含多個處理器的復雜系統間通信。消息傳遞機制中包含有一種特殊的輕量級消息傳遞事務類型,即門鈴消息(Doorbell),門鈴消息數據包僅可填充一個16位大小的數據負載,適用于發送SRIO通信的中斷信息,接收方將收到的門鈴事務放到門鈴消息隊列中,通過解析門鈴信息進行相應的響應操作。

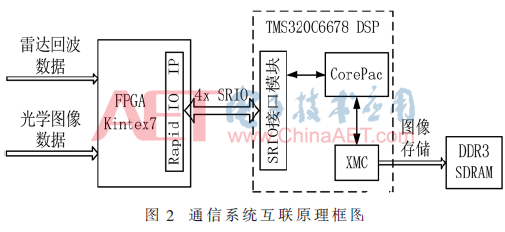

2.2 傳輸系統互聯設計

本文設計的DSP與FPGA通信系統基于圖2所示的高速串行Rapid IO接口進行互聯設計。在FPGA端選用Xilinx公司的Kintex7系列芯片,FPGA對外接口接收雷達回波數據或者光學相機采集的圖像數據,然后通過4路SRIO高速接口將數據實時傳輸給DSP芯片,FPGA的SRIO接口采用開發平臺提供的IP核進行設計實現。DSP端芯片選用TI公司的TMS320C6678高性能多核浮點型處理器,該芯片采用全新的Keystone架構和C66x內核,其內部有8個速度達到1.25 GHz的高性能定點/浮點CPU內核,每個內核的單周期定點性能高達32MAC,浮點性能高達16FLOP,單個CorePac內核中配置了32 KB一級程序存儲器(L1P)、32 KB一級數據存儲器(L1D)以及512 KB二級局部存儲器(L2),高性能的計算能力和高速緩存能力有效地支撐了復雜圖像處理算法的工程化應用需求。同時6678處理器內部集成了DDR3控制器模塊,帶有64 bit位寬的DDR3存儲器接口總線,最高速率可達1 600 MTS,可供尋址的空間達到了8 GB,本系統外掛了4片256×64 bit的DDR3 SDRAM,總容量達到2 GB,完全滿足系統數據緩存需求,DSP處理器可以通過EDMA的方式直接對DDR3存儲器進行讀寫訪問,減少了通過內核CPU讀寫大數據的資源占用,有效提升系統并行運算效能。

3 通信系統軟件設計

3.1 SRIO接口驅動設計

根據上文的互聯系統設計,為了實現接口通信功能需進行接口軟件設計,DSP端的SRIO外設模塊驅動編程主要有以下幾個方面:

(1)通信設備ID設置

SRIO模塊支持8位和16位兩種模式ID設置,8位的ID可容納256個單獨設備,16位ID可容納65 536個單獨設備,通信雙方需采用相同設置模式,但要設置為不同的ID號,本系統采用8位ID模式設置,DSP和FPGA ID號設置如下:

#define SRIO_DSP_BASE_ID (0x00)

#define SRIO_FPGA_BASE_ID (0xFF)

(2)SRIO工作模式配置

SRIO模塊可配置成1x、2x和4x等多種端口模式使用,可通過路徑控制寄存器PLM_SP(n)_PATH_CTL的PATH_CONFIG和PATH_MODE作用域進行編程配置。本系統采用4x模式配置,單通道速率配置為3.125 Gb/s,具體配置程序如下:

CSL_SRIO_Enable3_125GBaud(hSrio, 0);

CSL_FINS(hSrio-》RIO_PLM[0].RIO_PLM_SP_PATH_CTL,SRIO_RIO_PLM_SP_PATH_CTL_PATH_CONFIGURATION, 4);

CSL_FINS(hSrio-》RIO_PLM[0].RIO_PLM_SP_PATH_CTL, SRIO_RIO_PLM_SP_PATH_CTL_PATH_MODE, 4);

(3)SerDes模塊配置

SRIO接口通過SerDes(Serialize Deserialize)模塊接收和發送高速串行差分信號,該模塊由TX、RX、PLL、S2P(serial-to-parallel)、P2S(parallel-to-serial)及時鐘恢復等部分組成,初始化配置主要對PLL模塊的SRIO_SERDES_CFGPLL寄存器的MPY域賦值0x00010100,表示PLL倍頻5倍,并對ENPLL位賦值1使能PLL; 對SRIO_SERDES_CFGTX[0-3]和SRIO_SERDES_CFGRX[0-3]寄存器的RATE位賦值0x01,表示每個時鐘周期采樣兩位數據,結合時鐘倍頻配置可以計算出傳輸速率rate=clk*MPY*RATE=312.5MHz*5*2bit=3.125 Gb/s,即得到需要的速率,配置功能函數如下:

CSL_BootCfgSetSRIOSERDESConfigPLL(cfgPll);

for(index = 0; index 《 4; index++)

{

CSL_BootCfgSetSRIOSERDESRxConfig(index, cfgRx);

CSL_BootCfgSetSRIOSERDESTxConfig(index, cfgTx);

}

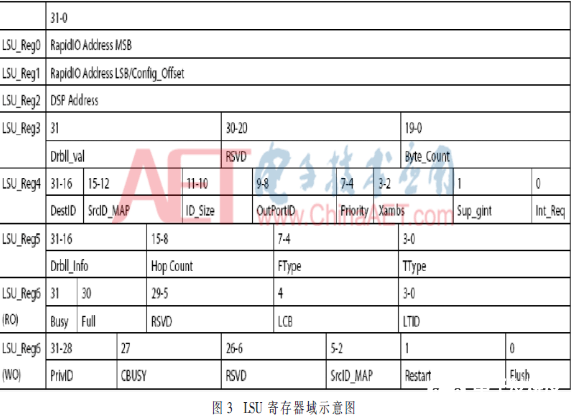

(4)LSU模塊配置

SRIO的Direct I/O和Message Passing兩種傳輸機制使用不同的傳輸控制模塊,其中控制Direct I/O模式包發送的為LSU(Load/Store Unit)模塊,系統中一共有8個LSU,每個LSU都有獨立的7個寄存器,即LSU_Reg0--LSU_Reg6,Reg0--Reg4用來配置傳輸控制信息,REG5、REG6用來存儲命令和狀態信息,Reg6有只讀和只寫兩種模式,其他寄存器都是可讀可寫的,LSU寄存器組定義如圖3所示。

由圖3可見LSU的Reg0~4中主要配置了Direct I/O傳輸的控制信息,如源地址、目的地址、數據長度、設備ID、端口號、優先級等;Reg5寄存器配置門鈴信息和包格式等命令信息;Reg6在只讀模式下通過Busy和Full位信息確認指令寄存器和影寄存器是否空閑,該兩位信息都為0時表示當前LSU可用, LTID位和LCB位信息一起用于確認傳輸的完成信息(completion code)。

LSU寄存器配置可使用CSL庫文件中的API函數CSL_SRIO_SetLSURegx()對每一個寄存器單獨賦值編程,也可通過編輯結構體SRIO_LSU_TRANSFER變量對ByteCount、DestID、deviceID、TType、FType、Drbll_Info等關鍵成員變量進行賦值,然后通過API函數CSL_SRIO_SetLSUTransfer()完成整個傳輸的配置和啟動。

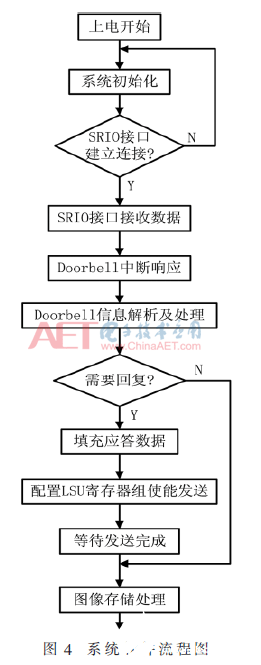

3.2 數據傳輸系統軟件設計

本文設計的DSP與FPGA通信系統通信節點較少,傳輸數據量大,屬于點對點的高速數據傳輸,所以SRIO接口采用Direct I/O傳輸方式和Doorbell消息相結合的方案進行數據交互,數據包格式采用Direct I/O方式的SWRITE流寫操作,傳輸方案實現簡單,同時通信發起方在數據發送完成后發送Doorbell消息通知接收方傳輸完成,接收方收到Doorbell消息后進行相應處理,保證通信過程的實時性和正確性。具體軟件流程如圖4所示。

系統上電啟動后,軟件對DSP系統中時鐘、定時器、存儲器、中斷等必要設備進行初始化,在SRIO模塊初始化過程中需等待DSP與FPGA的SRIO接口連接成功才表示初始成功,然后便可以進行自定義的數據傳輸操作了。根據TMS320C6678 DSP存儲空間配置,本系統中DDR3緩存地址區域為0x80000000—0xFFFFFFFF,大小為2 GB,SRIO接口可直接對存儲空間進行讀寫訪問。根據系統設計FPGA每發送完一組數據后,都將附帶發送一個Doorbell消息作為完成標記,Doorbell的16 bit信息位填充內容為0x0001,表示使用DOORBELL0_ICRR寄存器的ICR1映射中斷事件,系統中設置CPU中斷4作為響應Doorbell事件的CPU中斷,DSP收到Doorbell消息后將觸發CPUINT4,程序跳轉執行中斷響應函數,在中斷響應函數中查詢中斷狀態位,對接收數據包的正確性進行判斷,然后通過EDMA模塊將數據快速搬移到DDR3指定地址鎖存,并調用算法對數據進行處理。當DSP需要向FPGA端回復應答信息時,DSP程序通過配置LSU寄存器組向FPGA存儲地址發送數據,當LSU的Reg0~Reg5配置完成后傳輸開始,程序軟件通過查詢LSU傳輸完成信息與Reg6中記錄的LCB位信息進行比較,判斷當前傳輸是否成功。

4 測試與驗證

針對上文所設計的SRIO互聯系統進行性能測試,系統設計單通道傳輸速度為3.125 Gb/s,物理層SerDes模塊采用8B/10B編碼,所以4通道的SRIO接口理論傳輸速度為3.125×4×8/10=10 Gb/s。實際測試過程中采用多組長度不同的數據進行測試,每組測試數據多次運行取平均值,測試結果如表2所示。

測試結果表明,本文設計的DSP與FPGA互聯系統能夠按照設計需求穩定工作,數據讀寫正確,傳輸速度較為穩定,當數據量較大時通信開銷占總傳輸時間比例減小,整體傳輸速度超過8 Gb/s,達到理論值10 Gb/s的80%以上,傳輸效率較為理想。

5 結論

本系統基于TI多核DSP TMS320C6678的SRIO接口模塊建立DSP與FPGA之間的高速通信互聯系統,采用SRIO模塊4x接口模式及每路接口3.125 Gb/s的傳輸速率實現DSP與FPGA間高速穩定的數據傳輸,同時使用DSP自帶DDR3控制器模塊實現對DSP外部擴展DDR3 SDRAM存儲芯片的讀寫訪問,從而實現系統內部數據傳輸及共享存儲。該系統已經在大視場高分辨率光學圖像處理、實時SAR雷達成像等多個工程項目中得到應用驗證。

參考文獻

[1] Texas Instruments.TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor[Z].2014.

[2] Texas Instruments.KeyStone Architecture Serial Rapid IO(SRIO) User Guide[Z].2012.

[3] Texas Instruments.KeyStone Architecture DDR3 Memory Controller User Guide[Z].2011.

[4] Texas Instruments.TMS320C66x DSP CorePac User Guide[Z].2013.

電子發燒友App

電子發燒友App

評論