隨著各種高速長時間物理實驗要求的不斷提高,系統(tǒng)對高速的數(shù)據(jù)采集模塊的需求也越來越高,在許多特殊應用的場合中,系統(tǒng)也需要對大量突發(fā)的數(shù)據(jù)進行采集處理,用FPGA實現(xiàn)的高刷新率高分辨率圖像采集系統(tǒng),用于船載雷達圖像記錄。該系統(tǒng)由AD、FPGA、SDRAM組成,AD芯片把雷達提供的以VGA接口方式給出的圖像信號轉換成數(shù)字信號,F(xiàn)PGA控制時序通過整頁突發(fā)的模式寫入SDRAM中,并提供了后續(xù)處理的接口。

中國船級社規(guī)定從2004年開始,在國內和國際航行的船舶中都必須安裝船載航行數(shù)據(jù)記錄儀,其中船載雷達圖像記錄儀是很重要的一部分,船載雷達圖像按VGA圖像標準輸出,其分辨率在640×480-1280×1024之間,刷新率在60-85Hz之間。目前常見的圖像采集系統(tǒng)多是針對復合視頻信號的采集,或者是針對CCD圖像信號的采集。這些圖像采集系統(tǒng)并不能滿足雷達圖像采集的要求,即使少數(shù)針對高分辨率高刷新率圖像的采集系統(tǒng)也是以計算機板卡的形式出現(xiàn),運行時需要一臺計算機。

目前一些速度高達1GSPS的基于VME總線的數(shù)據(jù)采集系統(tǒng),通過4路,每路采集速度高達250MHz的系統(tǒng)實現(xiàn)1GSPS速度的數(shù)據(jù)采集。但由于該類系統(tǒng)中沒有大容量的數(shù)據(jù)緩存,因此并不能實現(xiàn)高速長時間的數(shù)據(jù)采集。另外一些系統(tǒng)采用一種基于FPGA,使用多SDRAM作為數(shù)據(jù)緩存的采集系統(tǒng)。該類系統(tǒng)解決了長時間高速采集的問題,可以對頻率為100MHz,16bit位寬的數(shù)據(jù)進行采集。但是由于它采用了多個FIFO來降低SDRAM的工作頻率,使得該類系統(tǒng)應用在需要嚴格的數(shù)據(jù)同步的高速圖像采集系統(tǒng)中會出現(xiàn)一些數(shù)據(jù)難以同步的問題,還有一種PC板卡形式的高分辨率圖像采集卡,該系統(tǒng)直接對圖像進行壓縮后存儲,并通過PCI接口提供給PC,這種形式既不適合船舶上狹小的空間,也不能滿足船舶失事時對數(shù)據(jù)的保護要求。

本文提出一種高分辨率高刷新率圖像采集系統(tǒng)。該系統(tǒng)使用于嵌入式系統(tǒng)中,不僅體積小,還解決了數(shù)據(jù)保護的問題,可用于船載雷達圖像記錄系統(tǒng)。該系統(tǒng)可支持對多達4路8bit位寬最高采樣率達120MHz的數(shù)據(jù)通道,或者一路VGA圖像信號,可對采集數(shù)據(jù)進行長時間采集存儲。具體的連續(xù)采集時間根據(jù)系統(tǒng)所采用的SDRAM容量大小有所變化。該系統(tǒng)還為數(shù)據(jù)的后續(xù)處理提供了ASRAM接口,使得用于緩存數(shù)據(jù)的SDRAM也可作為后續(xù)處理CPU的系統(tǒng)內存。這樣既可以提高數(shù)據(jù)的處理速度,方便后續(xù)針對雷達圖像的壓縮或者識別處理,也節(jié)省了資源。

采集系統(tǒng)設計

系統(tǒng)分析及芯片選擇

首先確定系統(tǒng)要求。目前標準規(guī)定的VGA分辨率從640×480-1280×1024之間可調,刷新率為60-80Hz可調。系統(tǒng)應能接受最高情況為分辨率1280×1024,刷新率60Hz。在這種情況下,圖像像素點頻率為:1280×1024×60=75MHz。

VGA是用于給顯示器等模擬設備提供圖像信號的模擬接口。它有RGB3個模擬信號分量以及行場同步信號,其中行場同步信號是符合TTL電平的脈沖信號。由于模擬的VGA信號中包含有場同步時間和行同步時間及消隱時間,因此當圖像為1280×1024@60Hz的情況下,AD轉換后像素點頻率要比實際算出來的75MHz還高。這么高的采樣率對于AD提出了很高的要求。因此采用Analog Device公司的芯片。AD芯片具有3路采樣精度為8bit的通道,最高采樣率為140MSPS,具有300M的模擬帶寬,并且專門對計算機及工作站圖像接口進行了優(yōu)化,最高可滿足對分辨率為1280×1024,刷新率為75Hz的視頻進行采樣。

由于AD的采樣率比較高,相應的輸出數(shù)據(jù)率很也高。在系統(tǒng)要求的最高情況下,象素點頻率為108MHz,相應的數(shù)據(jù)率為324Mbit/s(RGB3個分量,每個分量8bit)。同時,由于采集的是圖像數(shù)據(jù),因此系統(tǒng)對行同步要求比較高,因為如果在某一行的圖像數(shù)據(jù)中丟失了某一個或多個點的數(shù)據(jù),整個圖像就會產生傾斜,如圖1所示。圖a為正確采集后得圖像,沒有發(fā)生傾斜;圖b為行采集數(shù)據(jù)小于顯示的水平分辨率;圖c為行采集數(shù)據(jù)大于顯示的水平分辨率。因此需要對每行的數(shù)據(jù)進行突發(fā)存儲,保證數(shù)據(jù)不丟失。突發(fā)的長度為圖像的水平分辨率。

從上面的分析可知,AD后數(shù)據(jù)的及時存儲要求很高,在極端條件下系統(tǒng)必須以110MHz左右的頻率進行突發(fā)長度為1280×3Byte的存儲。傳統(tǒng)的通過DSP把數(shù)據(jù)存儲到SDRAM的方法不能滿足這么高的速度和這么長的突發(fā)長度。因此我們采用FPGA直接控制SDRAM存儲的方式進行。考慮到圖像數(shù)據(jù)的頻率和大小,我們采用工作在133MHz的SDRAM。

由于原始的圖像數(shù)據(jù)量很大,需要占用比較大的存儲空間,因此對采集到的圖像數(shù)據(jù)還要進行后續(xù)處理。所以FPGA除了接收AD轉換后的數(shù)據(jù)和控制SDRAM之外,還需要為圖像的后續(xù)處理提供接口。

綜上所述FPGA需要實現(xiàn)如下功能:同步接收AD采集的數(shù)據(jù);讀寫SDRAM;提供后續(xù)圖像處理接口;提供控制接口。

設計中采用Altera公司Cyclone系列的FPGA EP1C6。EP1C6具有2個鎖相環(huán),包含5980個邏輯單元,相當于12萬門的規(guī)模,同時還包含了最高頻率200MHz,92160bit的內部RAM。該芯片的頻率和引腳IO等資源都能很好的滿足本系統(tǒng)的要求。

總體設計

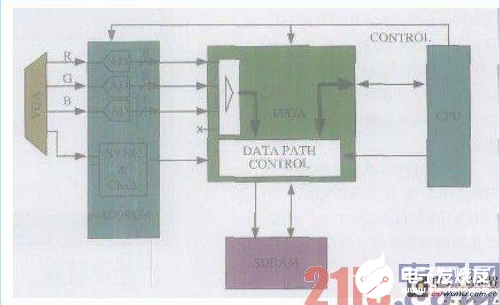

采集系統(tǒng)總體框圖如圖2所示。

采集系統(tǒng)由AD、FPGA、SDRAM和主CPU組成。整個系統(tǒng)由CPU控制。進行采集時,首先CPU根據(jù)行場同步信號判斷圖像的分辨率和刷新率,并對AD和FPGA進行相應的設置。其次,CPU使能FPGA進行采集。待采集一幀結束后,CPU即可對圖像數(shù)據(jù)進行處理。

AD模塊能夠采集多種VGA圖像格式,但卻不能自動檢測圖像格式,必須通過它提供的IIC接口進行設置,我們在主CPU中實現(xiàn)對圖像格式的自動檢測,并對AD模塊進行設置,另外,不同格式的VGA圖像中場同步信號的有效脈沖電平沒有統(tǒng)一,AD模塊可以對輸入的場同步信號極性進行自動檢測并表示在內部寄存器中,通過讀取該寄存器可以判斷輸入VGA信號場同步的極性。AD模塊輸出的場同步信號可以實現(xiàn)對輸入場同步信號的反相。FPGA內部的同步邏輯只支持一種有效電平的場同步信號,因此在采集前需要通過讀取AD內部的寄存器判斷當前輸入同步信號的極性,以確定是否需要設置AD芯片對場同步信號進行反相處理。

為了方便主CPU對FPGA的控制,F(xiàn)PGA提供了IIC接口。主CPU可以通過與AD模塊一樣的IIC接口控制FPGA。設置采集圖像的大小,圖像存儲起始地址,消隱時間長短等信息,從而保證采集圖像大小精確、完整,同時為了方便主CPU對圖像進行后續(xù)的處理,F(xiàn)PGA把存儲圖像的SDRAM轉換成ASRAM接口提供給CPU處理,從而把存儲圖像的空間直接映射到了CPU的尋址空間。CPU可以通過DMA快速的對圖像數(shù)據(jù)進行讀取和處理,提高系統(tǒng)效率。

FPGA內部設計

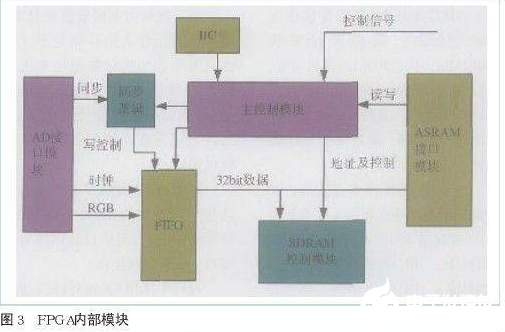

FPGA內部模塊如圖3所示。

FPGA內部由主控制、SDRAM控制器、AD接口、FIFO、ASRAM接口、IIC等模塊組成。主控制模塊負責接收CPU的控制信號和協(xié)調各個模塊之間的工作,SDRAM控制模塊實現(xiàn)對SDRAM的操作邏輯。AD接口模塊接收AD模塊輸出的數(shù)據(jù)和同步信號并保證圖像數(shù)據(jù)的行場同步,ASRAM接口模塊轉換CPU對ASRAM的操作為對SDRAM的操作指令,IIC邏輯模塊接收CPU對FPGA采集系統(tǒng)的各種參數(shù)設置和控制。[page]

系統(tǒng)FPGA主要時鐘頻率有SDRAM工作頻率133MHz,由EP1C6自帶的PLL倍頻產生;AD模塊輸出的像素時鐘,由AD芯片內部PLL產生,IIC模塊中的時鐘,由CPU產生。其中AD芯片輸出的時鐘根據(jù)不同的輸入圖像格式有比較大的變動范圍,從25-108MHz,而SDRAM的讀寫時鐘固定為133MHz。因此在這兩個不同頻率的時鐘之間必須加FIFO來同步,F(xiàn)IFO使用QuartusII軟件中提供的免費IP核,通過使用FPGA內部高速RAM來實現(xiàn)。

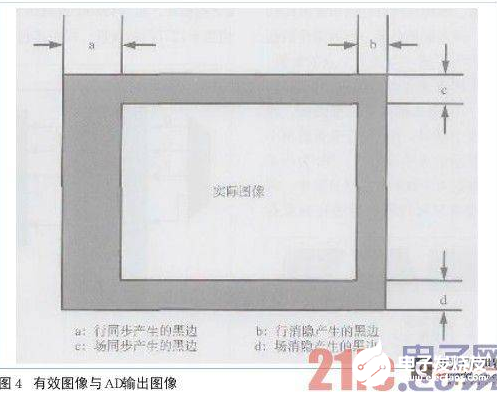

AD模塊負責與AD芯片的接口邏輯。前面已經分析了圖像采集中同步的重要性,如果圖像中的某一行數(shù)據(jù)不完整,那么將影響到整個圖像。AD模塊通過AD芯片輸出的行場同步信號來實現(xiàn)圖像數(shù)據(jù)的同步,以AD芯片輸出點頻作為FIFO模塊的寫時鐘,行場同步信號的組合邏輯組成FIFO的寫使能。另外,由于模擬的VGA接口存在有行、場同步時間和行、場消隱時間,為了保證圖像采集的精度和完整,AD芯片要求把點頻設置為比實際有效點頻大20%-30%,因為在AD轉換后的圖像中行幅和場幅往往比實際圖像大,造成圖像有比較大的黑邊。如圖4所示。為了獲得準確的圖像數(shù)據(jù),AD模塊設置了計數(shù)器可以過濾圖像起始的黑邊。其計數(shù)值可以通過IIC接口進行設置。

SDRAM有多種不同長度的突發(fā)模式。在本設計中由于AD輸出的頻率最高接近110MHz,突發(fā)存儲的長度比較長,為了能保證數(shù)據(jù)能夠及時存儲,工作頻率為133MHz的SDRAM必須工作在整頁突發(fā)的模式,以達到最高的數(shù)據(jù)吞吐率。

為了提高通用性,本設計中把SDRAM接口轉換成ASRAM接口提供給主CPU,避免了SDRAM工作頻率和CPU外部時鐘不同時造成的SDRAM控制權切換的麻煩,提高對各種CPU的兼容性。ASRAM接口邏輯實現(xiàn)對CPU地址到SDRAM地址的映射及操作時序的轉換。主控制模塊產生相應的SDRAM控制指令,控制SDRAM讀寫。SDRAM的操作對于CPU來說是透明的。

該采集系統(tǒng)也可對4路8bit的AD通道進行采集,因為FPGA內部的AD邏輯模塊提供了32bit的接口,VGA采集方式只用了其中24bit。采用4路8bit模式時只需把前端AD部分做一些調整。

實際應用

在中國船級社對船載航行數(shù)據(jù)記錄儀的性能要求中,要求船載航行數(shù)據(jù)記錄儀應能連接到欲記錄其圖像的雷達顯示器的視頻緩存輸出,通過專用的雷達緩存輸出接口,數(shù)據(jù)記錄儀需記錄一系列單個和整屏的視頻幀。該要求設計的顯示器的分辨率應在640×350到1280×1024之間,刷新率在60-85Hz之間。采用本設計可以完整實現(xiàn)該要求。

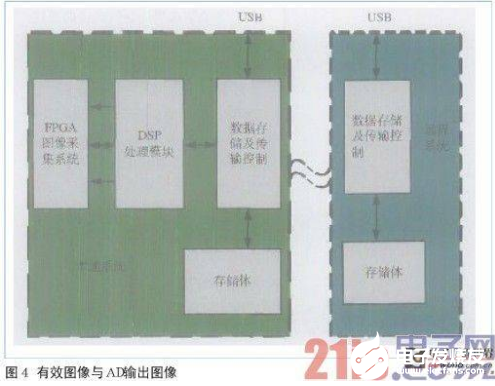

圖5所示為完整的雷達圖像記錄系統(tǒng)框圖。

總體上系統(tǒng)由本地端系統(tǒng)和遠程系統(tǒng)兩大部分組成。本地端負責對雷達圖像的采集壓縮和存儲備份。遠程系統(tǒng)保存雷達圖像的副本。本地系統(tǒng)由采集、處理、存儲傳輸3大部分組成。采集部分就是前文所述的以FPGA為核心的雷達圖像采集系統(tǒng)。處理部分采用TI公司C6000系列DSP作為系統(tǒng)的CPU。存儲傳輸部分主芯片則采用了Samsung公司的SOC芯片S3C2410。存儲體則采用了多片大容量的NAND Flash。

遠程系統(tǒng)與本地系統(tǒng)中的存儲和傳輸部分一樣。它只負責對雷達圖像的存儲。

本地系統(tǒng)和遠程系統(tǒng)通過485或者以太網相互通信。同時,本地系統(tǒng)和遠程系統(tǒng)都提供了USB接口。在計算機上可以通過USB接口讀取設備中存儲的圖像,并對設備參數(shù)進行設置。

本文介紹的高速圖像采集系統(tǒng)完整實現(xiàn)了預期的功能,能夠對最高分辨率為1280×1024刷新率為60Hz的雷達圖像進行采集,并通過ASRAM接口把圖像數(shù)據(jù)提供給CPU進行后續(xù)處理。

該采集系統(tǒng)適用于嵌入式系統(tǒng)中,成功應用于船載雷達數(shù)據(jù)記錄儀中,實現(xiàn)對雷達圖像的采集,通過了實際測驗。主要性能如下:采集圖像分辨率從640×350到1280×1024可調,刷新率從60-85Hz可調,在15s采集一次的情況下可以保存24小時的雷達圖像,并可以通過USB接口在計算機上重現(xiàn)雷達圖像。

此外,本采集系統(tǒng)實現(xiàn)了對高速突發(fā)長度長的數(shù)據(jù)的采集,并提供了相對通用的控制和存取接口,使得該系統(tǒng)的應用不僅僅局限于雷達圖像的采集。通過修改前端的AD模塊,該系統(tǒng)還能同時對4路位寬為8bit,采樣率最高位120MHz的AD通道進行數(shù)據(jù)采集,使它適用于其他需要高速采集的場合中。具有較強的通用性。

電子發(fā)燒友App

電子發(fā)燒友App

評論