異步串行數據接口要求接收器恢復數據,方式是對比特流進行檢查,并在所發送數據未附帶時鐘時確定每個位的采樣位置。有幾種方法可以在 Xilinx FPGA 中實現此類接收器。RocketIO收發器就是專門為這一任務設計的,但并非在所有 Xilinx FPGA 中都可用。根據器件系列和速度級別不同,SelectIO 的輸入端和 FPGA 邏輯資源可以實現比特率高達近 1 Gb/s 的異步串行接收器。

對于行程短且抖動小的數據,每個位周期對比特流采樣四次左右足矣。這種低過采樣率數據恢復技術在 XAPP224 《數據恢復》中有描述。不過,如果未經過位轉換數據行程就很長或者所要求的抖動容限高時,就需要較高的過采樣率,這在傳統上需要使用多個時鐘相位,常常要占用若干數字時鐘管理器 (DCM) 及大量全局時鐘資源。

Xilinx Virtex-4 和 Virtex-5 器件的每個輸入引腳都有與其相關的高精度可編程延遲單元。這些延遲單元被稱為 IDELAY,可用于實現過采樣器,這種過采樣器僅利用極少的 FPGA 邏輯資源,而更重要的是,進行 8 倍過采樣只需一個 DCM 和兩個全局時鐘資源。與使用多個 DCM的技術相比,這種解決方案可提供更高的抖動容限。

如果配以適當的數據恢復方案,就可以將本文所述的過采樣技術用于多種不同的數據協議,在Virtex-5 器件中采樣率可達 550 Mb/s,而在 Virtex-4 器件中可達 500 Mb/s。我們舉例說明如何使用這種技術,用參考設計實現一個以 270 Mb/s 運行的 SD-SDI (SMPTE 259M) 接收器。

過采樣技術

使用過采樣的異步串行數據恢復技術要求接收器對輸入的比特流快速采樣,其速度足以在每個位周期中采集多個樣本。這種采樣方法可提供有關比特流的足夠信息,從而可以確定位轉換的位置,并且保證每個位的采樣點都靠近位中心而遠離轉換區。

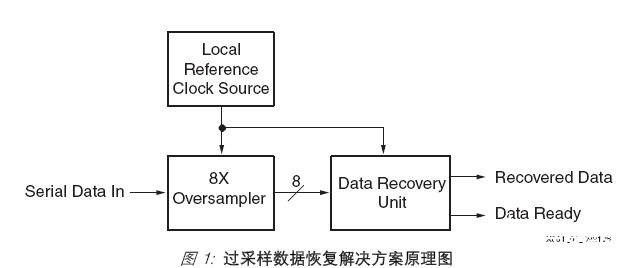

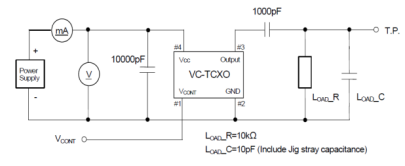

圖1 所示為一典型異步串行數據過采樣數據接收器。此接收器由兩大部分組成:過采樣器和數據恢復單元 (DRU)。過采樣器在每個位周期對比特流進行多次采樣,采集足夠多數據傳輸給DRU。DRU 必須在每個位周期中取得足夠的樣本,以便確定發生位轉換的位置,然后在距離轉換區安全的位置對各個位進行采樣。通常,過采樣器在每個位周期中能向 DRU 提供的樣本越多,DRU 對位轉換發生位置的判斷就越準確,對數據的恢復也越精確。每個位周期取得較多樣本可以提高 DRU 的抖動容限。

有多種方法可以在 Xilinx FPGA 中實現過采樣器。可以將 RocketIO 收發器用作過采樣器,在某些情況下以 1 Gb/s 或更高比特率進行過采樣。實際上,一些 RocketIO 收發器內置了過采樣接收器(稱為數字接收器),所支持的比特率低于普通接收器。

在用 SelectIO 輸入端接收異步串行比特流時,通常限制最大可支持比特率的是 FPGA 的最大時鐘速率,而非 IOB 所支持的最大速率。因為過采樣器必須在每個位周期內對比特流多次采樣,所以采樣時鐘必須明顯快于比特率。使用采樣時鐘的多個時鐘相位,即可在不提高時鐘頻率的情況下增加每個位周期的樣本數量,但是這種方法需要以某種方式精確地生成并分配多個時鐘相位,而且會用盡多個全局時鐘布線資源。例如,使用相互間隔 45 度的四個時鐘相位,并且使用各時鐘相位的兩個邊沿,就可以保證 8 倍過采樣的基本時鐘頻率與比特率相同。

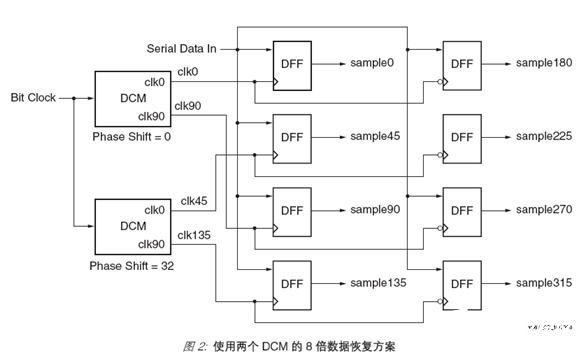

可以用 DCM 為串行輸入的過采樣創建多個時鐘相位(參見 XAPP224 中的圖2)。不過,根據時鐘頻率和每個位周期樣本數不同,可能需要多個 DCM 才能提供足夠的時鐘相位。如果使用多個 DCM,這些 DCM 的輸出就會在相互間產生相對抖動,這樣就會降低采樣點的精確性,從而降低接收器的抖動容限。圖2 中使用的方案還要求與四個時鐘相位對應的四個全局時鐘。不過,如果所有比特率都相同,就可用這四個全局時鐘來支持多個過采樣器。

Xilinx 針對是否符合 SD-SDI 協議對多時鐘相位過采樣器進行了實驗;因為支持的電纜長,這種協議要求位轉換之間的行程長,抖動容限高。這些實驗顯示,任何低于 6X SD-SDI 比特流的過采樣都無法提供足夠的抖動容限,而 8 倍過采樣是較為現實的下限。如圖2 所示,使用四個時鐘相位的 8 倍過采樣方案需要兩個 DCM。Xilinx 的實驗顯示,這兩個 DCM 在時鐘相位上產生的相對抖動將 DRU 的抖動容限降到了無法接受的程度。如果可以只使用一個 DCM,那么就能減輕時鐘相位抖動問題,但仍然需要四個全局時鐘。一個 Virtex-5 PLL 就可以生成四個低抖動的時鐘相位,但仍需四個全局時鐘將這四個時鐘相位傳送到過采樣器。Virtex-4 器件不具備這種 PLL。

使用 IDELAY實現高效過采樣

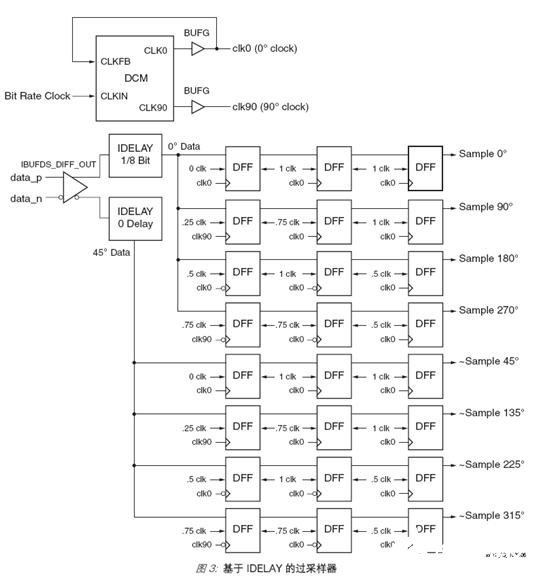

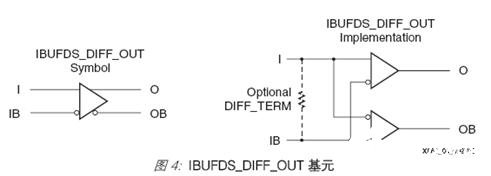

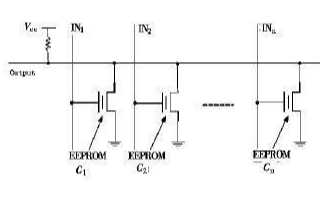

圖3 所示為基于 IDELAY 的過采樣器。一個 DCM 用來創建間隔 90 度的兩個時鐘相位。使用這兩個時鐘相位的兩個邊沿,可以在一個位周期內給定四個間隔均等的采樣點。串行比特流通過稱為 IBUFDS_DIFF_OUT 的基元進入 FPGA。因為此基元僅支持 LVDS 輸入,所以串行數據必須為 LVDS 格式。一般的 LVDS 輸入基元只向 FPGA 提供一個信號,但 IBUFDS_DIFF_OUT 基元會將接收到的真實信號及其反轉信號都提供給 FPGA。如圖4 所示,IBUFDS_DIFF_OUT 使用兩個差分接收器,一個在 LVDS 對的 P 輸入 IOB 中,另一個在其 N 輸入 IOB。這些差分接收器各向 FPGA 提供一個信號,N 側 IOB 發出的信號與 P 側 IOB 提供的信號反相。

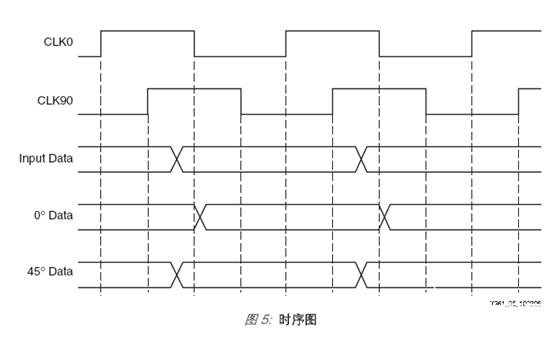

Virtex-4 和 Virtex-5 器件中的每個 IOB 都有一個 IDELAY 基元與之關聯。不過,由于IBUFDS_DIFF_OUT 緩沖器從 LVDS 對的兩個不同 IOB 提供兩個輸入信號副本,而這兩個比特流副本可經不同的 IDELAY 基元分別發送,這致使它們有不同的延遲量。IBUFDS_DIFF_OUT的 P 側提供的比特流真實副本被與其關聯的 IDELAY 延遲八分之一個位周期。用于IBUFDS_DIFF_OUT 反相輸出的 IDELAY 設置為零延遲。這兩個 IDELAY 模塊提供兩個不同的比特流“相位”。過采樣器用兩個時鐘相位的雙沿對這兩個比特流相位分別采樣,所以每個位周期可采集比特流八次,如圖5 所示。

乍看似乎奇怪的是,標為有零相移延遲的數據其實是來自有八分之一位周期延遲的 IDELAY 模塊,而標為有 45 度相移的數據卻是來自有零延遲的 IDELAY 模塊。但這是正確的。圖5 中的CLK0 說明了這一示例。比特流的兩個相位均在 CLK0 的上升時鐘沿采樣。從有八分之一位周期延遲的 IDELAY 采集的樣本代表比從有零延遲的 IDELAY 采集到的樣本“早”八分之一位周期的輸入數據。

還有一點可能看似奇怪的是,使用兩個 IDELAY,卻將其中一個設置為零延遲。但這樣做是為了確保兩個信號副本使用同等布線資源,從而盡量減輕數據信號兩個相位間的歪斜。

如第 4 頁圖3 所示,各樣本通過由三個觸發器構成的流水線送至主時鐘域(零度時鐘的上升沿)。第一觸發器是采樣觸發器,偶爾會因為比特流異步采樣而處于亞穩態。為了規避亞穩態引起的問題,本設計在流水線中第一與第二觸發器之間至少讓出四分之三時鐘周期,以便給第一觸發器留出時間在樣本被時鐘驅動進入第二觸發器之前穩定下來。當樣本被時鐘驅動進入流水線中第三觸發器時,樣本已送入主時鐘域,而且亞穩態已解除。

如果包括流水線中第一觸發器上的延遲量,任何樣本通過流水線的總延遲都恰好是兩個時鐘周期。以 315 度的樣本為例,第一觸發器使用 90 度時鐘的下降沿,所以為該觸發器被時鐘驅動四分之三時鐘周期。第一到第二觸發器的延遲是四分之三時鐘周期,而第二到第三觸發器的延遲是半個時鐘周期。加起來恰好是兩個時鐘周期。

與第 3 頁圖2 所示的雙 DCM 技術相比,這種基于 IDELAY 的過采樣技術在性能及資源使用方面都有優勢。顯然,這種技術少用了一個 DCM 和兩個全局時鐘。因為只使用一個 DCM,所以各時鐘相位之間相對更穩定。因為 IDELAY 基元不會加劇抖動,所以各數據相位之間相對抖動甚微。因此,這種過采樣技術可以提供更精準的可重復性比特流采樣,并且可以提高接收器的抖動容限。

IDELAY 基元可提供每 tap 78 ps 的高精度延遲。延遲值 6 提供 468 ps 的延遲,非常接近 270Mb/s 位周期的八分之一 (463 ps)。270 Mb/s 是視頻應用的常用比特率,在參考設計中用作示范比特率。

如果 FPGA 正在接收比特率相同的多個異步比特流,就可以用 DCM 提供的兩個全局時鐘相位作為時鐘來驅動所有比特流的過采樣器。因此,這種技術對于接收比特率相同的多個比特流非常有效。

第 4 頁圖3 中的 DCM 不能在進行時鐘乘法運算的同時提供兩個相隔 90 度的時鐘相位。因此,DCM 的輸入端需要一個比特率時鐘。不過,Virtex-5 器件時鐘管理管道中的 PLL 可以同時對輸入的時鐘進行乘法運算并提供兩個不同的時鐘相位,并且允許使用較低頻率的輸入參考時鐘。

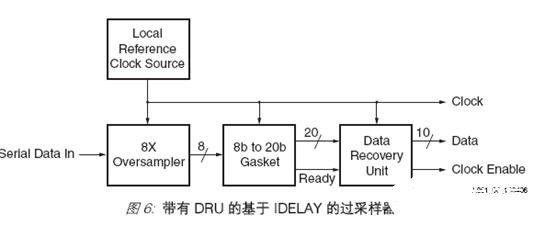

圖6 所示為連接至 DRU 的基于 IDELAY 的過采樣器設計。這種 DRU 支持 8 倍過采樣,當初的開發目的是在 RocketIO 收發器上用作過采樣器。由于這一原因,它預置一個 20 位的輸入矢量,所以就需要少量接口邏輯將采樣器的 8 位輸出端與 DRU 的 20 位輸入端銜接起來。DRU在其輸出端口生成 10 位的恢復數據字,同時生成一個信號,一旦數據字生效則該信號被置位。DRU 還可以生成 20 位的輸出字。

參考設計

可以從 http://www.xilinx.com/cn/bvdocs/appnotes/xapp861.zip 下載參考設計文件。

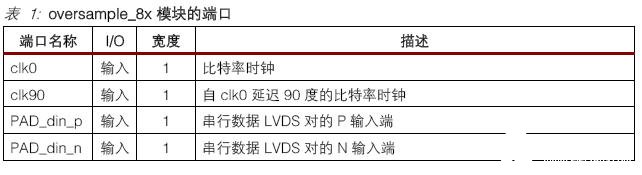

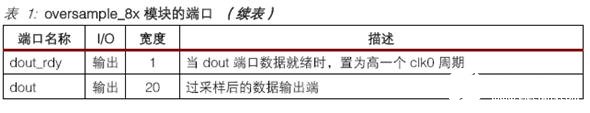

過采樣器模塊稱為 oversample_8x。其端口如表1 所示。

oversample_8x 模塊還接受一個稱為 IDELAY_45_DEGREES 的 Verilog 參數或 VHDL 類屬參數,其默認值為 6。此值設置 IDELAY 的延遲量,以便在數據上獲得一個 45 度的相移(八分之一位周期)。默認值 6 是對應 270 Mb/s 的正確 IDELAY 值 (78 ps * 6 ≈ (1 / 270 MHz) / 8)。如果比特率是 270 Mb/s 以外的其他值,就必須將 IDELAY_45_DEGREES 的正確值傳輸到該模塊。

在內部差分終端 (DIFF_TERM) 開啟的狀態下,用 IOSTANDARD 屬性值“LVDS_25”在oversample_8x 模塊內實例化 IBUFDS_DIFF_OUT 輸入緩沖器。如果應用要求不同的IOSTANDARD 屬性或者要求關閉差分終端,則必須修改在 oversample_8x 模塊中的IBUFDS_DIFF_OUT 緩沖器上設置的約束條件.IBUFDS_DIFF_OUT 只能用于 LVDS I/O 標準。

DRU 模塊稱為 os48_1011x20bTo10b_top2。其端口如表2 所示。名稱以 A/B 開頭的所有端口實際上都是雙端口,其中一個對應 A 通道,另一個對應 B 通道。

DRU 的 A_recclk 和 B_recclk 端口必須由連接到各自 oversample_8x 模塊 clk0 輸入端口的同樣的比特率時鐘驅動。過采樣器的 dout 和 dout_rdy 端口分別驅動 DRU 的 A/B_din20b 和A/B_en 端口。

為 DRU 正確指定信號位順序至關重要。DRU 有兩個位順序輸入端,一個指定 DRU 輸入數據的位順序,另一個指定 DRU 輸出數據的位順序。不能獨立地指定 DRU 兩個通道的位順序。

10 位和 20 位輸出端口均由 DRU 提供。兩個端口始終處于活動狀態,應用可選擇使用任一個。各通道的 10 位和 20 位端口各有其輸出使能,通常用作對下游邏輯的時鐘使能。在典型應用中,驅動 oversample_8x 的 clk0 端口和 DRU 的 A/B_recclk 端口的比特率參考時鐘用作接收器中下游邏輯的時鐘,如解碼器、成幀器和查錯器等。當 DRU 的輸出端口上有新的恢復數據字時,用 DRU 的時鐘使能輸出僅在這些時鐘周期上啟用下游邏輯。

模塊 FPGA 資源的利用

表3 所示為實現完整的 8 倍過采樣單元和數據恢復單元所需的 FPGA 資源。DRU 基于 BlockRAM。因為 Xilinx FPGA 中的 Block RAM 有雙端口,所以 DRU 設計可以處理兩個異步數據流。這樣,同樣數量的 Block RAM 既可以處理一個異步通道,也可以處理兩個異步通道。在Virtex-4 器件中,無論 DRU 處理一個還是兩個通道,都需要有兩個 RAMB16 Block RAM。在Virtex-5 器件中,DRU 需要一個半 RAMB36 Block RAM (一個 RAMB18,一個 RAMB36)。

表3 中的結果是用 ISE8.2 獲得的,其 XST 設置為面積優化,串行比特率為 270 Mb/s。在Virtex-4 和 Virtex-5 FPGA 的最低速度級別下,如果將 XST 設置為面積優化則有可能滿足比特率為 270 Mb/s 的時序。

時序

IDELAY 基元的粒度為 78 ps。因此,由于 78 ps 的粒度與本技術要求的八分之一位周期延遲剛好相符,有些比特率值相對于其他值就會更適合這一技術。例如,比特率為 270 Mb/s 時,八分之一位周期約為 463 ps,而 6 * 78 ps 為 468 ps。因此,使用延遲值 6 會使 IDELAY 對信號的延遲量非常接近八分之一位周期。

這種技術不能用于 DCM 的 CLKFX 輸出端。其主要原因是,時鐘相位的抖動要盡可能低,而DCM 的 CLKFX 輸出端的抖動要遠遠高于 CLK0 和 CLK90 輸出端。在 Virtex-5 器件中,也可以用時鐘管理管道中的 PLL 提供這兩個時鐘相位。

重要的是,要妥善約束 DRU 和下游邏輯的時序。這通常需要多周期時序約束,因為所用時鐘是比特率時鐘,而 DRU 和下游邏輯則往往通過使用時鐘使能而在字速率下運行。兩個不同的時鐘使能被用到,因此必須給予妥善約束。

過采樣器對 DRU 的 A_en 或 B_en 輸入生成一個時鐘使能 (dout_rdy),以使其僅當準備好向DRU 輸入 20 位過采樣數據時 DRU 才會被時鐘驅動。如果過采樣器的實例名為 OVRSAMPLE,則使用以下約束指明每 20 個時鐘(稱為“sclk”)周期 DRU 輸入才會被時鐘驅動一次:

NET “sclk” TNM_NET = BIT_CLK;

TIMESPEC TS_BIT_CLK = PERIOD BIT_CLK 270 MHz HIGH 50 %;

NET “OVRSAMPLE/period《0》” TNM = DRU_IN_CE;

TIMESPEC TS_DRU_IN_CE = FROM DRU_IN_CE TO DRU_IN_CE BIT_CLK / 20;

串行時鐘的 PERIOD 約束是以頻率給定,從而使時鐘使能的 TIMESPEC 等于串行時鐘的TIMESPEC 除以 20。如果串行時鐘的 PERIOD 約束是以周期而非頻率給定,則時鐘使能的TIMESPEC 必須等于串行時鐘的 TIMESPEC 乘以 20。

另一個時鐘使能由 DRU 在其使能輸出端生成。DRU 有四個輸出端使能,每通道兩個。在每通道兩個輸出端使能中,一個對應于 10 位的輸出,另一個對應于 20 位的輸出。10 位的輸出端口使能(A_dout10bEn 或 B_dout10bEn)平均每 10 個串行時鐘周期被置位一次。不過,因為實際數據比特率對于串行時鐘為異步,所以在 10 位輸出端使能的各次置位之間偶爾會有 9 或11 個時鐘周期。實際上,DRU 也可以在 10 位輸出端使能的各次置位之間生成短至 5 個時鐘周期的數據字。因此,對于由 DRU 時鐘使能輸出端驅動的邏輯,應該以所希望的最小時序編寫其多周期時序約束。如果使用 DRU 的 10 位時鐘使能輸出端,并且信號名為“rx_ce”,那么以下時序約束可以妥善約束由 rx_ce 信號啟用的 DRU 下游的任何邏輯。有必要在 Verilog 或VHDL 代碼中對來自 DRU 的時鐘使能信號應用一個 KEEP 約束,以使時鐘使能將源代碼保持為其給定的名稱,從而可以在用戶約束文件 (UCF) 中使用同樣的名稱。

NET “rx_ce” TNM = RXCE;

TIMESPEC TS_RXCE = FROM RXCE TO RXCE BIT_CLK / 5;

位置約束

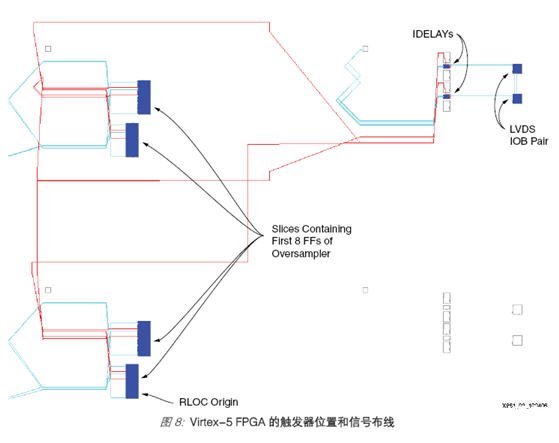

要從過采樣器中獲得良好性能,重要的是應將第一組的八個觸發器(即直接從 IDELAY 基元輸出端采集數據的觸發器)放置在盡量靠近 IDELAY 基元處,并且從兩個 IDELAY 基元到八個觸發器的布線對于所有八個觸發器來說應盡量相同。過采樣器模塊應設計成允許在約束文件中放置一個 RLOC 起點,以約束這第一組的八個觸發器。應將 RLOC 起點設置成使觸發器在 CLB中的位置盡可能緊靠 IDELAY 基元的左側,因為這樣放置可提供最直接的信號布線。如果不可能將觸發器置于 IDELAY 基元的左側,可以將其放在緊靠其右側的位置,只是性能會稍有降低。

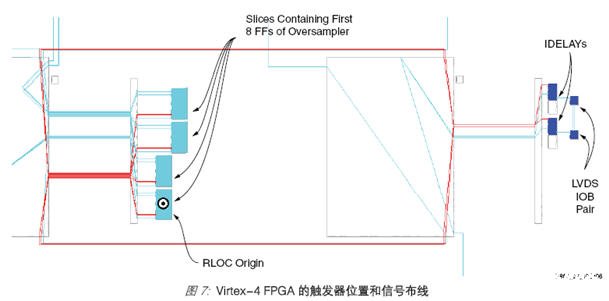

圖7 所示為觸發器緊靠 IDELAY 基元左側的 Virtex-4 器件。圖中以紅色表示從兩個 IDELAY 基元到觸發器的數據信號布線。

XAPP861 (v1.0) 2006 年 10 月 13 日www.xilinx.com/cn 11

R 以下約束顯示如何將設計中的兩個 oversample_8x 模塊分別指定給不同的 U_SET,以及如何對其指定 RLOC_ORIGIN 約束,以將其置于各自 IOB 的旁邊。在本示例中,兩個oversample_8x 模塊的實例名分別為 OVRSAMPLE1 和 OVRSAMPLE2。

INST “OVRSAMPLE1” U_SET=USET_OVR1;

INST “OVRSAMPLE1” RLOC_ORIGIN = X0Y24;

INST “OVRSAMPLE2” U_SET=USET_OVR2;

INST “OVRSAMPLE2” RLOC_ORIGIN = X50Y24;

結論

本文所述技術使用 Virtex-4 和 Virtex-5 器件中各 IOB 內置的 IDELAY 資源來實現用于異步串行比特流的高效高性能8倍過采樣器。當用多個 DCM 生成時鐘相位時,這種技術可以提供比多時鐘相位法更高的采樣精度。因為 IDELAY 資源可以為各比特流提供更多采樣點,所以只需一個 DCM 和兩個全局時鐘即可提供對以同樣比特率運行的任意數量的異步比特流進行 8 倍采樣所需的所有時鐘。

責任編輯:gt

電子發燒友App

電子發燒友App

評論