ASIC和FPGA具有不同的價(jià)值主張,在作出選擇前必須仔細(xì)評(píng)估。兩種種技術(shù)對(duì)比。這里介紹了ASIC和FPGA 的優(yōu)勢(shì)與劣勢(shì)。

2011-03-31 17:30:09 5382

5382

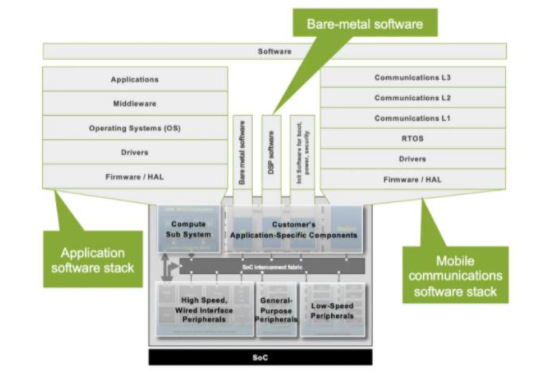

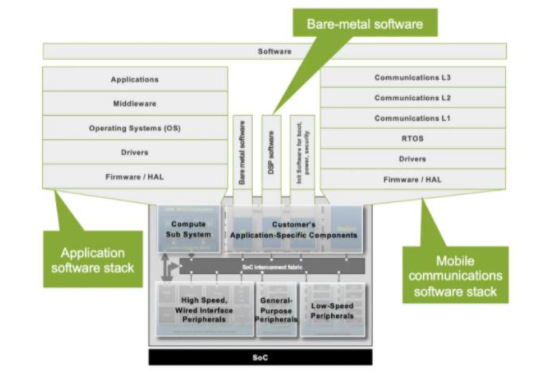

什么是FPGA原型?? FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過(guò)將RTL移植到現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)來(lái)驗(yàn)證專(zhuān)門(mén)應(yīng)用的集成電路(ASIC),專(zhuān)用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能

2022-07-19 16:27:29 1735

1735 FPGA原型在數(shù)字芯片設(shè)計(jì)中非常重要,因?yàn)橄啾扔梅抡嫫鳎蛘呒铀倨鞯葋?lái)跑仿真,FPGA的運(yùn)行速度,更接近真實(shí)芯片,可以配合軟件開(kāi)發(fā)者來(lái)進(jìn)行底層軟件的開(kāi)發(fā)。這一流片前的軟硬件的協(xié)同開(kāi)發(fā),是其最不可替代的地方。

2023-05-10 10:44:00 4791

4791

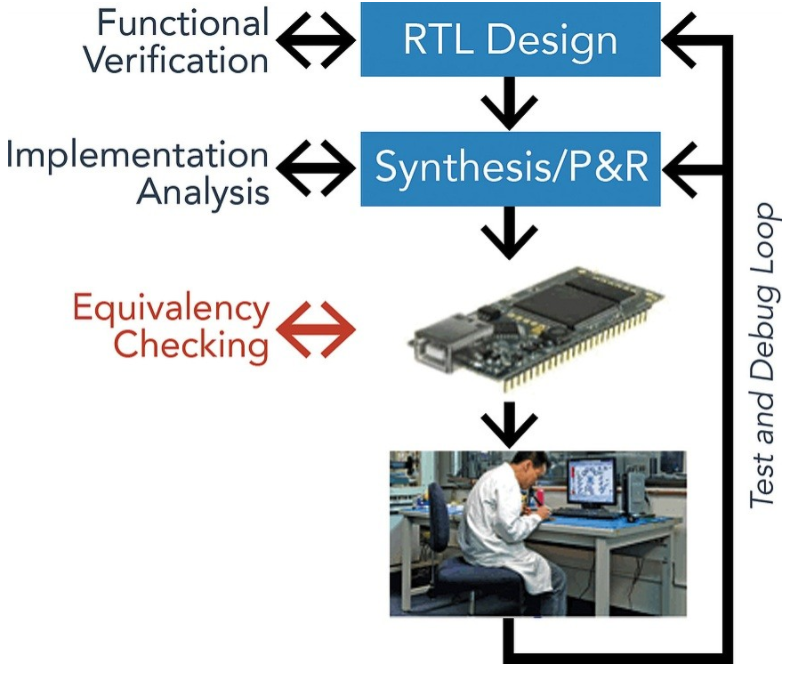

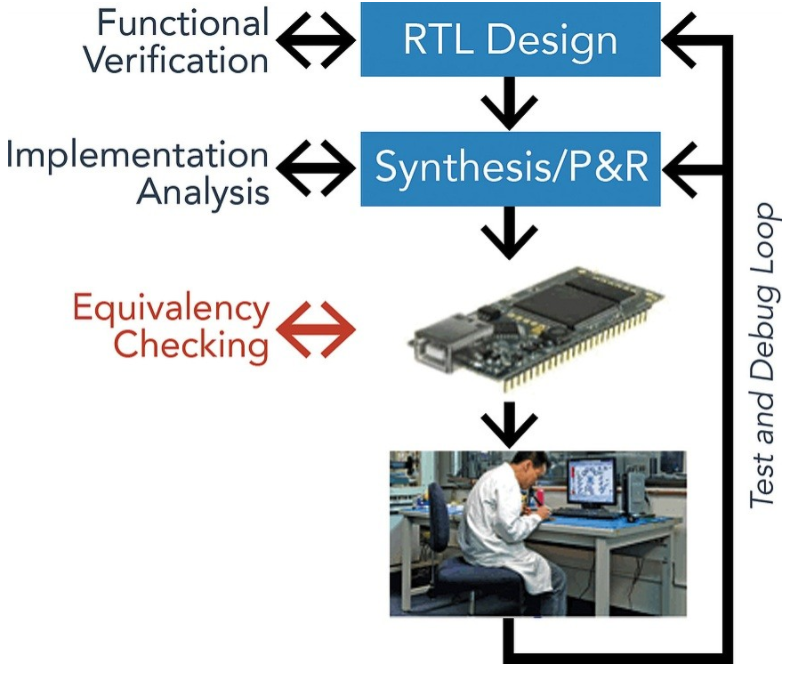

ASIC的設(shè)計(jì)流程是怎樣的?FPGA的開(kāi)發(fā)流程又是怎樣的?

2021-11-01 07:08:47

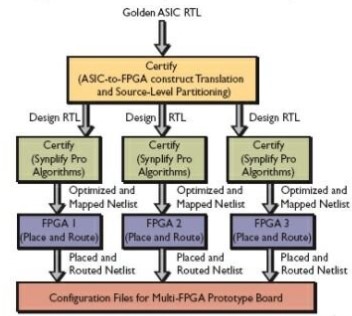

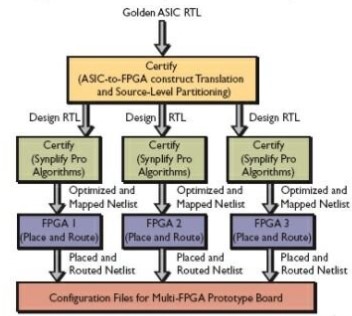

原型驗(yàn)證過(guò)程中的ASIC到FPGA的代碼是怎樣進(jìn)行轉(zhuǎn)換的?

2021-05-08 09:16:18

原型驗(yàn)證---用軟件的方法來(lái)發(fā)現(xiàn)硬件的問(wèn)題 在芯片tap-out之前,通常都會(huì)計(jì)算一下風(fēng)險(xiǎn),例如存在一些的嚴(yán)重錯(cuò)誤可能性。通常要某個(gè)人簽字來(lái)確認(rèn)是否去生產(chǎn)。這是一個(gè)艱難的決定。ASIC的產(chǎn)品NRE

2019-07-11 08:19:24

。 ASIC在離開(kāi)生產(chǎn)線后再也無(wú)法改變。這就是為什么設(shè)計(jì)師在大規(guī)模量產(chǎn)之前需要完全確保設(shè)計(jì)正確無(wú)誤。工程師可以利用FPGA的可重配置這一優(yōu)勢(shì),進(jìn)行ASIC的原型驗(yàn)證,以便在將設(shè)計(jì)發(fā)送到代工廠之前,可以在

2020-12-01 17:41:49

專(zhuān)用集成電路(ASIC)采用硬接線的固定模式,而現(xiàn)場(chǎng)可編程門(mén)陣列 (FPGA)則采用可配置芯片的方法,二者差別迥異。可編程器件是目前的新生力量,混合技術(shù)也將在未來(lái)發(fā)揮作用。 與其他技術(shù)一樣,有關(guān)

2019-07-19 06:24:30

講的很好,主要講解了廠商A和X兩個(gè)高端驗(yàn)證平臺(tái)。電子版,可以看看(中文)

2015-08-25 14:14:18

1ASIC 驗(yàn)證技術(shù).................................................11.1 ASIC 設(shè)計(jì)流程

2015-09-18 15:26:25

ASIC設(shè)計(jì)-FPGA原型驗(yàn)證

2020-03-19 16:15:49

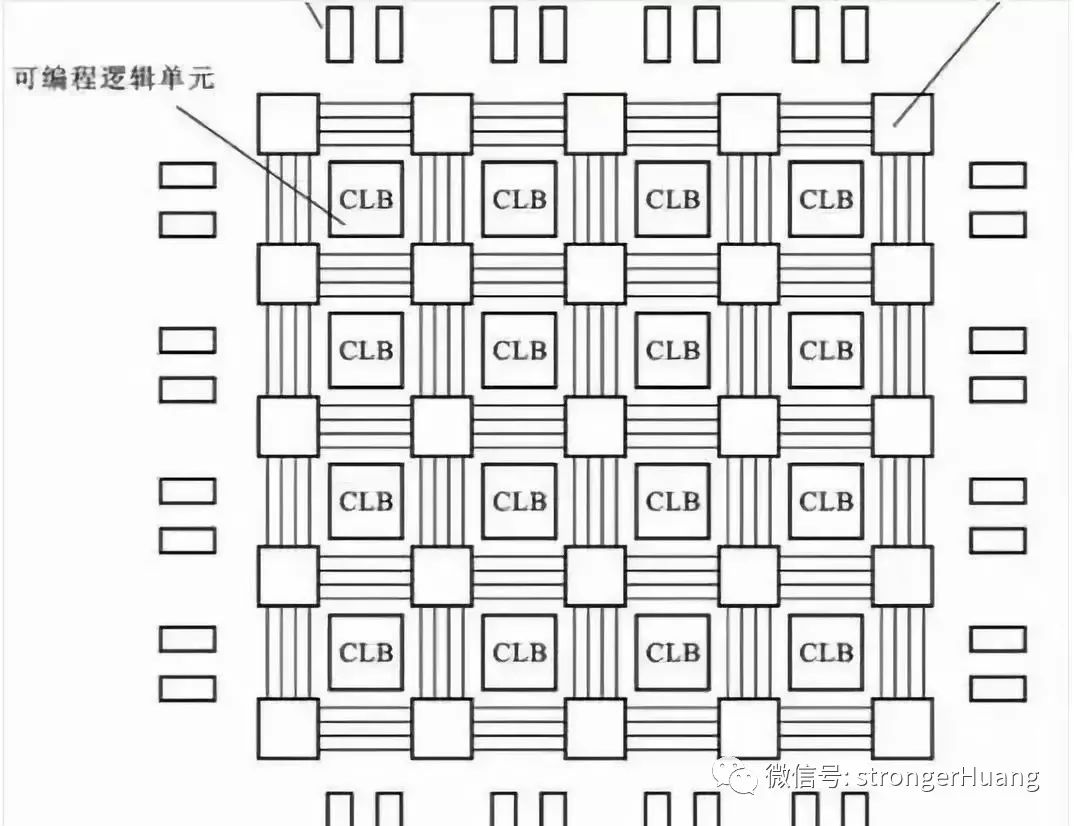

。ASIC 的特點(diǎn)是面向特定用戶的需求, ASIC 分為全定制和半定制。亮點(diǎn)在于專(zhuān)用,量身定制所以執(zhí)行速度較快。一句話總結(jié)就是,市場(chǎng)上買(mǎi)不到的芯片。水果的 A 系列處理器就是典型的 ASIC。二、FPGA

2020-09-25 11:34:41

。ASIC的特點(diǎn)是面向特定用戶的需求, ASIC分為全定制和半定制。亮點(diǎn)在于專(zhuān)用,量身定制所以執(zhí)行速度較快。一句話總結(jié)就是,市場(chǎng)上買(mǎi)不到的芯片。水果的A系列處理器就是典型的ASIC。FPGA是可復(fù)用

2017-09-02 22:24:53

ASIC是專(zhuān)用集成電路設(shè)計(jì),FPGA是可編程邏輯陣列,DSP和單片機(jī)(MCU?)是不是有點(diǎn)像?這四個(gè)我只接觸過(guò)FPGA,就是自己布置邏輯單元,可以使用IP核,最后下到開(kāi)發(fā)板驗(yàn)證。現(xiàn)在我想問(wèn):如果我要實(shí)現(xiàn)一個(gè)電子系統(tǒng),這四個(gè)方案有什么區(qū)別?鑒于天朝的本科其實(shí)沒(méi)講什么東西,所以到現(xiàn)在沒(méi)搞清。。。

2015-09-21 11:34:58

,如果出貨量大的話,工廠大規(guī)模生產(chǎn)玩具的成本會(huì)比用樂(lè)高積木做便宜許多。FPGA和ASIC也是如此,在同一時(shí)間點(diǎn)上用最好的工藝實(shí)現(xiàn)的ASIC的加速器的速度會(huì)比用同樣工藝FPGA做的加速器速度快5-10倍

2016-12-15 19:21:50

FPGA原型驗(yàn)證已是當(dāng)前原型驗(yàn)證的主流且成熟的芯片驗(yàn)證方法——它通過(guò)將RTL移植到現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)來(lái)驗(yàn)證ASIC的功能,并在芯片的基本功能驗(yàn)證通過(guò)后就可以開(kāi)始驅(qū)動(dòng)的開(kāi)發(fā),一直到芯片

2020-08-21 05:00:12

ASIC是一種為專(zhuān)門(mén)目的而設(shè)計(jì)的集成電路,是指應(yīng)特定用戶要求和特定電子系統(tǒng)的需要而設(shè)計(jì)、制造的集成電路。ASIC的特點(diǎn)是面向特定用戶的需求,亮點(diǎn)在于運(yùn)行速度在同等條件下比FPGA快。FPGA作為

2017-06-12 15:56:59

FPGA與ASIC(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書(shū)《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-10 11:34:28

FPGA設(shè)計(jì)驗(yàn)證關(guān)鍵要點(diǎn)不同于ASIC設(shè)計(jì),FPGA設(shè)計(jì)中的標(biāo)準(zhǔn)元件或客制化實(shí)作,一般欠缺大量的資源及準(zhǔn)備措施可用于設(shè)計(jì)驗(yàn)證。由于可以重新程式化元件,更多時(shí)候驗(yàn)證只是事后的想法。本文將探討在FPGA

2010-05-21 20:32:24

我已經(jīng)完成了我的fpga實(shí)現(xiàn),如何轉(zhuǎn)向asic實(shí)現(xiàn)?我們正在使用ieee_proposed。這項(xiàng)技術(shù)具體嗎?

2020-03-19 09:28:49

先進(jìn)的設(shè)計(jì)與仿真驗(yàn)證方法成為SoC設(shè)計(jì)成功的關(guān)鍵。一個(gè)簡(jiǎn)單可行的SoC驗(yàn)證平臺(tái),可以加快SoC系統(tǒng)的開(kāi)發(fā)與驗(yàn)證過(guò)程。FPGA器件的主要開(kāi)發(fā)供應(yīng)商都針對(duì)自己的產(chǎn)品推出了SoC系統(tǒng)的開(kāi)發(fā)驗(yàn)證平臺(tái),如

2019-10-11 07:07:07

。HAPS-51采用FPGA陣列Xilinx Virtex-5 LX330和板上存儲(chǔ)器,加快了ASIC驗(yàn)證的速度。先前的HAPS系統(tǒng)在存儲(chǔ)器存取方面采用子板,而最新的HAPS-51則采用位于板上并靠近

2018-11-20 15:49:49

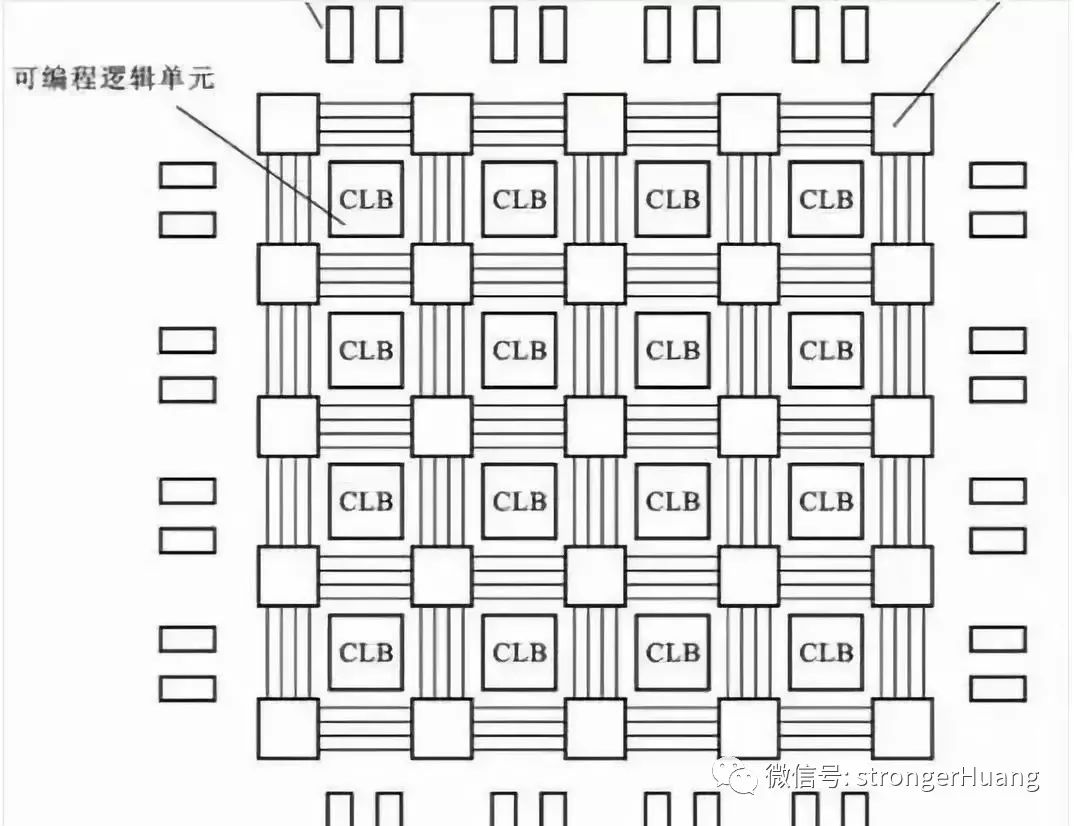

多種配置模式:并行主模式為一片FPGA加一片EPROM的方式;主從模式可以支持一片PROM編程多片FPGA;串行模式可以采用串行PROM編程FPGA;外設(shè)模式可以將FPGA作為微處理器的外設(shè),由微處理器

2012-02-27 17:46:03

[導(dǎo)讀]什么是FPGA,單片機(jī),DSP,ASIC?你真的知道嗎?ASIC原本就是專(zhuān)門(mén)為某一項(xiàng)功能開(kāi)發(fā)的專(zhuān)用集成芯片,比如你看攝像頭里面的芯片,小小的一片,集成度很低,成本很低,可是夠用了。一個(gè)山寨

2021-07-16 08:13:27

落,特別是在具有稀疏性的網(wǎng)絡(luò)中,門(mén)控時(shí)鐘是最簡(jiǎn)單易行的降低功耗的做法。FPGA對(duì)這一特點(diǎn)的弱支持將導(dǎo)致原型驗(yàn)證可能存在不完整性問(wèn)題。除此之外,多時(shí)鐘域的問(wèn)題在FPGA的原型驗(yàn)證也是一個(gè)問(wèn)題,由于FPGA

2023-03-28 11:14:04

的設(shè)計(jì)驗(yàn)證步驟,大概只有ASIC流程的50%-70%。最頭大的流片過(guò)程,FPGA是不需要的。

這就意味著,開(kāi)發(fā)ASIC,可能需要幾個(gè)月甚至一年以上的時(shí)間。而FPGA,只需要幾周或幾個(gè)月的時(shí)間。

剛才說(shuō)到

2024-01-23 19:08:55

中國(guó)通信網(wǎng)絡(luò)設(shè)備廠商華為正在其部分產(chǎn)品中或采用ASIC以取代Altera的FPGA。這項(xiàng)進(jìn)展將影響Altera的銷(xiāo)售,并可能打擊“FPGA正在取代ASIC傳統(tǒng)地位”頗具爭(zhēng)議性的說(shuō)法。華為首次采用ASIC到底會(huì)對(duì)Altera的銷(xiāo)售有何影響?FPGA和ASIC之間的拉鋸戰(zhàn)到底誰(shuí)的勝算更大?

2019-09-17 06:26:40

如何會(huì)加快32的運(yùn)行速度

2023-11-06 07:58:24

我的設(shè)計(jì)完全在Verilog中,并且已經(jīng)使用Spartan FPGA進(jìn)行了測(cè)試。我將源代碼提供給ASIC工廠,以實(shí)現(xiàn)作為ASIC使用他們(我認(rèn)為)的概要工具。我的問(wèn)題是,有沒(méi)有辦法使用任何

2019-07-25 13:44:31

ASIC驗(yàn)證能夠采用的主要技術(shù)是什么?如何利用現(xiàn)成FPGA開(kāi)發(fā)板進(jìn)行ASIC原型開(kāi)發(fā)?

2021-05-08 07:51:04

可編程門(mén)陣列FPGA具有可編程特性,用戶根據(jù)特定的應(yīng)用定制電路結(jié)構(gòu),因此其處理速度大大超過(guò)通用處理器。與ASIC相比,FPGA的缺點(diǎn)是在提供靈活的可編程同時(shí),則以芯片的面積、功耗和速度做為代價(jià)。

2019-09-03 07:44:22

較慢的CPU,將NN的FPGA實(shí)現(xiàn)與GPU / NPU和ASIC的實(shí)現(xiàn)進(jìn)行一下對(duì)比。事實(shí)證明,FPGA的獨(dú)特優(yōu)勢(shì)在于其可重新配置能力。這也解釋了為什么目前很多學(xué)術(shù)資源研究如何將FPGA高效地用于NN

2023-02-08 15:26:46

隨著基于FPGA進(jìn)行原型設(shè)計(jì)的復(fù)雜性不斷增加,市場(chǎng)對(duì)更好調(diào)試技術(shù)的需求也日益增加。FPGA原型設(shè)計(jì)可用于驗(yàn)證、早期軟件開(kāi)發(fā)、概念證明等,因此變得非常重要。它的主要職責(zé)仍然是執(zhí)行這些任務(wù),而不是試圖找出因原型構(gòu)建錯(cuò)誤而造成的問(wèn)題。

2019-09-27 07:05:17

設(shè)計(jì)周期,提高設(shè)計(jì)質(zhì)量。現(xiàn)場(chǎng)可編程門(mén)陣列FPGA具有可編程特性,用戶根據(jù)特定的應(yīng)用定制電路結(jié)構(gòu),因此其處理速度大大超過(guò)通用處理器。與ASIC相比,FPGA的缺點(diǎn)是在提供靈活的可編程同時(shí),則以芯片的面積、功耗和速度做為代價(jià)。

2019-07-29 08:33:45

浮點(diǎn)是最優(yōu)選的數(shù)據(jù)類(lèi)型,可確保算法建模和仿真的高精度計(jì)算。傳統(tǒng)上,當(dāng)您想要將這種浮點(diǎn)算法部署到FPGA或ASIC硬件時(shí),您唯一的選擇是將算法中的每種數(shù)據(jù)類(lèi)型轉(zhuǎn)換為定點(diǎn),以節(jié)省硬件資源并加快計(jì)算速度

2018-09-11 21:59:16

在過(guò)去10年間,全世界的設(shè)計(jì)人員都討論過(guò)使用ASIC或者FPGA來(lái)實(shí)現(xiàn)數(shù)字電子設(shè)計(jì)的好處。通常這些討論將完全定制IC的性能優(yōu)勢(shì)和低功耗與FPGA的靈活性和低NRE成本進(jìn)行比較。設(shè)計(jì)隊(duì)伍應(yīng)當(dāng)在ASIC

2019-07-15 07:00:39

。基于FPGA的原型驗(yàn)證方法憑借其速度快、易修改、真實(shí)性的特點(diǎn),已經(jīng)成為ASIC芯片設(shè)計(jì)中重要的驗(yàn)證方法[2].本文主要描述高頻RFID芯片的FPGA原型驗(yàn)證平臺(tái)的設(shè)計(jì),并給出驗(yàn)證結(jié)果。

2019-06-18 07:43:00

。基于FPGA的原型驗(yàn)證方法憑借其速度快、易修改、真實(shí)性的特點(diǎn),已經(jīng)成為ASIC芯片設(shè)計(jì)中重要的驗(yàn)證方法。本文主要描述高頻RFID芯片的FPGA原型驗(yàn)證平臺(tái)的設(shè)計(jì),并給出驗(yàn)證結(jié)果。1、RFID芯片的FPGA

2019-05-29 08:03:31

ASIC 芯片全定制費(fèi)用高、風(fēng)險(xiǎn)大、周期長(zhǎng),因此在全定制之前一般先用FPGA 或CPLD 等可編程邏輯器件做功能驗(yàn)證。但在一些空間極為有限、成本極低的應(yīng)用場(chǎng)合,采用FPGA 或者CPLD 顯然

2009-09-25 16:00:32 12

12 ASIC和FPGA設(shè)計(jì)中的多點(diǎn)綜合技術(shù)

盡管在技術(shù)發(fā)展的每一個(gè)時(shí)刻做出精確的預(yù)言是困難的,但ASIC和FPGA所集成的門(mén)數(shù)仍象數(shù)年前INTEL的Gordon Monre預(yù)言的那樣平均每18個(gè)月增加一倍.

2010-06-19 10:05:09 11

11 FPGA原型驗(yàn)證和其他驗(yàn)證方法是不同的,任何一種其他驗(yàn)證方法都是ASIC驗(yàn)證中的一個(gè)環(huán)節(jié),而FPGA驗(yàn)證卻是一個(gè)過(guò)程。由于FPGA與ASIC在結(jié)構(gòu)、性能上各不相同,ASIC是基于標(biāo)準(zhǔn)單元庫(kù),FPGA用的

2010-09-10 17:22:26 989

989 對(duì)ASIC設(shè)計(jì)進(jìn)行FPGA原型驗(yàn)證時(shí),由于物理結(jié)構(gòu)不同,ASIC的代碼必須進(jìn)行一定的轉(zhuǎn)換后才能作為FPGA的輸入。 現(xiàn)代集成電路設(shè)計(jì)中,芯片的規(guī)模和復(fù)雜度正呈指數(shù)增加。尤其在ASIC設(shè)計(jì)流程中

2011-03-25 15:16:20 108

108 MathWorks 近日宣布推出 HDL Coder,該產(chǎn)品 支持MATLAB 自動(dòng)生成 HDL 代碼,允許工程師利用廣泛應(yīng)用的 MATLAB 語(yǔ)言實(shí)現(xiàn) FPGA 和 ASIC 設(shè)計(jì)。

2012-03-07 09:27:18 2033

2033

本文描述ASIC驗(yàn)證方法和過(guò)程,有助于ASIC設(shè)計(jì)者對(duì)驗(yàn)證的認(rèn)識(shí)。模擬是驗(yàn)證ASIC并產(chǎn)生測(cè)試矢量的唯一途徑,設(shè)計(jì)者可以對(duì)ASIC芯片或者在ASIC應(yīng)用系統(tǒng)中進(jìn)行功能和時(shí)序模擬。

2012-05-24 09:32:47 23

23 本文描述ASIC驗(yàn)證方法和過(guò)程,有助于ASIC設(shè)計(jì)者對(duì)驗(yàn)證的認(rèn)識(shí)。模擬是驗(yàn)證ASIC并產(chǎn)生測(cè)試矢量的唯一途徑,設(shè)計(jì)者可以對(duì)ASIC芯片或者在ASIC應(yīng)用系統(tǒng)中進(jìn)行功能和時(shí)序模擬。

2012-05-24 09:32:47 27

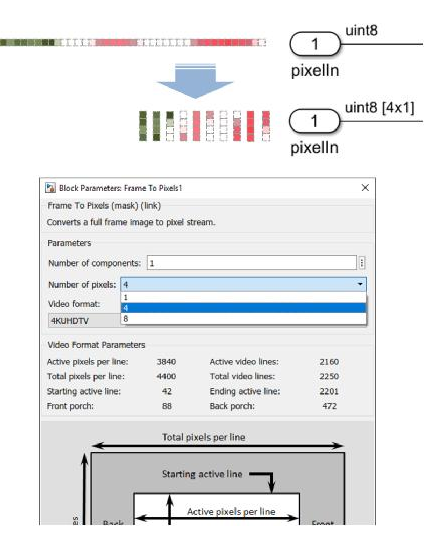

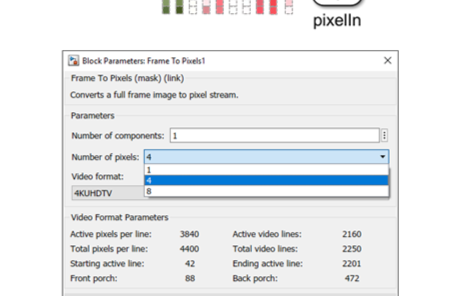

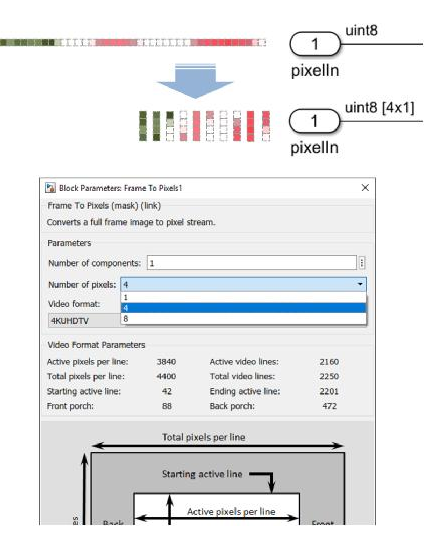

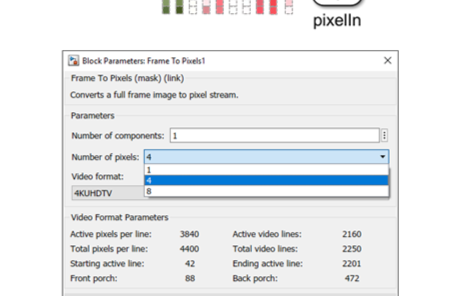

27 MathWorks 引入像素流處理算法,針對(duì)在FPGA和 ASIC上進(jìn)行視覺(jué)系統(tǒng)設(shè)計(jì)和實(shí)現(xiàn)。新的 Vision HDL Toolbox 縮短了從概念到設(shè)計(jì)的周期,并能在開(kāi)發(fā)流程早期發(fā)現(xiàn)設(shè)計(jì)錯(cuò)誤。

2015-05-07 17:24:02 1184

1184 在這個(gè)簡(jiǎn)短的網(wǎng)絡(luò)研討會(huì)上,來(lái)自 ?MathWorks?? 的工程師演示了如何使用 MATLAB? 、 Simulink?? 和 ?HDL Coder?? 實(shí)現(xiàn)和驗(yàn)證高性能 ?FFT (針對(duì)

2017-02-09 02:26:11 268

268 的 Release 2015a 中推出。Vision HDL Toolbox 為在 FPGA和 ASIC上進(jìn)行視覺(jué)系統(tǒng)設(shè)計(jì)和實(shí)現(xiàn)提供了像素流處理算法。該工具箱還包括一個(gè)靈活的設(shè)計(jì)框架,可支持一組多樣化

2017-02-09 04:17:11 185

185 ?7200? 萬(wàn)個(gè) ?ASIC? 門(mén)的容量。 FPGA? 原型設(shè)計(jì)系統(tǒng)通過(guò)添加多達(dá) ?3? 個(gè)附加電路板,可使用 ?Aldec? 背板 ?(HES7-BPx4)? 擴(kuò)展至 ?28800? 萬(wàn)個(gè) ?ASIC? 門(mén)。 了解更多 ??

2017-02-09 06:27:08 327

327 FPGA原型驗(yàn)證和其他驗(yàn)證方法是不同的,任何一種其他驗(yàn)證方法都是ASIC驗(yàn)證中的一個(gè)環(huán)節(jié),而FPGA驗(yàn)證卻是一個(gè)過(guò)程。

2017-02-11 12:46:11 2975

2975 電子系統(tǒng)設(shè)計(jì)人員使用FPGA來(lái)實(shí)現(xiàn)他們的原型開(kāi)發(fā),利用器件的可編程能力驗(yàn)證硬件和軟件。一旦設(shè)計(jì)準(zhǔn)備好進(jìn)行量產(chǎn)時(shí),設(shè)計(jì)人員尋找某類(lèi)ASIC以達(dá)到功耗、性能和成本目標(biāo),特別是,能夠提供硬件平臺(tái)和工具包的ASIC,支持目前采用了FPGA的設(shè)計(jì)

2017-10-14 10:18:11 4

4 ASIC 和 FPGA 具有不同的價(jià)值主張,選擇其中之一之前,一定要對(duì)其進(jìn)行仔細(xì)評(píng)估。2種技術(shù)的比較信息非常豐富。這里介紹了ASIC和FPGA的優(yōu)勢(shì)與劣勢(shì)。

2017-11-25 09:24:44 4374

4374 可容納2600萬(wàn)個(gè)ASIC門(mén),結(jié)合ProtoCompiler設(shè)計(jì)自動(dòng)化和調(diào)試軟件,可支持高達(dá)16億個(gè)ASIC門(mén)的設(shè)計(jì)。HAPS硬件與ProtoCompiler軟件的結(jié)合,極大地加速了軟件開(kāi)發(fā)、硬件/軟件集

2018-07-10 10:42:00 2067

2067 近年來(lái),ASIC設(shè)計(jì)規(guī)模的增大帶來(lái)了前所未有的芯片原型驗(yàn)證問(wèn)題,單顆大容量的FPGA通常已不足以容下千萬(wàn)門(mén)級(jí)、甚至上億門(mén)級(jí)的邏輯設(shè)計(jì)。現(xiàn)今,將整個(gè)驗(yàn)證設(shè)計(jì)分割到多個(gè)采用最新工藝大容量FPGA中,FPGA通過(guò)高速總線互聯(lián),成為大規(guī)模ASIC或SOC原型驗(yàn)證的極佳選擇。

2018-07-02 08:20:00 1695

1695 在不太遙遠(yuǎn)的過(guò)去,對(duì)ASIC設(shè)計(jì)團(tuán)隊(duì)而言,在這類(lèi)情況下主要的解決方案就是在內(nèi)部建立他們自己的定制多個(gè)FPGA的原型開(kāi)發(fā)板。然而,今天,使用現(xiàn)成的多個(gè)FPGA原型開(kāi)發(fā)板——例如,由Synplicity

2019-05-16 08:07:00 2742

2742

有人認(rèn)為,除了人才短缺、開(kāi)發(fā)難度較大,相比未來(lái)的批量化量產(chǎn)的ASIC芯片,FPGA在成本、性能、功耗方面仍有很多不足。這是否意味著,在ASIC大爆發(fā)之際,FPGA將淪為其“過(guò)渡”品的命運(yùn)?

2018-08-29 17:46:00 936

936 采用fpga原型技術(shù)驗(yàn)證asic設(shè)計(jì),首先需要把asic設(shè)計(jì)轉(zhuǎn)化為fpga設(shè)計(jì)。但asic是基于標(biāo)準(zhǔn)單元庫(kù),fpga則是基于查找表,asic和fpga物理結(jié)構(gòu)上的不同,決定了asic代碼需要一定

2019-07-23 08:07:00 1923

1923

該視頻推出了一種電機(jī)控制設(shè)計(jì)流程,支持在Mathworks MATLAB環(huán)境中設(shè)計(jì)和仿真高級(jí)模型。

2018-11-30 06:13:00 3665

3665 在相當(dāng)長(zhǎng)的一段時(shí)間內(nèi),FPGA、ASIC、DSP三者不同的技術(shù)特征造就了它們不同的應(yīng)用領(lǐng)域,DSP在數(shù)字信號(hào)方面是絕對(duì)的霸主,ASIC是專(zhuān)業(yè)定制領(lǐng)域的牛人,而FPGA由于其價(jià)格高、功耗大,主要

2018-11-29 14:37:02 647

647

FPGA是可編程ASIC。 ASIC:專(zhuān)用集成電路,它是面向?qū)iT(mén)用途的電路,專(zhuān)門(mén)為一個(gè)用戶設(shè)計(jì)和制造的。

2018-12-15 09:58:46 5195

5195 FPGA變得比之前更加流行了。現(xiàn)在的FPGA不再只是查找表(LUT)和寄存器的簡(jiǎn)單組合了,它已經(jīng)成為系統(tǒng)探索的架構(gòu),以及驗(yàn)證未來(lái)ASIC設(shè)計(jì)架構(gòu)的橋梁。

2019-06-21 17:52:12 4895

4895 ASIC芯片一旦流片功能就無(wú)法改變,基本專(zhuān)片專(zhuān)用。而FPGA可配置特性就可以應(yīng)用在功能會(huì)改變的場(chǎng)合,例如,原型驗(yàn)證,ASIC設(shè)計(jì)過(guò)程中會(huì)使用到FPGA來(lái)進(jìn)行原型驗(yàn)證;功能升級(jí),在產(chǎn)品中采用FPGA實(shí)現(xiàn)一些業(yè)內(nèi)暫時(shí)還沒(méi)成熟的解決方案,可以在后續(xù)功能變動(dòng)時(shí)方便升級(jí)。

2019-08-25 10:40:01 10934

10934

隨著處理器被添加到傳統(tǒng)FPGA中,可編程性被添加到ASIC中,FPGA和ASIC的分界線日益模糊。FPGA變得比之前更加流行了。

2019-10-18 15:01:51 2550

2550 發(fā)布了基于該FPGA的ASIC和SoC原型設(shè)計(jì)與驗(yàn)證系統(tǒng)的詳細(xì)信息。 proFPGA quad Intel? Stratix? 10 GX 10M FPGA 原型設(shè)計(jì)系統(tǒng)集成了四個(gè)基于英特爾Stratix 10

2019-12-06 15:09:14 2144

2144 FPGA vs. ASIC 你看好誰(shuí)?

2020-01-15 16:10:22 4104

4104 Vision HDL Toolbox 自動(dòng)生成經(jīng)過(guò) FPGA 驗(yàn)證的代碼,適用于高達(dá) 8k 分辨率的幀尺寸和高幀率視頻

2020-02-27 14:04:29 614

614

上處理高幀率 (HFR) 和高分辨率視頻的原生多像素流處理支持。視頻、圖像處理和 FPGA 設(shè)計(jì)工程師在處理 240fps 或更高分辨率的 4k 或 8k 視頻時(shí)可以加快權(quán)衡表現(xiàn)和實(shí)現(xiàn)的探索和仿真速度。

2020-03-01 12:40:38 725

725 Wilson Research Group 的一項(xiàng)最近研究發(fā)現(xiàn),48% 的 FPGA 設(shè)計(jì)項(xiàng)目和 71% 的 ASIC設(shè)計(jì)項(xiàng)目依賴 UVM 進(jìn)行設(shè)計(jì)驗(yàn)證。

2020-03-02 18:12:24 1019

1019 MathWorks宣布,隨著 2019b 發(fā)行版的 MATLAB 和 Simulink 產(chǎn)品系列最近上市,Vision HDL Toolbox提供對(duì)在 FPGA 上處理高幀率 (HFR) 和高分辨率視頻的原生多像素流處理支持。

2020-05-09 10:55:41 331

331

電子技術(shù)行業(yè)里面的攻城師們應(yīng)該對(duì)ASIC、FPGA和單片機(jī)這些名字都不陌生,但我相信并不是所有人都清楚ASIC和FPGA之間的區(qū)別和關(guān)系,下面我們分幾個(gè)方面去理清一下他們之間的瓜葛糾紛吧!

2020-06-04 11:36:11 5697

5697 RISC-V的發(fā)展速度比我預(yù)期的要快得多。我認(rèn)為這將給FPGA帶來(lái)一個(gè)巨大的機(jī)會(huì),使其可以更多地蠶食ASIC和ASSP。大多數(shù)SoC在通往ASIC的路上都要使用到FPGA,首先使用基于FPGA的仿真

2020-06-09 15:34:54 3709

3709 根據(jù)威爾遜研究集團(tuán)和西門(mén)子EDA的數(shù)據(jù),即使在EDA工具的研發(fā)上花費(fèi)了數(shù)十億美元,在驗(yàn)證人工上又花費(fèi)了數(shù)百億美元,但只有30%到50%的ASIC設(shè)計(jì)是第一次正確的。 即便如此,這些設(shè)計(jì)仍然有bug

2021-02-27 11:01:44 1436

1436

本文是本人對(duì)xilinx XC7V系列FPGA用于ASIC前端驗(yàn)證遇到問(wèn)題的總結(jié),為自己記錄并分享給大家,如果有歧義或錯(cuò)誤請(qǐng)大家在評(píng)論里指出。

2021-01-12 17:31:44 9

9 FPGA_ASIC-MAC在FPGA中的高效實(shí)現(xiàn)(理士電源技術(shù)有限公司)-該文檔為FPGA_ASIC-MAC在FPGA中的高效實(shí)現(xiàn)講解文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-08-04 19:03:13 8

8 將ASIC設(shè)計(jì)移植到FPGA芯片中,對(duì)于大部分設(shè)計(jì)團(tuán)隊(duì)來(lái)講都是巨大的挑戰(zhàn)。主要體現(xiàn)在:ASIC的設(shè)計(jì)一般都非常大,往往需要做多FPGA芯片劃分;需要支持足夠的處理性能;需要保證其功能的正確性;需要保證移植前后的功能具有等價(jià)性。

2022-04-14 15:01:08 1780

1780 隨著 FPGA 變得越來(lái)越大和越來(lái)越復(fù)雜,它們的設(shè)計(jì)和功能驗(yàn)證趨向于 ASIC。在現(xiàn)代 FPGA 設(shè)計(jì)流程的先進(jìn)性的推動(dòng)下,這種趨勢(shì)現(xiàn)在正在擴(kuò)展到實(shí)現(xiàn)驗(yàn)證領(lǐng)域。EC 現(xiàn)在是該流程的必要組成部分,保留了 FPGA 生產(chǎn)過(guò)程中的固有效率。

2022-06-14 09:21:55 1081

1081

需要門(mén)級(jí)驗(yàn)證:FPGA 和 ASIC 一樣需要設(shè)計(jì)級(jí)驗(yàn)證。但是,FPGA 在門(mén)級(jí)不是細(xì)粒度的,因此它們不需要門(mén)級(jí)驗(yàn)證。您將每個(gè)門(mén)都放置在 ASIC 設(shè)計(jì)中,因此您需要驗(yàn)證每個(gè)門(mén)。

2022-06-20 16:13:05 2184

2184

ASIC設(shè)計(jì)服務(wù)暨IP研發(fā)銷(xiāo)售廠商智原科技(Faraday Technology Corporation,TWSE:3035)今日發(fā)布FPGA-Go-ASIC驗(yàn)證平臺(tái)。

2022-07-29 10:08:16 784

784 FPGA vs ASIC 相同點(diǎn) 都設(shè)計(jì)使用硬件描述語(yǔ)言(HDL),如VHDL或Verilog。但ASIC相比于FPGA開(kāi)發(fā)上,代碼風(fēng)格更為隨意,因?yàn)?b class="flag-6" style="color: red">FPGA是先有電路,后有代碼,ASIC是先有代碼

2022-11-28 10:30:13 771

771 FPGA要取代ASIC了,這是FPGA廠商喊了十多年的口號(hào)。可是,FPGA地盤(pán)占了不少,ASIC也依舊玩得愉快。那么,這兩位仁兄到底有啥不一樣呢?

2023-03-31 14:41:41 1138

1138

FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過(guò)將RTL移植到現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)來(lái)驗(yàn)證專(zhuān)門(mén)應(yīng)用的集成電路(ASIC),專(zhuān)用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 FPGA做IC的原型驗(yàn)證,速度大概跑多少?很多ASIC運(yùn)行主頻遠(yuǎn)遠(yuǎn)高于FPGA,仿真能cover住嗎?

2023-06-19 09:49:00 542

542

FPGA和ASIC作為數(shù)字電路的常見(jiàn)實(shí)現(xiàn)方式,其聯(lián)系和區(qū)別備受關(guān)注。本文將從FPGA和ASIC的基本概念入手,深入研究它們的區(qū)別與聯(lián)系,以幫助讀者更好地理解兩者的應(yīng)用場(chǎng)景和選擇方法。

2023-08-14 16:38:51 1583

1583 FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過(guò)將RTL移植到現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)來(lái)驗(yàn)證專(zhuān)門(mén)應(yīng)用的集成電路(ASIC),專(zhuān)用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2024-01-12 16:13:01 220

220

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論