IIC總線是PHILIPS公司開發(fā)的一種簡單、雙向、二線制、同步串行總線。它只需兩根線(串行時(shí)鐘線和串行數(shù)據(jù)線)即可在連接于總線上的器件之間傳送信息。該總線是高性能串行總線,具備多主機(jī)系統(tǒng)所需要的裁決和高低速設(shè)備同步等功能,應(yīng)用極為廣泛。

目前市場上雖然有專用IIC總線接口芯片,但是地址可選范圍小、性能指標(biāo)固定、功能單一、使用不方便。根據(jù)IIC總線的電氣特性及其通訊協(xié)議,采用ALteRA公司的FLEX10K系列ISP器件EPF10K10LC84-3可以方便地實(shí)現(xiàn)IIC總線的通訊接口,且具有高速、易調(diào)試、可以靈活地實(shí)現(xiàn)地在線配置等優(yōu)點(diǎn),同時(shí)大大地減少了系統(tǒng)的開發(fā)周期。

1、IIC總線的數(shù)據(jù)傳輸規(guī)范

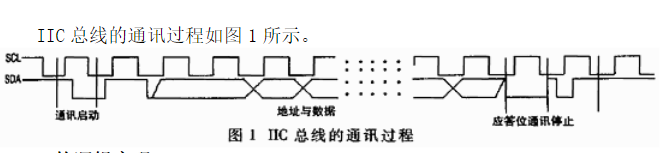

IIC總線主從機(jī)之間的一次數(shù)據(jù)傳送稱為一幀,由啟動信號、地址碼、若干數(shù)據(jù)字節(jié)、應(yīng)答位以及停止信號等組成。通訊啟動時(shí),主動發(fā)送一個(gè)啟動信號(當(dāng)SCL線上是高電平時(shí),SDA線上產(chǎn)生一個(gè)下降沿)、從機(jī)的地址碼(8位)和讀寫信號;通訊停止時(shí),主機(jī)發(fā)送一個(gè)停止信號(當(dāng)SCL線上是高電平時(shí),SDA線上產(chǎn)生一個(gè)上升沿)。在數(shù)據(jù)傳送過程中,當(dāng)SCL線上是高電平時(shí),必須保證SDA線上的數(shù)據(jù)穩(wěn)定;傳送一個(gè)字節(jié)的數(shù)據(jù),必須由接收機(jī)發(fā)一個(gè)應(yīng)答信號。總線的傳輸碼速率為100kbps(標(biāo)準(zhǔn))~400kbps(高速)。采用+5V電源供電時(shí),輸入電平規(guī)定為:VILmax=1.5V,VIHmin=3V;采用寬電源電壓時(shí),電平規(guī)定為:VILmax=1.5VDD,VIHmin=3VDD。

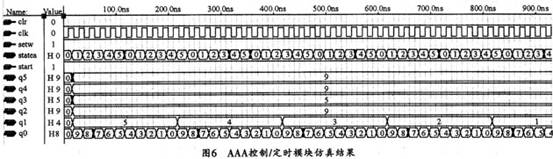

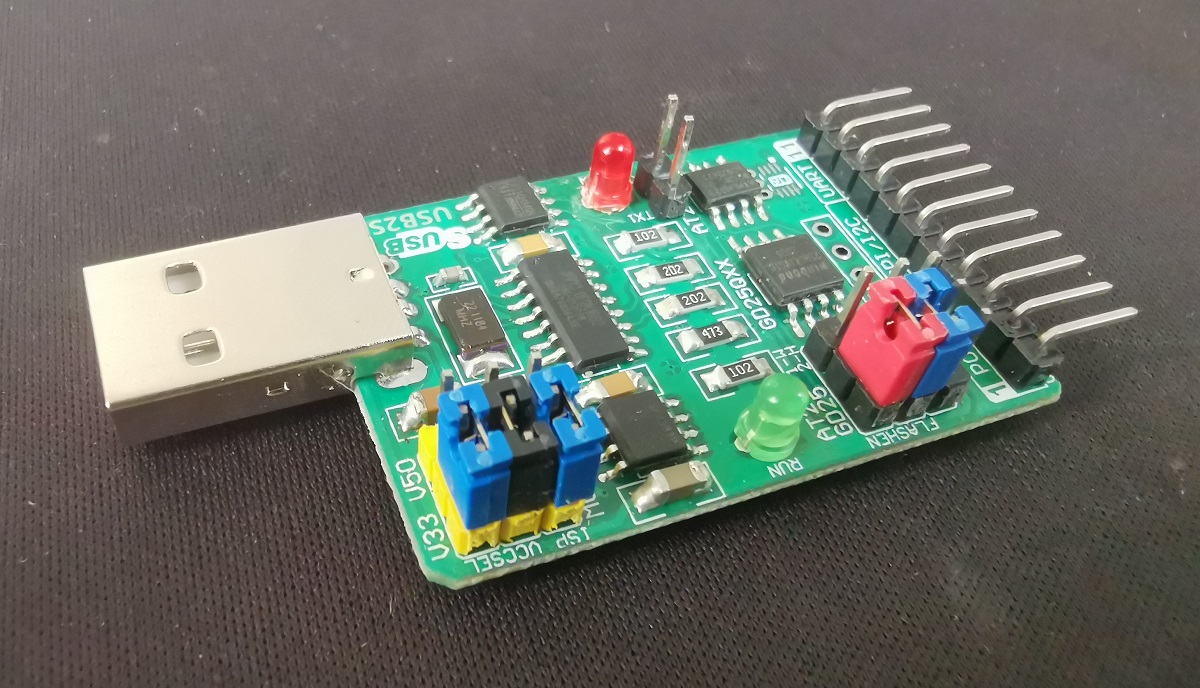

IIC總線的通訊過程如圖1所示。

2、ISP的邏輯實(shí)現(xiàn)

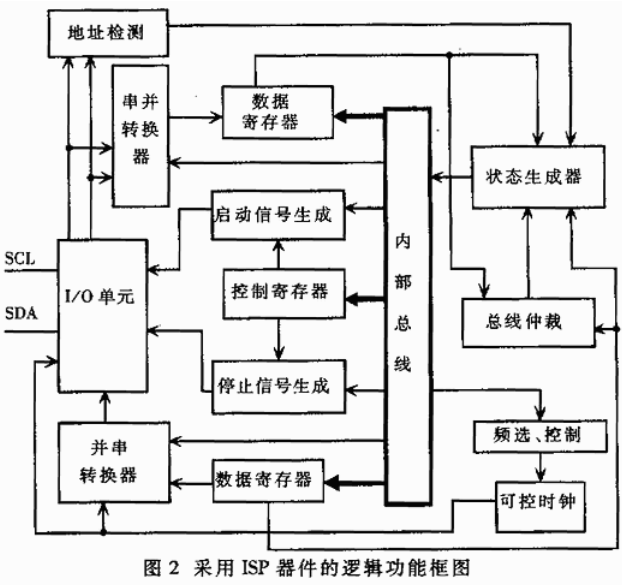

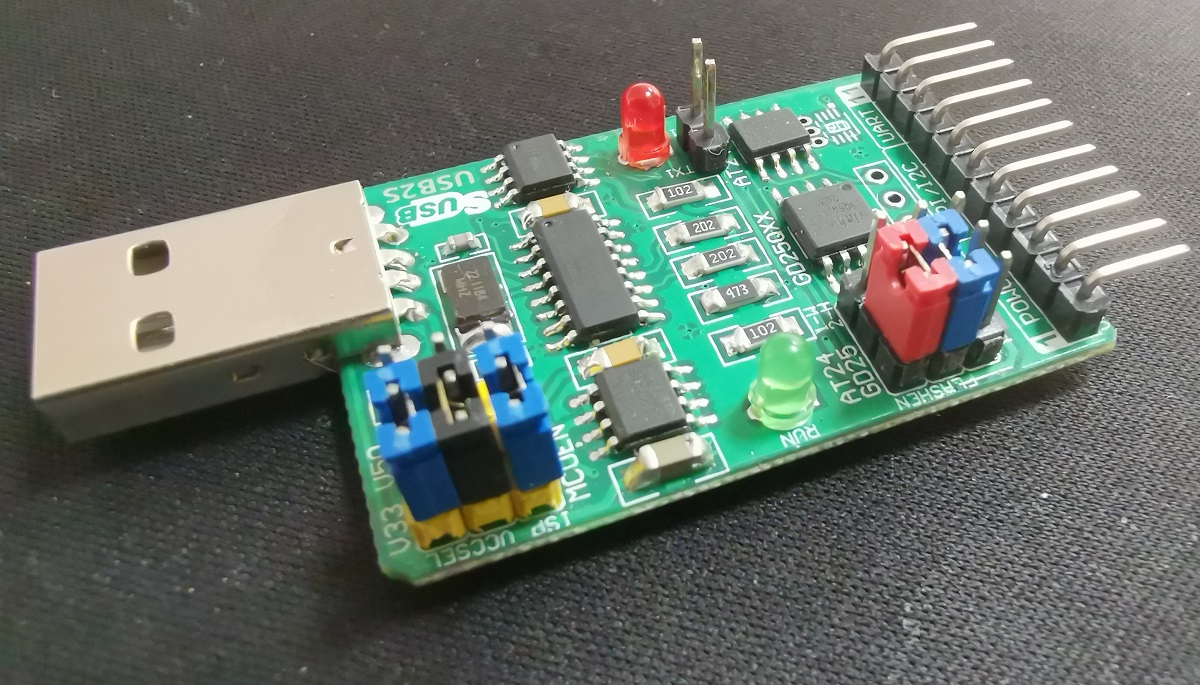

基于IIC總線的數(shù)據(jù)傳輸規(guī)范,為完成IIC總線的數(shù)據(jù)發(fā)送與接收,采用ISP器件實(shí)現(xiàn)通訊接口的邏輯功能框圖如圖2所示。通過頻選、控制、可控時(shí)鐘可獲得100kHz、200kHz、300kHz、400kHz的時(shí)鐘頻率。器件退出總線競爭后,時(shí)鐘線置高電平。

2.1 通訊的啟動與停止

在主機(jī)方式下,接收數(shù)據(jù)時(shí),ISP器件必須通過啟動信號生成器送出一個(gè)啟動信號,然后發(fā)送從機(jī)的地址信號和讀寫信號。只有這樣,才能在總線上發(fā)送數(shù)據(jù)。該過程由控制寄存器啟動。VHDL描述如下:

PROCESS(WR,CS)

——CS IS THIS CHIP‘S SELECT SIGNAL ADDRS:=’0‘;

IF(Ctrreg(0)=’1‘AND Ctrreg(3)=’1‘ AND SCL1=’1‘)THEN

——Ctrreg 為控制寄存器

CLK1COUNT:=’0‘;

SDA1:=’1‘;

IF(CLK1 EVENT AND CLK=’0‘)THEN

IF(CLK1COUNT=’3‘)THEN

SDA1:=’1‘;

ADDRS:=’1‘;

Ctrreg(3):=’0‘;

CSTA:=’1‘;

ELSE[page]

CLK1COUNT:=CLK1COUNT+1;

END IF;

END IF;

END IF;

IF(ADDRS=’1‘AND SCL1 ’EVENT AND SCL1=‘1’)THEN

························——將數(shù)據(jù)寄存器中的數(shù)據(jù)

························——及WR信號移位發(fā)出(略)

END IF;

END PROCESS;

當(dāng)一次通訊結(jié)束時(shí),主機(jī)要發(fā)送停止信號。該過程同樣同控制寄存器控制;當(dāng)控制字第二位為‘1’時(shí),ISP器件產(chǎn)生停止信號。VHDL描述與啟動類似。

2.2 發(fā)送數(shù)據(jù)

在主機(jī)方式下,完成啟動和地址信號發(fā)送后即開始發(fā)送數(shù)據(jù)。發(fā)送數(shù)據(jù)時(shí)并串轉(zhuǎn)換器在SCL的下降沿移位,保證SCL高電平時(shí)SDA上的數(shù)據(jù)穩(wěn)定。發(fā)送的進(jìn)程由WR信號和從機(jī)的應(yīng)答信號啟動。

當(dāng)ISP器件在總線競爭失敗時(shí),由處理器將ISP器件轉(zhuǎn)為從機(jī)工作方式,處理器向地址檢測電路送該器件在系統(tǒng)中的地址。只有在接收到的地址信息與該器件所設(shè)的地址相同時(shí),才發(fā)出應(yīng)答信號,開始通訊。每發(fā)送一個(gè)字節(jié)即將SDA拉高,等待接收機(jī)的應(yīng)答信號,準(zhǔn)備下一個(gè)數(shù)據(jù)。

2.3 接收數(shù)據(jù)

在主機(jī)方式下,完成通訊啟動和地址信號發(fā)送后便開始準(zhǔn)備接收數(shù)據(jù)。每接收一個(gè)字節(jié)后要發(fā)出應(yīng)答信號,產(chǎn)生一個(gè)負(fù)脈沖作為中斷請求信號輸出給處理器。若此時(shí)系統(tǒng)忙,則拉低SCL電平迫使發(fā)送機(jī)進(jìn)入等待狀態(tài)。從機(jī)方式下的接收與主機(jī)方式下一樣。VHDL描述如下:

PROCESS(SDA1)

SACK:=‘0’;

FULL1:=‘0’;

STP:=‘0’;

INTQ:=‘1’;

IF(CSTA=‘1’ AND ADDOK=‘1’)THEN

IF(SCL‘1’EVENT AND SCL1=‘0’)THEN

……——接收數(shù)據(jù),串入并出移位(略)

FULL1:=‘1’;

END IF;

END IF;

IF(FULL1=‘1’)THEN

IF(RD‘EVENT AND RD=’1‘AND

SCL1’EVENT AND SCL1=‘0 AND

BUSY=’0‘)THEN

SDA1:=’0‘;

FULL:=’0‘;

INTQ:=’0‘;

ELSE

SDA1:=’1‘;

IF(CLK1’EVENT AND CLK=‘0’ AND FULL1=‘0’)THEN

IF(CLK1COUNT‘20’)THEN

INTQ:=‘1’;

CLK1COUNT:=‘0’;[page]

ELSE

CLK1COUNT:=CLK1COUNT+1;

END IF;

END IF;

IF(SLAVE=‘1’ AND SCL=‘1’ AND SDA ‘EVENT AND SDA=’1‘)THEN

STP:=’1‘;

CSTA:=’0‘;

END IF;

END IF;

END PROCESS;

2.4 總線仲裁

在通訊過程中,ISP器件在發(fā)送數(shù)據(jù)的同時(shí)接收總線上的數(shù)據(jù),將該數(shù)據(jù)與已送的數(shù)據(jù)進(jìn)行比較,若不相同則置位狀態(tài)發(fā)生器的SLAVE,表示該主機(jī)退出競爭。通過處理給控制寄存器發(fā)送控制字可以讓ISP器件轉(zhuǎn)入從機(jī)工作方式。這時(shí)啟動地址檢測,禁止SCL的發(fā)送。在一次通訊結(jié)束后,將狀態(tài)生成器的END置位,此時(shí)處理器可以再次將ISP器件設(shè)置為主機(jī)方式。

2.5 控制寄存器與狀態(tài)生成器

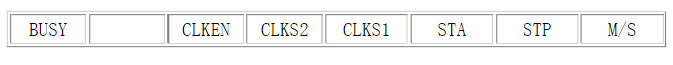

控制寄存器主要是定義ISP器件的工作狀態(tài),其各位的定義為:

BUSY:若該位為’1‘,主機(jī)作為接收機(jī)時(shí),不發(fā)應(yīng)答信號;

STA:啟動信號位;

STP:停止信號位;

M/S:主從機(jī)位,用于選擇芯片工作狀態(tài)(主機(jī)還是從機(jī));

CLKS1、CLKS2:頻選控制位;

CLKEN:SCL使能位,該位為1時(shí)SCL置高電平。

狀態(tài)生成器可以生成工作狀態(tài)信號(中斷、IIC總線競爭、從機(jī)方式時(shí)通訊開始與結(jié)束)供處理器查詢處理。

3、 參數(shù)配置

該器件可以配置為從100kbps(標(biāo)準(zhǔn))到400kbps(高速)的任何傳送速度,以滿足不同的需要。只需在VHDL(描述的結(jié)構(gòu)體中指明配置的參數(shù)即可實(shí)現(xiàn)配置,非常方便。

本設(shè)計(jì)只使用一片可編程芯片即可完成IIC總線接口的芯片功能。由于采用VHDL-93語言進(jìn)行設(shè)計(jì),具有良好的可移植性,可用于其它ISP廠家的產(chǎn)品中。通過ByteBlast下載線可以在線改變其功能,體現(xiàn)了ISP器件的優(yōu)越性。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論