介紹了一種基于CPLD技術(shù)的MOSFET器件保護(hù)電路的設(shè)計(jì)與實(shí)現(xiàn)。該電路設(shè)計(jì)方案具有抗干擾能力強(qiáng)、響應(yīng)速度快和通用性好的優(yōu)點(diǎn)。通過試驗(yàn)驗(yàn)證了該方案的正確性和可行性。##在功率MOSFET保護(hù)電路輸入

2014-04-25 11:15:47 1939

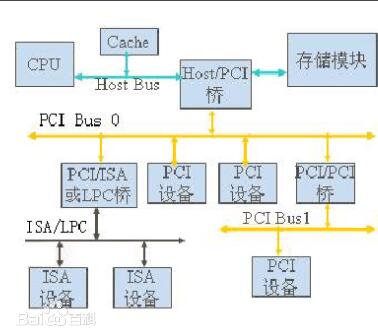

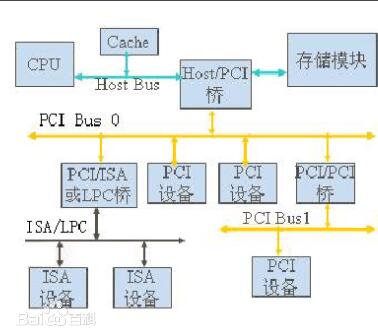

1939 本文主要詳解PCI總線與PXI總線有什么區(qū)別,首先介紹了PCI 總線結(jié)構(gòu)圖、特點(diǎn)及PCI總線性能,其次闡述了PXI總線的特性,最后介紹了PCI總線與PXI總線的區(qū)別。

2018-05-24 09:15:23 13959

13959

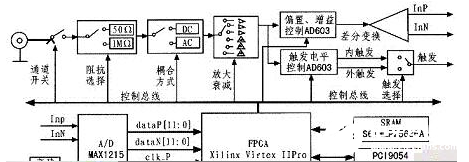

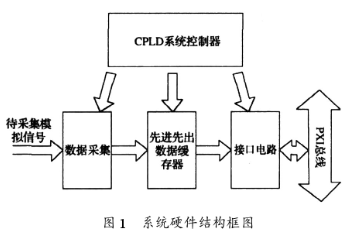

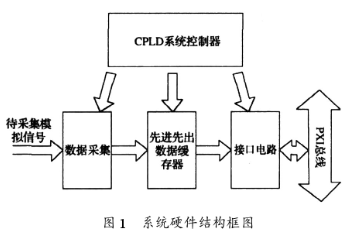

AD9054 高速A/D采集技術(shù)已在許多領(lǐng)域得到愈來愈廣泛的應(yīng)用,本文將詳細(xì)論述采用CPLD技術(shù)來實(shí)現(xiàn)120MHz高速A/D采集卡的設(shè)計(jì)方法,該采集卡具有包括負(fù)延遲觸發(fā)在內(nèi)的多種觸發(fā)方式,采用

2019-01-07 08:44:00 5713

5713

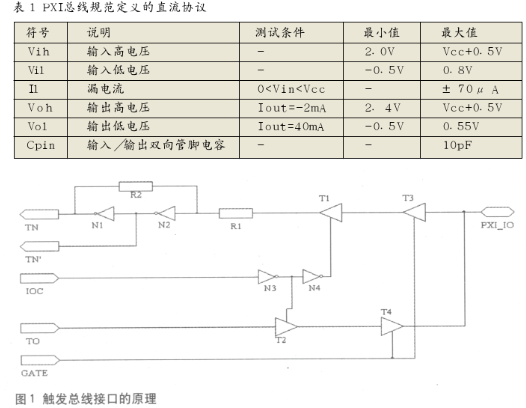

昨天帶大家認(rèn)識(shí)了PXI機(jī)箱之后,今天會(huì)詳細(xì)講解下關(guān)于PXI機(jī)箱的槽位號、背板、總線、電源、時(shí)鐘、觸發(fā)總線等相關(guān)的知識(shí)。歡迎持續(xù)關(guān)注~了解更多歡迎發(fā)郵件到ltt@hkaco.com

2021-12-31 06:04:56

cpld與8051的總線接口vhdl設(shè)計(jì)源碼cpld 與8051的總線接口VHDL源碼關(guān)于cpldbus51.VHD的說明: 很久之前我也想在網(wǎng)上找一份cpld與8051的總線方式接口的VHD源碼

2012-08-10 18:56:47

總線的電氣規(guī)范大部份跟PCI相同,只是增加了一些儀器特性。基于以上考慮,我們決定通過設(shè)計(jì)一個(gè)PCI接口卡來系統(tǒng)地了解利用接口芯片PCI 9030開發(fā)PXI模塊的過程和方法。2、硬件設(shè)計(jì)目前實(shí)現(xiàn) PCI

2019-05-05 09:29:33

的配置空間,可實(shí)現(xiàn)即插即用。這些優(yōu)點(diǎn)使得PCI總線在數(shù)據(jù)采集、嵌入式系統(tǒng)和測控等領(lǐng)域得到廣泛應(yīng)用。實(shí)現(xiàn)PCI總線協(xié)議目前主要有專用接口芯片和CPLD實(shí)現(xiàn)兩種方式。專用接口芯片使用簡單方便、工作穩(wěn)定可靠

2019-06-20 05:00:03

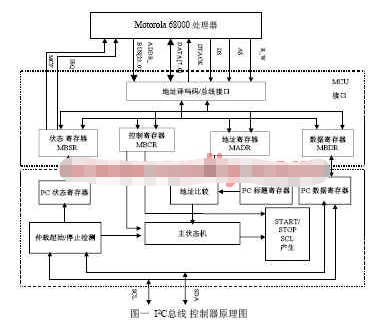

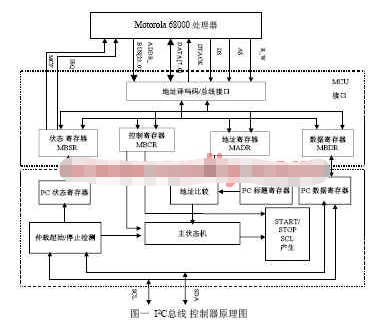

的QuartusII作為設(shè)計(jì)工具,以EPM7128系列的CPLD芯片實(shí)現(xiàn)了上述的接口電路。其總體設(shè)計(jì)如圖2所示。其中,地址譯碼模塊負(fù)責(zé)對MCU的地址總線進(jìn)行譯碼,產(chǎn)生地址選通信號;控制信號模塊負(fù)責(zé)產(chǎn)生一些總的控制信號

2019-05-23 05:01:08

求一款以CPLD為控制核心的16位高精度數(shù)字電壓表設(shè)計(jì)方案

2021-04-13 06:59:40

、計(jì)數(shù)、總線接口等很多方面,在信號處理領(lǐng)域的應(yīng)用也非常活躍。MAX7000系列是ALTERA公司采用先進(jìn)的0.8μm CMOS EEPROM技術(shù)制造的高性能、高密度的CPLD[1]。MAX7000的結(jié)構(gòu)可

2019-05-31 05:00:03

、計(jì)數(shù)、總線接口等很多方面,在信號處理領(lǐng)域的應(yīng)用也非常活躍。MAX7000系列是ALTERA公司采用先進(jìn)的0.8μmCMOSEEPROM技術(shù)制造的高性能、高密度的CPLD[1]。MAX7000的結(jié)構(gòu)可完全

2019-06-05 05:00:14

IP核來實(shí)現(xiàn)PCI接口,利用基于PCI協(xié)議的IP核來實(shí)現(xiàn)PCI接口,這種設(shè)計(jì)開發(fā)速度較快,靈活性較好,但是IP核價(jià)格昂貴。采用FPGA實(shí)現(xiàn)PCI總線協(xié)議。采用CPLD/FPGA等可編程邏輯器件實(shí)現(xiàn)PCI

2019-05-30 05:00:02

核處理器NIOSⅡ作為系統(tǒng)的主控制器,結(jié)合ARINC429專用器件和其他外圍設(shè)備實(shí)現(xiàn)數(shù)據(jù)的收發(fā)功能。 ARI NC429接口板由數(shù)據(jù)收發(fā)、存儲(chǔ)器擴(kuò)展、監(jiān)控、PCI總線接口等模塊組成。NIOSⅡ控制

2019-04-26 07:00:08

INT3~I(xiàn)NT6的位置一樣。另外,其他一些通用的控制信號二者也盡量做到一致。 在接口電路中,盡量使用CPLD或FPGA器件,可根據(jù)不同外部系統(tǒng)的要求對器件進(jìn)行擦寫。4 I/O讀寫和中斷操作可移植性

2018-11-26 11:21:21

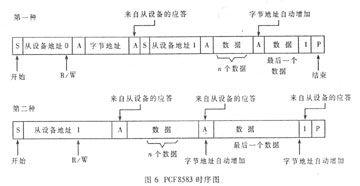

IIC總線通訊接口器件的CPLD實(shí)現(xiàn)摘要:介紹了采用ALTERA公司的可編程器件EPF10K10LC84-3實(shí)現(xiàn)IIC總線的通訊接口的基本原理,并給出了部分的VHDL語言描述。該通訊接口與專用的接口芯片相比,具有使用靈活、系統(tǒng)配置方便的特點(diǎn)。 [/hide]

2009-10-30 14:57:35

KPXI系列PXI總線產(chǎn)品架構(gòu)分析吉時(shí)利的混合測試解決方案是業(yè)界最先進(jìn)的PXI和測試設(shè)備混合結(jié)構(gòu),通過分布式編程和并行執(zhí)行能夠極大地加快測試時(shí)間。本文介紹的內(nèi)容是一個(gè)在較大系統(tǒng)中使用KPXI產(chǎn)品的參考方案。

2009-12-08 14:48:53

寄存器和器件相關(guān)寄存器。圖1為接口功能結(jié)構(gòu)圖。 2.1 VXI總線接口譯碼電路 VCPLD是可由用戶進(jìn)行編程實(shí)現(xiàn)所需邏輯功能的數(shù)字集成電路,它具有高性能、高集成度、高度靈活適用等諸多優(yōu)點(diǎn)。使用CPLD

2018-11-27 11:48:33

規(guī)范上強(qiáng)制增加了環(huán)境性能測試與主動(dòng)冷卻裝置,以簡化系統(tǒng)集成并確保不同廠商產(chǎn)品之間的互用性。此外,PXI還在高速PCI總線的基礎(chǔ)上補(bǔ)充了測量與自動(dòng)化系統(tǒng)專用的定時(shí)與觸發(fā)特性。 總的來說,PXI是一種堅(jiān)固

2009-06-22 18:51:23

分享一種智能卡接口的設(shè)計(jì)方案

2021-05-27 06:01:19

的結(jié)構(gòu)體中指明配置的參數(shù)即可實(shí)現(xiàn)配置,非常方便。本設(shè)計(jì)只使用一片可編程芯片即可完成IIC總線接口的芯片功能。由于采用VHDL-93語言進(jìn)行設(shè)計(jì),具有良好的可移植性,可用于其它ISP廠家的產(chǎn)品中。通過ByteBlast下載線可以在線改變其功能,體現(xiàn)了CPLD中的ISP器件的優(yōu)越性。

2019-05-22 05:00:02

、計(jì)數(shù)、總線接口等很多方面,在信號處理領(lǐng)域的應(yīng)用也非常活躍。MAX7000系列是ALTERA公司采用先進(jìn)的0.8μm CMOS EEPROM技術(shù)制造的高性能、高密度的CPLD[1]。MAX7000的結(jié)構(gòu)

2018-12-14 10:57:58

(Digital Signal Processor)與CPLD的連接是通過DSP的外部存儲(chǔ)器接口實(shí)現(xiàn)的。我們通過/IS管腳將其擴(kuò)展到外部I/O空間,數(shù)據(jù)總線的高8位和地址總線的低8位與CPLD相連,并且我們將

2019-05-21 05:00:16

求大佬分享一種基于CPLD的USB總線的隔離接口實(shí)現(xiàn)方案

2021-04-13 06:25:30

,使用CPLD器件可以極大地縮短產(chǎn)品開發(fā)周期,給設(shè)計(jì)修改帶來很大方便[1]。本文以ALTERA公司的MAX7000系列為例,實(shí)現(xiàn)MCS51單片機(jī)與PC104ISA總線接口的并行通信。采用這種通信方式,數(shù)據(jù)傳輸準(zhǔn)確

2019-06-20 05:00:02

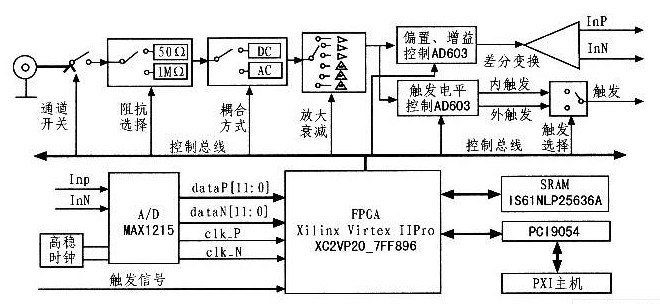

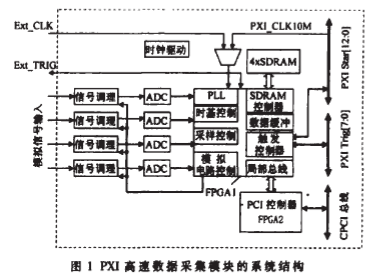

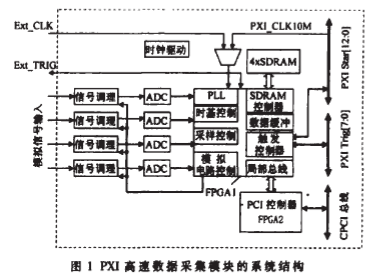

NB6L16差分接收器,其接收的最高信號頻率可達(dá) 6 GHz。 2.3 PXI總線接口電路設(shè)計(jì) 專用PCI接口芯片加CPLD/FPGA的接口方案,采用專用接口芯片PCI9030雖沒有像直接采用

2012-12-17 11:59:09

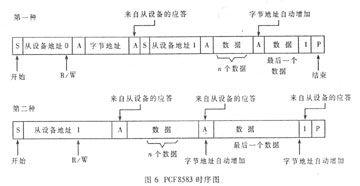

用電器、通訊設(shè)備及各類電子產(chǎn)品中已廣泛應(yīng)用DSP芯片。但大多數(shù)的尚未提供I2C總線接口,本文將介紹一種基于CPLD的已實(shí)現(xiàn)的高速DSP的I2C總線接口方案。1 I2C通信協(xié)議I2C總線是一種用于IC器件之間

2018-12-03 15:17:53

獨(dú)立的配置空間,可實(shí)現(xiàn)即插即用。這些優(yōu)點(diǎn)使得PCI總線在數(shù)據(jù)采集、嵌入式系統(tǒng)和測控等領(lǐng)域得到廣泛應(yīng)用。實(shí)現(xiàn)PCI總線協(xié)議目前主要有專用接口芯片和CPLD實(shí)現(xiàn)兩種方式。專用接口芯片使用簡單方便、工作穩(wěn)定

2019-05-29 05:00:02

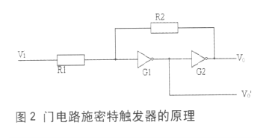

本文將詳細(xì)論述采用CPLD技術(shù)來實(shí)現(xiàn)120MHz高速A/D采集卡的設(shè)計(jì)方法,該采集卡具有包括負(fù)延遲觸發(fā)在內(nèi)的多種觸發(fā)方式,采用CPLD復(fù)雜可編程邏輯器件(又稱FPGA)EPM7128SQC100-7和AD公司的高速模數(shù)轉(zhuǎn)換器(A/D)AD9054BST-135來實(shí)現(xiàn)。

2021-04-30 06:27:01

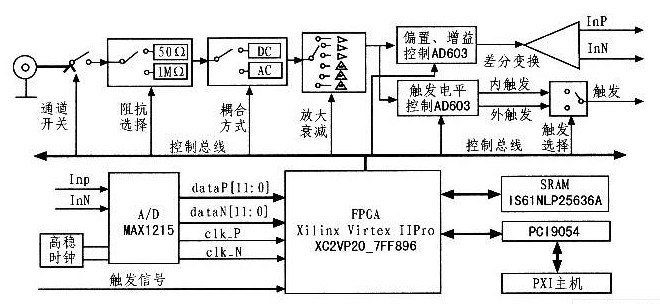

本文給出了基于PXI總線接口的高速數(shù)字化儀模塊的設(shè)計(jì)實(shí)現(xiàn)方法,介紹了高速數(shù)據(jù)采集系統(tǒng)中LVDS接口、LVPECL接口電路結(jié)構(gòu)及連接方式,并在所設(shè)計(jì)的數(shù)字化儀模塊中得到應(yīng)用。

2021-04-14 06:18:38

如何采用Altera的CPLD器件實(shí)現(xiàn)時(shí)間統(tǒng)一系統(tǒng)的B碼源設(shè)計(jì)?

2021-05-07 06:21:24

本設(shè)計(jì)采用了復(fù)雜可編程器件CPLD,用CPLD完成了PC104總線與429總線通訊的主要電路,大大節(jié)省了硬件資源,本文著重介紹了CPLD部分的設(shè)計(jì)。

2021-04-29 06:47:46

本文在對異步串行通信協(xié)議進(jìn)行分析的基礎(chǔ)上,根據(jù)實(shí)際工程的需要,對異步串行通信控制器進(jìn)行了詳細(xì)設(shè)計(jì),并結(jié)合CPLD器件,采用VHDL語言,對設(shè)計(jì)方案進(jìn)行了實(shí)現(xiàn)和驗(yàn)證,通過最后時(shí)序仿真的波形圖得出

2021-05-28 06:53:11

受到限制。因此,我們采用ALTERA公司的FPGA器件設(shè)計(jì)SPI總線的通信接口,該總線接口具有高速、配置靈活等優(yōu)點(diǎn),大大地縮短了系統(tǒng)的開發(fā)周期。

2019-08-09 08:14:34

PCI總線特點(diǎn)及開發(fā)現(xiàn)狀PCI接口配置空間的實(shí)現(xiàn)求一款在PCI總線上利用FPGA技術(shù)設(shè)計(jì)PCI總線接口的設(shè)計(jì)方案

2021-04-15 06:17:20

求一種DSP+CPLD新型的智能儀器的設(shè)計(jì)方案

2021-05-08 07:54:25

本文提出一種利用復(fù)雜可編程邏輯器件(Complex Programmable Logic Device,CPLD)設(shè)計(jì)技術(shù)[3]實(shí)現(xiàn)專用鍵盤接口芯片的方案。

2021-04-15 06:55:36

求一種基于USB總線的ARINC429總線接口模塊的設(shè)計(jì)方案。

2021-04-30 07:01:51

本文介紹了一種基于計(jì)算機(jī)總線的CPLD加密電路的設(shè)計(jì)方案。

2021-04-29 06:16:32

介紹采用ALTERA 公司的可編程器件,實(shí)現(xiàn)I2C 總線的通信接口的基本原理; 給出部分VHDL語言描述。該通信接口與專用的接口芯片相比, 具有使用靈活, 系統(tǒng)配置方便的特點(diǎn)。

2009-05-14 13:16:00 26

26 本文根據(jù)SPI 同步串行接口的通信協(xié)議,介紹了在CPLD 中利用VHDL 語言實(shí)現(xiàn)PC/104

總線擴(kuò)展SPI 接口的設(shè)計(jì)原理和編程思想。通過該方法的介紹,使得那些沒有SPI

接口功能的

2009-05-30 09:28:18 41

41 從自主研發(fā)的角度,介紹了一種以PXI 總線為接口,采用現(xiàn)場可編程門陣列(FPGA)為邏輯控制單元的數(shù)據(jù)采集系統(tǒng)。在介紹系統(tǒng)總體設(shè)計(jì)方案的基礎(chǔ)上,詳細(xì)討論了采集部分的功能實(shí)

2009-07-08 14:54:24 18

18 介紹了采用CPLD 實(shí)現(xiàn)DSP 芯片TMS320C6713 和背板VME 總線之間高速數(shù)據(jù)傳輸?shù)南到y(tǒng)設(shè)計(jì)方法。設(shè)計(jì)中采用VHDL 語言對CPLD 進(jìn)行編程。同時(shí)由于CPLD 的現(xiàn)場可編程特性,增強(qiáng)了整個(gè)系統(tǒng)

2009-08-15 08:39:23 51

51 設(shè)計(jì)一種基于MCS-51 單片機(jī)與FPGA/CPLD 的總線接口邏輯,實(shí)現(xiàn)單片機(jī)與可編程邏輯器件數(shù)據(jù)與控制信息的可靠通信,使可編程邏輯器件與單片機(jī)相結(jié)合,優(yōu)勢互補(bǔ),組成靈活的、軟硬件

2009-09-22 10:16:40 83

83 本文介紹了一種利用PXI 總線將GPS 信號引入到系統(tǒng)中的設(shè)計(jì)。該電路利用GPS 實(shí)現(xiàn)守時(shí)定位,并將秒信號經(jīng)過FPGA 處理,將其作為觸發(fā)信號同步系統(tǒng)各部分。并在主機(jī)中完成驅(qū)動(dòng)開

2009-12-19 14:18:08 23

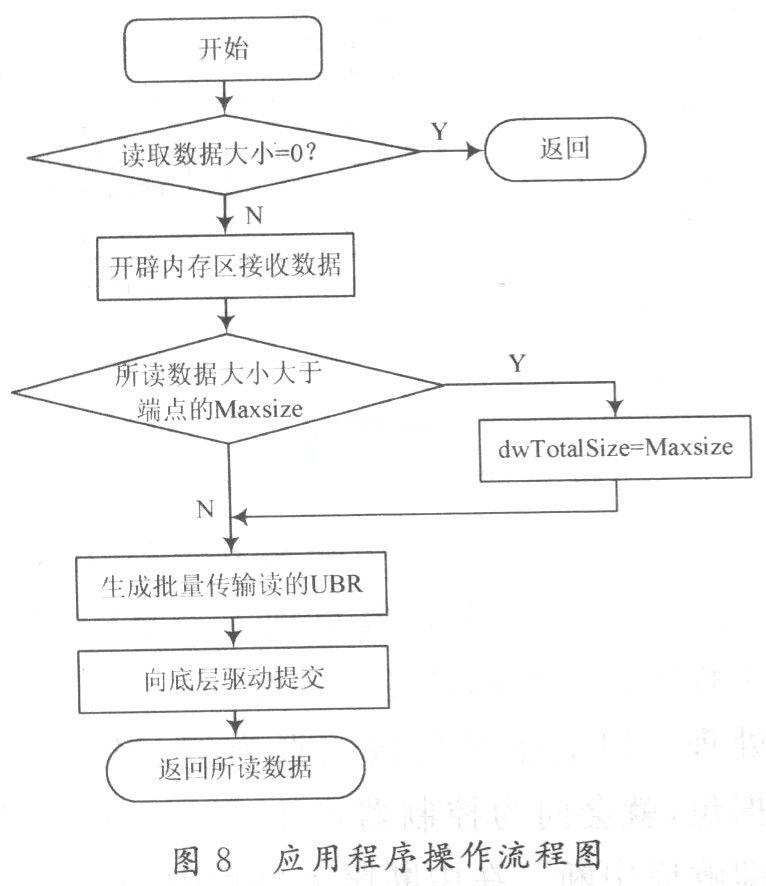

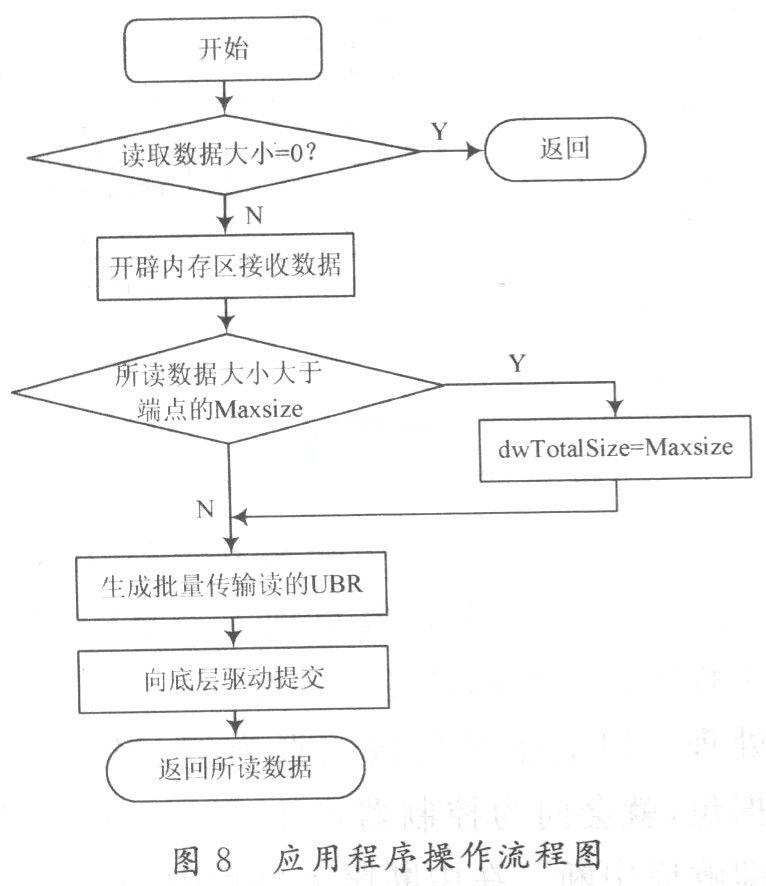

23 本文詳細(xì)介紹了USB 總線的光隔離接口的隔離原理、硬件組成及控制程序的設(shè)計(jì)。該實(shí)現(xiàn)方案采用先進(jìn)的高速光隔離技術(shù)和CPLD 控制技術(shù),對基于USB 的測試與測量的設(shè)備、人體起保

2009-12-23 15:04:38 25

25

針對1553B 總線協(xié)議控制器基本依賴于進(jìn)口專用芯片現(xiàn)狀,提出了以Xilinx 公司

Virtex-II Pro FPGA 為核心實(shí)現(xiàn)1553B 總線接口邏輯的系統(tǒng)設(shè)計(jì)方案。采用SOPC 技術(shù),將

PowerPC 40

2010-01-25 14:38:57 31

31 CPLD 器件應(yīng)用隨著生產(chǎn)工藝的逐步提高以及 CPLD 開發(fā)系統(tǒng)的不斷完善,CPLD 器件容量也由幾百門飛速發(fā)展到百萬門以上,使得一個(gè)復(fù)雜數(shù)字系統(tǒng)完全可以在一個(gè)芯片中實(shí)現(xiàn)。HDL

2010-01-27 11:40:02 48

48 基于I2C 總線的大型開關(guān)矩陣設(shè)計(jì)與實(shí)現(xiàn)作者:王振生 劉耀周 劉煥照摘要:本文介紹了一種采用 USB 接口,利用I2C 總線傳輸數(shù)據(jù),由CPLD 控制多路復(fù)用器件的大型開關(guān)矩陣結(jié)構(gòu)

2010-02-06 10:42:46 43

43 摘要:介紹了一種采用CPLD實(shí)現(xiàn)嵌入式CPU外圍電路的方法,將數(shù)據(jù)總線、譯碼單元、分頻電路及邏輯電路集成于一片CPLD,大大縮小了印制板的面積并提高了系統(tǒng)可靠性,同時(shí),由于CPLD

2010-05-10 09:23:49 29

29 本文詳細(xì)介紹了USB總線的光隔離接口的隔離原理、硬件組成及控制程序的設(shè)計(jì)。該實(shí)現(xiàn)方案采用先進(jìn)的高速光隔離技術(shù)和CPLD控制技術(shù),對基于USB的測試與測量的設(shè)備、人體起保護(hù)作用

2010-07-21 17:26:16 19

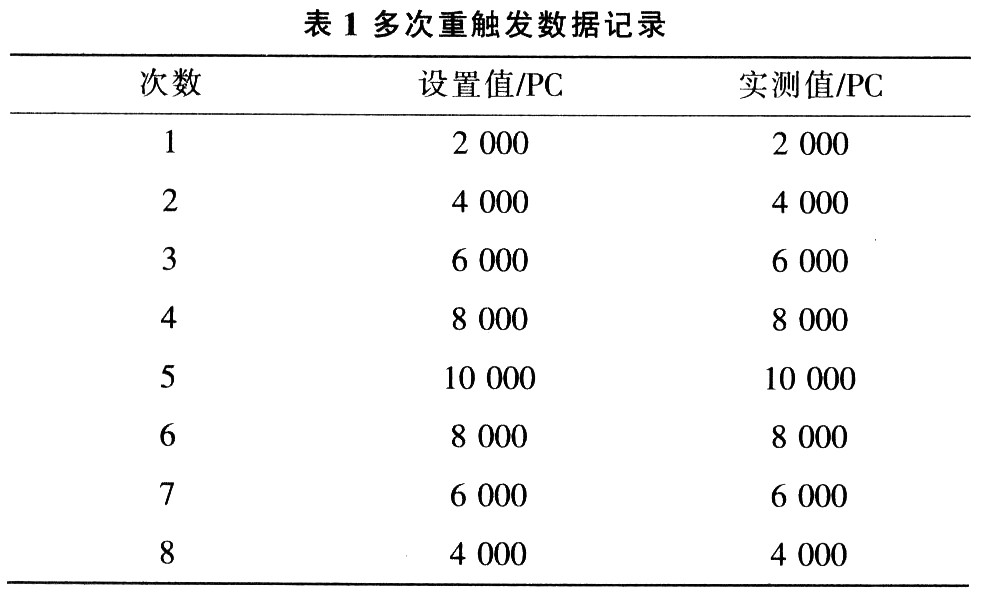

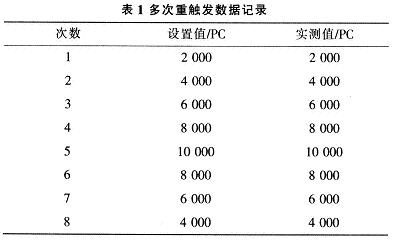

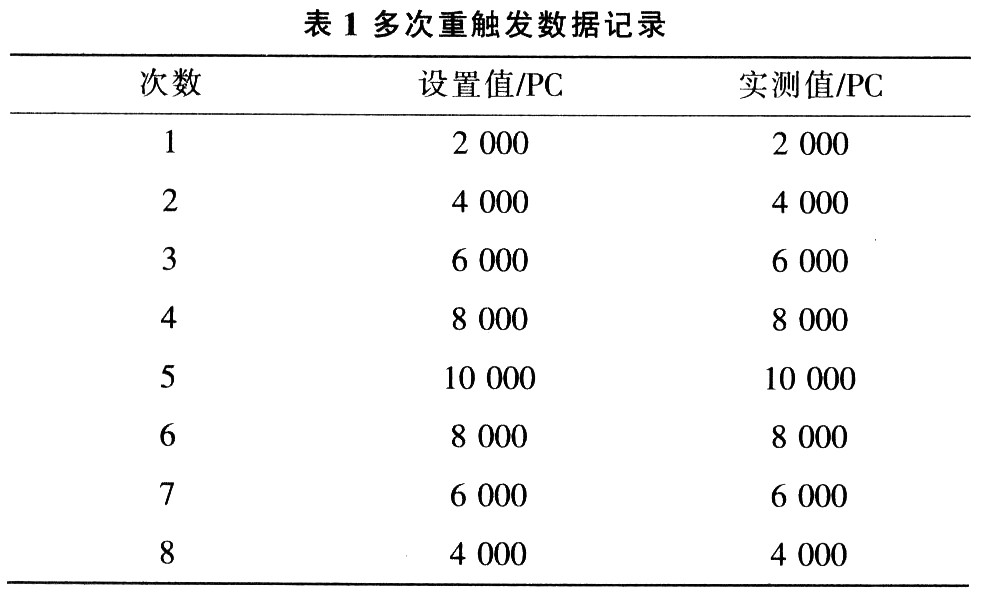

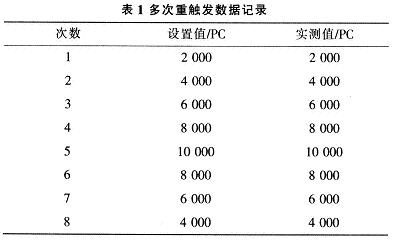

19 提出一種基于CPLD的多次重觸發(fā)存儲(chǔ)測試系統(tǒng)設(shè)計(jì)方案,詳細(xì)介紹系統(tǒng)硬件設(shè)計(jì)以及CPLD內(nèi)部控制原理,并對CPLD控制電路仿真。該系統(tǒng)體積小、功耗低,能夠?qū)崟r(shí)記錄多次重觸發(fā)信號

2010-12-30 16:05:11 22

22 摘 要: 本文采用Altera的CPLD實(shí)現(xiàn)了PCI總線至UTOPIA接口的邏輯轉(zhuǎn)換控制,為低成本實(shí)現(xiàn)ATM終端奠定了基礎(chǔ)。

2006-03-11 13:16:50 864

864

摘要:用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL設(shè)計(jì)部分。CPLD(Complex Programmable Logi

2006-05-26 21:52:11 872

872

基于DSP與CPLD的I2C總線接口的設(shè)計(jì)與實(shí)現(xiàn)

帶有I2C總線接口的器件可以十分方便地將一個(gè)或多個(gè)單片機(jī)及外圍器件組成單片機(jī)系統(tǒng)。盡管這種總線結(jié)構(gòu)沒有并行總線那

2009-03-28 15:07:47 1105

1105

基于CPLD的非多路復(fù)用與多路復(fù)用總線轉(zhuǎn)換橋的設(shè)計(jì)與實(shí)現(xiàn)

微處理器對外并行總線接口方式一般分為兩種,一種為多路復(fù)用方式,數(shù)據(jù)與地址采用共用引腳,分時(shí)傳輸;另一

2009-03-28 15:08:27 753

753

I2C器件接口IP核的CPLD設(shè)計(jì)

根據(jù)單片機(jī)I2C串行擴(kuò)展的特點(diǎn),在EDA軟件MaxplusII的環(huán)境下,利用AHDL語言,建立IP核。此設(shè)計(jì)利用狀態(tài)機(jī)實(shí)現(xiàn),在給出設(shè)計(jì)的同時(shí)詳細(xì)說明IP核的建立

2009-03-28 16:21:35 1076

1076

摘要:用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL設(shè)計(jì)部分。

關(guān)鍵詞:CPLD

2009-06-20 13:34:28 1116

1116

摘 要:本文介紹了一種利用可編程器件CPLD實(shí)現(xiàn)CAN總線與微機(jī)之間接口的設(shè)計(jì),說明了設(shè)計(jì)思想和設(shè)計(jì)方案,并給出了使用MAX+PLUS Ⅱ軟件圖形輸入法的邏輯設(shè)計(jì)和

2009-06-20 14:56:08 571

571

PXI 總線有哪些模塊?性能如何?

PXI 總線常用模塊有如下幾種:

(1) 模擬量I/O常用的有8、12、16、21、24 位

2009-09-06 22:43:37 1219

1219 基于CPLD的單片機(jī)與PCI接口設(shè)計(jì)解決方案

8位單片機(jī)在嵌入式系統(tǒng)中應(yīng)用廣泛,然而讓它直接與PCI總線設(shè)備打交道卻有其固有缺陷。8位單片機(jī)只有16位

2009-09-26 17:41:20 825

825

一種基于CPLD的單片機(jī)與PCI接口設(shè)計(jì)方案

0 引言

8位單片機(jī)在嵌入式系統(tǒng)中應(yīng)用廣泛,然而讓它直接與PCI總線設(shè)備打交道卻有其固有缺陷。8

2009-11-12 09:56:50 582

582 采用CPLD的多次重觸發(fā)存儲(chǔ)測試系統(tǒng)解決方案

概述:提出一種基于CPLD的多次重觸發(fā)存儲(chǔ)測試系統(tǒng)設(shè)計(jì)方案,詳細(xì)介紹系統(tǒng)硬件設(shè)計(jì)以及CPLD內(nèi)部控制

2010-03-17 11:37:51 531

531

機(jī)載TM總線接口設(shè)計(jì)方案

概述:在研發(fā)第四代戰(zhàn)機(jī)過程中,TM總線成為機(jī)載航空總線的研究熱點(diǎn)之一。提出一種利用EDA技術(shù)的TM總線接口設(shè)計(jì)。硬件

2010-03-24 09:56:46 1102

1102

采用CPLD的多次重觸發(fā)存儲(chǔ)測試系統(tǒng)的實(shí)現(xiàn)

1 引言

多次重觸發(fā)技術(shù)應(yīng)用于多種場合,如一個(gè)30齒的齒輪,設(shè)齒輪嚙臺(tái)系數(shù)為1.2,若測量其中1齒多次嚙合

2010-03-25 09:04:36 602

602

提出了一種使用CPLD解決雙端口RAM地址譯碼和PCI接口芯片局部總線仲裁的的硬件設(shè)計(jì)方案,并給出了PCI總線接口芯片

2011-01-07 12:13:03 1891

1891

在電路設(shè)計(jì)中,I2C總線是比較常用的兩線式串行通信方式,大多數(shù)的CPU都擅長于并口操作,不具備直接操作I2C總線接口的能力。為了使不具備I2C總線接口能力的CPU通過對并口的簡單操作實(shí)現(xiàn)對I2C總線接口的控制,在分析I2C總線常用工作模式的基礎(chǔ)上,設(shè)計(jì)實(shí)現(xiàn)工作

2011-02-12 16:11:01 95

95 使用PCI9054 提供的DMA 傳輸方式,并由其Local 端配置和啟動(dòng)DMA 傳輸來完成數(shù)字頻譜數(shù)據(jù)的傳輸,達(dá)到用PXI 總線實(shí)現(xiàn)數(shù)字頻譜分析儀與工控機(jī)的高速數(shù)據(jù)傳輸?shù)哪康摹?

2011-09-22 18:06:14 3818

3818

出了一種PCI總線從設(shè)備的CPLD實(shí)現(xiàn)方法。該方法遵從PCI規(guī)范2.2版,實(shí)現(xiàn)了資源自動(dòng)配置并且支持?jǐn)?shù)據(jù)突發(fā)傳輸。試驗(yàn)證明該方法的有效性,其突發(fā)傳輸速率可達(dá)20 MBs -1 。

2011-11-30 17:06:11 60

60 PXI定時(shí)和同步模塊利用觸發(fā)總線、星形觸發(fā)以及PXI的系統(tǒng)參考時(shí)鐘來實(shí)現(xiàn)高級的多設(shè)備同步。 通過共享定時(shí)和同步,可大大提高測量精度,實(shí)現(xiàn)高級觸發(fā)方案,或者將多個(gè)設(shè)備同步作為

2012-03-05 14:54:25 4246

4246

文中主要介紹了采用CPLD實(shí)現(xiàn)32 bit 33 MHzPCI從設(shè)備接口的設(shè)計(jì)方法,該從設(shè)備接口模塊遵從PCI規(guī)范2.2版,實(shí)現(xiàn)了資源的自動(dòng)配置,支持突發(fā)傳輸,并為用戶提供了一個(gè)簡單的接口。設(shè)計(jì)完成

2012-08-06 15:18:22 1788

1788

基于CPLD的SGPIO總線實(shí)現(xiàn)及應(yīng)用

2017-01-24 16:00:51 75

75 基于I2C總線的處理器的聯(lián)網(wǎng)設(shè)計(jì)方案

2017-01-26 11:36:55 11

11 GPS接收機(jī)中1553B總線接口的CPLD設(shè)計(jì)

2017-02-07 15:53:43 10

10 ALVTH16821器件是20位總線接口觸發(fā)器,具有3態(tài)輸出,設(shè)計(jì)用于2.5V或3.3VVCC操作,但具有向5-V系統(tǒng)環(huán)境提供TTL接口的能力。

2022-07-11 10:13:40 8

8 時(shí)序信號監(jiān)測設(shè)備主要用于飛行器火T品信號、時(shí)序指令等信號的監(jiān)測,是飛行器地面測試的重要組成部分。針對該設(shè)備對便攜性、可靠性要求較高的特點(diǎn),采用基于PXI總線的測試技術(shù)的一體式設(shè)計(jì),充分考慮各種故障

2017-11-07 10:10:07 13

13 實(shí)驗(yàn)內(nèi)容 將基本RS觸發(fā)器,同步RS觸發(fā)器,集成J-K觸發(fā)器,D觸發(fā)器同時(shí)集成一個(gè)CPLD芯片中模擬其功能,并研究其相互轉(zhuǎn)換的方法。 實(shí)驗(yàn)的具體實(shí)現(xiàn)要連線測試。 原理圖 如圖6-1

2017-12-05 09:33:41 13

13 PXI總線是NI公司在計(jì)算機(jī)外設(shè)總線PCI的基礎(chǔ)上實(shí)現(xiàn)的新一代儀器總線,已經(jīng)成為業(yè)界開放式總線的標(biāo)準(zhǔn),基于PXI總線的數(shù)字化儀模塊是現(xiàn)代測試系統(tǒng)中重要的一種數(shù)據(jù)記錄與處理設(shè)備。設(shè)計(jì)一個(gè)雙通道12

2018-12-18 08:04:00 2637

2637

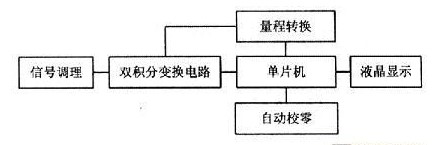

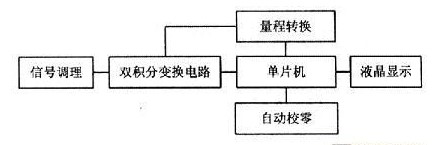

設(shè)計(jì)了基于CPLD的數(shù)字電壓表,采用CPLD器件作為核心處理電路,用單片機(jī)進(jìn)行控制,能較好地減小外界干擾,提高分辨率。該數(shù)字電壓表能夠自動(dòng)轉(zhuǎn)換量程,從而可提高數(shù)字電壓表的性能。

2019-04-23 08:28:00 2030

2030

介紹了一種用CPLD(復(fù)雜可編程邏輯器件)作為核心控制電路的測試系統(tǒng)接口,通過時(shí)cPLD和竹L電路的比較及cPLD在系統(tǒng)中實(shí)現(xiàn)的強(qiáng)大功能,論述了CPLD在測試系統(tǒng)接口中應(yīng)用的可行性和優(yōu)越性,簡單介紹

2019-01-01 16:18:00 1472

1472

PXI總線是NI公司在計(jì)算機(jī)外設(shè)總線PCI的基礎(chǔ)上實(shí)現(xiàn)的新一代儀器總線,已經(jīng)成為業(yè)界開放式總線的標(biāo)準(zhǔn),基于PXI總線的數(shù)字化儀模塊是現(xiàn)代測 試系統(tǒng)中重要的一種數(shù)據(jù)記錄與處理設(shè)備。設(shè)計(jì)一個(gè)雙通道12

2020-03-15 16:45:00 1833

1833

實(shí)現(xiàn)PCI總線協(xié)議目前主要有專用接口芯片和CPLD實(shí)現(xiàn)兩種方式。專用接口芯片使用簡單方便、工作穩(wěn)定可靠,但往往具體應(yīng)用中只用到部分功能,并且需要可編程邏輯配合使用,這樣不僅浪費(fèi)專用芯片的資源,而且

2020-03-20 09:54:04 1268

1268

得到的數(shù)字信號先被送入先進(jìn)先出存儲(chǔ)器進(jìn)行緩存,當(dāng)緩存器所存儲(chǔ)的數(shù)據(jù)達(dá)到半滿/全滿時(shí),將發(fā)送一個(gè)半滿/全滿標(biāo)志信號,觸發(fā)中斷,由系統(tǒng)控制器通過PXI總線讀取數(shù)據(jù)。整個(gè)系統(tǒng)的工作邏輯時(shí)序控制由1片CPLD控制芯片來編程實(shí)現(xiàn),接口邏輯采用通用的PXI總線接口邏輯芯片PCI9030來實(shí)現(xiàn)。

2020-04-10 09:17:27 917

917

可編程器件CPLD,用CPLD完成了PC104總線與429總線通訊的主要電路,大大節(jié)省了硬件資源,本文著重介紹了CPLD部分的設(shè)計(jì)。

2020-04-12 11:46:53 1826

1826

重點(diǎn)描述了PXI儀用模塊必須具有的PCI/PXI總線接口、精密時(shí)基和觸發(fā)控制器的實(shí)現(xiàn),最后探討了PXI儀用模塊針對EMC應(yīng)采取的措施。實(shí)際應(yīng)用表明所設(shè)計(jì)的PXI儀用模塊完全符合PXI硬件規(guī)范,達(dá)到了設(shè)計(jì)要求。

2020-04-13 09:12:16 1682

1682

的MCU,可采用軟件模擬,有通用軟件包可以使用,但功能比較簡單。在MCU(以Motorola 68000系列為例)和CPLD電子系統(tǒng)設(shè)計(jì)中,利用CPLD器件資源,按照I2C總線協(xié)議標(biāo)準(zhǔn)模式,設(shè)計(jì)了功能完善的I2C總線控制器,給出了設(shè)計(jì)思路和實(shí)現(xiàn)方法。

2020-08-11 17:03:55 1508

1508

本文首先介紹了箭載測試系統(tǒng)的總體設(shè)計(jì)方案,包括 F C AE 1553 總線的基本特性、層次模型、 拓?fù)浣Y(jié)構(gòu) 、 協(xié)議各層功能 分析 等 ,以及總線接口模塊的設(shè)計(jì)方案和功能組成等 。

2021-04-09 17:18:17 6

6 基于CPLD/FPGA的半整數(shù)分頻器設(shè)計(jì)方案

2021-06-17 09:37:02 21

21 CAN總線接口EMC標(biāo)準(zhǔn)電路設(shè)計(jì)方案

2021-07-12 10:45:28 199

199 昨天帶大家認(rèn)識(shí)了PXI機(jī)箱之后,今天會(huì)詳細(xì)講解下關(guān)于PXI機(jī)箱的槽位號、背板、總線、電源、時(shí)鐘、觸發(fā)總線等相關(guān)的知識(shí)。歡迎持續(xù)關(guān)注~了解更多歡迎發(fā)郵件到ltt@hkaco.com

2022-01-10 14:49:32 4

4 電子發(fā)燒友網(wǎng)站提供《基于CPLD/FPGA的多串口擴(kuò)展設(shè)計(jì)方案.pdf》資料免費(fèi)下載

2023-10-27 09:45:17 2

2

電子發(fā)燒友App

電子發(fā)燒友App

評論