引言

SOPC是Altera公司提出的片上可編程系統解決方案,它將CPU、存儲器、I/O接口、DSP模塊以及鎖相環的系統設計所必需的模塊集成到一塊FPGA上,構成一個可編程的片上系統,使設計的電路在其規模、可靠性、體積、功耗、功能、上市周期、開發周期、產品維護以及硬件升級等多方面實現最優化。

目前在Altera SOPC“》SOPC Builder下集成了包括UART、SPI、Ethernet、SDRAM、Flash、DMA 等控制器的IP核。此外,用戶也可以根據系統的需要自己設計或者購買第三方廠商的IP核,通過Avalon總線像搭積木一樣方便地將其捆綁在系統上。IP 核是經過功能驗證的知識產權核,使用IP 核有以下優勢:(1)提高設計性能;(2)降低產品開發成本;(3)縮短設計周期;(4)設計靈活性強;(5)仿真方便;(6) OpenCore Plus 支持無風險應用。

當然本論文所說的IP 核功能沒有那么豐富,實際上就是一個功能驗證正確的用戶邏輯,和商業應用的IP 核還有一定的差距。本文的主要工作就是通過硬件描述語言描述了視頻信號的采集,分配,存儲以及色度空間的轉換等邏輯,并且驗證了功能的正確性。

1.視頻編解碼Camera_show原理

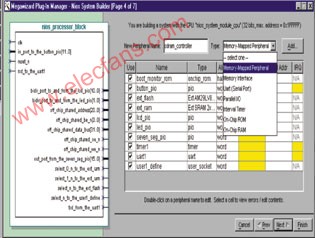

嵌入式攝像控制系統除了必要的電源電路以外,還要包括存儲電路、通信電路和下載電路等,所有的設備均與Avalon總線連接,這里主要介紹用戶邏輯接口Camera_show,它完成了模擬視頻數據轉化成數字視頻數據并在VGA上顯示的功能,主要包括模擬視頻信號的采集、分配(串并轉換電路完成)、存儲(存儲控制邏輯和片上RAM完成)和色度空間轉換。具體的功能框圖如圖1所示。

圖1 用戶邏輯Camera_show的原理框圖

2.視頻編解碼IP核Camera_Show設計

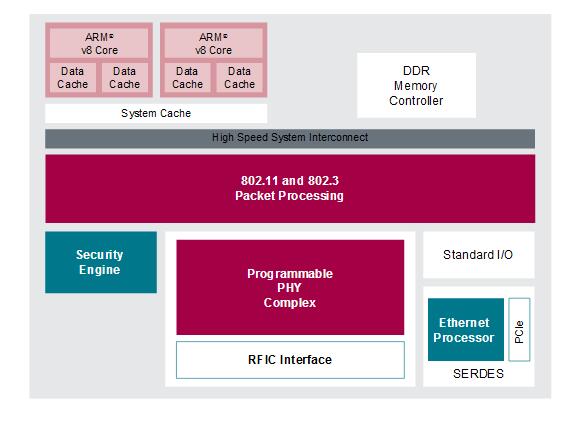

視頻編解碼IP核主要完成的功能包含視頻信號的采集、分配、存儲以及色度空間的轉換。模擬視頻信號經過ADV7181B 后變成了符合ITU-R656 的YUV 數字信號,但是要對YUV 信號進行處理必須將這三路信號分開并行處理,所以需要采集分配這三路信號,這是2.1 的IP核需要實現的功能;由于模擬視頻信號是隔行掃描的,但是CRT 顯示器是逐行掃描,如果不加處理那么必然會導致行錯開,所以需要將數據進行存儲,通過控制實現隔行變逐行,這是2.2 的IP 核需要實現的功能;最后經過處理的YUV 三路數字信號,需要完成色度空間的轉換變成RGB 信號,這是2.3 的IP 核需要實現的功能。

2.1 YUV 信號的采集、分配

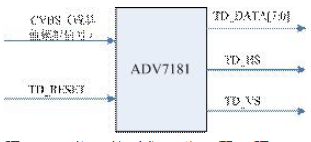

在嵌入式攝像控制系統中,ADV7181主要承擔著模擬攝像頭的視頻數據進行解碼的任務,將CVBS的等模擬信號轉化成ITU-R656標準的YUV信號。圖2給出了ADV7181的功能框圖。

圖2 ADV7181功能框圖

由圖可以看到,對于輸入的CVBS 等模擬信號經過ADV7181B芯片轉換后輸出YUV 信號,行同步信號HS, 幀同步信號VS。這些就是需要的數字視頻信號,也就解決了數字視頻源的問題。圖2 給出了YUV 信號的組成排列方式,“FF,00,00”作為AV 信號的開始,所以需要構造一個檢測電路。注意到SAV 和EAV 均是FF , 00 , 00 開頭但是XY 的值不一樣。根據芯片資料,XY[4]表示的是V ,即有用信號與空白信號的分界點,如果V=0則表示的是SAV,否則是EAV 。XY[6]是場信號的區分標志。0 是奇場,1 是偶場。

模擬信號的一行是1716 個CLOCK ,有用信號是1440 個CLOCK ,在信號采集和分配的過程中,僅需對有用信號進行采集,所以利用檢測到SAV 作為一個標志,啟動信號的分配過程是非常有必要的。

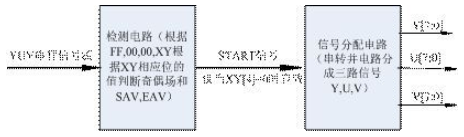

由于YUV 信號在模擬信號中是交織著的,所以需要一個信號選擇電路。YUV 一共是三路信號,設計一個計數器進行選擇,計數是O和2時,是UV信號,計數是1 和3 時是Y 信號,完成的實際上是串行信號轉并行信號的過程。以上過程可以用圖3的原理框圖來表示。

圖3 YUV信號的采集、分配原理圖

在硬件描述語言中,完成上述過程還是比較簡單的。例如檢測電路,只要描述一個移位寄存器就可以了,具體代碼如下:

wire Y_check=((R3==8‘hff)&&(R2==8’h00)&&(R1==8‘h00))?1:0;

always@(posedge CLOCK)

begin

RR1=TD_D; RR2=Rl; RR3=R2;

end

always@(negedge CLOCK)

begin

Rl=RR1; R2=RR2; R3=RR3;

end

其中的wire 變量Y_check 就是當檢測到FF,00,00的時候就為1的標志。根據上文所述,區分SAV 和EAV 是根據XY[4]來決定,區分奇偶場是根據XY[7]來區分,所以只有隨后的信號是SAV 的時候,信號分配電路才有效,所以需要描述一段邏輯來判斷,代碼如下:

reg START,Field;

always@(posedge CLOCK)begin

if(Y_check==1)

begin

START=~TD_D[4];

Field=TD_D[6];

end

end

START信號就是開始信號采集、分配的標志,只有當TD_D=0 也就是START= 1時信號分配電路才會工作。串轉并電路代碼如下:

reg [1:0] COUNTER;

always@(posedge CLOCK)begin

if (!START)

COUNTER=0;

else COUNTER = COUNTER + 1;

end

reg YPix_clock;

always@(posedge CLOCK) begin

case(COUNTER)

0 : begin Cbb=TD_D;YPix_clock=0;end

1 : begin YY =TD_D;CCr =Crr;CCb=Cbb;YPix_clock=1;end

2 : begin Crr=TD_D;YPix_clock=0;end

3 : begin YY=TD_D;CCr=Crr;CCb=Cbb;YPix_clock=1;end

endcase

end

以上代碼完成了圖3的功能,輸入的信號名為TD_D,輸出的三路信號是Cbb , YY , Crr。注意到還有個YPix_clock,實際上是27M 的2 分頻,這個時鐘非常有用,在下面將詳細闡述。 {{分頁}}

2.2 YUV 信號的存儲

要將視頻信號隔行變逐行,有2 種解決方法:

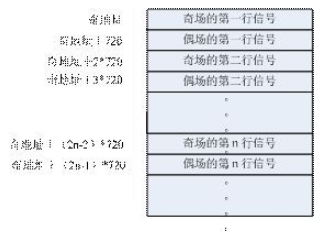

第1種:將一幀的數據存儲下來,根據奇偶場的不同(區分可以根據XY[7]),在寫周期的時候,因為奇場的行之間有偶場的信號,所以寫數據的時候需要跳地址寫,根據行同步信號(或者SAV也可以)來區分行,換行的時候地址要加額外的720(用來存放夾雜在奇場信號中的偶場信號),直到出現偶場信號(也就是XY[6]=1)地址切換為初始基地址加720,其余的同奇行的處理方法,具體的地址分配表參照圖4。

圖 4 地址分配表

在讀周期只需要按照順序讀出就可以了,需要注意的是寫時鐘是13.5M,讀時鐘是27M,而且對于Y、U、V信號要進行分別存儲。

第2種:將一行的數據存儲下來,因為1716 個時鐘周期剛好等于VGA 兩行的時間,所以在這段時間里可以將7加個有效視頻信號讀取2遍,以奇行的信號去取代偶行的信號,達到隔行變逐行的目的。在實現上只要是兩個RAM塊進行乒乓操作就可以了,具體在后文闡述。

比較兩種實現方法,方法1的優點在于圖像沒有失真,即奇偶行信號依舊相間在一起,方法2 卻不能做到這一點,而且方法1 也可以通過乒乓方式提高運行的速度,但是由于讀寫時鐘的不同步,每個存儲空間應當讀2遍。方法2也是讀2遍,但是是每行讀2遍,方法1是一幀數據讀2遍。

方法1的缺點在于存儲的數據量太大。一幀數據僅Y分量就是8bit*720*525 =3024000bit = 378KB,這個數據是不適合在SRAM中操作的,需要使用SDRAM,而操作SDRAM 是比較復雜的,所以一般考慮使用方法2,因為它需要很小的空間,而且可以利用FPGA的片內資源就可以實現。當圖像數據傳輸很快的時候,人眼基本上是分不清奇偶場信號的,所以方法2是可行的。在講方法2之前,需要了解在流水線操作中經常使用的乒乓操作,這是可編程邏輯常用的設計思想和技巧。乒乓操作常常應用于數據流控制,典型的乒乓操作如圖5所示。

圖5 乒乓操作示意圖

乒乓操作的處理流程描述如下:輸入數據流通過“輸入數據流選擇單元”,等時地將數據流分配到兩個數據緩沖模塊。數據緩沖模塊可以是任何存儲模塊,比較常用的存儲單元是雙口RAM ( DPRAM ),單口RAM ( SPRAM)和FIFO等。在第一個緩沖周期,將輸入的數據流緩存到“數據緩沖模塊1”。在第2個緩沖周期,通過“輸入數據流選擇單元”的切換,將輸入的數據流緩存到“數據緩沖模塊2”,與此同時,將“數據緩沖模塊1”緩存的第1個周期的數據通過“輸出數據流選擇單元”的選擇,送到“數據流運算處理模塊”被運算處理。在第3 個緩沖周期,通過“輸入數據流選擇單元”的再次切換,將輸入的數據流緩存到“數據緩沖模塊1”,與此同時,將“數據緩沖模塊2”緩存的第2個周期的數據通過“輸出數據流選擇單元”的選擇,送到“數據流運算處理模塊”被運算處理。如此循環,周而復始。

乒乓操作的最大特點是,通過“輸入數據流選擇單元”和“輸出數據流選擇單元”按節拍、相互配合的切換,將經過緩沖的數據流沒有時間停頓地送到“數據流運算處理模塊”,被運算和處理。把乒乓看成一個整體,站在這個模塊的兩端看數據,輸入數據流和輸出數據流都是連續不斷的,沒有任何停頓,因此非常適合對數據流進行流水線式處理。所以乒乓方式常常應用于流水線式算法,完成數據的無縫緩沖與處理。

在FPGA里面,使用乒乓操作是面積與速度互換原則的一個體現。

方法2 可以這樣實現:在FPGA內部使用Megacore,構造一個雙口的RAM, 雙口RAM 的輸入輸出信號的硬件描述語言定義如下:

RAM2 u (.data_a (iDATA [7:0]) ,

.wren_a (I_a ) ,

.address_a(COUNTER_a [9 : 0] ) ,

.clock_a ( CLOCK_ a) ,

.q_a(DATA_a [ 7 : 0 ] ) ,

.data_b(iDATA[7:0]),

.wren_b (I_b),

.address_b(COUNTER_b[9:0]) ,

.clock_b(CLOCK_b) ,

.q_b(DATA_b[7:0]) ) ;

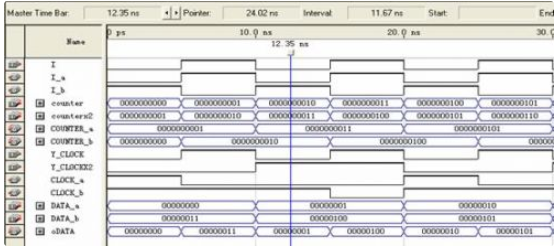

使用的信號包括:數據信號data_a, dat_b;讀寫有效信號wren_a, wren_b;地址信號address_a, address_b;時鐘信號clock_a,clock_b;輸出數據信號q_a,q_b。可以看到所有的信號都是成對出現的,就是為了進行乒乓方式的數據傳輸。分成了兩個RAM區域,A 和B,相當于前面講乒乓方式里的數據緩沖模塊1 和2。兩個RAM 塊是交替著讀寫(由I_a和I_b決定),輸出數據流也是由I 決定。剛說到寫時鐘是13.5M,讀時鐘是27M,所以clock_a 和clock_b必須是讀寫時鐘切換著輸入,而且地址的計數也不一樣,寫周期時候地址增加的時鐘是13.5M,讀周期地址增加的時鐘是27M。所以每行的數據讀了兩遍,相當于隔行變逐行。圖6是在Quartus II下RAM的乒乓操作功能仿真圖:

圖6 RAM的乒乓操作仿真圖 {{分頁}}

RAM塊進行乒乓方式操作信號的分配表如下:

最后輸出的DATA信號進入下一級單元,即YUV到RGB的轉換。

2.3 顏色-空間轉換部分設計

為什么要有這個轉換呢?因為不論是電視機還是CRT顯示器,都是使用RGB三基色合成的方法來顯示顏色。用RGB三基色來表示彩色的確很直觀,但是如果把這種方法用作圖像傳輸則絕不是一個好方法。主要是因為:

(1) 與黑白圖像不兼容;

(2) 占用太多帶寬;

(3) 抗干擾能力差。

本系統圖像傳感器輸出YCbCr信號,需要進行到RGB信號的轉換,用于CRT顯示。YCbCr 到RGB按照下面公式進行轉換:

R = 1.164 ( Y-16 ) + 1.596 ( Cr-128 );

G = 1.164 ( Y-16 )- 0.813 ( Cr-128 ) - 0.392(Cb-128);

B = 1.164 ( Y-16 ) + 2.017 ( Cb-128 );

觀察上面公式可以發現,轉換均需要乘加運算,并且式子中用到了小數,所以必須要對系數進行放大。經過合理轉化,公式如下:

R = (1/256) * ( 298*Y + 409*Cr - 57065 );

G = (1/256) * ( 298*Y - 100*Cb - 208*Cr + 34718 );

B = (1/256) * ( 298*Y + 516*Cb - 70861 );

用Verilog HDL編寫代碼,實現YUV到RGB的轉化。其中共包括3個模塊跟1個仿真激勵。在模塊const_mult中,主要實現乘法運算,主要代碼如下:

module const_mult (Clock, ClockEnable, Reset, Color, Color_Out);

parameter IN_SIZE = 8;

parameter OUT_SIZE = 16; // output size width (integer)

parameter CST_MULT = 66; // constant multiplicand (integer)

........

always @(posedge Clock or posedge Reset)

begin : COLOR_KCM

if (Reset)

Color_Out 《= 0;

else if (ClockEnable)

Color_Out 《= CST_MULT * Color;

end

endmodule

模塊csc.v中,調用const_mult模塊,通過參數傳遞改變參數IN_SIZE, OUT_SIZE, CST_MULT的值,然后實現加法運算。

以R = (1/256) * ( 298*Y + 409*Cr - 57065 )為例,主要代碼如下:

const_mult #(8, 18, 298) R_KCM_Y(.Clock(Clock), .ClockEnable(ClockEnable), .Reset(Reset), .Color(Y),.Color_Out(R_Y_KCM));

const_mult #(8, 18, 0 ) R_KCM_Cb(.Clock(Clock), .ClockEnable(ClockEnable), .Reset(Reset), .Color(Cb),.Color_Out(R_Cb_KCM));

const_mult #(8, 18, 409) R_KCM_Cr(.Clock(Clock), .ClockEnable(ClockEnable), .Reset(Reset), .Color(Cr),.Color_Out(R_Cr_KCM));

// Adder for (Cr + constant)

always @(posedge Clock or posedge Reset)

begin : R_Cr_C_Adder

if (Reset)

R_Cr_C 《= 0;

else if (ClockEnable)

R_Cr_C 《= R_Cr_KCM - 57065;

end

// Adder for (Y + Cb)

always @(posedge Clock or posedge Reset)

begin : R_Y_Cb_Adder

if (Reset)

R_Y_Cb 《= 0;

else if (ClockEnable)

R_Y_Cb 《= R_Y_KCM + R_Cb_KCM;

end

// Adder for R =》 Y + Cb + constant

always @(posedge Clock or posedge Reset)

begin : R_Adder

if (Reset)

R_full 《= 0;

else if (ClockEnable)

R_full 《= R_Y_Cb + R_Cr_C;

End

用以實現G、B的代碼與上面類似,在此不再贅述。以下代碼實現R_full*1/256功能。

always @(R_full or G_full or B_full)

begin

if(R_full[17]) R = 0;

else if(R_full[16]) R = 255;

else R = R_full [15:8];

……

end

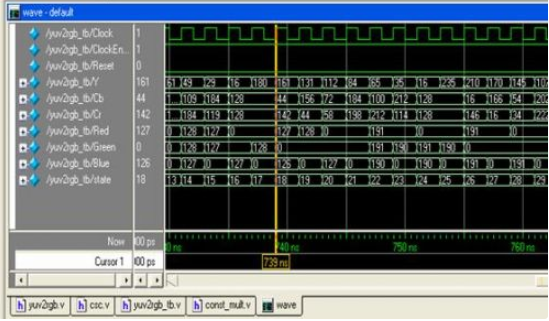

主模塊yuv2rgb實現子模塊的調用,用Modelsim進行了仿真。仿真波形如圖7所示:

圖7 YUV到RGB的轉化仿真圖

3.結論

本文設計了基于SOPC”》SOPC的視頻編解碼控制器IP核,根據自頂向下的設計思想,將IP核進行層次功能劃分,并對IP核的仿真驗證,實現了視頻信號的采集,分配,存儲以及色度空間的轉換。本IP核具有很好的移植性,可以方便的應用到以Nios II為核心的各種需要視頻編解碼控制器功能的嵌入式中。

責任編輯:gt

電子發燒友App

電子發燒友App

評論