本帖最后由 一只耳朵怪 于 2018-6-25 15:38 編輯

我在6678上跑一個時鐘和IPC程序,設置的是在兩個核 上跑,通過核0發(fā)中斷給核1來觸發(fā)其運行,然后核1在給核0發(fā)一個中斷最為

2018-06-25 04:40:47

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨立的,只是集成在了一起呢,還是占用了FPGA的資源來形成一個RAM?如果我以ROM的形式調用該IP核,在

2013-01-10 17:19:11

與8051的系統(tǒng)結構相同,如圖1所示。該IP核兼容所有8051指令系統(tǒng),內部資源包括:8位CPU,尋址能力達2×64K;4 KB的ROM和128字節(jié)的RAM;4個8位I/O口;16位內部定時/計數器;5個中

2012-08-11 11:41:47

請問各位大神,我想問一下用FPGA做卷積碼有什么注意的地方?

2015-04-07 12:57:40

有誰知道現在國內外有哪些公司賣FPGA的圖像處理相關的IP核?

2015-04-28 21:34:24

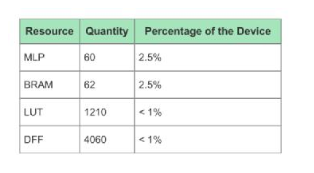

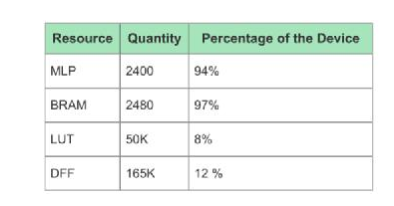

, 節(jié)約將近90% 的邏輯資源。 軟核(Soft IP Core) : 軟核在EDA 設計領域指的是綜合之前的寄存器傳輸級(RTL) 模型;具體在FPGA 設計中指的是對電路的硬件語言描述,包括邏輯描述

2018-09-03 11:03:27

inference在設備端上做。嵌入式設備的特點是算力不強、memory小。可以通過對神經網絡做量化來降load和省memory,但有時可能memory還吃緊,就需要對神經網絡在memory使用上做進一步優(yōu)化

2021-12-23 06:16:40

卷積神經網絡為什么適合圖像處理?

2022-09-08 10:23:10

的突破。AlexNet 在百萬 量級的 ImageNet數據集上對于圖像分類的精度大幅 度超過傳統(tǒng)方法,一舉摘下了視覺領域競賽 ILSVRC2012的桂冠。自 AlexNet之后,研究者從卷積神經網 絡

2022-08-02 10:39:39

,用于描述網絡的方程中也有 32 個偏差和 32 個權重。CIFAR神經網絡是一種廣泛用于圖像識別任務的CNN。它由兩種主要類型的層組成:卷積層和池化層,它們在神經網絡的訓練中都發(fā)揮了很大的作用。卷積層

2023-02-23 20:11:10

圖像處理FPGA 設計基本方法:1.陣列結構結合流水線處理設計例如RGB圖像,包括三組數據,處理時需要并行三通道后,每個通道進行分別的串行流水處理。2.緩存設計幀緩存 行緩存 列對齊3.資源分辨率 處理窗口 對資源影響成倍增加

2019-01-04 13:59:26

Alter IP在設計中的作用2.使用Alter 的基本宏功能2.定制基本的宏功能2.1定制基本宏功能2.2實現基本宏功能2.3設計實例3.使用Alter的IP核3.1定制IP核3.2實現IP 核3.3設計實例想一起學習的可以加我(張工)2232894713

2014-09-16 17:52:27

本帖最后由 enlinux123 于 2014-11-7 16:41 編輯

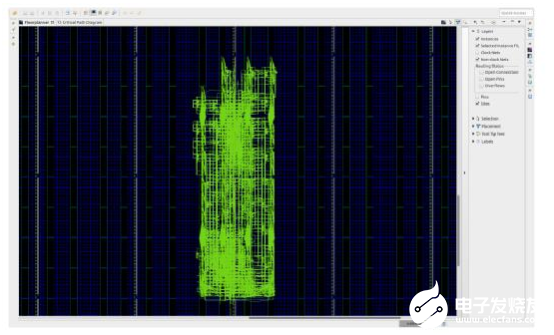

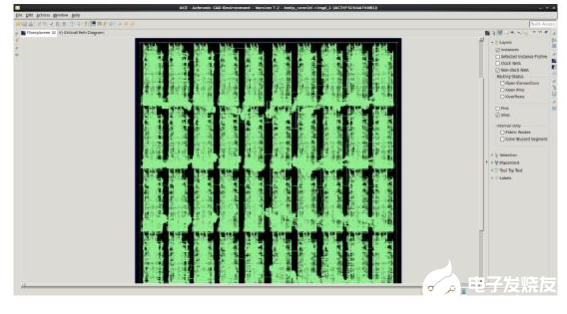

想參加技術培訓學習可以加張工2232894713最近一段時間一直在研究基于FPGA的圖像處理,乘著這個機會和大家交流

2014-11-05 09:50:00

本帖最后由 upmcu 于 2012-7-28 15:07 編輯

截圖:FPGA控制實現圖像系統(tǒng)視頻圖像采集.pdfFPGA在多制式視頻轉換系統(tǒng)中的應用.pdfFPGA在圖象處理中

2012-07-28 14:28:52

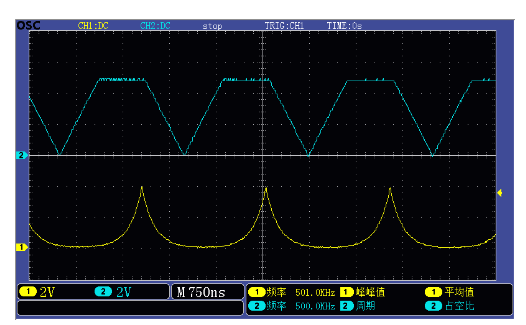

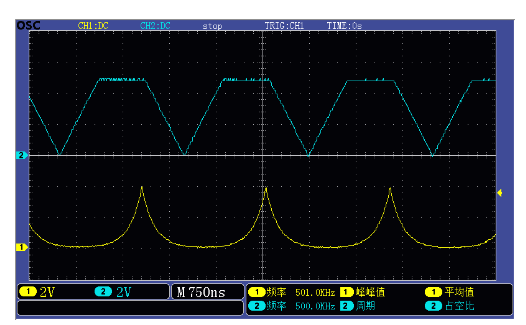

ADC實測4MHz采樣速率結果AT32F403 ADC實測4MHz采樣速率

2023-10-19 06:24:46

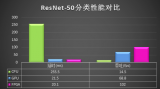

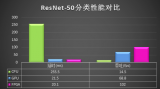

* 16 * 16(INT8 MAC) * 2 * 0 55G / 1024 = 17.6 TOPS

如果enable winograd INT8的算力可以提高一倍,winograd 要求卷積核必須是3*3

2023-09-19 08:11:10

到不同的輸出數據,比如顏色深淺、輪廓。相當于如果想提取圖像的不同特征,則用不同的濾波器filter,提取想要的關于圖像的特定信息:顏色深淺或輪廓。一張動圖詳解卷積操作在CNN中,濾波器filter(帶著

2018-10-17 10:15:50

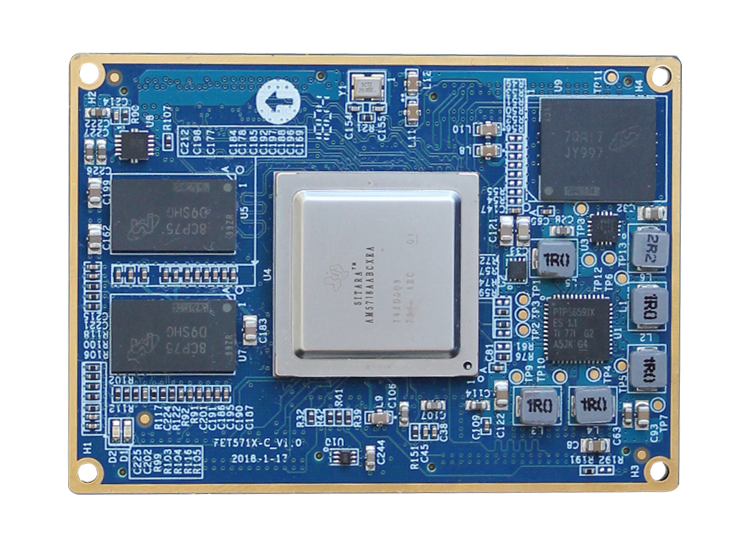

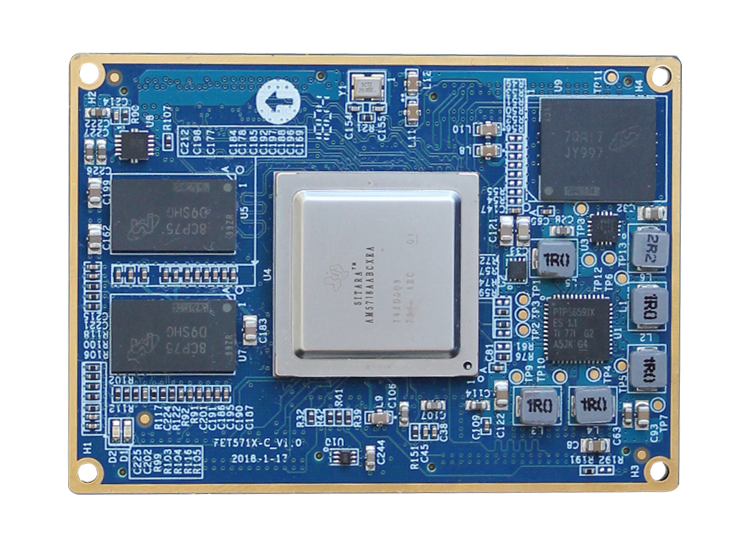

RISC MPU。最高ARM主頻達1GHz,DSP主頻最高達750MHz。多核異構具有性能強、開發(fā)簡單等特點。具有千兆網口、HDMI、SATA、CAN 、GPMC拓展口等重要接口。適合音視頻、通信、工控等行業(yè)。學習討論QQ群:173867122 。聯系QQ:***`

2015-11-28 09:15:09

1GHz,DSP主頻最高達750MHz。多核異構具有性能強、開發(fā)簡單等特點。具有千兆網口、HDMI、SATA、CAN、GPMC拓展口等重要接口。適合音視頻、通信、工控等行業(yè)。學習討論QQ群:173867122。聯系QQ:***`

2015-12-03 23:20:24

to 180MHz providing up to 288 DMIPS. ”288 DMIPS的工作性能是否指程序跑在flash空間的情況下??而且不需要將程序從flash拷貝到RAM運行就能達到此性能

2018-05-25 03:39:19

的,以IP核的形式,在FPGA器件上運行,基于FPGA的解決方案使用FPGA為核心器件,實現H.264編解碼的IP核,此解決方案為純硬件的解決方案,啟動時間可以忽略,編解碼延遲為固定的延遲,在一定

2018-05-07 17:14:42

, 繼承了該接口的諸多優(yōu)點,也更適合此類場景應用,為用戶提供了一種算力邊緣側部署的解決方案,同時MXM接口還可以為用戶提供其它架構算力模塊搭配方案,如MXM界面的寒武紀算力卡,MXM界面的登臨算力卡等

2022-05-18 15:52:40

膨脹處理,其中B是一個卷積模板或卷積核,其形狀可以為正方形或圓形,通過模板B與圖像A進行卷積計算,掃描圖像中的每一個像素點,用模板元素與二值圖像元素做“與”運算,如果都為0,那么目標像素點為0,否則

2018-11-23 16:39:34

NPU算力集成有哪些特性呢?RK1808內置的NPU算力集成有何功能?

2022-02-16 07:52:14

STM32H750獲取OV5640攝像頭圖像及上位機解碼(一維碼&二維碼)1. 目的針對靜止拍攝圖像場景,實現STM32H750對500萬像素OV5640攝像頭進行圖像捕獲,并通過串口將數據

2021-08-20 06:16:09

使用TC387芯片配置Autosar OS發(fā)現主核跑飛了,其他核正常運行OS任務切換,PC指針指向_IF_CONST區(qū)域,D[4]寄存器為1,D[15]寄存器為4,根據這兩個寄存器用計算規(guī)則計算出的TCN和TIN好像有問題,在Trap中跑飛,請問一下,大家有什么思路推薦嗎

2024-03-06 08:24:21

芯片介紹上寫浮點運算能力達到20GFLOPS,是說1秒鐘能算20G次浮點數運算嗎?按照主頻1.25GHz算,相當于每ns計算16次浮點數運算對嗎?那如果計算1百萬次浮點數加法需要多少時間呢?能不能請懂的人估算一下~~【我估算的和實測的差別太大了,不知道是不是估算方法出了什么問題】

2019-01-07 11:08:27

USB3.0口高速傳輸無損圖像的高速相機。高速相機利用USB3.0口的極速傳輸能力,在640×480的VGA分辨率時,可以達到1100幀/秒的傳輸速度。一個相機加一個筆記本電腦就可以組成一套高速錄像系統(tǒng),用

2019-01-16 12:53:45

目的本文介紹廣州星嵌DSP C6657+Xilinx Zynq7035平臺下Xilinx Zynq7035算力指標。基本概念FLOPs/FLOPSFLOPs,Floating Point

2022-12-15 21:19:38

已下是rx580顯卡算力9-11 Mh 沒有開啟計算模式,挖幾分種重啟自動開啟,計算模式只支持WIN1022-28 Mh 原版BIOS,開啟時序,并設置超頻29-32 Mh 正常算力,卡體質不同算力

2021-07-23 06:59:09

sTm32可以做卷積核濾波圖片嗎

2023-09-21 07:17:26

stm32f103有沒有圖像卷積算法函數或者例程參考下載

2023-09-22 06:34:33

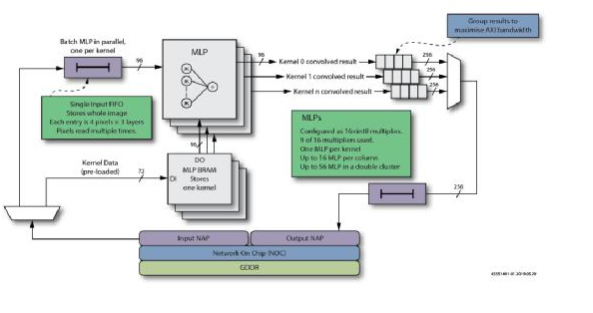

,能夠實現高效地圖像檢測、識別、分類等AI應用。早前在該架構基礎之上,深鑒科技做出了第一代FPGA產品,已經在攝像頭市場實現了批量出貨。 DPU計算核心采用全流水設計結構設計,內部集成了大量的卷積運算器

2018-03-23 15:27:20

,得到訓練參數2、利用開發(fā)板arm與FPGA聯合的特性,在arm端實現圖像預處理已經卷積核神經網絡的池化、激活函數和全連接,在FPGA端實現卷積運算3、對整個系統(tǒng)進行調試。4、在基本實現系統(tǒng)的基礎上

2018-12-19 11:37:22

,曾多次參加電子設計競賽并獲獎,參與首屆Xilinx全國大學生FPGA創(chuàng)新設計邀請賽。曾獨立設計完成“基于卷積神經網絡的自動駕駛系統(tǒng)”,項目在嵌入式ARM平臺上使用了大量圖像采集與處理算法,達到在常見

2018-12-19 11:36:24

項目名稱:基于cortex-m系列核和卷積神經網絡算法的圖像識別試用計劃:本人在圖像識別領域有三年多的學習和開發(fā)經驗,曾利用nesys4ddr的fpga開發(fā)板,設計過基于cortex-m3的軟核

2019-04-09 14:12:24

FPGA的測試版產品上,當運行在300MHz的頻率時可以得到的等效算力和峰值算力分別為39.5 TFLOPS和48 TFLOPS。預計在量產版的Stratix 10上,穩(wěn)定運行頻率將達到550MHz

2019-08-11 04:00:00

旋鈕設置到最高溫度,實測溫度為453度左右。

最后,我們實際測試下大面積鋪銅+大焊點的效果,先來一張準備測試用素材的全家福。

烙鐵溫度調到400度左右,輕松熔化大焊點。

總結下:阿爾達H-30T

2023-11-30 23:05:32

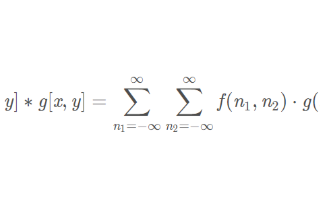

。將一個卷積核在(x,y)空間像素點的輸出,和它前后的幾個卷積核上的輸出做權重歸一化。使用了重疊的最大值池化層。3x3的池化核,步長為2,因此產生了重疊池化效應,使得一個像素點在多個池化結果中均有輸出

2018-06-07 17:26:31

集成了常用IP核,使之可以靈活的用來進行系統(tǒng)設計。在單片FPGA芯片上實現導航信息的高速解算,將會有廣闊的發(fā)展空間。針對現有小型無人機導航解算系統(tǒng)解算速度慢、多處理器臃腫可靠性差的缺點,文中設計了一種

2019-07-03 06:57:34

車載以太網在數據發(fā)送過程中的編碼,4b-3b-2t-pam3。其中在3b-2t的時候,導致頻率降為原來的2/3,所以100base-T1的mdi傳輸頻率為66.7MHz;對于1000base-T1,同樣采用4b-3b-2t-pam3的編碼方式,為什么傳輸頻率為750MHz呢?

2023-12-13 11:24:39

嗨,我的輸入是800Mhz差分時鐘。我需要800Mhz,800Mhz 90度相位輸出時鐘。看起來800Mhz 90度沒有正確相移。它匹配0度相位輸出。我生成3個200Mhz時鐘,相位為0/90

2019-04-18 07:40:02

了。下面介紹幾種深度學習的方法,它們使識別錯誤率極大地降低。 卷積神經網絡:AlexNet 在 2012 年,深度學習第一次被運用到 ImageNet 比賽中。其效果非常顯著, 錯誤率從前一年的 26

2018-05-11 11:43:14

in Network。AlexNet中卷積層用線性卷積核對圖像進行內積運算,在每個局部輸出后面跟著一個非線性的激活函數,最終得到的叫做特征函數。而這種卷積核是一種廣義線性模型,進行特征提取時隱含地假設了特征是線性

2018-05-08 15:57:47

夠更容易配置和優(yōu)化 Am 處理器運行的軟件。 AlexNet 是一個從 Arm Computer 庫中為 Raspberry Pi 設計的神經網絡網絡( CNN) , 從 1 000 個圖像組中進行圖像

2023-08-29 08:05:37

?

很簡單,在對算力性能和規(guī)模的極致追求下,現在整個行業(yè)根本不在乎什么成本和功耗。在英偉達的長期努力下,GPU的核心數和工作頻率一直在提升,芯片面積也越來越大,屬于硬剛算力。功耗靠工藝制程,靠水冷等

2024-01-23 19:08:55

FPGA在工業(yè)領域應用廣泛,邏輯資源分別為27072/51360,與國外友商產品pin to pin兼容,主要用于多通道/高速AD采集或接口拓展。因其價格低、質量穩(wěn)定、開發(fā)環(huán)境易用等優(yōu)點,受到工業(yè)用戶的廣泛

2023-03-31 16:48:05

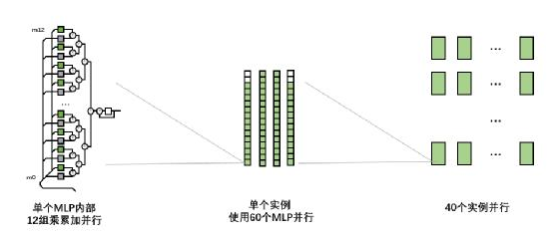

FPGA 的并行性優(yōu)點和 PYNQ-Z2 自身資源情況,設計卷積運算模塊為 16 個 通道并行計算來提升運算速度。16 通道 3×3 逐通道卷積的輸入數據塊為 16×22×42,卷積核 為 16×3

2023-06-20 19:45:12

,減少了硬件資源的占用。該方案在Cyclone II FPGA 芯片EP2C35F484 上實現,占用 20 070 個邏輯單元(少于60% 的資源),系統(tǒng)最高時鐘達到100 MHz 。與傳統(tǒng)的128 位數據路徑設計相比,更方便與處理器進行接口。

2012-08-11 11:53:10

結構,即在內存中開辟一個整數數組來進行計數,但是在FPGA 中定義數組是非常消耗資源的,尤其是當數組成員的位寬很大時。例如用觸發(fā)器來統(tǒng)計256 灰度的720p 圖像的直方圖,將消耗4000 個邏輯單元

2012-05-14 12:37:37

我們在此基礎上修改,從而實現,基于FPGA的動態(tài)圖片的Sobel邊緣檢測、中值濾波、Canny算子邊緣檢測、腐蝕和膨脹等。那么這篇文章我們將來實現基于FPGA的Sobel邊緣檢測。圖像邊緣:簡言之,邊緣

2017-08-29 15:41:12

FPGA 上實現卷積神經網絡 (CNN)。CNN 是一類深度神經網絡,在處理大規(guī)模圖像識別任務以及與機器學習類似的其他問題方面已大獲成功。在當前案例中,針對在 FPGA 上實現 CNN 做一個可行性研究

2019-06-19 07:24:41

多芯核結構ARM芯片的選擇:為了增強多任務處理能力、數**算能力、多媒體以及網絡處理能力,某些供應商提供的ARM芯片內置多個芯核,目前常見的ARM+DSP,ARM+FPGA,ARM+ARM等結構。多

2011-09-05 11:52:40

影響FPGA設計周期生產力的最大因素是什么?如何提高FPGA設計生產力?

2021-05-06 09:26:04

卷積層實現在上一篇文章中,我解釋了卷積層是對圖像的過濾過程,但是并沒有解釋輸入輸出通道如何處理,過濾時圖像的邊緣處理等。由于本文旨在實現層面的理解,因此我將詳細介紹這些要點。處理 I/O 通道在圖像

2023-02-24 15:41:16

://t.elecfans.com/topic/65.html?elecfans_trackid=t***cy 開關電源原理與設計-張占松(pdf完整版)

2016-04-01 09:03:55

工作原理與工程設計方法。內容包括PWM變換器和軟開關PWM變換器的電路拓撲、原理、控制及動態(tài)分析等。開關電源原理與設計-張占松(pdf完整版)1[hide][/hide]開關電源原理與設計-張占松(pdf完整版)2[hide][/hide]`

2011-11-22 10:52:45

背景介紹數據、算法和算力是人工智能技術的三大要素。其中,算力體現著人工智能(AI)技術具體實現的能力,實現載體主要有CPU、GPU、FPGA和ASIC四類器件。CPU基于馮諾依曼架構,雖然靈活,卻

2021-07-26 06:47:30

大俠好,歡迎來到FPGA技術江湖,江湖偌大,相見即是緣分。大俠可以關注FPGA技術江湖,在“闖蕩江湖”、\"行俠仗義\"欄里獲取其他感興趣的資源,或者一起煮酒言歡。

今天

2023-05-25 18:08:24

目前市場上炙手可熱的芯片礦機 當數芯動 A10PRO , 7g 版本的 算力750m 功耗 1300w 這款機器廠家出廠時預定價格在 48900 左右那時候定的客戶到如今 機器價格已經漲到

2021-07-23 07:39:58

的可以參考一下,歡迎一起交流學習。話不多說,上貨。

使用FPGA做圖像處理優(yōu)勢最關鍵的就是:FPGA能進行實時流水線運算,能達到最高的實時性。因此在一些對實時性要求非常高的應用領域,做圖像處理

2023-06-08 15:55:34

編者按: 在剛剛結束的 PyCon China 2022 大會上,龍蜥社區(qū)開發(fā)者朱宏林分享了主題為《ARM 芯片的 Python+AI 算力優(yōu)化》的技術演講。本次演講,作者將向大家介紹他們在倚天

2022-12-23 16:02:46

,在雙線性匯合結果后使用線性SVM分類等價于在描述向量間使用了多項式核。由于兩個向量外積的映射等于兩個向量分別映射之后再卷積,有研究工作使用隨機矩陣近似向量的映射。此外,通過近似核估計,我們可以捕獲

2019-06-08 08:00:00

本帖最后由 一只耳朵怪 于 2018-6-20 09:40 編輯

在TI官網上下載的例程,VLFFT,在6678評估板上可以跑通,可以看到創(chuàng)建了多線程任務,知道使用的是IPC模塊,但是不清楚主

2018-06-20 05:56:21

核的分類和特點有哪些?在FPGA設計中的核分為哪幾種?核基FPGA是如何設計的?軟核的設計及使用是什么?

2021-04-14 06:25:39

概述EasyGo FPGA Solver是EasyGo開發(fā)的專門部署在FPGA 硬件上的解算器軟件。根據不同的應用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

The HFA1110 is a unity gain closed loop buffer that achieves-3dB bandwidth of 750MHz, while

2009-01-08 18:21:29 12

12 in theindustrial, scientific, medical (ISM) band at 288MHz to945MHz carrier frequencies. The IC also includes a lowphase noise fractional-N synthesiz

2012-03-02 15:22:35 13

13 基于FPGA硬件實現固定倍率的圖像縮放,將2維卷積運算分解成2次1維卷積運算,對輸入原始圖像像素先進行行方向的卷積,再進行列方向的卷積,從而得到輸出圖像像素。把圖像縮放過程

2012-05-09 15:52:04 34

34 ,自然語言處理,推薦算法,圖像識別等廣泛的應用領域。 FPGA云服務器提供了基于FPGA的深度卷積神經網絡加速服務,單卡提供約3TOPs的定點計算能力,支持典型深度卷積網絡算子,如卷積、逆卷積、池化、拼接、切割等。有效加速典型網絡結構如VggNet、GoogLeNet、ResNet等。

2017-11-15 16:56:36 724

724

針對圖像自動標注中因人工選擇特征而導致信息缺失的缺點,提出使用卷積神經網絡對樣本進行自主特征學習。為了適應圖像自動標注的多標簽學習的特點以及提高對低頻詞匯的召回率,首先改進卷積神經網絡的損失函數

2017-12-07 14:30:50 4

4 框架.該框架在經典的深度卷積神經網絡AlexNet基礎上分別從網絡框架和網絡內部結構兩個方面對網絡做了優(yōu)化和改進,進一步提升了網絡的特征表達能力.同時,通過在全連接層引入隱層使得網絡能夠同時具備學習圖像特征和二值哈希

2017-12-15 13:58:51 3

3 電子發(fā)燒友網為你提供TI(ti)DS90CR288A相關產品參數、數據手冊,更有DS90CR288A的引腳圖、接線圖、封裝手冊、中文資料、英文資料,DS90CR288A真值表,DS90CR288A管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:10:12

與 FCN 通常CNN網絡在卷積層之后會接上若干個全連接層, 將卷積層產生的特征圖(feature map)映射成一個固定長度的特征向量。以AlexNet為代表的經典CNN結構適合于圖像級的分類和回歸

2018-09-26 17:22:02 491

491 /APC連接器。BGO747(FCO,SCO)用于CATV光節(jié)點系統(tǒng),工作在40~750MHz頻率范圍內。工作時放大器電源腳和光二極管偏壓腳連接24V(DC)電壓,其模塊包括一個適合波長1290

2019-03-29 09:05:01 260

260 RM Cortex-A15,主頻1.5GHz

DSP C66x,主頻750MHz

2個雙核ARM Cortex-M4,主頻213MHz

2個雙核PRU,主頻200MHz

2019-12-03 16:27:21 5516

5516

圖像卷積操作(convolution),或稱為核操作(kernel),是進行圖像處理的一種常用手段,

2020-03-13 16:44:03 3066

3066

模擬帶寬實測,探頭X1:6MHz,探頭X10:》30MHz(由于信號發(fā)信器只能發(fā)出30MHz的正弦波,在30Mhz時實測信號衰減比大于90%,實際帶寬接近50MHz)。

2020-08-28 10:59:55 1628

1628

ADP3088:1 MHz,750馬巴克調節(jié)器,數據Sheet

2021-04-16 16:51:48 1

1 AD8370:LF至750 MHz數控VGA數據表

2021-04-21 09:38:29 6

6 本文通過通俗易懂的文字解釋了圖像卷積、邊緣提取以及濾波去燥的概念及其分類。? 一、圖像卷積 現在有一張圖片 f(x,y) 和一個kernel核 w(a,b)。 卷積(Convolution):卷積

2021-04-30 09:38:51 4601

4601

ADRF6801:750 MHz至1150 MHz正交解調器,帶小數N PLL和VCO數據表

2021-04-30 20:50:02 2

2 連接機制,促進卷積層之間的信息流通,實現煙霧圖像局部特征和全局特征的融合。在此基礎上,構造應用于煙霧識別的深度卷積神經網絡,并在訓練樣本和標簽的凸組合上完成訓練以增強模型的泛化能力。實驗結果表明,與 Alexnet、

2021-05-14 11:32:36 9

9 了一種基于FPGA的SIM卷積神經網絡加速器架構。以YOOV2目標檢測算法為例,介紹了將卷積神經網絡模型映射到FPGA上的完整流程;對加速器的性能和資源耗費進行深λ分析和建模,將實際傳輸延時考慮在內,縮小了加速器理論時延與實際時延

2021-05-28 14:00:22 23

23 本期開小灶Heyro將帶領大家進入下一趟旅程——基于卷積神經網絡的圖像分類算法講解,從而幫助大家了解在卷積神經網絡結構下衍生出的被用于圖像分類的經典算法。

2022-04-06 14:50:36 4686

4686 給出目前的框圖,如下所示,外部輸入25M,由Interface的PLL生成150/750MHz(離開148.5MHz有點偏差也沒關系),hdmi_ip接收前面測試的RGB數據后,模擬HDMI協議

2022-09-06 10:16:38 1764

1764 FPGA最大的優(yōu)勢體現在其低功耗和并行運算的特點上,數字圖像蘊含數據量大,采用FPGA可以在保證低功率運算的情況下,有效提高圖像算法的實時性。

2023-04-07 09:40:07 2879

2879 電子發(fā)燒友網站提供《PyTorch教程7.2之圖像卷積.pdf》資料免費下載

2023-06-05 10:13:56 0

0 電子發(fā)燒友網站提供《PyTorch教程8.1之深度卷積神經網絡(AlexNet).pdf》資料免費下載

2023-06-05 10:09:58 0

0 卷積神經網絡如何識別圖像? 卷積神經網絡(Convolutional Neural Network, CNN)由于其出色的圖像識別能力而成為深度學習的重要組成部分。CNN是一種深度神經網絡,其結構

2023-08-21 16:49:27 1284

1284 常見的卷積神經網絡模型 典型的卷積神經網絡模型 卷積神經網絡(Convolutional Neural Network, CNN)是深度學習中最流行的模型之一,其結構靈活,處理圖像、音頻、自然語言

2023-08-21 17:11:41 1641

1641

電子發(fā)燒友App

電子發(fā)燒友App

評論