時鐘網(wǎng)絡(luò)反映了時鐘從時鐘引腳進(jìn)入FPGA后在FPGA內(nèi)部的傳播路徑。

2019-09-10 15:12:31 6343

6343

只有在腦海中建立了一個個邏輯模型,理解FPGA內(nèi)部邏輯結(jié)構(gòu)實(shí)現(xiàn)的基礎(chǔ),才能明白為什么寫Verilog和寫C整體思路是不一樣的,才能理解順序執(zhí)行語言和并行執(zhí)行語言的設(shè)計(jì)方法上的差異。在看到一段簡單程序的時候應(yīng)該想到是什么樣的功能電路。

2022-08-25 11:12:00 739

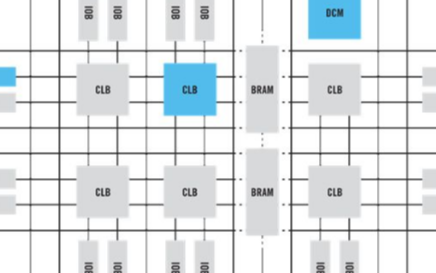

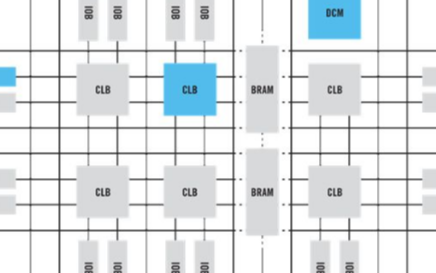

739 每一個系列的FPGA都有其相應(yīng)的內(nèi)部結(jié)構(gòu)),FPGA芯片主要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌專用硬件模塊。

2022-10-25 09:01:05 1818

1818 比特流是一個常用詞匯,用于描述包含FPGA完整內(nèi)部配置狀態(tài)的文件,包括布線、邏輯資源和IO設(shè)置。大多數(shù)現(xiàn)代FPGA都是基于SRAM的,包括Xilinx Spartan 和Virtex 系列

2022-11-30 10:59:17 733

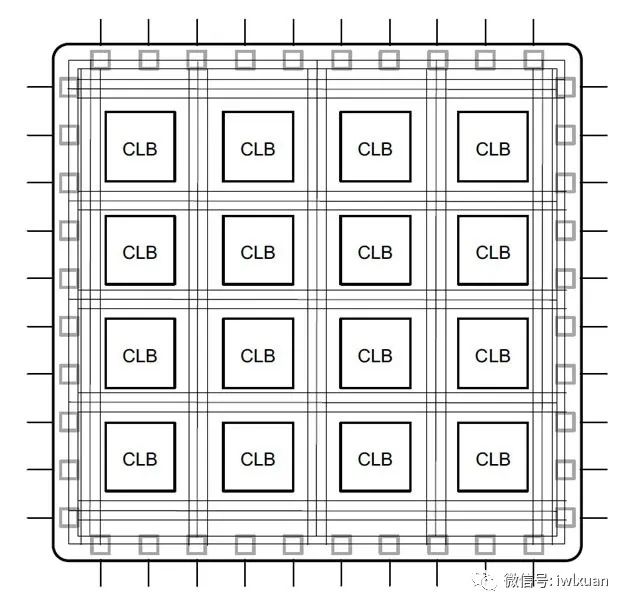

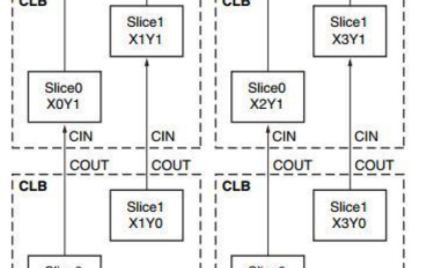

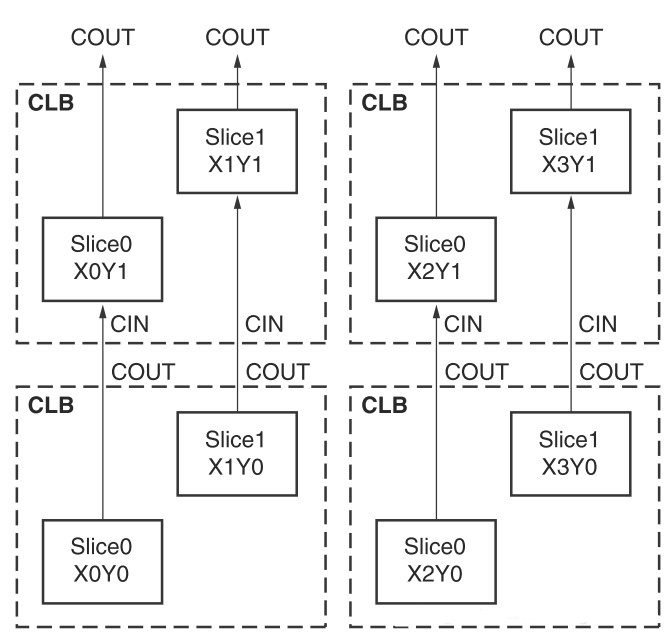

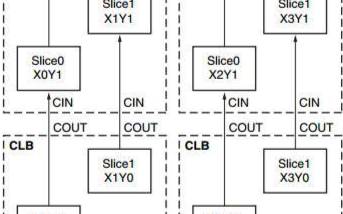

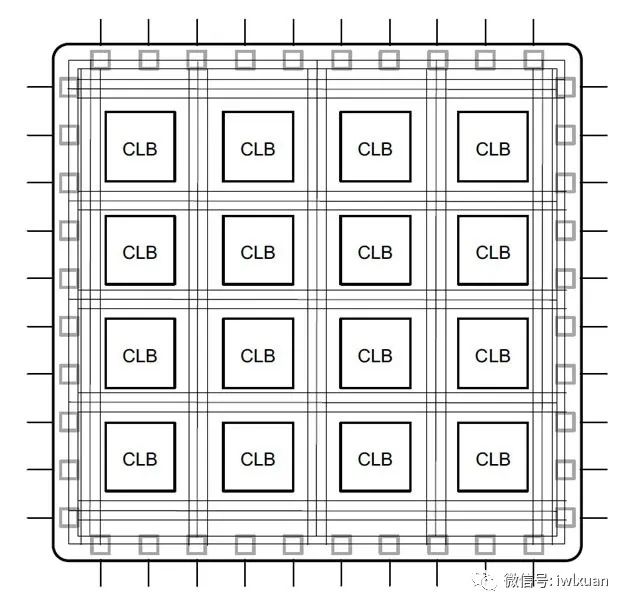

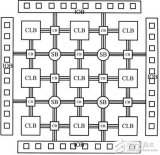

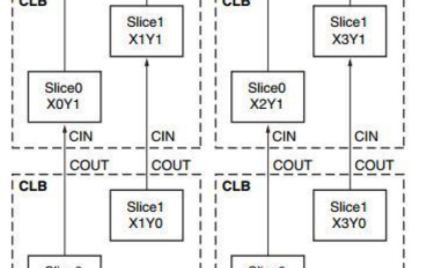

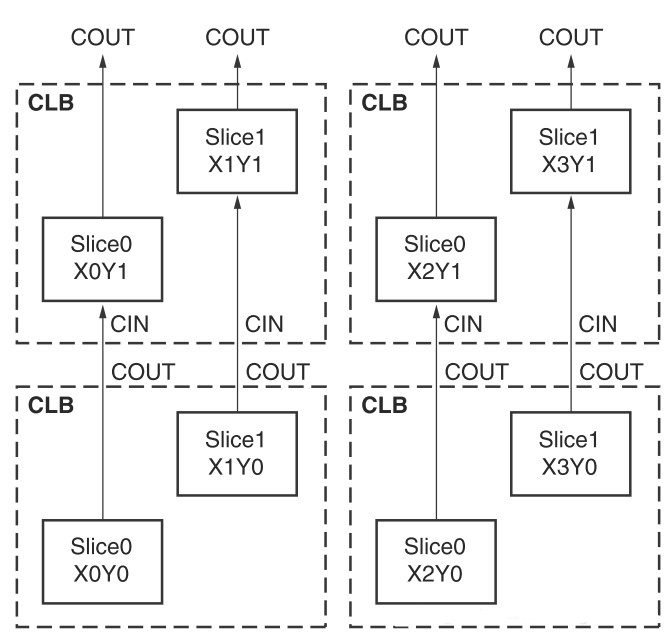

733 以Xilinx主流的7系列為例,一顆FPGA內(nèi)部通常都會有數(shù)千到數(shù)十萬不等的可配置邏輯塊(Configurable Logic Block,簡稱CLB)

2023-08-15 16:09:50 509

509

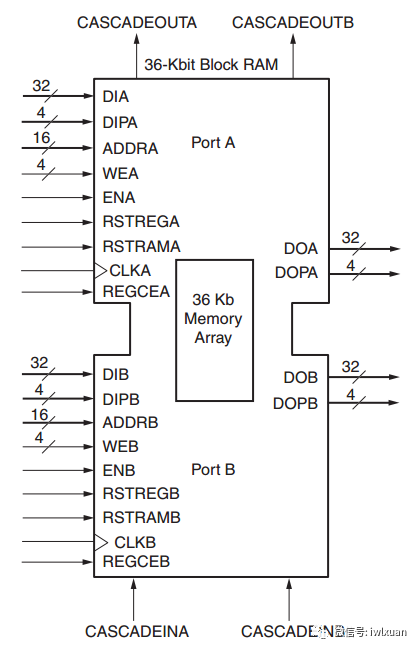

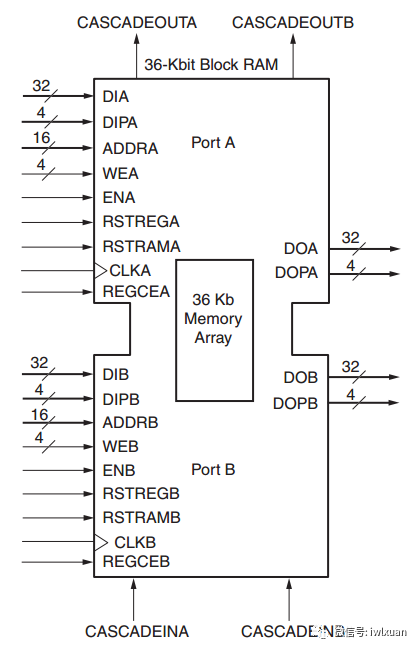

FPGA內(nèi)嵌的存儲器單元包括塊RAM(BRAM)和分布式RAM。

2023-08-15 16:11:05 567

567

Kintex-7 FPGA的內(nèi)部結(jié)構(gòu)相比傳統(tǒng)FPGA的內(nèi)部結(jié)構(gòu)嵌入了DSP48E1,PCIE,GTX,XADC,高速IO口等單元,大大提升了FPGA的性能。

2023-08-24 09:26:56 1393

1393

大多數(shù)FPGA都具有內(nèi)嵌的塊RAM,這大大拓展了FPGA的應(yīng)用范圍和靈活性。塊RAM可被配置為單端口RAM、雙端口RAM、內(nèi)容地址存儲器(CAM)以及FIFO等常用存儲結(jié)構(gòu)。RAM、FIFO是比較普及的概念,在此就不冗述。

2023-08-29 10:14:50 1367

1367

51單片機(jī)的內(nèi)部結(jié)構(gòu)簡介內(nèi)部結(jié)構(gòu)簡介51單片機(jī)是指集成在一個芯片上的一個微型計(jì)算機(jī),它的各種功能,包括CPU、存儲器、基本輸出/輸入接口、定時器、中斷系統(tǒng) 等。8051單片機(jī)是MC—51系列單片機(jī)中

2021-07-22 09:19:57

8051內(nèi)部結(jié)構(gòu)供大家參考。

2013-12-17 08:59:04

即可。

下面是一個4輸入與門的例子。

二、基于查找表(LUT)的FPGA的結(jié)構(gòu)

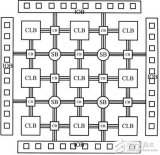

我們看一看Xilinx Spartan-II的內(nèi)部結(jié)構(gòu),如下圖:

Spartan-II主要包括CLBs

2023-11-03 11:18:38

求FPGA內(nèi)部資源{:soso_e100:}相關(guān)資料,發(fā)lishenghhuc@126.com,謝謝

2012-09-27 16:55:44

下面給大家介紹FPGA LUT的結(jié)構(gòu)

2018-07-09 04:57:10

這個MAX II器件的邏輯結(jié)構(gòu)在altera的器件中非常具有典型性,altera的FPGA也基本都是類似的內(nèi)部結(jié)構(gòu)。在器件的周圍布滿了I/O塊,這些I/O塊直接連接控制著器件外部裸露的I/O管腳。I/O

2015-01-27 11:43:10

可重構(gòu)設(shè)計(jì)是指利用可重用的軟、硬件資源,根據(jù)不同的應(yīng)用需求,靈活地改變自身體系結(jié)構(gòu)的設(shè)計(jì)方法。FPGA器件可多次重復(fù)配置邏輯的特性使可重構(gòu)系統(tǒng)成為可能,使系統(tǒng)兼具靈活、便捷、硬件資源可復(fù)用等性能

2011-05-27 10:22:36

,實(shí)際上每一個系列的FPGA都有其相應(yīng)的內(nèi)部結(jié)構(gòu)),FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌

2017-05-09 15:10:02

(LUT)的FPGA的結(jié)構(gòu)我們看一看xilinx Spartan-II的內(nèi)部結(jié)構(gòu),如下圖: xilinx Spartan-II 芯片內(nèi)部結(jié)構(gòu)Slices結(jié)構(gòu)Spartan-II主要包括CLBs,I

2012-04-28 14:57:28

使能的觸發(fā)器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時序邏輯設(shè)計(jì)。一般來說,比較經(jīng)典的基本可編程單元的配置是一個寄存器加一個查找表,但不同廠商的寄存器和查找表的內(nèi)部結(jié)構(gòu)有一定的差異,而且

2019-09-24 11:54:53

使能的觸發(fā)器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時序邏輯設(shè)計(jì)。一般來說,比較經(jīng)典的基本可編程單元的配置是一個寄存器加一個查找表,但不同廠商的寄存器和查找表的內(nèi)部結(jié)構(gòu)有一定的差異,而且

2016-07-16 15:32:39

使能的觸發(fā)器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時序邏輯設(shè)計(jì)。一般來說,比較經(jīng)典的基本可編程單元的配置是一個寄存器加一個查找表,但不同廠商的寄存器和查找表的內(nèi)部結(jié)構(gòu)有一定的差異,而且

2016-08-23 10:33:54

使能的觸發(fā)器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時序邏輯設(shè)計(jì)。一般來說,比較經(jīng)典的基本可編程單元的配置是一個寄存器加一個查找表,但不同廠商的寄存器和查找表的內(nèi)部結(jié)構(gòu)有一定的差異,而且

2016-09-18 11:15:11

使能的觸發(fā)器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時序邏輯設(shè)計(jì)。一般來說,比較經(jīng)典的基本可編程單元的配置是一個寄存器加一個查找表,但不同廠商的寄存器和查找表的內(nèi)部結(jié)構(gòu)有一定的差異,而且

2016-10-08 14:43:50

00000000000001000010....0...01111111111 二.基于查找表(LUT)的FPGA的結(jié)構(gòu) 我們看一看xilinx Spartan-II的內(nèi)部結(jié)構(gòu),如下圖:xilinx

2008-05-20 09:46:10

SoCFPGA器件在一個器件中同時集成了處理器和FPGA體系結(jié)構(gòu)。將兩種技術(shù)合并起來具有很多優(yōu)點(diǎn),包括更高的集成度、更低的功耗、更小的電路板面積,以及處理器和FPGA之間帶寬更大的通信等等。這一同類最佳的器件發(fā)揮了處理器與FPGA系統(tǒng)融合的優(yōu)勢,同時還保留了獨(dú)立處理器和FPGA方法的優(yōu)點(diǎn)。

2019-09-26 07:59:27

CTLE的結(jié)構(gòu)中都包括什么?CTLE 由什么構(gòu)成?

2021-03-06 07:39:00

IGBT的工作原理和作用是什么?IGBT的內(nèi)部結(jié)構(gòu)是怎樣組成的?IGBT的特點(diǎn)有哪些?

2021-10-15 06:01:58

OLED內(nèi)部結(jié)構(gòu)主要結(jié)構(gòu)主要結(jié)構(gòu)包括,MCU、 (經(jīng)典款用的是SSD1306;方屏SSD1317;豎屏SH1107;有些新款用的是SSD1315)GDDRAM(我們寫入的顯示數(shù)據(jù)存放在這里)、Command register(命令寄存器,寫入的命令放在這里)等部分。各芯片數(shù)據(jù)手冊鏈接如下:SSD1306

2022-02-17 07:45:10

Pbuf是什么?Pbuf的內(nèi)部結(jié)構(gòu)是怎樣的?UDP處理的輸入輸出的流程是怎樣的?

2021-11-03 07:37:04

SAC內(nèi)部是個什么結(jié)構(gòu)呢?如何使用SAC呢?主要用在哪些方面呢

2021-10-09 06:19:21

Xilinx_FPGA_內(nèi)部結(jié)構(gòu)深入分析存儲單元存儲單元可以配置為D觸發(fā)器,就是我們常說的FF,Xilinx稱之為FD;也可以配置為鎖存器,Xilinx稱之為LD。輸出和三態(tài)通路各有一對寄存器外加一

2012-08-02 22:48:10

光耦內(nèi)部結(jié)構(gòu)原理光耦內(nèi)部結(jié)構(gòu): 光耦合器是以光形式傳遞信號的,內(nèi)部電路是由光敏三極管和發(fā)光二極管組合成一個電子元件被封裝在個塑料殼內(nèi),接入電路后,輸入端的電信號

2010-06-19 10:45:17

⑴ 結(jié)合Xilinx、Altera 等公司的FPGA 芯片,簡要羅列一下FPGA 內(nèi)部的資源或?qū)S媚K,并簡要說明這些資源的一些作用或用途。(至少列出5 項(xiàng),越多越好)⑵ 如果,對內(nèi)部特定資源,曾有

2012-03-08 11:03:49

有沒有人知道信號在fpga內(nèi)部結(jié)構(gòu)上運(yùn)行的最大頻率?我無法在數(shù)據(jù)表中找到它。理論是灰色的,只有生命之樹永遠(yuǎn)!以上來自于谷歌翻譯以下為原文is there anyone knows

2019-01-30 08:26:43

` 本帖最后由 HUANGYEZHIYING 于 2016-3-16 10:51 編輯

以我現(xiàn)在的水平來說FPGA內(nèi)部結(jié)構(gòu),那簡直就是管中窺豹,盲人摸象,螳臂擋車,豬鼻子插大蒜,總之,定會獻(xiàn)丑

2016-03-10 18:46:28

公司的器件中非常具有典型性,Altera公司的FPGA也基本都是類似的內(nèi)部結(jié)構(gòu)。在器件的周圍布滿了I/O塊,這些I/O塊直接連接控制著器件外部裸露的I/O管腳。I/O塊中包括了雙向的I/O緩沖以及一些

2017-11-21 22:28:24

單片機(jī)內(nèi)部結(jié)構(gòu)分析單片機(jī)的基本概念存儲器的工作原理

2021-02-19 06:27:20

變頻器內(nèi)部結(jié)構(gòu)_變頻器內(nèi)部結(jié)構(gòu)圖 1.主控電路 主要功能如下:(1)接受各種信號 1)在功能預(yù)置階段,接受對各功能的預(yù)置信號: 2)接受從鍵盤或外接輸入端子輸入的給定信號; 3)接受從外接輸入端子

2016-09-05 10:49:17

學(xué)fpga的內(nèi)部結(jié)構(gòu)和各接口實(shí)驗(yàn)怎么學(xué),看什么資料

2014-05-10 18:38:05

運(yùn)行的高速公路網(wǎng)絡(luò)一樣,為FPGA外部高速接口和內(nèi)部可編程邏輯的數(shù)據(jù)傳輸提供了超高帶寬(~27Tbps)。圖1Speedster 7t FPGA結(jié)構(gòu)圖NoC使用一系列高速的行和列網(wǎng)絡(luò)通路在整個FPGA

2020-05-12 08:00:00

為什么fpga內(nèi)部每個小的模塊的輸出輸入都有一個選擇是寄存器輸入還是直接輸入的選擇器,設(shè)置這樣是出于什么考慮

2014-10-05 13:59:54

在fpga內(nèi)部LE基本單元里,都有一個carry chain,誰能解釋一下這個carry chain的具體作用

2015-07-16 21:02:39

`芯片封裝內(nèi)部結(jié)構(gòu)經(jīng)典封裝知識,內(nèi)部結(jié)構(gòu)完美呈現(xiàn),分析芯片封裝的每一個知識點(diǎn)。[hide][/hide]`

2008-06-11 16:10:13

我想了解下FPGA的硬件內(nèi)部結(jié)構(gòu),有沒有針對FPGA內(nèi)部的詳細(xì)硬件介紹的書籍推薦一下?

2019-05-13 00:09:55

`賣家所提供的資料太少了,希望各位大牛為我分析一下這個設(shè)備的內(nèi)部結(jié)構(gòu)。`

2019-01-18 17:52:49

主要講解了fpga設(shè)計(jì)、方法和實(shí)現(xiàn)。這本書略去了不太必要的理論、推測未來的技術(shù)、過時工藝的細(xì)節(jié),用簡明、扼要的方式描述fpga中的關(guān)鍵技術(shù)。主要內(nèi)容包括:設(shè)計(jì)速度高、體積小、功耗低的體系結(jié)構(gòu)方法

2012-03-01 14:59:23

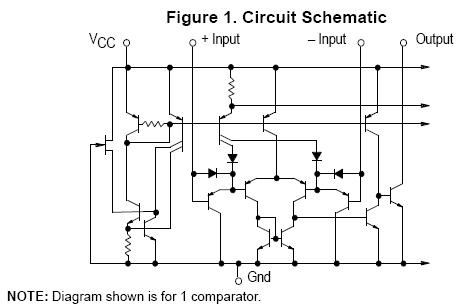

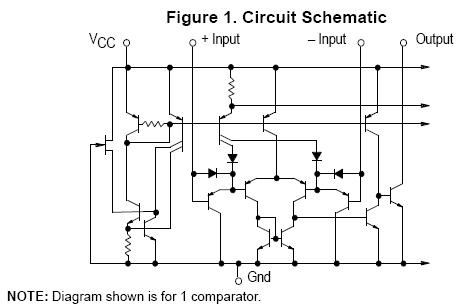

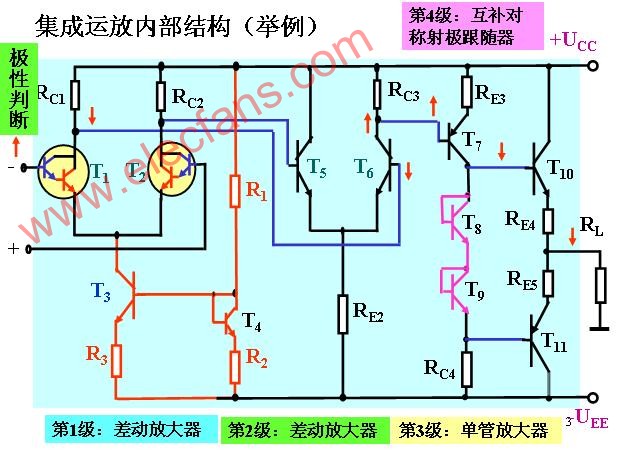

lm339內(nèi)部電路結(jié)構(gòu)

2008-01-18 10:39:39 3229

3229

華為NodeB的內(nèi)部結(jié)構(gòu)和單板介紹

華為BTS3812結(jié)構(gòu)如下:

華

2009-06-30 09:33:14 2988

2988

三極管的結(jié)構(gòu)

三極管的內(nèi)部結(jié)構(gòu)為兩個PN結(jié),由三層半導(dǎo)體區(qū)形成的。

2009-09-23 08:19:37 37980

37980

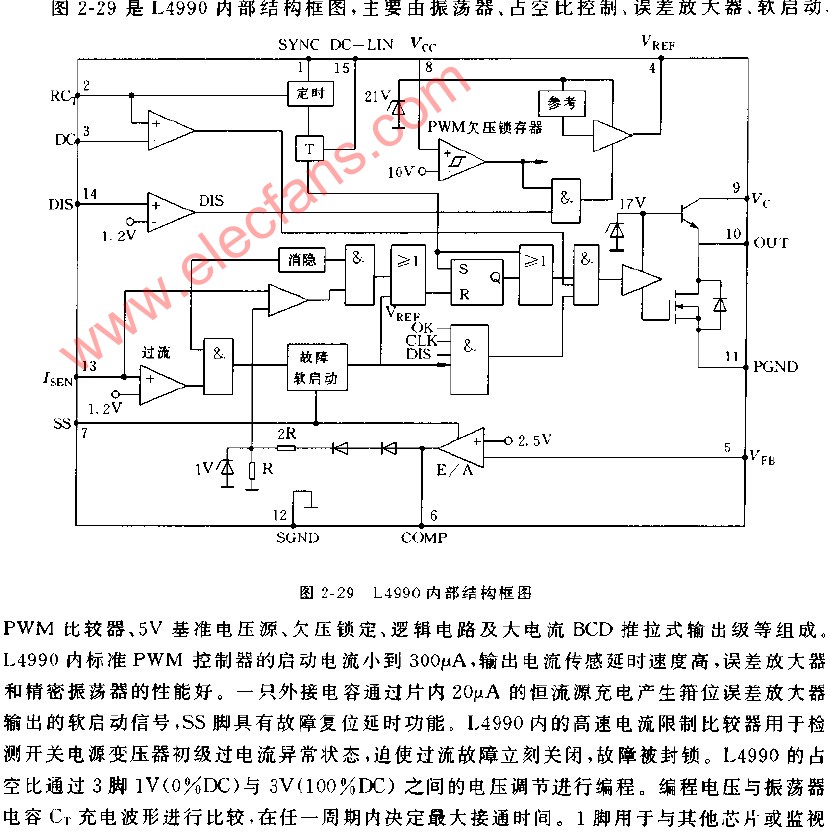

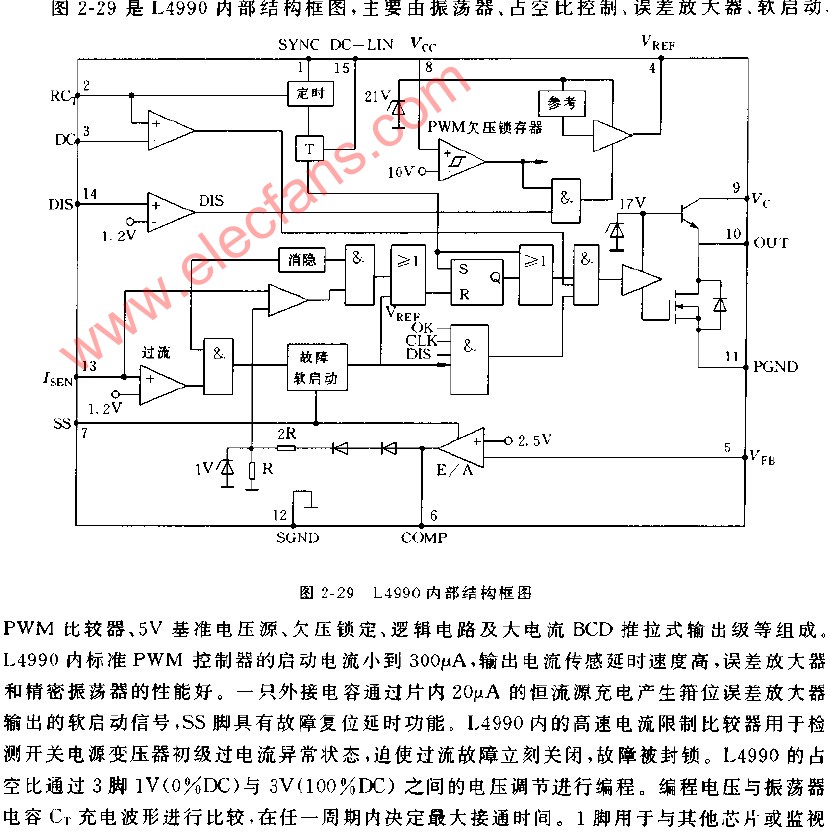

L4990內(nèi)部結(jié)構(gòu)框圖

2009-10-15 11:52:44 714

714

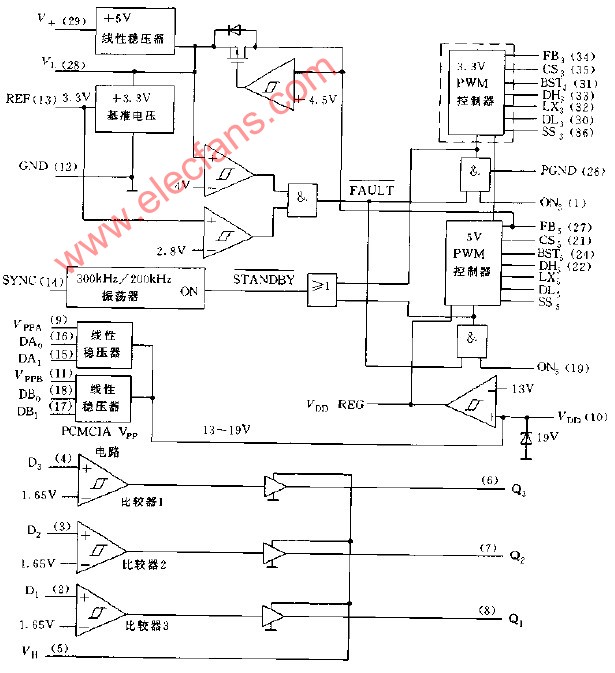

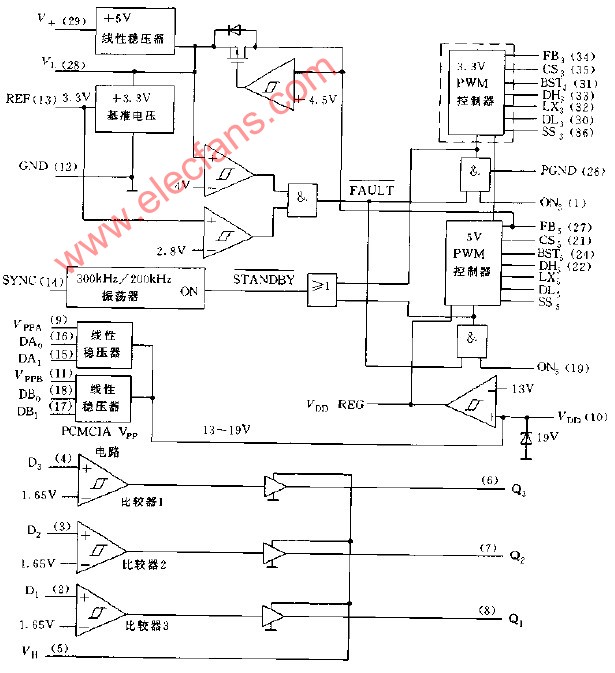

MAX782內(nèi)部結(jié)構(gòu)框圖

內(nèi)部框圖

2009-11-14 16:24:13 873

873

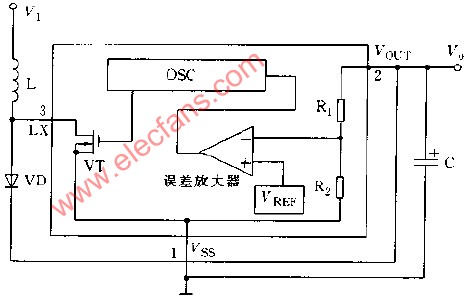

RH5RC內(nèi)部結(jié)構(gòu)框圖.

RH5RC內(nèi)部結(jié)構(gòu)框圖如圖所示,它由基

2009-11-14 16:43:07 838

838

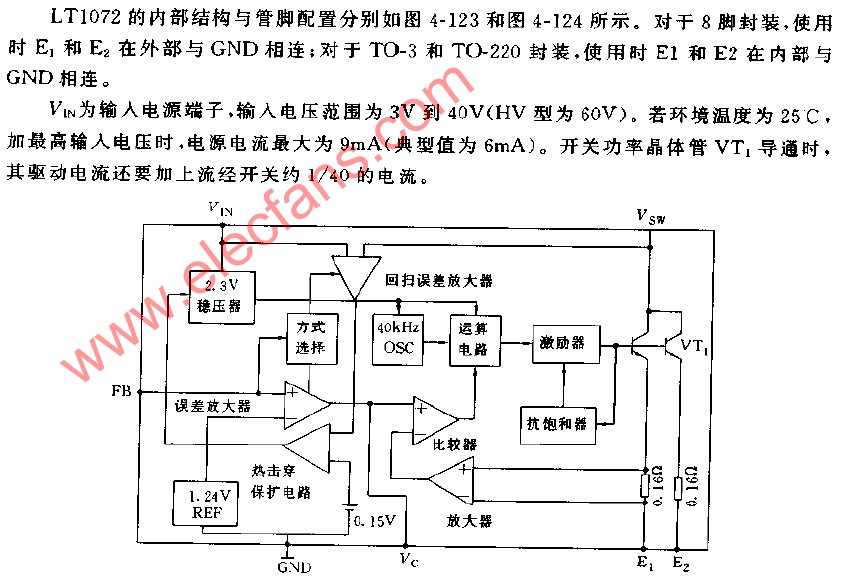

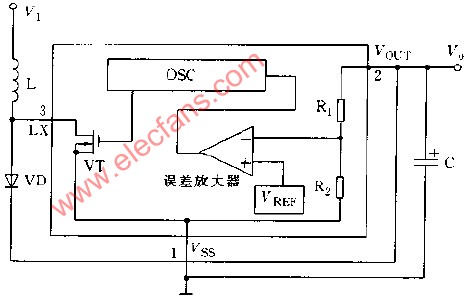

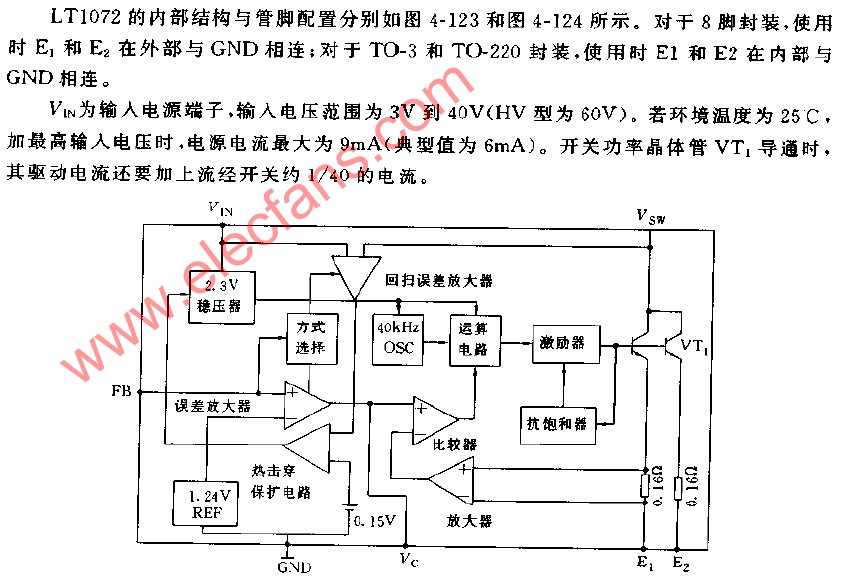

LT1072的內(nèi)部結(jié)構(gòu)框圖

2009-11-14 16:59:08 907

907

蓄電池內(nèi)部結(jié)構(gòu)

2009-11-16 14:15:35 5147

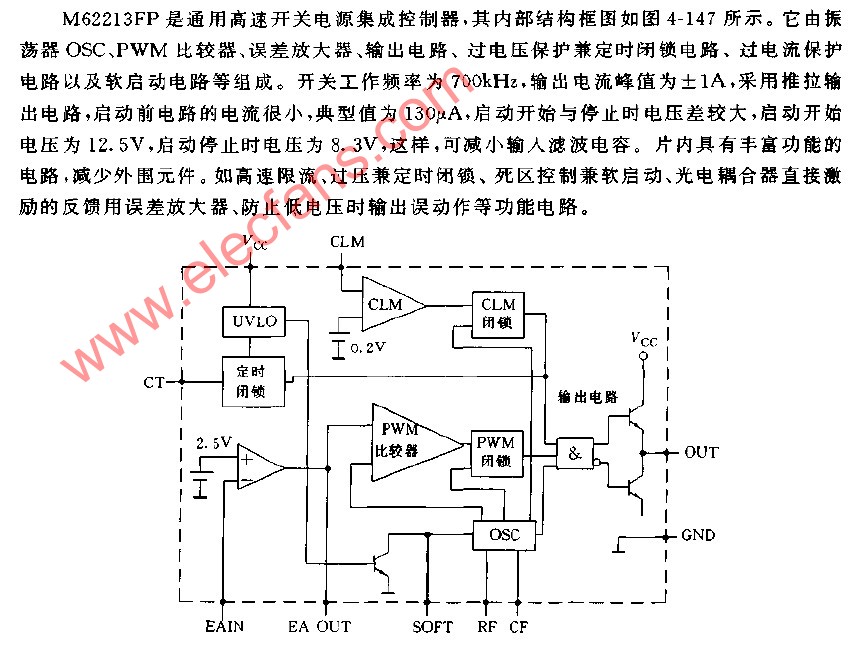

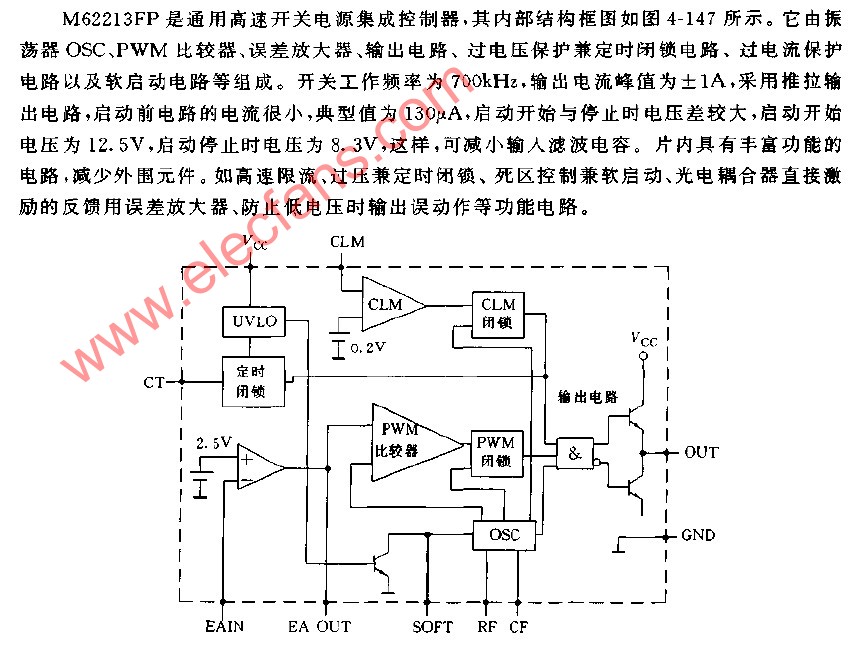

5147 M62213FP內(nèi)部結(jié)構(gòu)框圖

2009-12-31 13:13:43 1141

1141

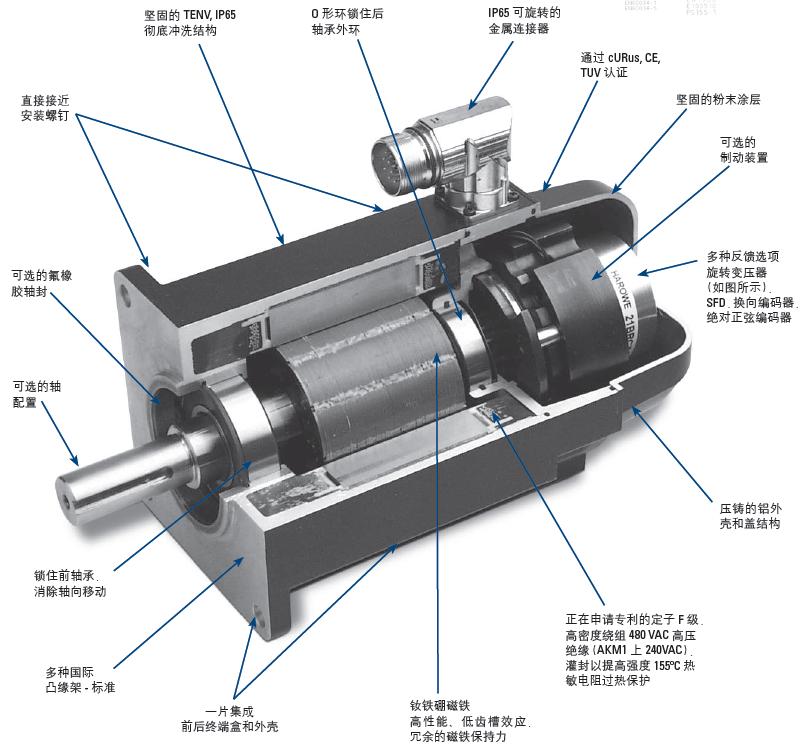

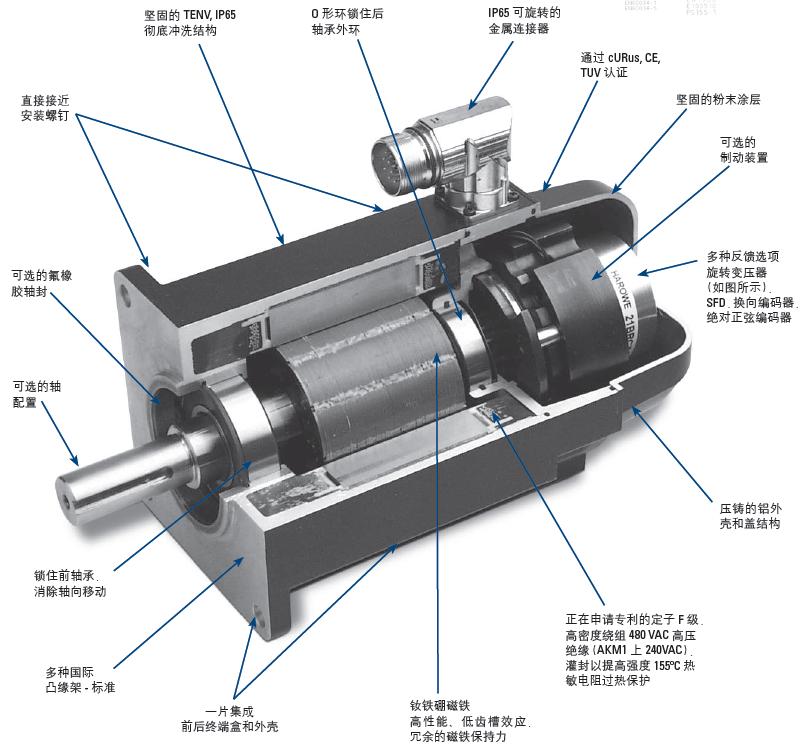

伺服電機(jī)內(nèi)部結(jié)構(gòu)

2010-02-25 17:38:03 4367

4367

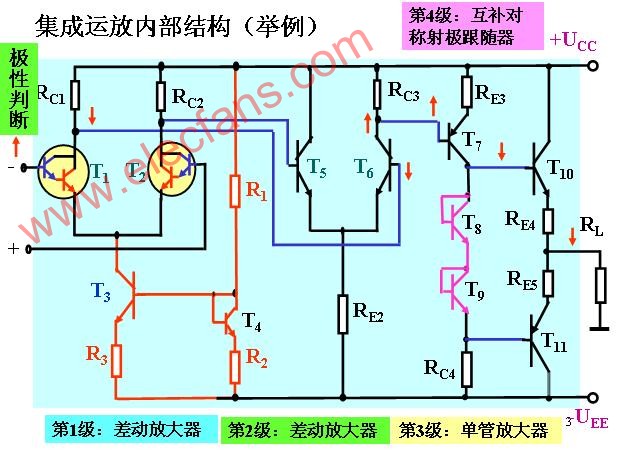

集成運(yùn)放內(nèi)部結(jié)構(gòu)電路圖

2010-04-13 10:30:26 21067

21067

動鐵耳機(jī)的內(nèi)部結(jié)構(gòu)

2010-05-17 18:28:13 9155

9155 高級FPGA設(shè)計(jì)結(jié)構(gòu)

2011-01-10 10:36:50 293

293 RCC器件的內(nèi)部結(jié)構(gòu)及應(yīng)用,反激式開關(guān)電源集成電路包括振蕩器、小占空比產(chǎn)生電路、占空比選擇電路和消隱電路。

2012-03-12 16:36:55 2855

2855

熱賣光耦型號內(nèi)部結(jié)構(gòu)圖

2012-06-26 15:14:36 2495

2495

異步FIFO結(jié)構(gòu)及FPGA設(shè)計(jì),解決亞穩(wěn)態(tài)的問題

2015-11-10 15:21:37 4

4 引入IP核的三維FPGA結(jié)構(gòu)研

2017-01-07 20:32:20 2

2 我這個題目想說明的是,FPGA的內(nèi)部的有其相應(yīng)的Fabric,如何在開發(fā)過程中最好最大限度的使用它。

2017-02-11 12:53:11 1158

1158 元件的內(nèi)部結(jié)構(gòu)

2017-03-04 17:48:29 6

6 FPGA內(nèi)部的RAM M9K

2017-04-07 11:40:04 4

4 FPGA采用了邏輯單元陣列LCA這樣一個概念,內(nèi)部包括可配置邏輯模塊CLB、輸出輸入模塊IOB和內(nèi)部連線三個部分。

2017-05-17 16:35:32 36888

36888

的兼容性。 這里詳細(xì)介紹了Virtex 系列FPGA 芯片的數(shù)據(jù)流大小及結(jié)構(gòu)。Virtex支持一些新的非常強(qiáng)大的配置模式,包括部分重新配置,這種配置機(jī)制被設(shè)計(jì)到高級應(yīng)用中,以便通過芯片的配置接口能夠訪問及操作片內(nèi)數(shù)據(jù)。但想要配置芯片,對它的數(shù)據(jù)流結(jié)構(gòu)的了解是必不可少的。

2017-11-18 11:37:38 2027

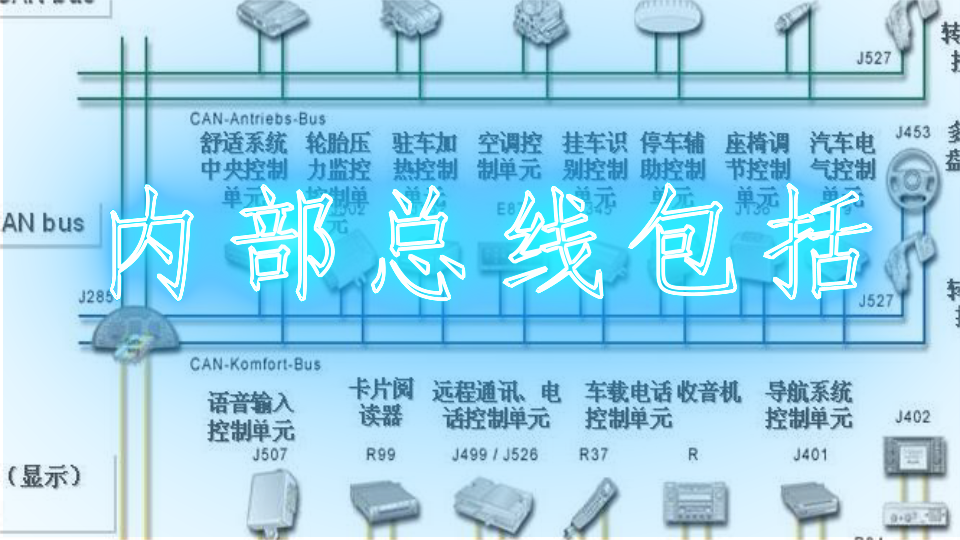

2027 內(nèi)部總線,將處理器的所有結(jié)構(gòu)單元內(nèi)部相連。它的寬度可以是8、16、32、64或128位。本視頻主要詳細(xì)闡述了內(nèi)部總線主要包括了哪些。

2018-11-24 10:43:38 10722

10722

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內(nèi)部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸入輸出模塊IOB(Input Output Block)和內(nèi)部連線(Interconnect)三個部分。

2019-12-02 07:05:00 1522

1522

Xilinx的FPGA的基本結(jié)構(gòu)是一樣的,主要由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核等。

2019-06-11 14:28:17 3600

3600

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內(nèi)部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內(nèi)部連線(Interconnect)三個部分。

2019-06-27 17:52:56 25584

25584 FPGA架構(gòu)主要包括可配置邏輯塊CLB(Configurable Logic Block)、輸入輸出塊IOB(Input Output Block)、內(nèi)部連線(Interconnect)和其它內(nèi)嵌單元四個部分。

2019-10-15 11:19:22 690

690

目前市場上90%以上的FPGA來自于xilinx和altera這兩家巨頭,而這兩家FPGA的實(shí)現(xiàn)技術(shù)都是基于SRAM的可編程技術(shù),FPGA內(nèi)部結(jié)構(gòu)基本一致,所以本文僅以xilinx的7系列FPGA介紹。

2019-10-20 09:03:00 2380

2380

Xilinx的FPGA的基本結(jié)構(gòu)是一樣的,主要由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核等。

2020-01-10 15:39:12 1592

1592

了革命性的新型二維片上網(wǎng)絡(luò)(2D NoC)。2D NoC如同在FPGA可編程邏輯結(jié)構(gòu)上運(yùn)行的高速公路網(wǎng)絡(luò)一樣,為FPGA外部高速接口和內(nèi)部可編程邏輯的數(shù)據(jù)傳輸提供了超高帶寬(~27Tbps

2020-03-04 15:59:39 1517

1517 FPGA架構(gòu)主要包括可配置邏輯塊CLB(Configurable Logic Block)、輸入輸出塊IOB(Input Output Block)、內(nèi)部連線(Interconnect)和其它內(nèi)嵌單元四個部分。

2020-03-20 11:34:44 1125

1125

本文主要以Xilinx Virtex Ⅱ系列為例,對FPGA 內(nèi)部結(jié)構(gòu)作簡要介紹,其內(nèi)容主要來自Xilinx Virtex Ⅱdatasheet 、user guide 、以及其它來自Xilinx 網(wǎng)站上的資料。

2020-09-17 14:40:00 14

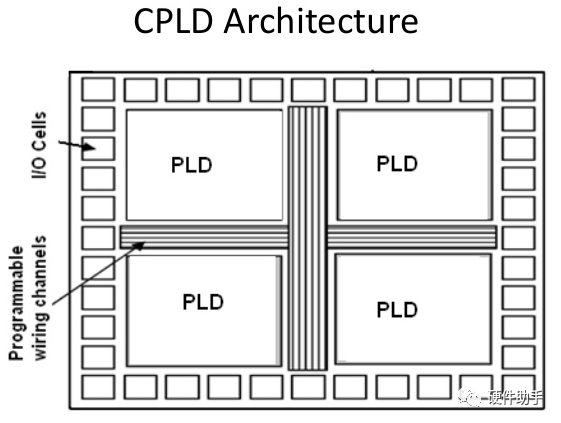

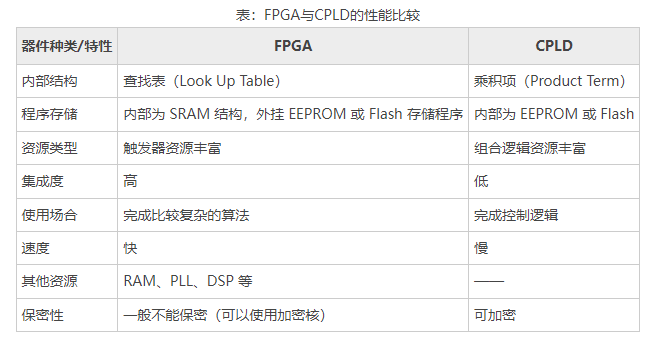

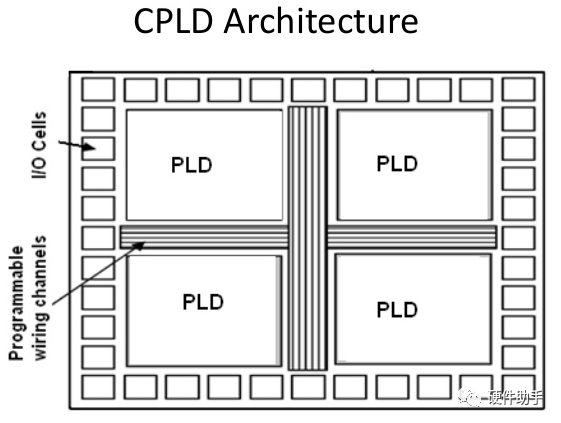

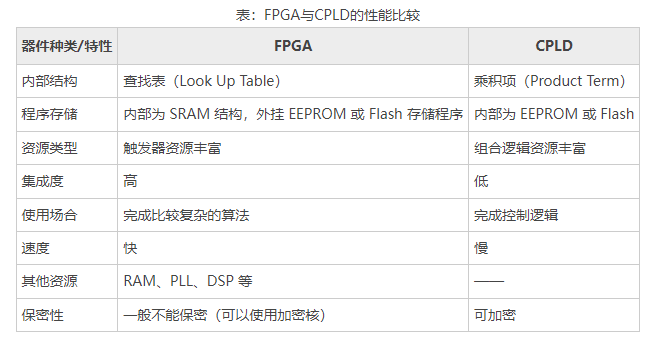

14 本文主要介紹CPLD和FPGA的基本結(jié)構(gòu)。 CPLD是復(fù)雜可編程邏輯器件(Complex Programable Logic Device)的簡稱,FPGA是現(xiàn)場可編程門陣列(Field

2020-09-25 14:56:33 12233

12233

pogopin彈簧針的內(nèi)部結(jié)構(gòu)設(shè)計(jì)常見有反鉆孔、斜剖面、增加圓珠等結(jié)構(gòu),每種結(jié)構(gòu)應(yīng)用不同。

2022-01-14 12:11:53 1271

1271 ?xilinx 的 FPGA 時鐘結(jié)構(gòu),7 系列 FPGA 的時鐘結(jié)構(gòu)和前面幾個系列的時鐘結(jié)構(gòu)有了很大的區(qū)別,7系列的時鐘結(jié)構(gòu)如下圖所示。

2022-07-03 17:13:48 2592

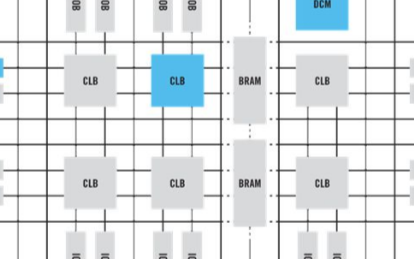

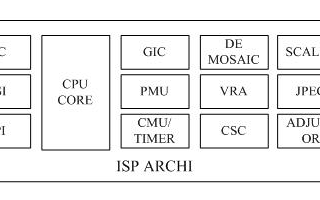

2592 isp的主要內(nèi)部構(gòu)成包括哪些 ISP就是Image Signal Processor 的簡稱,也就是圖像信號處理器。ISP在相機(jī)系統(tǒng)中占有核心主導(dǎo)的地位,是構(gòu)成相機(jī)的重要設(shè)備。ISP是用來對前端圖像

2022-10-18 17:10:22 3110

3110

“時鐘是時序電路的控制者”這句話太經(jīng)典了,可以說是FPGA設(shè)計(jì)的圣言。FPGA的設(shè)計(jì)主要是以時序電路為主,因?yàn)榻M合邏輯電路再怎么復(fù)雜也變不出太多花樣,理解起來也不沒太多困難。

2022-12-02 09:53:11 473

473 ,兩者的功能基本相同,編程等過程也基本相同(燒寫文件不一樣,但是是由軟件自動產(chǎn)生的),只是芯片內(nèi)部的實(shí)現(xiàn)原理和結(jié)構(gòu)略有不同。

2023-06-28 11:30:22 1499

1499

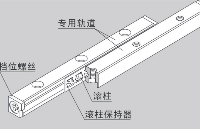

交叉導(dǎo)軌的內(nèi)部結(jié)構(gòu)

2023-08-16 17:52:25 557

557

ldo內(nèi)部結(jié)構(gòu)和工作原理? LDO是線性穩(wěn)壓電源的一種類型,其內(nèi)部結(jié)構(gòu)和工作原理是非常重要的電子工程學(xué)習(xí)內(nèi)容。在本文中,我們將深入了解LDO的內(nèi)部結(jié)構(gòu)和工作原理,包括其關(guān)鍵組件和實(shí)現(xiàn)機(jī)制。 LDO

2023-08-18 15:01:11 1260

1260 激光雷達(dá)的內(nèi)部結(jié)構(gòu)主要包括什么?? 激光雷達(dá)(Lidar)是一種通過激光發(fā)射器向目標(biāo)物發(fā)送激光束,利用接收器接收反彈回來的激光,生成高精度三維點(diǎn)云數(shù)據(jù)的測量工具。它是自動駕駛、機(jī)器人導(dǎo)航等領(lǐng)域

2023-08-23 16:57:44 1649

1649 開關(guān)電源的內(nèi)部損耗大致包括 開關(guān)電源是現(xiàn)代電力電子技術(shù)中的一種高效能、壓降小、重量輕的電源。它具有高效、小型、輕量等優(yōu)點(diǎn),應(yīng)用廣泛。但同時也存在著其內(nèi)部損耗這一問題。開關(guān)電源的內(nèi)部損耗主要包括幾個

2023-08-27 16:13:17 743

743 如果FPGA沒有外部時鐘源輸入,可以通過調(diào)用STARTUP原語,來使用FPGA芯片內(nèi)部的時鐘和復(fù)位信號,Spartan-6系列內(nèi)部時鐘源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

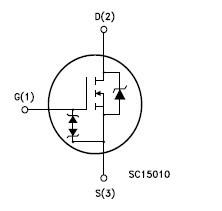

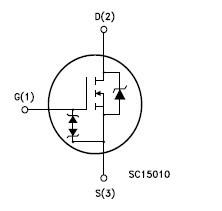

MOSFET和IGBT內(nèi)部結(jié)構(gòu)不同,決定了其應(yīng)用領(lǐng)域的不同。

2023-11-03 14:53:42 500

500

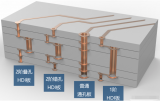

今天畫了幾張多層PCB電路板內(nèi)部結(jié)構(gòu)圖,用立體圖形展示各種疊層結(jié)構(gòu)的PCB圖內(nèi)部架構(gòu)。

2024-01-02 10:10:54 173

173

上具有顯著優(yōu)勢,特別適用于實(shí)時性要求高的應(yīng)用場景。 設(shè)計(jì)靈活與可重構(gòu)性:FPGA芯片屬于硬件可重構(gòu)的芯片結(jié)構(gòu),其內(nèi)部設(shè)置了數(shù)量豐富的輸入輸出單元引腳及觸發(fā)器。這種靈活性使得FPGA能夠根據(jù)不同的應(yīng)用需求,通過重新配置內(nèi)部邏輯結(jié)構(gòu),實(shí)現(xiàn)不同的

2024-03-14 16:46:48 130

130 FPGA芯片的工作原理主要基于其內(nèi)部的可配置邏輯單元和連線資源。包括以下工作原理: 首先,FPGA內(nèi)部包含可配置邏輯模塊(CLB)、輸出輸入模塊(IOB)和內(nèi)部連線(Interconnect)三個

2024-03-14 17:17:51 117

117 FPGA 芯片的內(nèi)部架構(gòu)并沒有沿用類似 PLA 的結(jié)構(gòu),而是采用了邏輯單元陣列(Logic Cell Array,LCA)這樣一個概念,改變了以往 PLD 器件大量使用與門、非門的思想,主要使用查找表和寄存器。

2024-03-21 17:03:33 170

170

電子發(fā)燒友App

電子發(fā)燒友App

評論