案例說明

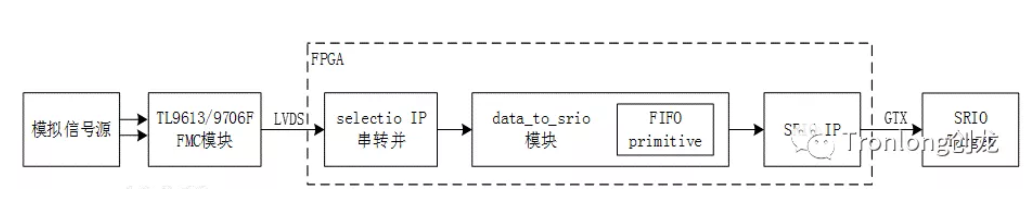

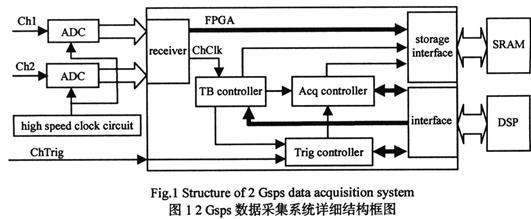

1. Kintex-7 FPGA使用SRIO IP核作為Initiator,通過AD9613模塊采集AD數據。AD9613采樣率為250MSPS,雙通道12bit,12bit按照16bit發送,因此數據量為16bit * 2 * 250M = 8Gbps;

2. AD數據通過SRIO由Kintex-7發送到C6678 DSP(Target)的0x0C3F0000~0x0C3F7FFF的地址空間,數據量為32KByte,使用SWRITE方式,期間每傳16KByte數據后就發送一個DOORBELL信息,讓C6678做乒乓處理。Kintex-7通過SRIO與C6678連接,共4個lane,每個lane的通信速率為5Gbps,數據有效帶寬為20Gbps * 80% = 16Gbps;

3. 采集到的AD數據可分別通過Xilinx Vivado和TI CCS軟件查看波形,并在C6678做FFT處理。

此開發案例基于創龍Kintex-7+C6678評估板TL6678F-EasyEVM展開。

案例框圖

案例演示

硬件連接

(1) 將創龍AD9613高速AD模塊TL9613/9706F(此模塊集成高速DA,DA芯片為AD9706)通過FMC接口與評估板連接。

(2) 信號發生器設置成兩路正弦波輸出,幅度設置:1.5Vpp以及無直流偏置,頻率設置:1MHz。

(3) 信號發生器的兩路輸出分別連接到模塊的ADC_CHA、ADC_CHB。

1.FPGA端

參考TL6678F-EasyEVM評估板光盤用戶手冊《基于下載器的程序固化與加載》文檔中“Vivado下bit文件加載步驟”章節,將tl_fmc_ad9613_srio_tl6678f_xc7k325t.bit文件燒錄到FPGA。燒寫bit文件時,指定調試文件tl_fmc_ad9613_srio_tl6678f_xc7k325t.ltx,可以觀察到ILA調試信號,查看ADC采樣波形。

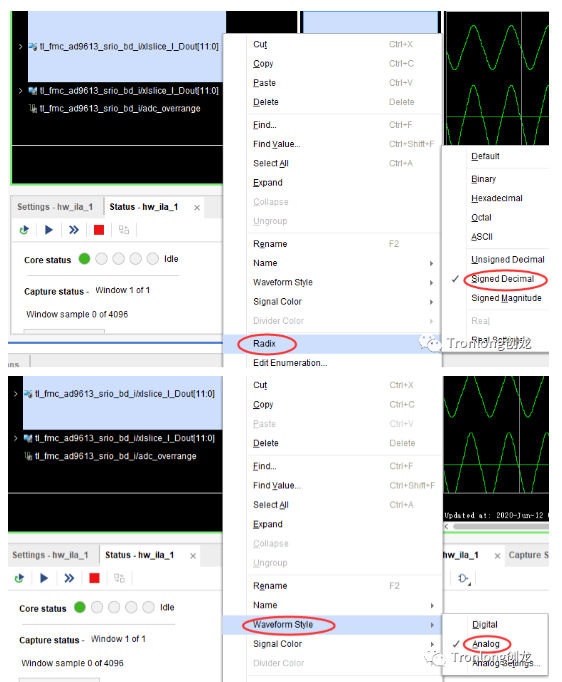

ADC兩路信號在ILA內嵌邏輯分析儀中均設置為有符號數、模擬波形顯示,如下圖所示:

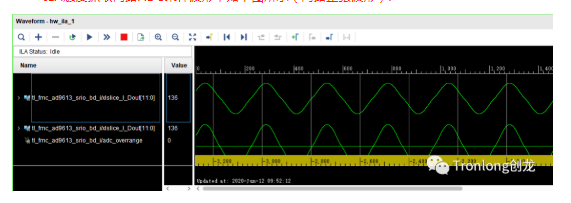

ILA觸發抓取兩路ADC采樣波形,如下圖所示(兩路正弦波形):

2.DSP端

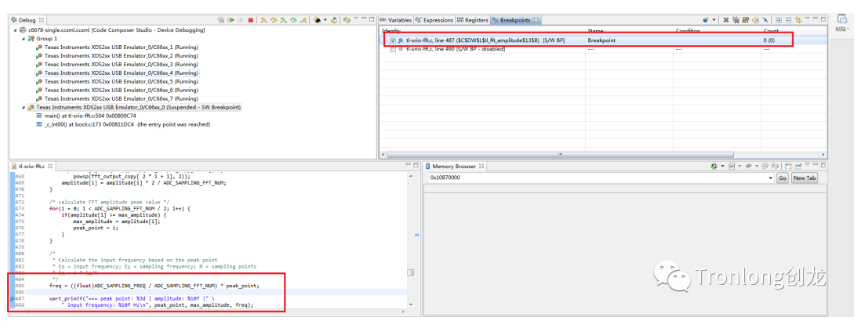

參考TL6678F-EasyEVM評估板光盤用戶手冊《CCS工程的生成與加載》文檔,在“tl-fmc-ad9613-srio/DSP/src”目錄下建立CCS工程并導入到CCS軟件中編譯生成tl-srio-fft.out文件,通過仿真器加載tl-srio-fft.out文件到DSP端。將tl-srio-fft.out下載到C6678 Core0 ~ Core7核中,在tl-srio-fft.c窗口中紅色框標注的地方創建breakpoint,使DSP程序運行后能暫停,如下圖所示:

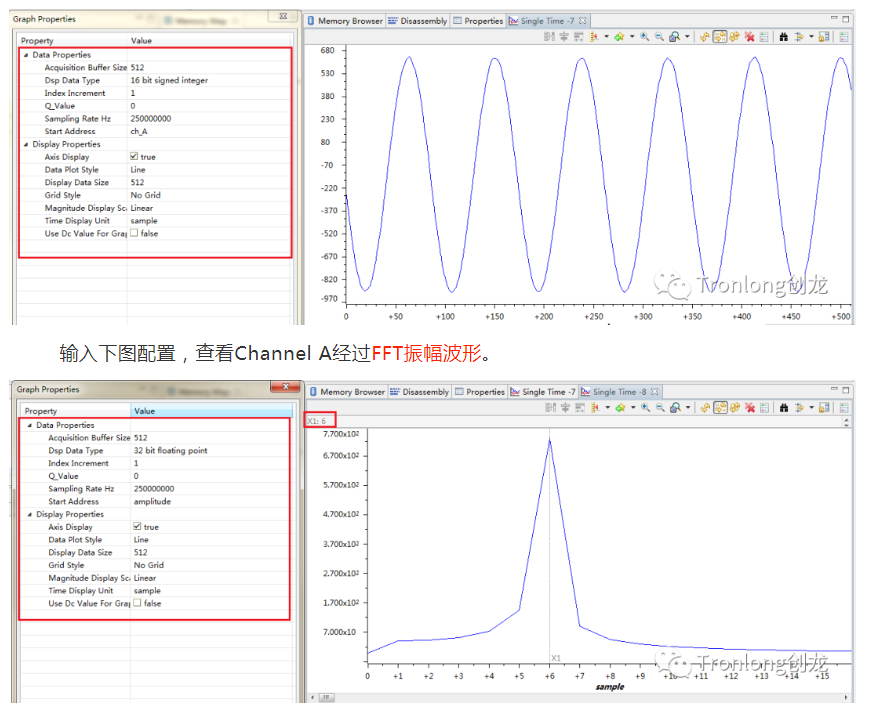

因為Core0負責系統初始化,為確保其他核跟Core0是同步開始傳輸,所以Core0核最后運行(Core0核可查看原始波形以及振幅波形,其他核僅可查看原始波形)。運行程序,DSP程序正常暫停,可通過圖像波形形式查看數據,使用Graph工具,輸入下述配置,查看Channel A波形數據。

若出現波形顯示不正常或沒有波形產生,請參考以下操作:

1.請確保已正常加載GEL文件。

2.請確保Breakpoint設置成功,DSP程序能夠暫停。

3.請硬件斷電重啟后重新燒寫FPGA和DSP程序。

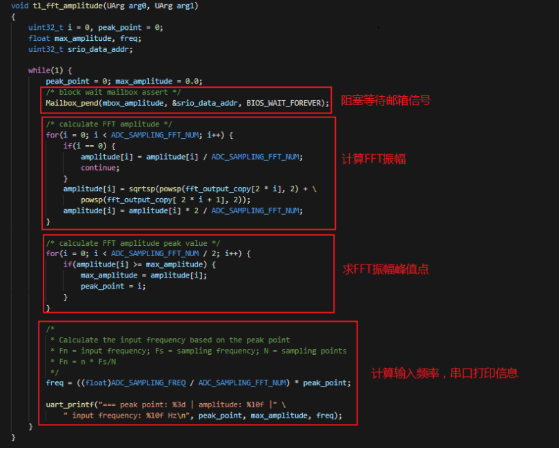

頻率計算

FFT變換點數N=512,AD采樣率Fs為250MSPS。某點n所表示的頻率為:Fn=n*(Fs/N) (n 》=0)。當n=0時,Fn為0,因為第一點表示的是直流分量,所以頻率為0,幅值也為0,因為該正弦波沒有直流分量。

從上面的FFT振幅波形圖中可以看出,Channel A在第6個點處有信號,所以對應的頻率為Fn = 6 * (Fs/N) = 6 * 250MHz / 512 = 2.9296875 MHz。對應原始信號3MHz。

此處存在誤差,目前采樣點為512個,一個點表示Fs/N= 488.281KHZ,所以如果需要提高精度,用戶可以提高采樣點。

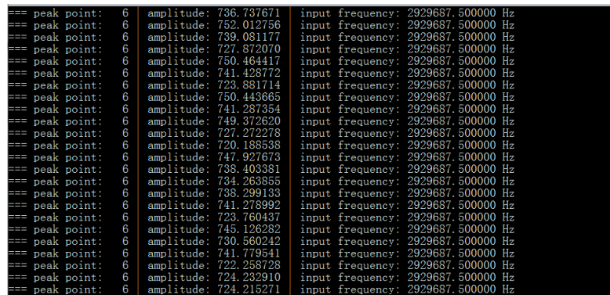

通過查看串口輸入數據,也可查看處理結果。其中peak point代表振幅圖峰值點橫坐標;amplitude代表振幅圖幅值;input frequency根據振幅圖計算的輸入頻率。

關鍵代碼說明

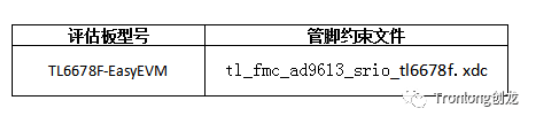

1.管腳約束

例程管腳約束文件位于Vivado工程“srcconstraints”目錄下。

2.FPGA端的代碼

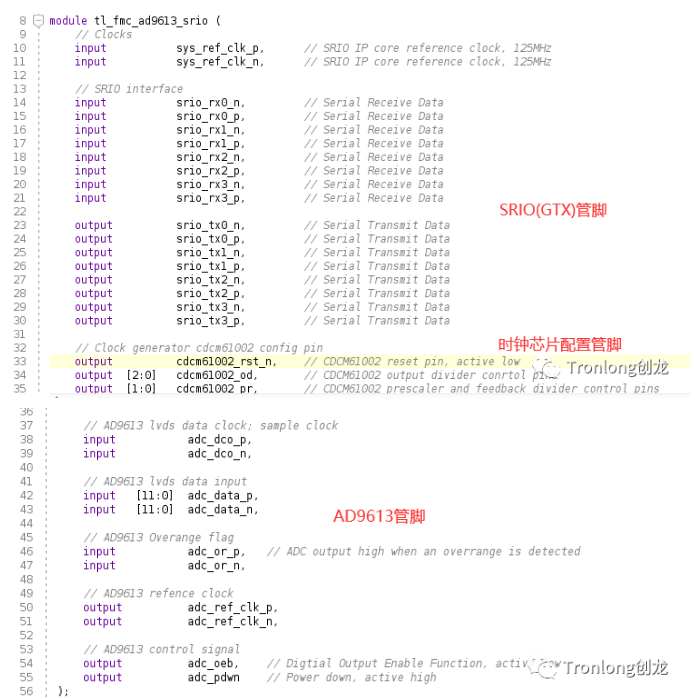

頂層文件tl_fmc_ad9613_srio.v的主要功能:

(1)端口定義。

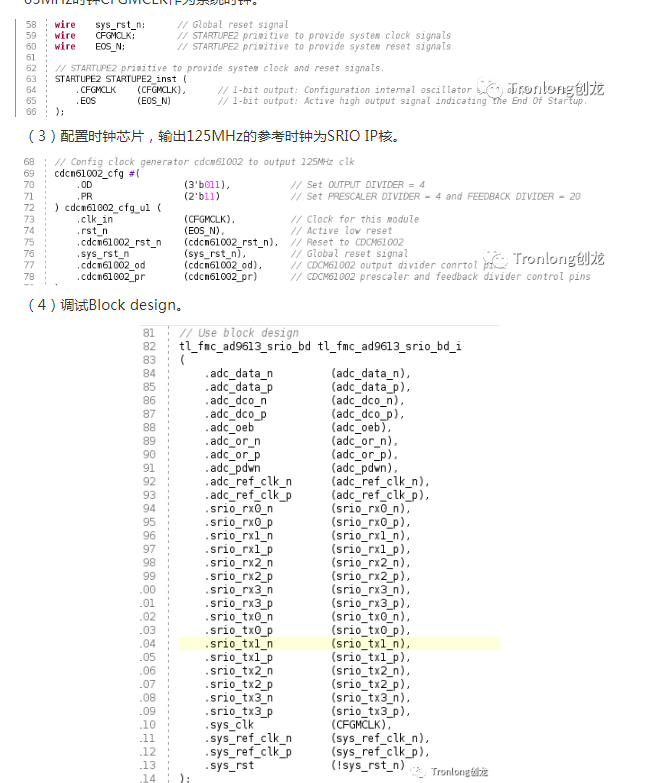

(2)使用STARTUPE2原語提供的EOS作為系統復位信號,使用STARTUPE2原語提供的內部65MHz時鐘CFGMCLK作為系統時鐘。

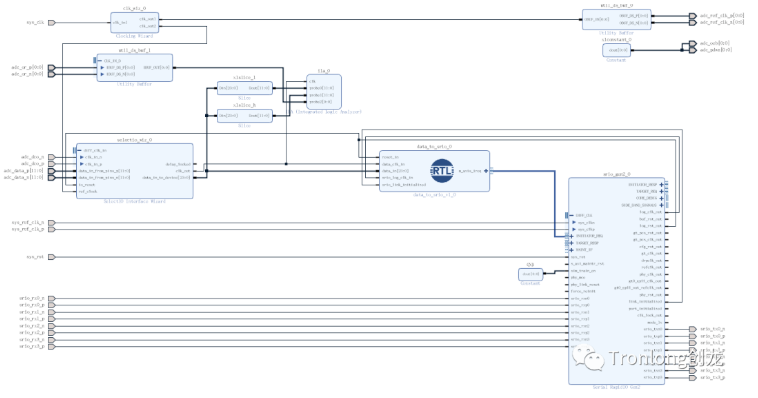

可以查看生成的RTL原理圖:

3.DSP端的代碼

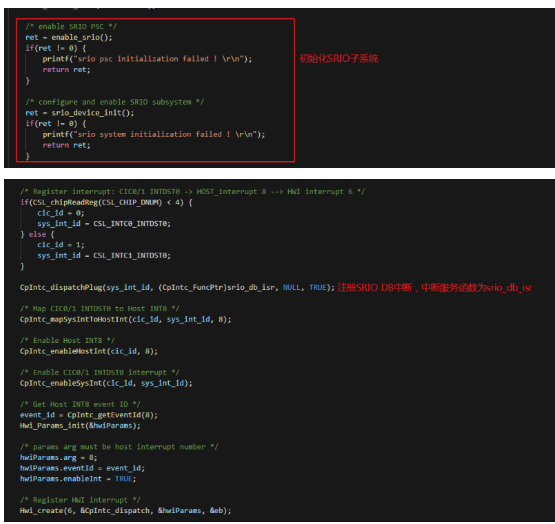

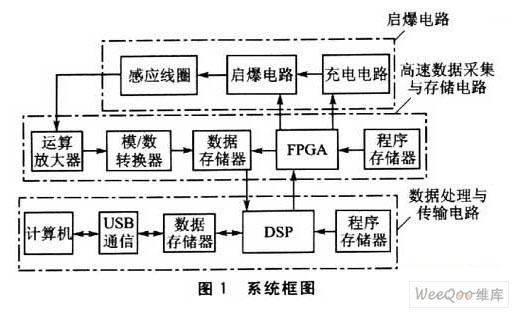

(1)main函數初始化srio子系統,hwi中斷注冊。

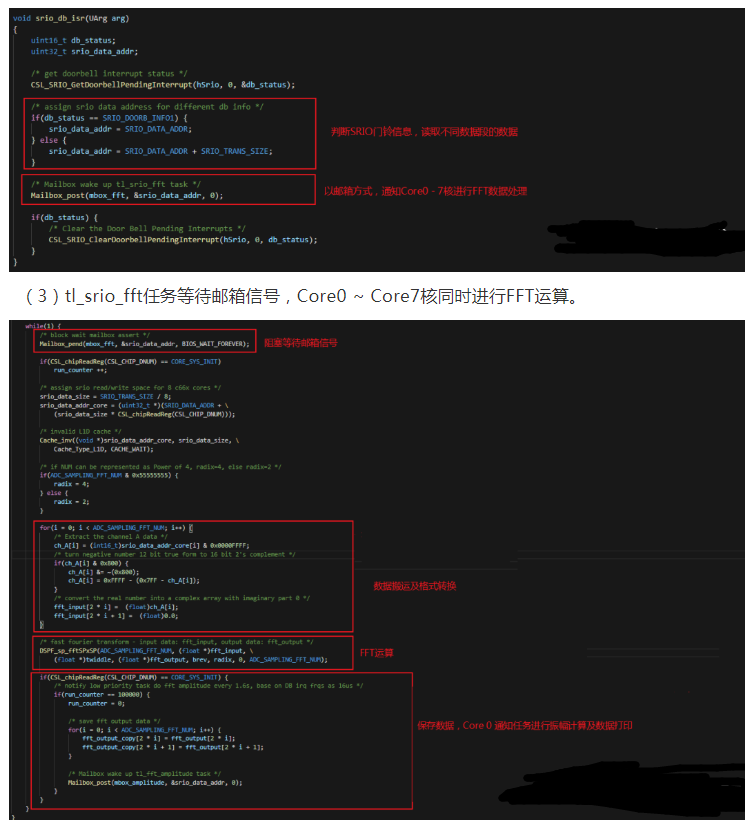

(2)srio_db_isr響應srio doorbell中斷,以郵箱方式通知Core0 ~ Core7核同時進行FFT運算。

(4)tl_fft_amplitude任務等待信號量置位,Core0核進行FFT振幅運算,通過串口打印數據處理結果。

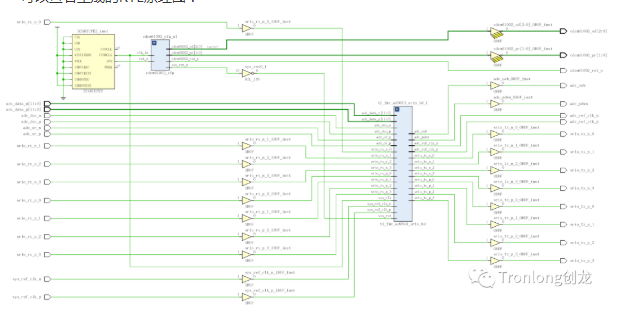

Block Design說明

Block Design如下

1.Select IO IP核配置說明

參考TL6678F-EasyEVM評估板光盤tl-fmc-ad9613例程的IP核與模塊介紹章節。

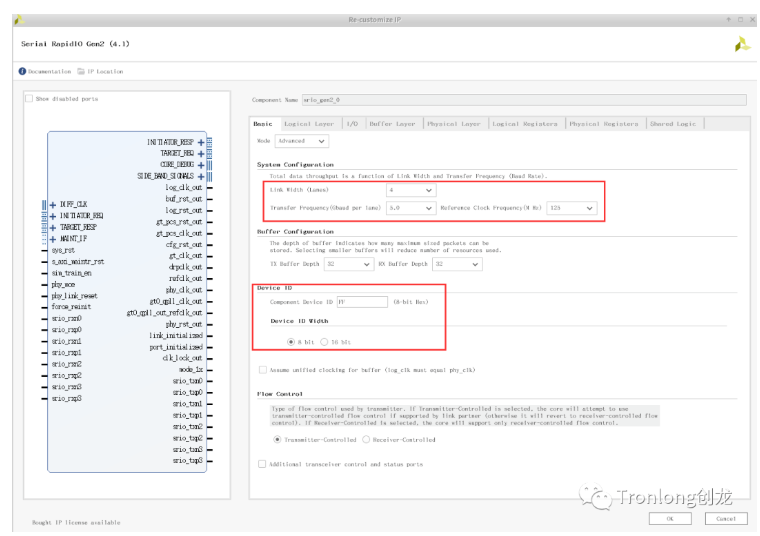

2.SRIO IP配置說明

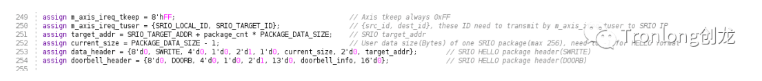

SRIO鏈路寬度設置為4個lane,通信頻率為5Gbps(即每個lane均為5Gbps),參考時鐘為125MHz;設置8bit位寬的ID,且ID=0xFF。

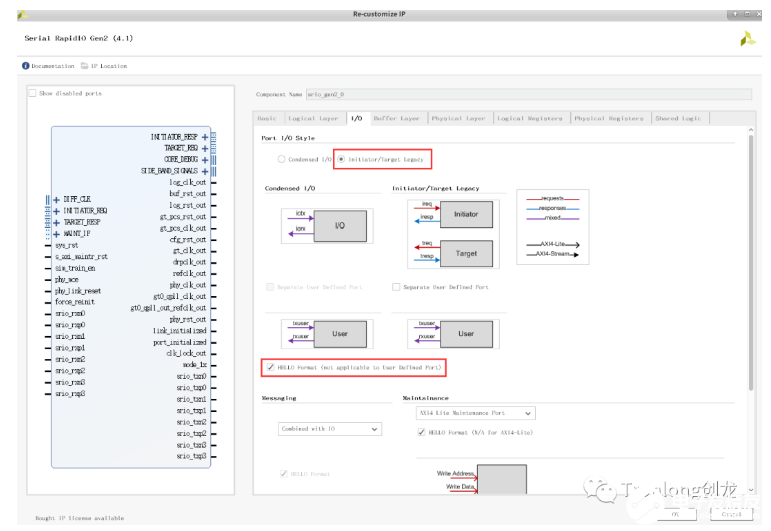

Port I/O Style選擇為Initiator/Target模式,其中Condensed I/O接收和發送均使用一個AXI4-Stream通道,Initiator/Target接收和發送采用不同的AXI4-Stream通道。

I/O Format:I/O端口配置使用HELLO格式包。

其他參數保持保持默認值即可。

更詳細說明請查閱IP核手冊:《pg007_srio_gen2.pdf》。

3.data_to_srio RTL模塊功能

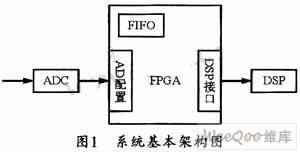

(1)連續不停地將AD9613采集的數據寫入FIFO。

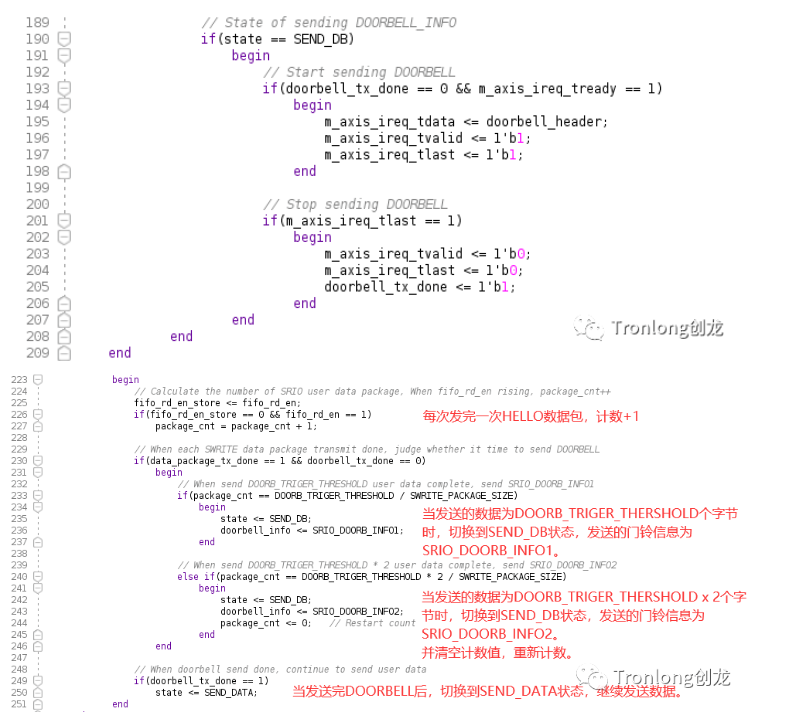

(2)控制FIFO讀操作,每次從FIFO讀取完指定的數據并通過AXI4-stream接口傳輸到SRIO IP。其中本例程每發送16KByte的數據就發送一個DOORBELL信息,通知Target(DSP)對數據做處理。

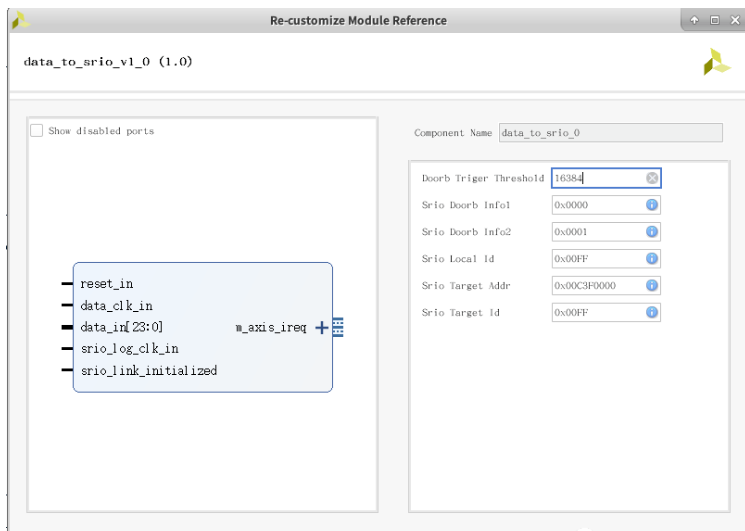

雙擊block degin中的模塊,可配置:

Doorb Triger Threshold: 門鈴觸發閾值,本例設置為16384Bytes = 16KB,即通過SRIO發送16KB的數據后就發送一個DOORBELL信息。

Srio Doorb info1:發送完Doorb Triger Threshold個字節的數據之后發送的門鈴信息。

Srio Doorb info2:發送完2倍的Doorb Triger Threshold個數據之后發送的門鈴信息。

Srio Target Addr:SRIO Target的內存地址。(本例設置的為DSP的MSMC地址0x0C3F0000)

Srio Target Id:SRIO Target的ID。

Srio Local Id:SRIO Iitiator的ID。

代碼解釋

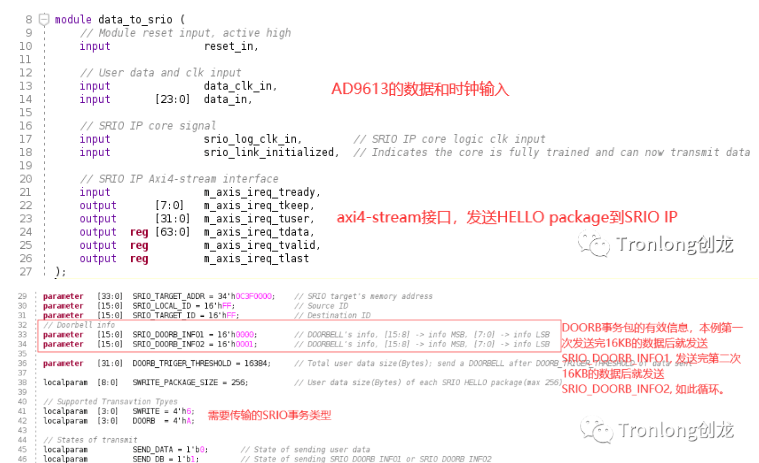

(1)端口定義

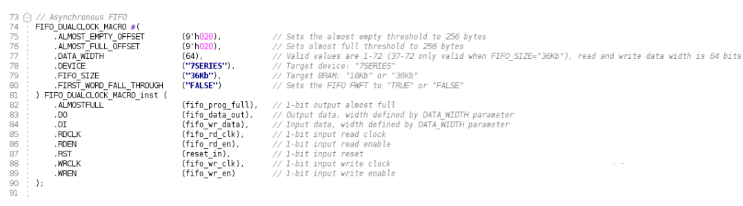

(2)FIFO原語

配置FIFO大小為36 Byte,讀寫數據的位寬為64bit(FIFO深度為512)。

ALMOST_EMPTY_OFFSET和ALMOST_FULL_OFFSET配置為0x20,即32;即當FIFO寫入數據個數大于32個,ALMOST_FULL輸出高電平。

本例FIFO設置位寬為64bit,所以64bit * 32 / 8 = 256 Byte,即當FIFO寫入數據大于256 Byte,ALMOST_FULL會輸出高電平。

因為SRIO的package最大有效數據為256 Byte,為了確保SRIO能傳輸完整的數據包,所以設置FIFO的門限值為256Byte.

FIFO原語詳細說明請查閱:《ug473_7Series_Memory_Resources.pdf》。

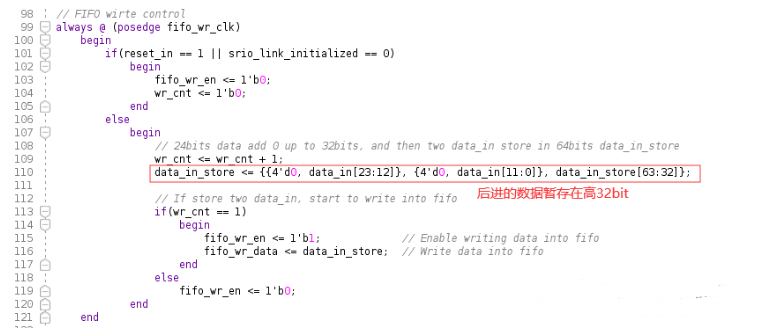

(3)FIFO寫控制

因為AD9613輸出的AD數據為雙通道的24bit,所以分別將兩個通道的數據補成16bit。然后保存到data_in_store中。

因為FIFO的位寬64bit,而上個步驟將AD的雙通道數據補成了32bit,所以每存夠兩個32bit的AD數據,湊成64bit的data_in_store,再使能fifo_wr_en信號,把64bit的數據寫入FIFO。

后寫入的數據存在高32位,發送到SRIO Target端(DSP),方便其按順序處理數據。

其中wr_cnt為一個1bit,計數只有0和1兩個值。

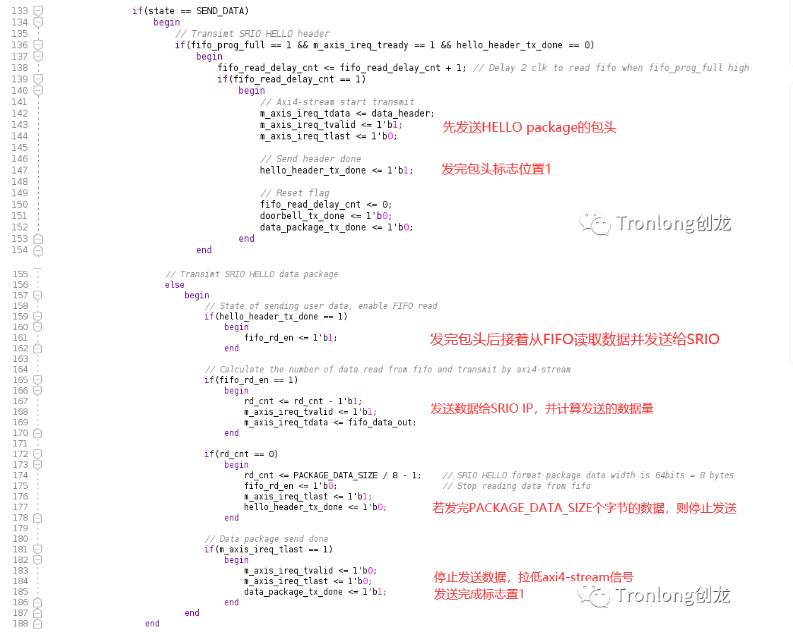

(4)讀取FIFO數據并打包HELLO格式發送數據

(6)狀態切換

本例設置的TOTAL_DATA_SIZE為32KByte,即每發送16KByte的數據包之后發送一個門鈴信息。

資料下載

點擊以下鏈接或掃描二維碼,獲取本案例源碼及TL6678F-EasyEVM評估板詳細資料。

http://site.tronlong.com/pfdownload

點擊鏈接:TL6678F-EasyEVM評估板

電子發燒友App

電子發燒友App

評論