D觸發器實現二分頻電路(D觸發器構成的2分頻電路)

2020-03-02 11:05:49

做了一個仿真:key_in作為D觸發器的輸入,led_out作為觸發器輸出,時鐘周期20ns,key_in每10ns隨機變化一次,這樣的設置下,key_in信號的變化沿有時會和時鐘上升沿重合,根據

2022-01-25 22:41:02

電路為什么要有觸發器這種結構?為什么要用時鐘同步起來呢?一個乘法器如果不設計成觸發的會是什么狀態?最近在想電路同步異步的時候想到這個問題。

2016-12-08 17:41:52

不變。所以,觸發器可以記憶1位二值信號。根據邏輯功能的不同,觸發器可以分為RS觸發器、D觸發器、JK觸發器、T和T′觸發器;按照結構形式的不同,又可分為基本RS觸發器、同步觸發器、主從觸發器和邊沿觸發器。

2009-09-16 16:06:45

;nbsp; 將基本RS觸發器,同步RS觸發器,集成J-K觸發器,D觸發器同時集成一個CPLD芯片中模擬

2009-10-10 11:32:55

觸發器實驗1)熟悉常用觸發器的邏輯功能及測試方法。2)了解觸發器邏輯功能的轉換。三.實驗內容及步驟 (1) 基本RS觸發器邏輯功能測試(2) JK觸發器邏輯功能測試(3) D觸發器邏輯功能的測試

2009-03-20 10:01:05

和脈沖延時。各種觸發器均可由分立元件構成,也可由集成電路來實現。但隨著集成電路技術的發展,集成觸發器品種逐漸增加,性能優良,應用日益廣泛。基本觸發電路有R-S觸發器,T觸發器,D觸發器,J-K觸發器等。

2012-06-18 11:42:43

觸發器輸入電路二極管D的作用是只把負的尖脈沖輸入觸發器,還可用來組成加速電路。

2009-09-22 08:28:30

同步復位D觸發器復位信號在所需時鐘邊沿才有效,復位操作需要同步于時鐘故稱作同步復位。代碼如下[code]module d_ff (input clk,input rst_n,input D

2012-03-05 14:02:11

,也就是說先有時鐘上升沿才有q的變化。如果下一個時鐘上升沿沒有到來,那么q的值就保持不變。因此,q的值是在時鐘上升沿之后一點點變化。這就是D觸發器,我們所有的FPGA電路都是基于這個結構來進行

2018-09-20 15:09:45

如圖, 將j-k觸發器用D觸發器代替,剛入門 求教

2014-01-09 20:56:31

JK觸發器和D觸發器所使用的時鐘脈沖能否用邏輯電平開關提供?為什么?

2023-05-10 11:38:04

時,相同的輸入反映在“從”的輸出上,從而使這種類型的觸發器沿或脈沖觸發。然后,當時鐘信號為“高”時,電路接收輸入數據,并在時鐘信號的下降沿將數據傳遞到輸出。換句話說,主從JK觸發器是“同步”設備,因為它僅以時鐘信號的時序傳遞數據。

2021-02-01 09:15:31

`這些單片,正沿觸發的觸發器利用TTL電路來實現具有直接清除輸入的D型觸發器邏輯。滿足建立時間要求的D輸入處的信息將在時鐘脈沖的上升沿傳輸到Q輸出。時鐘觸發發生在特定的電壓電平上,與正向脈沖的躍遷

2021-03-24 16:23:59

jk觸發器設計d觸發器,根據原理圖實現模8加1計數器,來源于西電慕課貌似這個軟件只有5.0和5.12兩個版本。在win10下拖曳器件會發生殘影的現象,而且無法修改連線。雖然有自動連線功能但感覺線連

2021-07-22 08:39:47

求助誰能教設計一個D觸發器

2014-12-24 22:54:35

,也就是說先有時鐘上升沿才有q的變化。如果下一個時鐘上升沿沒有到來,那么q的值就保持不變。因此,q的值是在時鐘上升沿之后一點點變化。這就是D觸發器,我們所有的FPGA電路都是基于這個結構來進行

2017-06-20 09:56:47

在實際的數字系統中,通常把能夠用來存儲一組二進制代碼的同步時序邏輯電路稱為寄存器.由于觸發器內有記憶功能,因此利用觸發器可以方便地構成寄存器。由于一個觸發器能夠存儲一位二進制碼,所以把n個觸發器

2018-10-27 22:38:21

兩個非門電路是如何組成一個D觸發器的?即可通俗說明下D觸發器嗎?

2023-05-10 10:32:03

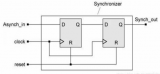

什么是同步邏輯和異步邏輯?同步電路和異步電路的區別在哪?為什么觸發器要滿足建立時間和保持時間?什么是亞穩態?為什么兩級觸發器可以防止亞穩態傳播?

2021-08-09 06:14:00

根據輸入信號改變輸出狀態。把這種在時鐘信號觸發時才能動作的存儲單元電路稱為觸發器,以區別沒有時鐘信號控制的鎖存器。觸發器是一種能夠保存1位二進制數的單元電路,是計算機中記憶裝置的基本單元,由它可以組成

2019-12-25 17:09:20

`如圖所示,圖中第一個觸發器D接第二個觸發器的非Q端,這個時序圖,整不明白啊,我的看法是:當第一個時鐘信號高電平來的時候,第一個觸發器的輸出狀態Q是不能判斷的啊,因為D接在第二個觸發器的非Q端。求大佬指點一下 這個圖,是如何工作的?`

2019-01-16 11:50:35

做個單穩態電路、后端做個雙穩態電路,按下并松開一次按鍵實現輸出狀態翻轉一次。現在有個問題:按下去馬上松開按鍵,很正常;但假如按下去的時間比較長,超過單穩態電路中,電容積分復位第一個D觸發器的時間,在松開

2014-09-25 16:47:34

觸發器沒有使用相同的時鐘信號,需要分析哪些觸發器時鐘有效哪些無效分析步驟和同步時序電路一樣,不過要加上時鐘信號有關D觸發器的例題抄自慕課上的一個題目,注意第二個觸發器反相輸出端同時連接到復位端JK

2021-09-06 08:20:26

。為了避免這種情況,在存儲了所需數據之后,使用稱為“時鐘”或“使能”輸入的附加輸入將數據輸入與觸發器的鎖存電路隔離。結果是,僅當時鐘輸入處于活動狀態時,D輸入條件才會復制到輸出Q。然后,這構成了另一個

2021-02-03 08:00:00

1、在FPGA中使用門級結構設計D觸發器的思路一個邏輯電路是由許多邏輯門和開關組成的,因此用基本邏輯門的模型來描述邏輯電路結構是最直觀的。本實驗設計使用結構描述語句實現D觸發器功能,采用帶異步置位

2022-07-04 16:01:57

,主要是在邊沿的時候。下面來介紹個多級D觸發器濾除邊沿抖動。不說廢話直接上代碼圖片。程序代碼: //----------觸發時鐘控制抖動濾除的時間--------------------reg

2013-12-17 12:19:46

我正在嘗試使用 PTP 實現時鐘同步,請幫忙。

2023-03-31 09:00:46

如何用D觸發器實現2分頻 原理在線等

2016-07-03 19:37:58

本帖最后由 gk320830 于 2015-3-5 20:47 編輯

如何用JK觸發器構成D觸發器 電路圖來人給個圖吧..

2011-11-14 15:21:03

型的觸發器(flip-flops)電路具有指示器,如T(切換)、S-R(設置/重置)J-K(也可能稱為Jack Kilby)和D(延遲)。典型的觸發器包括零個、一個或兩個輸入信號,以及時鐘信號和輸出信號

2018-07-03 11:50:27

單片機內部有大量寄存器, 寄存器是一種能夠存儲數據的電路, 由觸發器構成。1.觸發器觸發器是一種具有記憶存儲功能的電路, 由門電路組成。 常見的觸發器包括: RS 觸發器、 D 觸發器和 JK觸發器

2022-01-20 07:13:51

我在做畢設的時候max232芯片壞掉了,要做畢業設計,現在手頭上只有74ls的2個D觸發器和4個JK觸發器。想求一個mulitsim的電路圖能夠按照rs232協議實現二進制數據的發送和接收。就差

2020-03-20 12:07:51

怎樣去設計一種基于門電路的D觸發器呢?如何對基于門電路的D觸發器進行仿真?

2021-09-14 06:21:42

我要給寄存器送數,希望第一個時鐘脈沖送入輸入的數據,后面的時鐘脈沖都送入另一個寄存器里的數據。問了下老師說用D觸發器輸入1就能實現,實在是不會啊,具體怎么實現呢,或者有什么其它的實現方法呢?

2020-04-03 23:16:17

習時把這一章分為兩節,它們分別是:§5、1 時序電路的概述§5、2 觸發器 5、1 時序電路的概述 這一節我們來學習一些關于時序電路的概念,在學習時要注意同步時序電路和異步時序電路的區別一:時序電路

2018-08-23 10:36:20

,也就是說先有時鐘上升沿才有q的變化。如果下一個時鐘上升沿沒有到來,那么q的值就保持不變。因此,q的值是在時鐘上升沿之后一點點變化。這就是D觸發器,我們所有的FPGA電路都是基于這個結構來進行

2019-01-17 17:24:19

Jack Kilby)和D(延遲)。典型的觸發器包括零個、一個或兩個輸入信號,以及時鐘信號和輸出信號。一些觸發器還包括一個重置當前輸出的明確輸入信號。第一個電子觸發器是在1919年由

2019-06-20 04:20:50

用高頻時鐘檢測低頻時鐘的上升沿,用兩個D觸發器還是一個D觸發器?一個D觸發器,如下描述[code]always@(posedge clk_quick)beginclk_buf

2014-12-18 15:45:26

電后,與非門的1腳為低電平,故U1A輸出端第3腳為高電平,3腳與與非門的12腳相連,故12腳也為高電平。 2、電路剛上電時,D觸發器的RD引腳通過電容C1,電阻R2上電復位,使D觸發器的輸出Q=D

2023-03-20 15:33:48

使用帶同步清零端的D觸發器(清零高電平有效,在時鐘下降沿執行清零操作)設計下一個下降沿觸發的D觸發器,只能使用行為語。使用設計出的D觸發器輸出一個周期為10個時間單位的時鐘信號。下面是網上的答案

2015-07-30 21:01:49

D觸發器結構的五分頻器邏輯電路

2019-09-11 11:29:19

怎樣去設計一個基于數字電路的D觸發器?如何對基于數字電路的D觸發器進行仿真?

2021-09-16 06:45:31

電平觸發的D觸發器型號有哪些?大部分都是邊沿觸發的,現在要用到電平觸發器,不知道具體型號沒法買到

2019-02-28 14:32:13

無論是用同步RS結構觸發器,還是用主從結構或邊沿觸發結構的觸發器,都可以組成寄存器。一般由D觸發器組成,有公共輸入/輸出使能控制端和時鐘,一般把使能控制端作為寄存器電路的選擇信號,把時鐘控制端作為數據輸入

2011-10-09 16:19:46

的分類 觸發器呢大體可以按這幾個部分分類:1、按晶體管性質分,可以分為BJT集成電路觸發器和MOS型集成電路觸發器。2、按工作方式分,可分為異步工作方式和同步工作方式,異步工作方式也就是不受時鐘控制

2015-04-07 17:47:42

5.1 基本RS觸發器5.2 時鐘控制的觸發器5.3 集成觸發器5.4 觸發器的邏輯符號及時序圖

2010-08-10 11:53:23 0

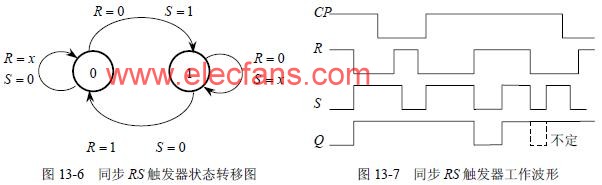

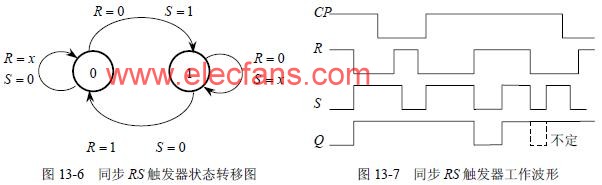

0 教學目標:1、 掌握鐘控同步RS觸發器的電路組成2、 掌握鐘控同步RS觸發器的工作原理及邏輯功能3、 了解觸發器的應用教學重難點:重點:鐘控同步 RS 觸

2010-08-18 14:57:41 16

16 時鐘觸發器的結構形式

2010-08-19 11:04:21 28

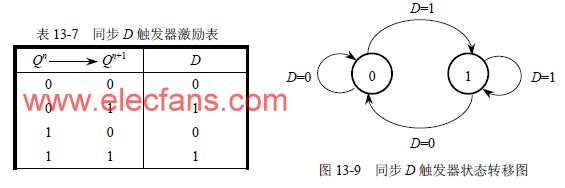

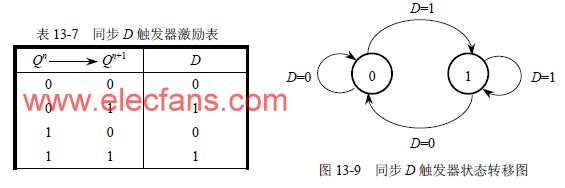

28 D觸發器

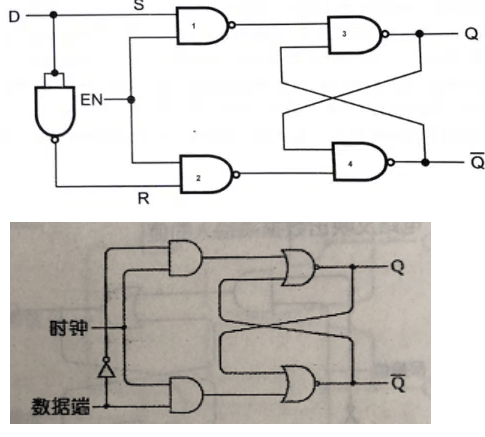

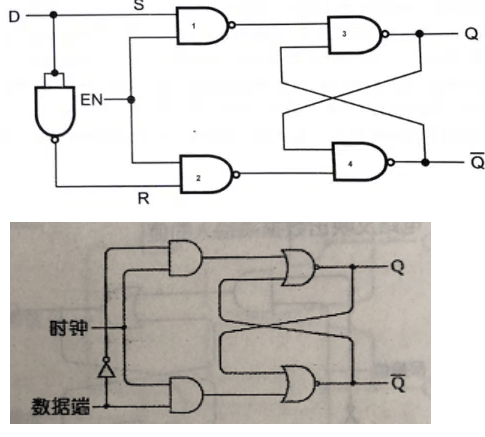

同步式D觸發器邏輯電路圖

D觸發器功能

2008-10-20 09:57:54 2222

2222

同步式D觸發器邏輯電路圖

2008-10-20 09:58:19 8302

8302

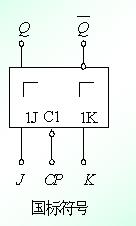

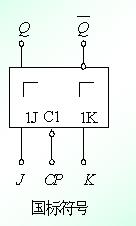

4.2.2 同步觸發器二、同步D觸發器1.電路結構2.邏輯功能3.特性方程4.狀態轉換圖三、同步JK觸發器1.電路結構2.邏輯功能3.特性方程4.狀態轉換

2009-03-30 16:17:07 3895

3895

D觸發器實現二分頻電路(D觸發器構成的2分頻電路)&

2009-06-12 13:58:56 75438

75438

T觸發器,什么是T觸發器

在數字電路中,凡在CP時鐘脈沖控制下,根據輸入信號T取值的不同,具有保持和翻轉功能的電路,即當T=0時

2009-09-30 18:26:07 27581

27581

觸發器的分類, 觸發器的電路

雙穩態器件有兩類:一類是觸發器,一類是鎖存器。鎖存器是觸發器的原始形式。基本

2010-03-09 09:59:59 1554

1554 可以將電平觸發器轉換成更為靈活的邊沿觸發器(采用時間控制方法)。邊沿觸發器只在上升沿或下降沿處對輸入采樣。這種轉換可以這樣來實現:將原來的時鐘信

2010-08-10 11:10:26 5657

5657

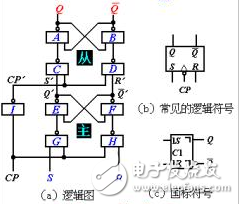

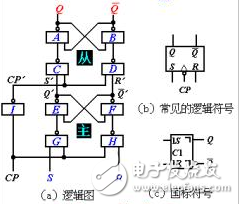

由與非門構成的同步RS觸發器如圖13-5(a)所示,其邏輯符號如圖13-5(b)所示。圖中門A和B構成基本觸發器,門C和E構成觸發引導電路。由圖13-5(a)可見,基本觸發器的輸

2010-08-18 09:00:00 15300

15300

為了避免同步RS觸發器的輸入信號同時為1,可以在S和R之間接一個“非門”,信號只從S端輸入,并將S端改稱為數據輸入端D,如圖15-8所示。這種單輸入的觸發器稱為

2010-08-18 09:06:00 11759

11759

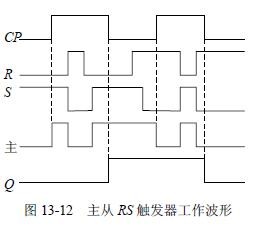

一、空翻問題由于在CP=1期間,同步觸發器的觸發引導門都是開放的,觸發器都可以接收輸入信號而翻轉,所以在CP=1期間,如果輸入信號發生多次變化,觸發器的

2010-08-18 09:08:32 19494

19494

本次重點內容:1、觸發器的概念和分類。2、同步觸發器、主從觸發器、邊沿觸發器的含義。

4.1.1 觸發器概述一、觸發

2010-08-19 08:57:47 19312

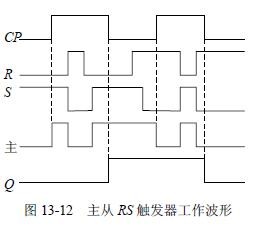

19312 圖13-11(a)所示為主從RS觸發器原理電路。它是由兩個高電平觸發方式的同步RS觸發器構成。其中門E、F、G、H構成主觸發器,時鐘信號為CP,輸出為Q、

2010-08-19 09:09:10 6371

6371

圖中所示是用CMOS電路D觸發器組成T型觸發器和J-K觸發器線路。圖示線路將D觸發器的Q端與D端相連,就可組成T

2010-09-20 03:31:35 17220

17220

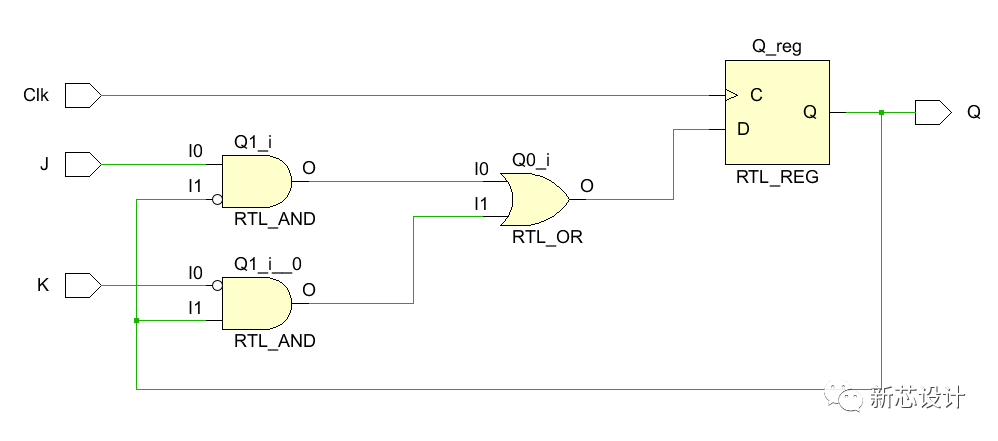

圖中所示是用J-K觸發器組成的D觸發器電路。

從J-K觸發器的邏輯圖已知在D觸發器端增

2010-09-24 00:21:27 6900

6900

數字電路--觸發器雙穩態觸發器

2016-12-20 17:32:40 0

0 實驗內容 將基本RS觸發器,同步RS觸發器,集成J-K觸發器,D觸發器同時集成一個CPLD芯片中模擬其功能,并研究其相互轉換的方法。 實驗的具體實現要連線測試。 原理圖 如圖6-1

2017-12-05 09:33:41 13

13 邊沿觸發器,指的是接收時鐘脈沖CP 的某一約定跳變(正跳變或負跳變)來到時的輸入數據。在CP=l 及CP=0 期間以及CP非約定跳變到來時,觸發器不接收數據的觸發器。具有下列特點的觸發器稱為邊沿觸發方式觸發器,簡稱邊沿觸發器。

2018-01-31 09:02:33 69651

69651

主從RS觸發器由兩個同步RS觸發器組成,它們分別稱為主觸發器和從觸發器。反相器使這兩個觸發器加上互補時鐘脈沖。

2018-02-08 14:23:24 24961

24961

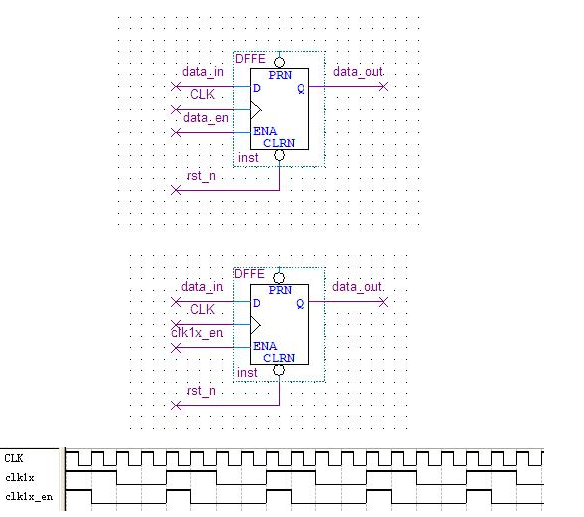

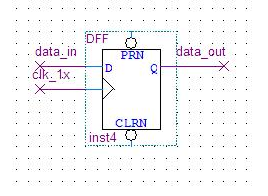

首選我們來聊聊時序邏輯中最基礎的部分D觸發器的同步異步,同步復位即復位信號隨系統時鐘的邊沿觸發起作用,異步復位即復位信號不隨系統時鐘的邊沿觸發起作用,置數同理,rst_n表示低電平復位,我們都知道

2019-07-26 10:17:16 24507

24507

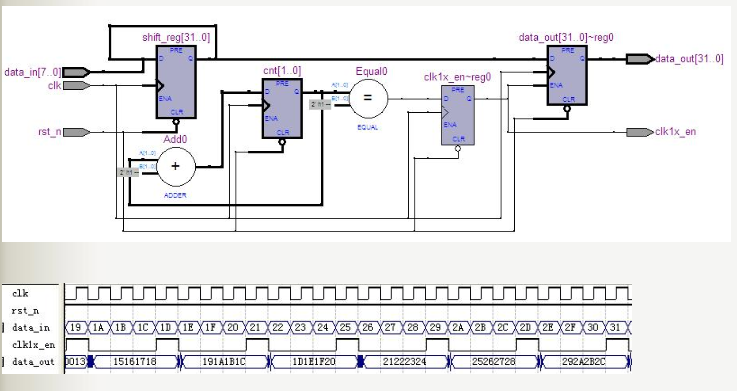

時鐘使能電路是同步設計的基本電路。在很多設計中,雖然內部不同模塊的處理速度不同,但由于這些時鐘是同源的,可以將它們轉化為單一時鐘處理。在ASIC中可以通過STA約束讓分頻始終和源時鐘同相,但FPGA

2021-10-01 10:16:00 6770

6770

上圖是用與非門實現的D觸發器的邏輯結構圖,CP是時鐘信號輸入端,S和R分別是置位和清零信號,低有效; D是信號輸入端,Q信號輸出端;

2022-09-19 15:22:24 4020

4020 什么是RS觸發器 其中R、S分別是英文復位 Reset 和置位 Set 的縮寫,作為最簡單的一種觸發器,是構成各種復雜觸發器的基礎。RS觸發器的邏輯電路圖如下圖所示。 RS觸發器可以用與非門實現或者

2022-10-19 17:49:59 7624

7624

的輸出連接,其狀態由主觸發器的狀態決定,稱為從觸發器。電路結構 主從RS觸發器由兩個同步RS觸發器組成,它們分別稱為主觸發器和從觸發器。反相器使這兩個觸發器加上互補時鐘脈沖。如圖7.4.1所示。 工作原理: 當CP=1時,主觸發器的輸入門G7和G8打開

2022-10-19 19:16:03 22366

22366

在數字電路中,為協調各部分動作一致,常要求某些觸發器于同一時刻工作,所以要引入同步信號。

2022-12-27 09:20:00 28823

28823 D 觸發器或數據觸發器是一種觸發器,它只有一個數據輸入“D”和一個時鐘脈沖輸入, 這種觸發器也稱為延遲觸發器,經常用于許多時序電路,如寄存器、計數器等。下面一起來了解一下D觸發器不同應用下的電路圖。

2023-01-06 14:19:46 4144

4144 鎖存器和觸發器有時組合在一起,因為它們都可以在其輸出上存儲一位(1或0)。與鎖存器相比,觸發器是需要時鐘信號(Clk)的同步電路。D 觸發器僅在時鐘從

2023-06-29 11:50:18 14168

14168

同步電路:存儲電路中所有觸發器的時鐘輸入端都接同一個時鐘脈沖源,因而所有觸發器的狀態的變化都與所加的時鐘脈沖信號同步。

2023-08-09 10:04:19 2249

2249

在傳統的異步 RS 觸發器中,當輸入的 R 和 S 同時為 1 時,會引發互鎖問題,輸出結果是不確定的。為了避免這個問題,常常使用帶有使能控制的同步觸發器,如帶有時鐘信號的 D 觸發器或 JK 觸發器。這些觸發器在時鐘邊沿上才會響應輸入信號,解決了異步 RS 觸發器的互鎖問題。

2023-08-28 15:44:35 2218

2218 的存儲單元,具有時鐘同步的特性。其中,D觸發器是數字電路設計中使用最廣泛的一種觸發器類型之一,因為它具有簡單、穩定和多功能等優點。

2023-08-31 10:50:19 6903

6903

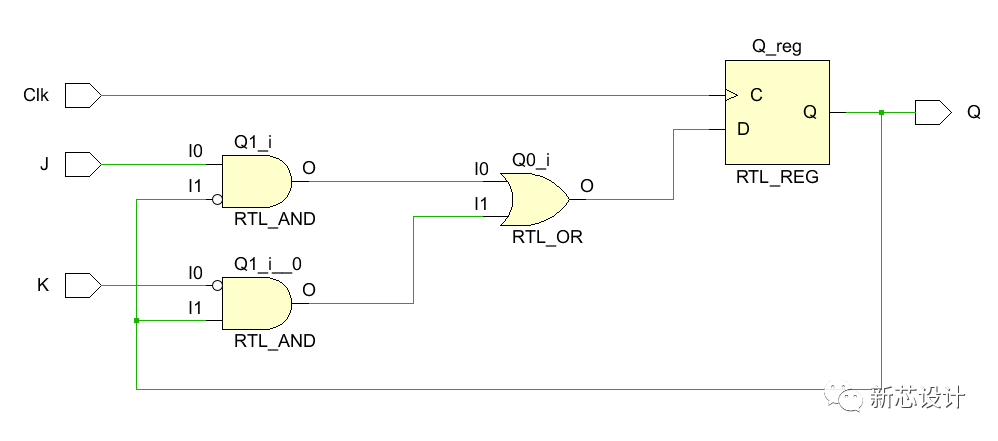

JK 觸發器的 Verilog 代碼實現和 RTL 電路實現

2023-10-09 17:29:34 2003

2003

同步電路:存儲電路中所有觸發器的時鐘輸入端都接同一個時鐘脈沖源,因而所有觸發器的狀態的變化都與所加的時鐘脈沖信號同步。

2023-11-13 12:30:17 459

459 計算機的時鐘節拍、頻率分頻、數據傳輸的幀同步等等。計數器可以通過級聯多個RS觸發器來實現,其中每個觸發器的輸出作為下一個觸發器的輸入。 頻率分頻器 RS觸發器可以用于構建頻率分頻器電路。頻率分頻器可以將一個輸入信號的頻率減小為

2023-11-17 16:03:44 751

751 D觸發器(D flip-flop)可以存儲一位二進制數據的狀態,因此具有記憶功能。D觸發器通常用于數字電路中,用于實現寄存器、計數器等電路,可以通過時鐘信號進行同步操作,使它們可以存儲和操作二進制數據。值得注意的是,D觸發器只能存儲一位二進制數據,如果要存儲更多的數據,則需要使用多位寄存器。

2023-11-29 14:52:03 839

839

和鎖存器的區別和聯系。 首先,我們來了解觸發器的概念。觸發器是一種能夠在時鐘信號的作用下存儲和延遲數據的器件。它們是由通用邏輯門電路實現的,可以看作是鎖存器的一種特殊形式。觸發器通常用于存儲和處理時序信號,由于其能夠

2023-12-25 14:50:46 452

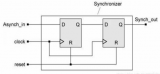

452 的案例和挑戰。 首先,讓我們來了解一級觸發器同步的概念。在計算機科學中,觸發器是一種用于在特定條件下自動執行某個操作的設備或軟件組件。觸發器可以是硬件電路,也可以是軟件程序。同步是指在兩個或多個設備之間實現信息

2024-01-16 16:29:35 127

127 原理 兩級觸發器同步是一種數字電路設計技術,用于確保數據在傳輸過程中的可靠性。它通過兩級觸發器的級聯來實現同步傳輸,可以有效地減少數據傳輸中的噪聲、時鐘抖動等因素對數據的干擾和誤差。 在兩級觸發器同步中,兩個觸發器都由同一

2024-01-16 16:29:38 252

252 。觸發電路通常由一個或多個觸發器、邏輯門和其他輔助元件構成。在數字系統和計算機系統中,觸發電路常用于時序控制、計數器和寄存器等模塊的設計。 同步電壓是指與時鐘信號同步的電壓信號。它的變化與時鐘信號的周期和幅度

2024-01-31 10:57:06 234

234 觸發器是數字電路中常用的組合邏輯電路,在現代電子系統中有著廣泛的應用。其中,最常用的兩種觸發器是T觸發器和JK觸發器。本文將詳細介紹T觸發器和JK觸發器的區別和聯系。 一、T觸發器 T觸發器是一種

2024-02-06 14:04:55 420

420 D觸發器是一種經典的時序邏輯電路,具有廣泛的應用領域。它的功能包括存儲和傳輸數據,以及在時鐘信號的作用下進行狀態轉換。本文將探討D觸發器的功能和狀態方程。 首先,讓我們從D觸發器的基本功能開始討論

2024-02-18 16:28:45 320

320

電子發燒友App

電子發燒友App

評論