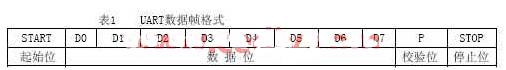

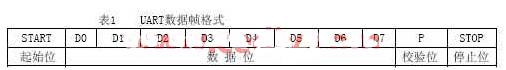

UART(通用異步收發器)是廣泛使用的串行數據傳輸協議。UART允許在串行鏈路上進行全雙工的通信。專用的UART集成電路如8250,8251,NS16450等已經相當復雜,有些含有許多輔助的模塊

2020-08-04 17:25:00 743

743

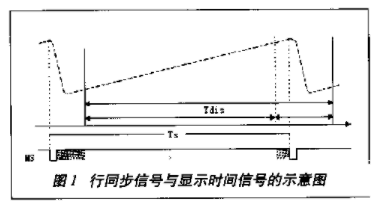

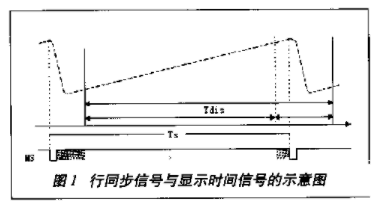

利用可編程器件CPLD/FPGA實現VGA彩色顯示控制器在工業現場中有許多實際應用。以硬件描述語言VHDL對可編程器件進行功能模塊設計、仿真綜合,可實現VGA顯示控制器顯示各種圖形、圖像、文字,并實現了動畫效果。

2020-08-30 12:03:59 882

882

本次的設計為多路UART/SPI通信系統,可以實現一對多的通信。系統可以運行在UART模式,也可以運行在SPI模式。我選擇這一課題的原因主要是目前我所在的實驗室需要寫基于UART的快速通信。這一

2022-10-24 10:55:09 997

997 的面陣CCD驅動時序發生器設計,基于CPLD的面陣CCD驅動時序發生器設計及其硬件實現,基于CPLD的線陣CCD驅動電路的設計,基于CPLD的線陣CCD驅動電路設計與實現,基于CPLD的線陣CCD驅動

2019-06-03 16:45:25

`CPLD/FPGA高級應用開發指南第1章可編程邏輯器件與EDA技術第2章Xilinx CPLD系列產品第3章Xilinx FPGA系列產品第4章Xilinx ISE應用基礎第5章FPGA高級

2013-06-02 10:13:17

它們的基本設計方法是借助于 EDA 設計軟件,用原理圖、狀態機和硬件描述語言等方法,生成相應的目標文件,最后用編程器或下載電纜,由 CPLD/FPGA 目標器件實現。 生產 CPLD/FPGA

2019-03-04 14:10:13

,這些數字器件理論上可以形成一切數字系統,包括單片機甚至CPU,FPGA在抗干擾和速度上有很大優勢。單片機實現原理:單片機——>軟件——>C編程——>順序執行

2012-02-27 13:37:04

:2004年8月 書號:ISBN 7121002124 本書主要介紹了基于CPLD/FPGA芯片和利用VHDL語言實現對常見數字通信單元及系統的建模與設計。 全書針對性和應用性強,可作為通信與信息專業

2012-02-27 11:31:10

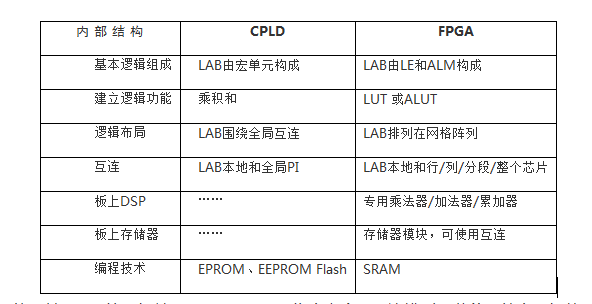

FPGA與CPLD的辨別和分類主要是根據其結構特點和工作原理。通常的分類方法是:將以乘積項結構方式構成邏輯行為的器件稱為CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列

2019-07-01 07:36:55

FPGA與CPLD的區別

盡管很多人聽說過CPLD,但是關于CPLD與FPGA之間的區別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復編程的邏輯器件”,但是在技術上卻有一些差異。簡單

2011-09-27 09:49:48

、路由性能極好,用戶可以改變他們的設計同時保持引腳輸出不變。與FPGA相比,CPLD的I/O更多,尺寸更小。如今,通信系統使用很多標準,必須根據客戶的需要配置設備以支持不同的標準。CPLD可讓設備做出

2012-10-26 08:10:36

和CPLD最大的區別是他們的存儲結構不一樣,這同時也決定了他們的規模不一樣。但是從使用和實現的角度來看,其實他們所使用的語言以及開發流程的各個步驟幾乎是一致的。對于大多數的初學者來說,學FPGA還是

2019-02-21 06:19:27

的缺點.到90年代,CPLD發展更為迅速,不僅具有電擦除特性,而且出現了邊緣掃描及在線可編程等高級特性.較常用的有Xilinx公司的EPLD和Altera公司的CPLD.2.FPGA FPGA通常包含三類

2020-08-28 15:41:47

CPLD是什么?FPGA包含哪幾類可編程資源呢?FPGA可編程器件和CPLD可編程器件有哪些相同點和不同點?

2021-11-10 07:42:51

用“與—或”表達式來描述,所以該“與或陣列”結構能實現大量的組合邏輯功能) 簡單的“與或”陣列:(PAL、GAL、CPLD) 含查找表的邏輯單元:(FPGA) CPLD和FPGA的主要

2020-07-16 10:46:21

和CPLD最大的區別是他們的存儲結構不一樣,這同時也決定了他們的規模不一樣。但是從使用和實現的角度來看,其實他們所使用的語言以及開發流程的各個步驟幾乎是一致的。對于大多數的初學者來說,學FPGA還是

2015-03-12 13:54:42

基于VHDL語言的數字鐘系統設計 基于FPGA的交通燈控制 采用可編程器件(FPGA/CPLD)設計數字鐘 數字鎖相環法位同步信號 基于FPGA的碼速調整電路的建模與設計 誤碼檢測儀

2012-02-10 10:40:31

隨著電子設計自動化(EDA)技術的發展,可編程邏輯器件FPGA/CPLD已經在許多方面得到了廣泛應用,而UART(通用異步收發器) 是在數字通信和控制系統中廣泛使用的串行數據傳輸協議。因此越來越多

2019-09-20 06:24:58

/cpld的設計和優化技巧。在討論fpga/cpld設計指導原則的基礎上,介紹了altera器件的高級應用;引領讀者學習邏輯鎖定設計工具,詳細討論了時序約束與靜態時序分析方法;結合實例討論如何進行設計優化

2020-05-14 14:50:30

Altera FPGA/CPLD設計(高級篇)》

2012-12-06 15:51:36

Altera FPGA_CPLD設計 高級篇

2023-08-05 18:38:20

可編程邏輯器件相關專輯 Altera-FPGA/CPLD設計,從基礎篇到高級篇由淺入深幫助大家學習

2018-10-08 15:43:55

`` 本帖最后由 yuxuandl 于 2013-5-3 22:10 編輯

Altera FPGA CPLD設計_基礎篇&高級篇兩本書,講解比較精細,適合初學和進階人士學習參考。ttach]``

2013-05-03 22:05:30

IIC總線通訊接口器件的CPLD實現摘要:介紹了采用ALTERA公司的可編程器件EPF10K10LC84-3實現IIC總線的通訊接口的基本原理,并給出了部分的VHDL語言描述。該通訊接口與專用的接口芯片相比,具有使用靈活、系統配置方便的特點。 [/hide]

2009-10-30 14:57:35

立題簡介:內容:MCU+CPLD/FPGA實現GPIO擴展與控制;來源:實際得出;作用:MCU+CPLD/FPGA實現GPIO擴展與控制;仿真環境:Quartus II 11.0;日期

2021-11-04 07:42:16

的邊界掃描測試第5章 Xilinx Foundation應用基礎第6章 Foundation高級應用第7章 VHDL語言簡介第8章 CPLD/FPGA在數字系統設計中的應用第9章 CPLD/FPGA在通信

2018-03-29 17:11:59

`CPLD、Spartan可編程器件的基礎知識,VHDL語言基礎,Foundation編輯工具使用,高級應用以及CPLD/FPGA在數字系統設計的應用。`

2021-04-06 11:43:55

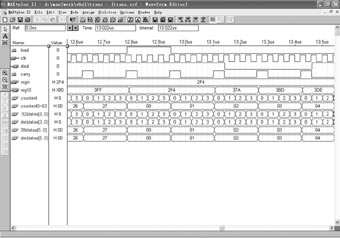

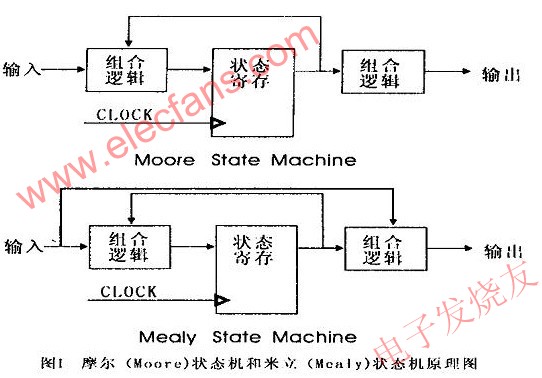

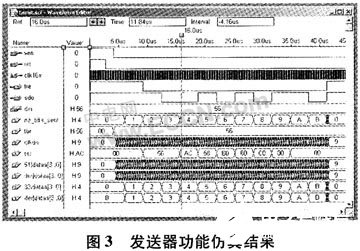

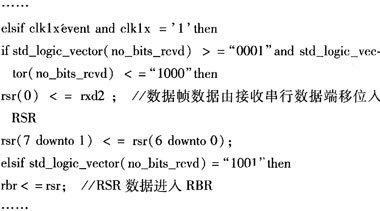

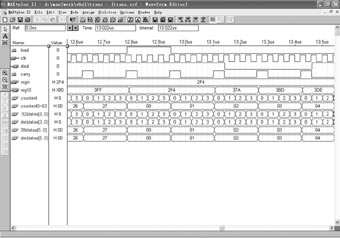

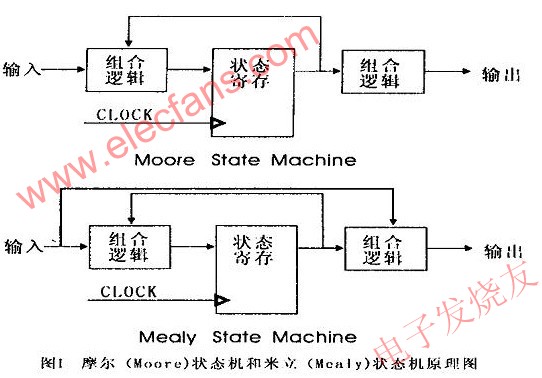

的UART的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA片上UART的設計,給出了仿真結果。關鍵詞:通用異步收發器;串口通信;現場可編程邏輯器件;有限狀態機

2019-06-21 07:17:24

1. FPGA 簡介第1節 什么是 FPGAFPGA 的全稱為 Field-Programmable Gate Array,即現場可編程門陣列。FPGA 是在 PAL、 GAL、 CPLD 等可編程器件

2022-01-25 06:45:52

可編程邏輯器件FPGA/CPLD結構與應用.ppt

2017-01-21 20:34:49

1、在FPGA中實現串口協議的設計在FPGA中實現串口協議,通過Anlogic_FPGA開發板上的“UART2USB”口接收從計算機發來的數據。實驗設計思路UART串口是一種類似于USB、VGA

2022-07-19 11:09:48

語言進行CPLD/FPGA設計開發,Altera和Lattice已經在開發軟件方面提供了基于本公司芯片的強大開發工具。但由于VHDL設計是行為級設計,所帶來的問題是設計者的設計思想與電路結構相脫節,而且

2019-06-18 07:45:03

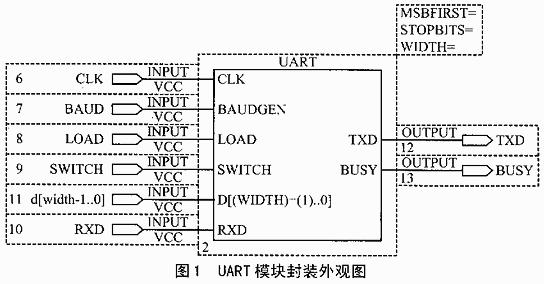

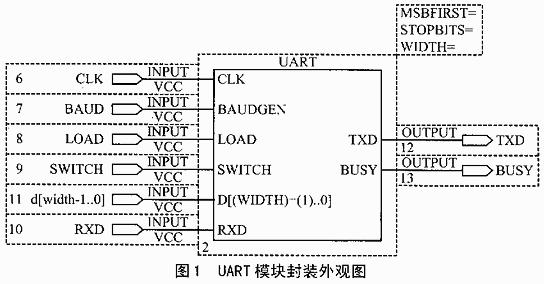

本文應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2021-05-07 06:33:09

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-08-19 06:15:33

串行通信發送器是什么工作原理?怎么用VHDL語言在CPLD上實現串行通信?

2021-04-13 06:26:46

),有時我們不需要使用完整的UART的功能和這些輔助功能。或者設計上用到了FPGA/CPLD器件,那么我們就可以將所需要的UART功能集成到FPGA內部。使用VHDL將UART的核心功能集成,從而使整個設計更加緊湊、穩定且可靠。本文應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2012-05-23 19:37:24

協議;3、 對基于FPGA實現物理層算法有豐富經驗;4、 精通Verilog或者VHDL硬件描述語言,具有扎實的編碼能力;5、 熟悉Xilinx/AlteraFPGA器件特性,熟練掌握synplify

2016-04-20 15:31:59

轉帖:采用高級語言開發FPGA的探索近年來,由于人工智能和金融數據分析等計算密集型領域的日益興起,異構計算越來越受到大家的重視。異構計算是指使用不同類型指令集和體系架構的計算單元組成系統的計算方式

2017-09-25 10:06:29

《Altera FPGA/CPLD設計(高級篇)》結合作者多年工作經驗,深入地討論了Altera FPGA/CPLD的設計、優化技巧。在討論FPGA/CPLD設計指導原則的基礎上,介紹了Altera器件的高級應用;引領讀者

2009-02-12 09:19:12 4799

4799 根據PC 機作為上位機和下位機的CPLD 串行通信的特點,簡介上位機VB 程序的編寫;詳述在EDA 軟件MAXPLUSII 的環境下,利用AHDL 語言,編寫下位機程序。此設計具有波特率高、傳輸準確

2009-04-15 08:40:14 17

17 根據PC 機作為上位機和下位機的CPLD 串行通信的特點,簡介上位機VB 程序的編寫;詳述在EDA 軟件MAXPLUSII 的環境下,利用AHDL 語言,編寫下位機程序。此設計具有波特率高、傳輸準確

2009-05-14 14:15:27 22

22 介紹采用Altera 公司的可編程器件實現串口通信的星型連接,扼要地介紹四路UART 串口通信網絡的星型連接的硬件和軟件的實現。在實現多點串口通信時,星型連接比總線型連接具有

2009-05-15 15:24:57 38

38 CPLD_FPGA高級應用開關指南的主要內容:第1章 可編程邏輯器件與EDA技術第2章 XilinxCPLD系列產品第3章 XilinxFPGA系列產品第4章 XilinxISE應用基礎第5章 FPGA高級設計技巧(一)

2009-07-24 16:00:16 51

51 UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。關鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 基于單片機的CPLD/FPGA被動串行下載配置的實現:介紹采用AT89S2051單片機配合串行E2PROM存儲器,實現CPLD/FPGA器件的被動串行模式的下載配置,闡述了其原理及軟硬件設計。 &nb

2009-10-29 21:57:22 19

19 本文設計了一種基于 FPGA 的UART 核,該核符合串行通信協議,具有模塊化、兼容性和可配置性,適合于SoC 應用。設計中使用Verilog HDL 硬件描述語言在Xilinx ISE 環境下進行設計、仿真,

2009-11-27 15:48:51 17

17 CPLD 器件應用隨著生產工藝的逐步提高以及 CPLD 開發系統的不斷完善,CPLD 器件容量也由幾百門飛速發展到百萬門以上,使得一個復雜數字系統完全可以在一個芯片中實現。HDL

2010-01-27 11:40:02 48

48 利用 FPGA 實現UART 的設計引 言隨著計算機技術的發展和廣泛應用,尤其是在工業控制領域的應用越來越廣泛,計算機通信顯的尤為重要。串行通信雖然使設備之間的連線大為減

2010-03-24 09:23:40 49

49 CPLD FPGA高級應用開發指南

2010-04-15 10:56:51 58

58 基于FPGA/CPLD芯片的數字頻率計設計摘要:詳細論述了利用VHDL硬件描述語言設計,并在EDA(電子設計自動化)工具的幫助下,用大規模可編程邏輯器件(FPGA/CPLD)實現

2010-04-30 14:45:13 132

132 文章介紹了一種在現場可編程門陣列(FPGA)上實現UART 的方法。首先闡述了UART 異步串行通信原理,然后介紹了實現UART異步串行通信的硬件接口電路及各部分硬件模塊,以及用硬件

2010-08-06 16:24:13 55

55 【摘 要】 通過設計實例詳細介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語言開發FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語言相比,使用VHDL語言的優越性。

2009-05-10 19:47:30 1111

1111

摘 要:通過設計實例詳細介紹了用Verilog HDL語言開發FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語言的優越性。

2009-06-20 11:51:28 1857

1857

摘 要: 串行通信是實現遠程測控的重要手段。采用VHDL語言在CPLD上實現了串行通信,完全可以脫離單片機使用。

關鍵詞:

2009-06-20 12:43:50 570

570

摘 要 :UART是廣泛使用的串行數據通訊電路。本設計包含UART發送器、接收器和波特率發生器。設計應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2009-06-20 13:14:52 982

982

基于CPLD/FPGA的多功能分頻器的設計與實現

引言

分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求

2009-11-23 10:39:48 1139

1139

采用CPLD/FPGA的VHDL語言電路優化原理設計

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件(PLD)的發展而發展起

2010-03-19 11:38:02 2318

2318

基于FPGA和CPLD數字邏輯實現ADC技術

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現

2010-05-25 09:39:10 1309

1309

隨著大規模和超大規模FPGA/CPLD器件的誕生和發展,以HDL(硬件描述語言)為工具、FPGA/CPLD器件為載體的EDA技術的應用越來越廣泛.從小型電子系統到大規模SOC(Systemonachip)設計,已經無

2010-09-10 17:30:27 1272

1272

在xo640上實現一個簡單的Uart,能夠解析串口數據,并在寄存器中存儲,用FIFO實現數據的傳遞。那么后期可以通過開發板上的串口經CPLD訪問各種數據。比如PC=CPLD=EEPROM等等,極大方便后期

2011-08-05 16:54:46 1741

1741 UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。

2011-12-17 00:15:00 57

57 altera FPGA/CPLD高級篇(VHDL源代碼)

2012-11-13 14:40:38 134

134 VB語言基礎_ 簡單易懂

2015-12-08 11:26:30 0

0 可編程邏輯器件FPGA/CPLD結構與應用

2016-12-11 23:38:39 0

0 同步異步通信轉換的CPLD_FPGA設計,有需要的下來看看

2016-12-16 22:13:20 8

8 在CPLD中用UART邏輯實現高速異步串行通信

2017-01-24 16:54:24 12

12 基于FPGA/CPLD的UART功能設計

2017-01-23 20:45:37 30

30 利用VB實現WinCC數據高級歸檔的研究和應用

2017-02-07 15:27:34 11

11 CPLD_FPGA的數字通信系統建模與設計

2017-09-04 11:10:01 14

14 CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。那么兩者到底有什么區別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區別。

2017-09-18 16:35:32 5

5 FPGA/CPLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現。 FPGA/CPLD如同一張白紙或是一堆積木,工程師可以通過傳統的原理圖輸入法

2017-10-09 09:52:20 14

14 數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2018-04-26 11:53:00 1121

1121

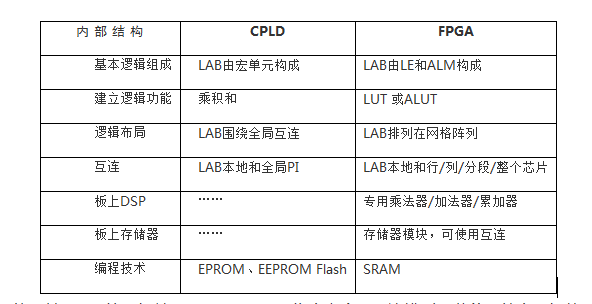

PLD和FPGA都是由邏輯陣列模塊構成的,但是CPLD LAB基于乘積和宏單元,而FPGA LAB使用基于LUT的邏輯單元。CPLD LAB圍繞中心全局互連排列,隨著器件中邏輯數量的增加,呈指數增長。

2018-04-17 17:08:00 2951

2951

以vb程序設計語言為工具,對特定的問題進行分析,并設計出解題的算法,根據得到的算法,用vb語言編寫出源程序的過程就是vb程序設計。

2018-03-12 18:05:57 107697

107697 CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。那么兩者到底有什么區別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區別。

2018-05-24 02:03:00 49472

49472

用CPLD(復雜可編程邏輯器件)設計乃至仿真、驗證、利用ISP(在系統可編程)對硬件調試都非常方便,所以開發周期很短,且I/O口隨意設定,故用CPLD設計專用芯片是大勢所趨。VB是一種面向對象的高級

2018-11-14 10:15:00 3521

3521

實現RS-232電平和TTL/CMOS電平轉換可以用接口芯片來實現,實現數據的串行到并行轉換用的是UART,它們是實現串行通信必不可少的兩個部分。雖然目前大部分處理器芯片中都集成了UART,但是一般

2019-10-18 07:54:00 2317

2317

介紹了采用CPLD和Flash器件對FPGA 實現快速并行配置,并給出了具體的硬件電路設計和關鍵模塊的內部編程思路。

2018-10-24 15:15:49 7

7 本文檔詳細介紹的是FPGA教程之CPLD與FPGA的基礎知識說明主要內容包括了:一、復雜可編程邏輯器件簡介二、CPLD的組成與特點三、FPGA的組成與特點四、CPLD與FPGA的異同五、主要的PLD廠商

2019-02-27 17:09:32 32

32 本文檔的主要內容詳細介紹的是FPGA教程之ALTERA的CPLD與FPGA器件的詳細資料說明主要內容包括了:一、Altera器件一般介紹,二、MAX 7000 系列器件,三、FLEX10K系列器件,四、邊界掃描測試

2019-02-27 17:27:31 15

15 本文檔詳細介紹的是FPGA教程之CPLD和FPGA的配置與下載的詳細資料說明主要內容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下載配置,三、FLEX/ACEX系列FPGA的下載配置,四、ALTERA的編程文件

2019-02-28 09:56:18 17

17 對于CPLD/FPGA初學者而言,如何實現雙向信號往往是個難題。duoduo 當年初接觸CPLD/FPGA的時候也為這個問題頭疼過。讓我們透過下面這個簡單的例子看看CPLD/FPGA設計中如何實現雙向信號。

2019-06-11 16:13:51 15

15 目前,CPLD/FPGA產品被廣泛地應用在航天、通訊、醫療、工控等各個領域。本書從現代電子系統設計的角度出發,基于全球最大的可編程邏輯器件生產廠商XiLinx公司的系列產品,系統全面介紹了CPLD

2019-09-05 08:00:00 22

22 FPGA/CPLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現。

2020-01-20 09:29:00 3264

3264 的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA上的UART的設計,給出仿真結果。

2020-07-07 17:28:03 10

10 的。本設計使用Xilinx的FPGA器件,只將UART的核心功能嵌入到FPGA內部,不但實現了電路的異步通訊的主要功能,而且使電路更加緊湊、穩定、可靠。

2021-04-27 14:07:25 8

8 基于FPGA的UART模塊設計與實現介紹說明。

2021-06-01 09:43:30 19

19 FPGA CPLD中的Verilog設計小技巧(肇慶理士電源技術有限)-FPGA CPLD中的Verilog設計小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 35

35 立題簡介:內容:MCU+CPLD/FPGA實現GPIO擴展與控制;來源:實際得出;作用:MCU+CPLD/FPGA實現GPIO擴展與控制;仿真環境:Quartus II 11.0;日期

2021-10-29 10:21:11 2

2 本次的設計為多路UART/SPI通信系統,可以實現一對多的通信。系統可以運行在UART模式,也可以運行在SPI模式。我選擇這一課題的原因主要是目前我所在的實驗室需要寫基于UART的快速通信。這一

2023-02-20 11:10:31 1160

1160 點擊上方 藍字 關注我們 ? FPGA 高級設計之實現功耗優化 與ASICs(Application Specific Integrated Circuits)比較,相似的邏輯功能,用FPGA來實現

2023-05-19 13:50:02 815

815 可編程邏輯包括 PAL、GAL、PLD 等。通過不斷發展,它已經發展成為現在的CPLD/FPGA。CPLD(復雜可編程邏輯器件)和FPGA(現場可編程門陣列)的功能基本相同,只是實現原理略有不同

2023-07-03 14:33:38 6041

6041

CPLD和FPGA都是由邏輯陣列模塊構成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。CPLD的LAB圍繞中心全局互連排列,隨著器件中邏輯數量的增加,呈指數

2024-01-23 09:17:04 280

280 VB語言和C++語言是兩種不同的編程語言,雖然它們都屬于高級編程語言,但在設計和用途上有很多區別。下面將詳細比較VB語言和C++語言的區別。 設計目標: VB語言(Visual Basic

2024-02-01 10:20:07 382

382

電子發燒友App

電子發燒友App

評論