圖像處理算法在各種場景中都有廣泛應用,借助于FPGA并行計算的優勢可以將算法性能有效提升,但為了提升系統整體性能,僅僅提升某一部分的性能是不夠的,一個好的方法是在FPGA內實現全部視頻輸入輸出接口

2020-11-04 12:07:05 3073

3073 74LS194引腳功能74LS194功能特征74ls194串行數據到并行數據的轉換

2021-03-02 07:00:20

本帖最后由 發燒友LV 于 2014-12-29 20:13 編輯

在FPGA中實現PID算法,面臨著小數的計算,請問大家一般是怎么處理的?

2014-12-03 21:59:29

采集數據中的量化噪聲,在進行數據壓縮前采用濾波的預處理技術。介紹LZW算法和滑動濾波算法的基本理論,詳細闡述用單片FPGA實現兩種算法的方法。最終測試結果表明,該設計方案能夠有效濾除數據中的高頻噪聲

2010-04-24 09:05:21

目標圖片格式。熵編解碼算法有多種,但是各種算法的實現都具有“存在數據依賴”的特點,無法實現大規模的并行改造。這個特點影響了GPU在圖片處理、編解碼算法中性能的發揮。而FPGA基于更小的控制粒度和多核并行

2018-08-01 09:55:53

湊,節約空間。FPGA由于其高度的并行和 靈活的配置特性,以高速、實時、低成本、高靈活性的優點應用于數字信號處理領域。本文敘述了采用FPGA實現光纖微擾動傳感器的數據處理的具體方案,提供 了一種高速實時數據處理

2020-09-04 09:56:23

[attach]***[/attach](給出雙口RAM的結構.介紹雙口RAM的忙邏輯,并主要介紹了在雷達終端的數據處理過程中兩個 CPU通過雙El RAM進行數據的儲存、交換和共享的設計原理和方法。

2012-08-11 16:21:22

的提升。運算速度或者數據路徑寬度都可以進一步提高,另外,時序操作可以在結構上增加一些并行度。這些措施中,每一種都可以提高一定的性能。在利用了目標FPGA器件靈活性的結構中實現算法,會獲得比較大的好處

2021-12-15 06:30:00

各位前輩好,新人自學FPGA,現在碰到一個費解的問題,我例化了一個rom核,輸出是十位的數據,現在需要接入到一個串行輸入的DA模塊上,在網上查到說需要將并行數據轉換為串行數據輸入到DA中,即把十位

2019-03-06 08:55:27

ADC出來到FPGA的并行數據線在PCB布線的時候是繞等長好還是不繞的好?MT-201筆記里的原話是“布設連接到接收器的數字走線時,請勿采用大量“轉接”(tromboning)來使所有走線保持等長。”這個“大量”到底怎么理解?一直沒找到類似的回答,還望指點,多謝!

2023-12-14 07:11:27

各位開發者: 大家好。我現在使用C28345通過XINTF連接FPGA,然后讀取FPGA采集的數據,具體流程是:當FPGA采集了50個數據時,通知DSP開始讀取數據,然后進行數據處理。想問下,這樣

2018-10-19 14:56:22

(n-1)個元素即可,不多說,移位寄存(也可調整元素順序,使得可算法描述里一一對應)~而數據有效位的處理,則需對line buffer輸出延遲(n+1)/2-1拍即可。實現結果對于行寬為3,行數為3

2022-07-15 14:51:07

DM642的學習版中,怎么在進行數據處理的同時進行串口通信?求大神指導啊糾結了好長時間了

2014-02-24 15:42:30

是遍歷性的算法,其運算量大,在實時處理中受到限制。利用2片TI公司的高速DSP芯片TMS320C6201,應用其HPI接口并行實現多種滑窗算法, 滿足了某雷達系統解模糊的實時需要。系統由2片

2019-04-08 09:36:19

FPGA實現的 FFT 處理器的硬件結構。接收單元采用乒乓RAM 結構, 擴大了數據吞吐量。中間數據緩存單元采用雙口RAM , 減少了訪問RAM 的時鐘消耗。計算單元采用基 2 算法, 流水線結構, 可在

2017-11-21 15:55:13

在信號處理中,FFT占有很重要的位置,其運算時間影響整個系統的性能。傳統的實現方法速度很慢,難以滿足信號處理的實時性要求。針對這個問題,本文研究了基于FPGA芯片的FFT算法,把FFT算法對實時性

2010-05-28 13:38:38

HX711如何進行數據處理?

2016-11-21 22:03:43

STM32 USART串口接收數據的具體步驟有哪些?STM32 USART串口是如何進行數據處理的呢?

2021-11-25 08:56:51

湊,節約空間。FPGA由于其高度的并行和 靈活的配置特性,以高速、實時、低成本、高靈活性的優點應用于數字信號處理領域。本文敘述了采用FPGA實現光纖微擾動傳感器的數據處理的具體方案,提供 了一種高速實時數據處理

2020-08-31 18:54:17

`我在一個小練習中需要處理圖像數據,一幀的圖像是并行進來的,如下圖所示:一幀總共有幾千個pixel。假設說我想給每一個pixel乘上一個不同的系數(使用乘法器實現),乘法器是流水線結構。請問有沒有

2017-11-10 14:03:48

我現在可以用labview將單片機采集的數據通過串口visa函數上傳在labview中,然后才可以進行數據處理,也就是發送完數據才可以進行數據處理,怎樣可以在發送數據的同時進行數據處理呢?請各位指教。

2014-09-11 15:05:38

基于FPGA的數據處理和控制

2012-05-08 19:51:37

數據均衡決策的過程。該設計使用了在一個平臺FPGA中實現的一個嵌入式PowerPC。協處理器的意義協處理器是一個處理單元,該處理單元與一個主處理單元一起使用來承擔通常由主處理單元執行的運算。通常,協

2015-02-02 14:18:19

/*名稱:并行數據轉換為串行數據 說明:切換連接到并串轉換芯片74LS165 的撥碼開關,該芯片將并行數據以串行方式發送到 8051 的RXD引腳,移位脈沖由 TXD提供,顯示在 P0 口

2012-03-02 09:38:12

。下面以實例說明RAM操作過程:當第9行數據要送來時,前8行數據已按順序存儲在RAM中。當傳感器送來G[1,9]時,模塊要進行以下工作:(1)把RAM第1列數據讀出;(2)然后把第1列后7行的數據連同G

2019-07-17 04:00:00

``實現本設計信號數據處理和控制所用的硬件結構如附件圖1(所用FPGA為V5-LX50T):數據流:AD6644對30M中頻信號進行采樣,將14位量化信號輸入FPGA。FPGA對采樣信號做DDC處理

2012-05-28 16:32:43

一個串口數據處理的VI程序,(串口通訊的數據可見20131112.dat文件), 實現對數據文件中的讀取、驗證、分析處理、顯示(數據需取絕對值---去除最高位的符號位即可,以十進制數的形式和曲線形式顯示)、存儲等。利用LabVIEW的強大信號分析處理功能,開發一套操作簡便的數據信息分析系統。

2013-11-29 12:01:13

DSP和A/D芯片間增加FPGA。FPGA是整個系統的時序控制中心和數據交換橋梁,而且能夠實現對底層的信號快速預處理,在很多信號系統中,底層的信號預處理算法要處理的數據量大;對處理速度要求高,但算法

2019-07-05 06:41:27

特點,采用數據流控制的方法實現了信息的并行處理,可以更加有效的實現多通道振動信號采集;同時為了提高數據的可靠性采用時間標定的方法進行數據的存儲和校驗。本文第一節介紹了該系統的整體設計方案,第二節

2019-07-01 06:11:15

需要實現兩塊FPGA之間的8位并行數據傳輸,用什么握手協議比較好呢?想請問一下各位的建議。這兩塊FPGA使用的時鐘是36M的,同一個晶振產生。除了8位數據線外,兩塊FPGA之間還有10根可供使用的線。

2015-01-26 14:20:10

在數字系統的設計中,FPGA+ARM 的系統架構得到了越來越廣泛的應用,FPGA 主要實現高速數據的處理;ARM 主要實現系統的流程控制.人機交互.外部通信以及FPGA 控制等功能.I2C.SPI

2019-09-17 06:21:10

FPGA選用的是XC3S1600E,使用XCF08PFSG48C進行配置,選用并行數據傳輸時,XCF08PFSG48C的片選信號CE一直處于低電平,不跳高,但其他都正常,是怎么回事?

2013-09-04 13:33:49

DSP技術廣泛應用于各個領域,但傳統的數字信號處理器由于以順序方式工作使得數據處理速度較低,且在功能重構及應用目標的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實現數字信號處理系統,具有很強的實時性和靈活性,因此利用FPGA實現數字信號處理成為數字信號處理領域的一種新的趨勢。

2019-10-17 08:12:27

單片機主要作用是控制外圍的器件,并實現一定的通信和數據處理。雖然單片機不擅長實現算法和進行復雜的運算,但在某些特定場合,不可避免地要用到數學運算。比如:在單片機進行數據采集時,會遇到數據的...

2022-01-07 06:48:00

DSP是注重數據處理。算法很重要。FPGA主要是做邏輯電路.現在很多框架都是基于DSP和FPGA的組合平臺,DSP作算法,FPGA作邏輯時序!FPGA一樣可以做DSP(DSP就是數字信號處理英文縮寫

2021-07-28 09:16:02

DSP芯片組成并行處理系統。另外,為充分發揮 DSP芯片在復雜算法處理上的優勢及FPGA在大數據量的底層算法上的優勢,設計了一種基于FPGA控制的多DSP并行處理系統。1 系統設計基于FPGA控制的多

2019-05-21 05:00:19

` 本帖最后由 ninghechuan 于 2017-8-30 08:20 編輯

我們為了實現動態圖像的濾波算法,用串口發送圖像數據到FPGA開發板,經FPGA進行圖像處理算法后,動態顯示到

2017-08-28 11:34:10

轉帖摘要: 針對嵌入式軟件無法滿足數字圖像實時處理速度問題,提出用硬件加速器的思想,通過FPGA實現Sobel邊緣檢測算法。通過乒乓操作、并行處理數據和流水線設計,大大提高算法的處理速度。采用模塊

2017-11-29 08:57:04

傳統數字濾波器硬件的實現主要采用專用集成電路(ASIC)和數字信號處理器(DSP)來實現。FPGA內部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結構,這種結構特別適用于并行處理結構,相對于傳統方法來說,其并行度和擴展性都很好,它逐漸成為構造可編程高性能算法結構的新選擇。

2019-10-22 07:14:04

FFT(快速傅里葉變換)在無線通信、語音識別、圖像處理和頻譜分析等領域有著廣泛應用。在FFT運算中,核心操作是蝶形運算,而蝶形運算的主要操作是向量旋轉,實現向量旋轉可用復數乘法運算來實現,但復數乘

2011-07-11 21:32:29

了設計的一大挑戰。FPGA可通過在單個FPGA中實現多個視頻處理器來提供強大的處理能力。那么現在的挑戰就變成了要使數據盡快且高效地從FPGA進出。DDR3存儲器系統在大多數情況下可以為這些基于FPGA的系統

2019-05-27 05:00:02

跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還是在校的學生,跨時鐘域處理也是面試中經常常被問到的一個問題。在本篇文章中,主要

2021-07-29 06:19:11

,延時節拍由方框中的數字表示。各級轉接器和延時單元起到對序列進行碼位抽取并將數據拉齊的作用。每級延時在FPGA內部用FIFO實現,不需要對序列進行尋址即可實現延時功能。數據串行輸入,經過3級流水處理后

2019-06-17 09:01:35

放大調整后,確保了通信系統信號輸出的幅度可基本維持在恒定的狀態。文中將AGC算法應用于音頻信號處理中,可實現FPGA,并可有效降低音頻信號輸出時的干擾,保證信號的穩定。2、 基于AGC算法的音頻信號處理

2020-10-21 16:42:15

嗨,我是Xilinx FPGA的新手并對其進行編程。我正在嘗試使用Spartan 3E設備XCS500E獲取32行并行數字數據。當數據存在時,我有一個可用的閃光線。有人可以給我一些指導來開始這個項目

2019-01-23 08:55:18

本文提出了一個基于FPGA 的信息處理的實例:一個簡單的人工神經網絡應用Verilog 語言描述,該數據流采用模塊化的程序設計,并考慮了模塊間數據傳輸信號同 步的問題,有效地解決了人工神經網絡并行數據處理的問題。

2021-05-06 07:22:07

請教一個問題:假設FPGA在一個同步信號(假設10kHz)的控制下,對一個高速ADC采樣,在同步信號的高電平采樣,同時開始數據處理,但是數據處理需要2個同步信號周期才能處理完數據。有沒有辦法保證數據

2018-08-16 11:50:48

數據庫優化法海量數據都被存儲在數據庫中,如何從數據庫中提取有用信息就需要用到數據庫優化法,常見的數據庫優化方法有數據分區、索引、緩存機制、分批處理、優化查詢語句、使用采樣數據進行數據挖掘等。7. 倒排索引

2018-03-23 14:23:22

用FPGA實現優化的指紋識別預處理算法在選取較優化的指紋識別預處理算法的基礎上,根據算法的結構選取具有并行處理、低功耗、速度快等特點的FPGA作為實現算法的基本器件。由于用FPGA實現復雜算法較傳統

2009-09-19 09:38:11

,就需要至少 7 比特的并行數據。而如果一個家電產品中同時有多個七段顯示器以及各種按鍵等,則并行數據量就更大了。而單片機輸入輸出端口總是有限的,為了能夠完成家用電器的更多的控制功能,用來驅動這些并行數據

2011-03-03 14:56:50

觸摸屏數據處理算法研究及實現

2012-08-15 16:32:39

ADC出來到FPGA的并行數據線在PCB布線的時候是繞等長好還是不繞的好?MT-201筆記里的原話是“布設連接到接收器的數字走線時,請勿采用大量“轉接”(tromboning)來使所有走線保持等長。”這個“大量”到底怎么理解?一直沒找到類似的回答,還望指點,多謝!

2018-08-22 08:18:15

執行的處理方式,使得其在高速大規模的數據處理方面有著無可替代的優勢,隨著FPGA工藝和設計水平的不斷提高,其在數字系統中扮演的角色也從邏輯膠合者提升到處理器的核心。FPGA在工業控制中的應用早在十年前

2022-01-20 09:34:26

單片機主要作用是控制外圍的器件,并實現一定的通信和數據處理。但在某些特定場合,不可避免地要用到數學運算,盡管單片機并不擅長實現算法和進行復雜的運算。下面主要是介紹如何用單片機實現數字濾波。在單片機

2022-01-18 07:00:34

針對硬件實現的h.264視頻編碼算法改進針對硬件實現的視頻編碼算法改進上海交通大學圖像通信與信息處理研究所 周怡吳昊方向忠摘要’ 從硬件實現的角度分析了算法# 重點研究了占用最多運算時間的預測部分

2008-06-25 11:35:14

高速專用GFP處理器的FPGA實現采用 實現了非標準用戶數據接入 網絡時,進行數據 封裝和解封裝的處理器電路在處理器電路中引入了緩沖區管理器,使得電路能夠有效處理突發到達 瞬時速率較高的客戶數據

2012-08-11 11:51:11

本文介紹了分布式測井數據自動處理系統的研究與實現;詳細介紹了測井曲線自動處理系統的模塊與組成;論述了分布式并行數據處理,人機交互,神經網絡算法實現等問題,給出

2009-06-15 10:34:23 8

8 隨著硬件發展趨于極限,建立并行數據庫管理系統已成為提高數據庫性能的必然選擇。本文在介紹了并行數據庫系統相關的概念之后, 討論了并行數據庫的物理組織結構,并介紹了一

2009-06-22 09:18:55 15

15 針對順序的模糊關聯規則算法在處理海量飛行數據時,由于算法可擴展性低、響應時間過長而帶來數據處理的不便,本文采用模糊關聯并行挖掘算法,先使用并行的模糊c-2均值算法

2009-12-30 12:51:20 12

12 觸摸屏數據處理算法

2010-02-11 10:35:41 55

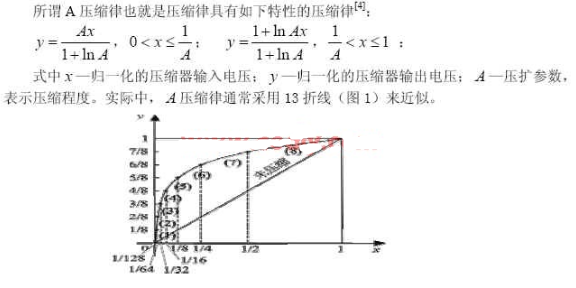

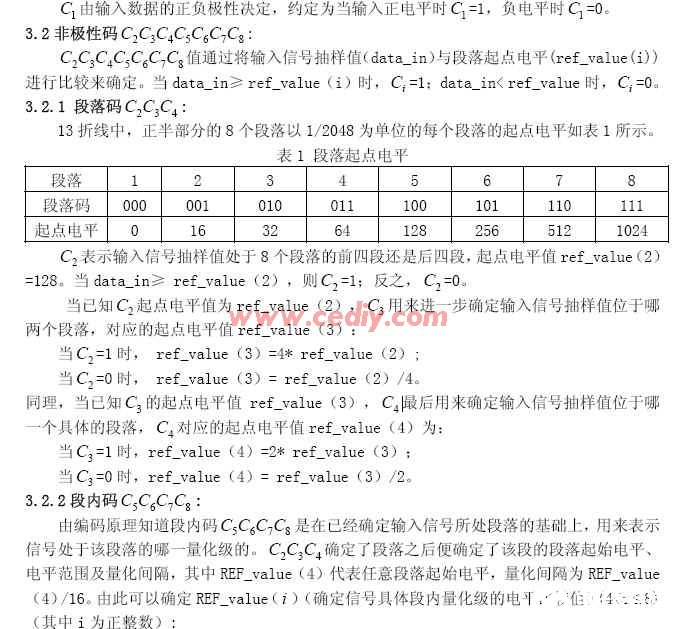

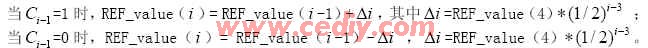

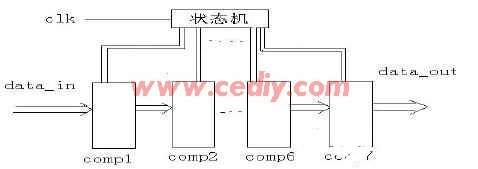

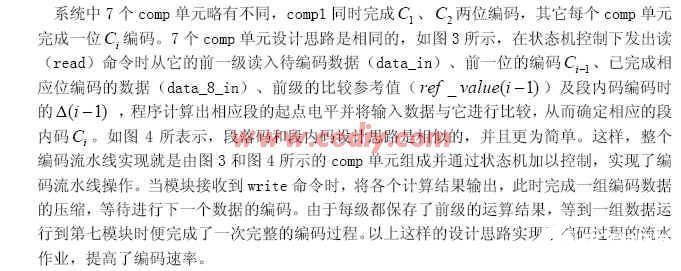

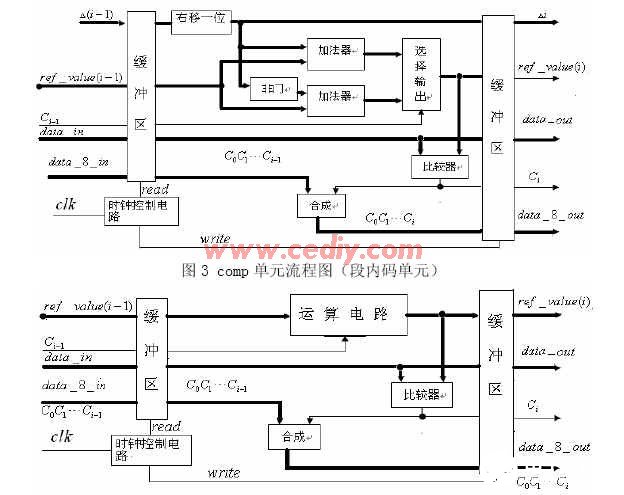

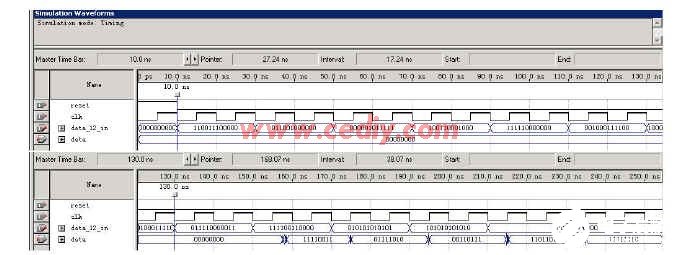

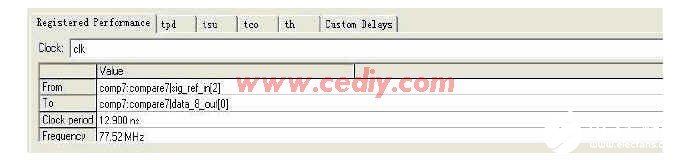

55 本文針對A律13折線法的算法特點,提出一種并行數據處理算法,實現了編碼的流水線操作。運用VHDL語言將其在FPGA中實現,借助quartus II6.0平臺進行驗證,并對驗證結果進行分析,評估了系統

2010-07-28 17:32:50 21

21 本文介紹的基于PCI總線的FPGA計算平臺的系統實現:通過在PC機上插入擴展PCI卡,對算法進行針對并行運算的設計,提升普通PC機對大計算量數字信號的處理速度。本設計采用5片FPGA芯片及

2011-08-21 18:05:31 1970

1970

測量精度和可靠性是儀器的重要指標,引入數據處理算法后,使許多原來靠硬件電路難以實現的信號處理問題得以解決,從而克服和彌補了包括傳感器在內的各個測量環節中硬件本身的

2011-12-01 16:06:44 93

93 。。。。。。串行數據轉換為并行數據。。。。。。。

2015-11-10 10:01:10 9

9 。。。。。。并行數據轉換為串行數據。。。。。。。

2015-11-10 10:00:07 0

0 基于FPGA的嵌入式多核處理器及SUSAN算法并行化

2016-08-30 18:11:47 24

24 實時圖像增強算法改進及FPGA實現,下來看看

2016-09-17 07:28:24 14

14 基于FPGA的自準直系統數據處理技術_王曄

2017-03-19 11:41:23 0

0 串行編碼原理得到8 位并行數據的CRC 校驗矩陣,之后對矩陣進行迭代簡化,得到32 位并行數據的參數矩陣,此參數矩陣作為該CRC 算法的核心實現了對數據進行預處理。最后對該算法進行了硬件實現,仿真及綜合結果表明,該算法可在單周期內完成對128 位并行數據的CRC 編碼和解碼校驗,

2017-10-30 16:39:25 3

3 提出了一種基于最優搜索的稀疏傅里葉變換(SFT)的并行實現設計。首先將輸入信號分為并行N組,分別進行快速傅里葉變換(FFT),實現信號頻率分量的取模處理,然后通過排序搜索獲得。經驗證,相較于FFTW

2017-11-15 13:25:50 2718

2718

針對CMOS圖像傳感器輸出的LVDS串行數據在傳輸過程中因數據無法對齊引起誤碼率升高,圖像分辨率降低問題,提出一種基于現場可編程門陣列FPGA的CMOS相機實時數據處理研究方案。采用VHDL硬件語言,對數據處理進行模塊化設計,確保高速數據的正確采樣,減少誤碼產生。

2017-11-15 16:19:01 3208

3208

為了滿足超高性能數據處理以及低功耗、簡單可編程性的應用,設計了一款基于TI TMS320C6678芯片和Xilinx公司XC5VSX95T芯片的4DSP+FPGA架構的數據處理板,同時設計了高帶寬

2017-11-16 12:21:44 5772

5772

隨著圖像數據的大量增加,傳統單處理器或多處理器結構的計算設備已無法滿足實時性數據處理要求。異構并行計算技術因其高效的計算效率和并行的實時性數據處理能力,正得到廣泛關注和應用。利用GPU在圖形圖像處理

2017-11-21 16:57:15 4

4 排名,BFS算法是Graph500的核心程序,是典型的數據密集型應用。從l-D數據劃分、優化的混合算法設計和遠程通信方式設計三個方面開展研究,在課題組設計的大數據處理并行結構原型系統上設計實現了多節點的并行BFS算法,在頂點、邊的數據規模下取

2017-11-23 11:26:56 0

0 為了解決kmeans算法在Hadoop平臺下處理海量高維數據時聚類效果差,以及已有的改進算法不利于并行化等問題,提出了一種基于Hash改進的并行化方案。將海量高維的數據映射到一個壓縮的標識空間,進而

2017-11-24 14:24:32 2

2 從而實現數據分塊;其次,利用.NET環境下的Parallel類對分塊數據進行并行暈渲處理,得到各個分塊數據的暈渲結果;最后,對各個分塊數據的暈渲圖像進行拼接,從而得到完整的地貌暈渲圖像。實驗結果表明:并行化改進算法的計算效率明

2017-11-30 10:30:22 0

0 隨著互聯網的飛速發展,需要處理的數據量不斷增加,在互聯網數據挖掘領域中傳統的單機文本聚類算法無法滿足海量數據處理的要求,針對在單機情況下,傳統LDA算法無法分析處理大規模語料集的問題,提出

2017-12-05 13:51:04 0

0 對于超字級并行(SLP)算法不能有效地處理大型程序中并行代碼率較小,且可向量化的代碼中可能存在對向量化不利的代碼的問題,提出了一種新型的SLP改進算法NSLPO。首先,將程序中不能向量化的非同構語句

2017-12-06 15:17:47 0

0 本文研究了基于Spark的并行數據挖掘,并將其應用到了流程對象數據分析中。文章通過對串行的流程 對象數據挖掘算法流的研究,提出了一種基于Spark并行計算框架的并行化算法流解決方案,并通過編 程實現、并行效率測試、算法調優,最終得出一個并行效果良好的并行數據挖掘方案。該并行方案明顯 提高了計算效率。

2017-12-30 17:31:04 0

0 由于FPGA的高速和并行處理特性,使其廣泛應用在高速信息處理系統中.以X射線能譜的前端數據處理為對象,提出了基于FPGA實現對高速數據的采集與處理的方法.同時討論了電子測量系統中的補償措施.

2018-09-21 15:50:58 13

13 本文利用FPGA并行結構、運算速度快的特點實現了材料缺陷的實時檢測。搭建了以FPGA為核心的缺陷數據處理系統的硬件電路;重點針對聚合物薄膜材料缺陷信號的數據特征,設計了基于FPGA的缺陷圖像預處理

2021-01-25 16:04:00 7

7 采用FPGA實現了非標準用戶數據接入sDH網絡時,進行數據GFP封裝和解封裝的處理器電路。在處理器電路中引入了緩沖區管理器,使得電路能夠有效處理突發到達、瞬時速率較高的客戶數據;采用了并行cRc算法

2021-01-27 16:38:03 7

7 采用FPGA實現了非標準用戶數據接入sDH網絡時,進行數據GFP封裝和解封裝的處理器電路。在處理器電路中引入了緩沖區管理器,使得電路能夠有效處理突發到達、瞬時速率較高的客戶數據;采用了并行cRc算法

2021-01-28 17:22:52 7

7 在選取較優化的指紋識別預處理算法的基礎上,根據算法的結構選取具有并行處理、低功耗、速度快等特點的FPGA作為實現算法的基本器件。由于用FPGA實現復雜算法較傳統器件從思考角度和實現方向上都有很大區別,所以本次設計從新的方向來完成傳統的指紋處理的設計。實際結果表明FPGA基本達到了設計的最初要求。

2021-02-03 15:53:00 11

11 出了四核心嵌入式并行處理器FPEP的結構設計并建立了FPGA驗證平臺.為了對多核處理器平臺性能進行評測,提出了基于OpenMP的3種可行的圖像處理領域的經典算法SUSAN算法的并行化方法:直接并行

2021-02-03 16:26:00 8

8 在數據通信中, 提高數據在通信中的可靠性,以及快速的數據處理能力一直是人們所追求的,循環冗余校驗CRC就是一種廣泛采用的差錯控制方法,也是一種最常用的信道編碼方法。在介紹CRC碼原理之后,以經典

2021-03-10 15:50:00 14

14 系統性能的關鍵之一。無損壓縮算法中,LZMA算法具有較高的壓縮率,但串行版本的LZMA算法壓縮速率很慢。采用多核架枃的處理器對無損壓縮算法進行并行化,是提升壓縮速率的一個研究方向。設計并實現了面向申威26010異構眾核處理器并行化LZM

2021-04-12 11:11:48 28

28 FPGA以擅長高速并行數據處理而聞名,從有線/無線通信到圖像處理中各種DSP算法,再到現今火爆的AI應用,都離不開卷積、濾波、變換等基本的數學運算。

2022-10-31 14:48:15 2413

2413 各種不同的計算和處理任務,例如數字信號處理(DSP)、圖像處理、機器學習、通信協議處理等。FPGA的特點使得它非常適合實現需要高度并行計算和低延遲的算法。

2023-08-16 14:31:23 1604

1604

單片機開發中,傳感器的數據處理算法

2023-10-17 17:35:32 366

366

電子發燒友App

電子發燒友App

評論