1、 前言

近年來,隨著嵌入式核心芯片的飛速發展,改變了傳統嵌入式系統的設計方法,嵌入式系統逐漸由板級向芯片級過渡,即片上系統——SOC。片上系統是追求產品系統最大包容的集成器件,是當前嵌入式應用領域的技術熱點。SOC的出現使集成電路發展成為集成系統,整個電子整機的功能可以集成到一塊芯片中,降低了設計成本,縮短了開發周期。因此,本文設計了一個基于FPGA的嵌入式系統,既能滿足嵌入式系統教學實驗的需要,同時也可作為嵌入式產品開發平臺。

2、 系統硬件設計

本系統要實現的功能包括:可以運行嵌入式操作系統;支持NIOS II開發;支持USB通訊;支持RS-232串口通訊;支持以太網通訊;支持JTAG接口在線調試與下載。

2.1 系統硬件框圖

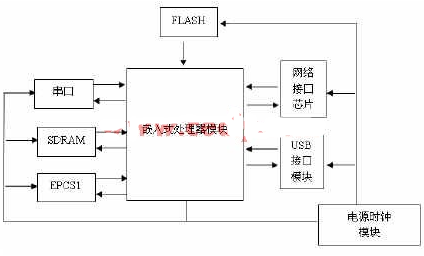

針對所需的功能,設計出系統的相應硬件平臺,硬件平臺主要是由嵌入式處理器模塊、存儲器模塊、包括以太網接口、USB接口和電源等外部接口電路模塊組成。系統硬件結構框圖如圖1 所示。

圖1 系統硬件結構圖

2.2 嵌入式處理器模塊

嵌入式處理器是整個系統的控制管理中心,主要功能是實現整個系統的控制和任務調試管理。在本系統中嵌入式處理器采用ALTERA公司的Cyclone系列的EP1C12Q240C8芯片,其采用QFP封裝,擁有12060個邏輯單元(LE)、52個M4K 存儲塊、全部RAM位數為239616、兩個鎖相環,以及249個可用的I/O腳, 其配置存儲器采用EPCS1,編譯后系統速度可以達到100MHz,支持ALTERA 公司的SOPC內核NIOS II系統的開發,NIOS II開發環境編譯后的可執行文件可以通過JTAG接口下載到開發板上的FLASH中去,可以支持一些嵌入式操作系統,比如MicroC/OS操作系統和?Clinux操作系統。

2.3存儲器模塊

2.3.1 專用串行配置器件EPCS1接口電路

EPCS系列器件是Altera公司提供的一種基于FLASH存儲器的專用串行配置器件,其具有串行接口,接口只需要四個引腳,能夠存儲Stratix II 系列、Cyclone系列的FPGA的配置信息,并在系統上電或者需要重新配置FPGA時,向FPGA發送配置信息。本系統用的串行配置器件EPCS1大小為1M字節,反復擦寫次數可多達十萬,可以輕松實現掉電保護

2.3.2 Flash存儲器接口電路

Flash存儲器具有低功耗、大容量、擦寫速度快、可整片或分扇區在系統編程(燒寫)、擦除等特點,因而在各種嵌入式系統中得到了廣泛的應用。

系統中用了一片AMD29LV320D FLASH存儲器,其單片存儲容量為32M位(4M字節),工作電壓為2.7V~3.6V,16位數據寬度。AMD29LV320D僅需3V電壓即可完成在系統的編程與擦除操作,通過對其內部的命令寄存器寫入標準的命令序列,可對Flash進行編程(燒寫)、整片擦除、按扇區擦除以及其他操作。

Flash存儲器在系統中通常用于存放程序代碼,系統上電或復位后從此獲取指令并開始執行,由于,在進行系統整體設計時,可以通過使用Quartus II對引腳進行配置,所以對于AMD29LV320D FLASH的三個功能引腳nCE、nOE、nWE,可以各接一個EP1C12Q240C8的通用I/O腳即可。

2.3.3 SDRAM存儲器接口電路

與Flash存儲器相比較,SDRAM不具有掉電保持數據的特性,但其存取速度大大高于Flash存儲器,且具有讀/寫的屬性,因此,SDRAM在系統中主要用作程序的運行空間、數據及堆棧區。當系統啟動時,CPU首先從復位地址0x0處讀取啟動代碼,在完成系統的初始化后,程序代碼調入SDRAM中運行,以提高系統的運行速度。同時,系統及用戶堆棧、運行數據也都放在SDRAM中。

系統中用了一片HY57V641620 SDRAM存儲器,其存儲容量為4組x16位(8M字節),工作電壓為3. 3V,常見封裝為54腳TSOP,兼容LVTTL接口,支持自動刷新(Auto-Refresh)和自刷新(Self-Refresh), 16位數據寬度。可滿足運行MicroC/OS操作系統、或者?Clinux操作系統及各種相對較復雜的算法的運行要求。

要在系統中使用SDRAM,要求微處理器具有刷新控制邏輯,或在系統中另外加入刷新控制邏輯電路。通過Altera公司提供的NIOS II開發工具可以將SDRAM控制器添加到NIOS CPU中,然后下載到EP1C12Q240C8中運行,因此可以方便地使用EP1C12Q240C8的通用I/O口與SDRAM相連接,同樣在進行系統整體設計時通過Quartus II定義引腳。

2.4 外部接口模塊

2.4.1以太網接口設計

系統采用realteck公司推出多年RTL8019AS網絡芯片。RTL8019AS芯片是一款應用廣泛的10M網絡芯片,支持以太網II 和IEEE802.3 10Base5,10Base2,10BaseT、支持可編程輸出的4-診斷 LED。利用RTL8019AS可以在NIOS II系統中方便的建立起完整的網絡服務器,可以通過網絡從FPGA芯片構成的軟嵌入式系統中收發數據。

RTL8019AS與EP1C12Q240C8通過外部總線進行連接。主要是把RTL8019AS的數據總線(SDO~SD15)、地址總線(SAO~SA5,SA8)、讀使能(IORB)、寫使能(IOWB)、中斷輸出信號(INTO)和中斷輸入信號(RSTDRV)與EP1C12Q240C8的通用I/O腳連接即可。

2.4.2 USB接口設計

系統采用Cypress公司的SL811HS芯片作為USB接口芯片,它是一種USB主機控制器,它能與全速或低速USB外圍設備通信。SL811HS能與各種微處理器、微控制器、FPGA以及DSP,ISA等各種總線進行接口,適用于各種要求配置USB主機或設備的嵌入式系統。

在USB接口電路設計中,SL811HS的8位數據線直接和FPGA芯片的8位數據線相連。其中需要注意的是,SL811HS的AO引腳和低8位地址線的最低位AO相連,即與鎖存器的地址輸出端的最低位相連。

2.4.3 串行接口設計

RS232是應用最為廣泛的UART接口,可以方便的實現與計算機的數據通訊;同時在調試基于FPGA的嵌入式操作系統時候,可以作為輔助調試接口,結果輸出到主機的超級終端上面。因為FPGA的通用I/O引腳可以在后期通過Quartus II軟件定義,所以只需選取EP1C12Q240C8的任意四個引腳與電平轉換器MAX3232C相連,通過MAX3232C 接RS232標準串行接口(DB9),可與PC機進行串行通信。

2.4.4 電源接口設計

系統需要使用1.5V、3.3V和5V三種直流電源,其中,EP1C12Q240C8內核使用1.5V電源,EP1C12Q240C8的I/O口、MAX3232C、LCD接口等器件使用3.3V電源,RTL8019AS使用5V電源。為簡化系統電源電路的設計,要求整個系統的輸入電壓為高質量的5V直流電壓電源,本系統采用電壓轉換芯片B1117來得到1.5V和3.3V的電壓。

2.4.5 系統時鐘電路設計

系統時鐘模塊為試驗系統提供時鐘信號,使其工作在指定的頻率下,是系統不可缺少的部分。本系統的時鐘信號由50MHz的有源晶振產生,為了使系統有穩定的時鐘輸入,要對晶振的輸入電壓通過簡單的LC濾波電路做濾波處理,使其電壓更加穩定,盡可能減小干擾。

2.4.6 復位電路設計

在系統中,復位電路主要完成系統的上電復位和系統在運行時用戶的按鍵復位功能。本系統根據實際需要,通過Quartus II軟件對復位信號進行延時設計,然后在外部再加以需要簡單的電路來實現。

2.4.7 JTAG接口設計

JTAG(Joint Test Action Group)是一種國際標準測試協議,主要用于芯片內部測試及對系統進行仿真、調試 。JTAG技術是一種嵌入式調試技術,它在芯片內部封裝了專門的測試電路,可以通過專用的JTAG測試軟件對芯片內部節點進行測試。EP1C12Q240C8有四個專用引腳TMS、TDI、TCK、TDO與Altera公司的專用下載電纜——Byte Blaster II通過一個十針的插座相連,用于下載以及在線調試。

3、 系統軟件設計

本系統主要的開發調試工具有SOPC Builder、Quartus II和 NIOS II IDE。SOPC Builder是一個自動化的系統開發工具,它能夠極大地簡化高性能SOPC的設計工作;Quartus II是Altera公司推出的CPLD/FPGA開發工具,Quartus II提供了完全集成且與電路結構無關的開發包環境,具有數字邏輯設計的全部特性,主要用于system-on-a-programmable-chip (SOPC)的設計環境;NIOS II IDE是NIOS II系列嵌入式處理器的基本軟件開發工具。所有軟件開發任務都可以NIOS II IDE下完成,包括編輯、編譯和調試程序。

3.1.系統軟件配置

采用NIOS處理器開發設計與采用傳統的處理器開發設計不同,開發者必須先配置處理器結構、設置接口等內容。也就是說,開發者必須根據實際需求構建一個處理器,而傳統的處理器具有固定接口、片內RAM和外部設備。系統設計所需的具體軟件配置如下:

(1)用SOPC Builder系統綜合軟件來進行NIOS軟核的軟件配置,包括NIOS CPU配置、片上ROM及RAM設置、FLASH設置、SDRAM設置、JTAG調試配置、加入定時器、加入外部RAM總線——Avalon三態總線橋、通訊接口、按鍵PIO與LED PIO設置、指定基地址和配置NIOS軟核,這樣整個NIOS軟核已經配置完畢,之后需要編譯,并生成圖形文件,成為Quartus II設計的一部分。

(2)使用Quartos II軟件來選取具體的Altera可編程器件系列,并對SOPC Builder生成的HDL設計文件進行布局布線;再使用Quartos II軟件選取目標器件并對NIOS II系統上的各種I/O口分配管腳,另外還要根據要求進行硬件編譯選項或時序約束的設置。在編譯的過程中,Quartos II從HDL源文件綜合生成一個適合目標器件的網表。最后生成配置文件。

(3)使用Quartos II編程器和Altera下載電纜,將配置文件下載到開發板上。當校驗完當前硬件設計后,再將新的配置文件下載到開發板上的非易失存儲器里。

3.2.嵌入式實時操作系統MicroC/OS-II的應用設計

目前比較流行的嵌入式操作系統主要有MicroC/OS-II , MicroCLinux,VxWorks等,考慮到系統資源以及NIOS II IDE 開發環境包含MicroC/OS-II實時操作系統,為設計者提供快速地搭建基于NIOS II處理器的MicroC/OS-II應用程序的能力,, 故本系統的操作系統選用MicroC/OS-II 。MicroC/OS-II 是一種可固化、可剪裁、占先式的多任務實時操作系統內核。它為每個任務分配單獨的堆棧, 提供多種系統服務可進行中斷管理。

創建一個基于NIOS II處理器的MicroC/OS-II軟件過程包含以下步驟:創建一個新的NIOS II IDE工程;設定MicroC/OS-II軟件工程庫;建立并運行NIOS II 下的MicroC/OS-II軟件工程。

一、 創建一個新的NIOS II IDE工程

創建一個新的NIOS II IDE工程的方法比較簡單,基本上按照向導就能完成,要注意的是在 Project Template(工程模板)選擇中, 要選擇 the MicroC/OS-II Tutorial,在New System Library Dialog Box 頁面中的Select Type of system library欄中要選擇MicroC/OS-II。

二、設定MicroC/OS-II的步驟

(1). 在NIOS II IDE的C/C++ Projects視圖中,右鍵在系統庫上單擊std_system_lib。

(2). 在彈出的菜單中選擇Properties打開Properties對話框。

(3). 單擊System Library顯示system library選項。

(4).單擊在RTOS 下面的RTOS Options。彈出MicroC/OS-II RTOS Options對話框。

(5).單擊“+”在在左邊的面板中,展開MicroC/OS-II目錄。MicroC/OS-II是高度映射可設定的。你選定的對話框中的選項被保存在os_cfg.h文件中。選定的MicroC/OS-II選項被包含在二進制中。通過單擊MicroC/OS-II下每一個選項檢查你所能選擇的選項。

(6).選擇默認設置單擊OK。你將返回系統庫選項對話框,然后單擊OK完成設置。

三、建立并運行NIOS II 下的MicroC/OS-II軟件工程

在這一部分,在嵌入式系統中設計并運行一個MicroC/OS-II程序,通過在嵌入式操作系統MicroC/OS-II下編寫2個互相調用任務來測試本系統的運行情況。

1.打開ucosii_tutorial.c

2.頭文件加入如下代碼

#include “system.h”

#include “altera_avalon_pio_regs.h”

#include “alt_types.h”

3.加入相關定義

#define TASK_STK_SIZE 1024

#define TaskStart_ID 0

#define Task1_ID 1

#define Task2_ID 2

#define TaskStart_Prio 1

#define Task1_Prio 4

#define Task2_Prio 3

OS_STK TaskStk[N_TASKS][TASK_STK_SIZE];

OS_EVENT *AckMbox;

OS_EVENT *TxMbox

4.在初始化函數 initCreateTasks函數中加入如下代碼

OSTaskCreateExt(TaskStart, 0, &TaskStk[0][TASK_STK_SIZE-1], TaskStart_Prio, TaskStart_ID, &TaskStk[0][0], TASK_STK_SIZE, 0, OS_TASK_OPT_STK_CHK );

OSTaskCreateExt(Task1, 0, &TaskStk[1][TASK_STK_SIZE-1], Task1_Prio, Task1_ID, &TaskStk[2][0], TASK_STK_SIZE, 0, OS_TASK_OPT_STK_CHK );

OSTaskCreateExt(Task2, 0, &TaskStk[2][TASK_STK_SIZE-1], Task2_Prio, Task2_ID, &TaskStk[3][0], TASK_STK_SIZE, 0, OS_TASK_OPT_STK_CHK );

5.增加執行2任務互相調用的代碼

void Task1(void * pParam)

{ //往接收消息隊列發送A

char txmsg;

INT8U err;

txmsg = ‘A’;

while(1)

{

OS_ENTER_CRITICAL();

printf( “Hello from task1\n” );

OS_EXIT_CRITICAL();

OSMboxPost(TxMbox, &txmsg);

OSMboxPend(AckMbox, 0, &err);

OSTimeDly(2);

}

}

void Task2(void * pParam)

{

char *rxmsg;

INT8U err;

while(1)

{

rxmsg = OSMboxPend(TxMbox, 0, &err);

OS_ENTER_CRITICAL();

printf( “Hello from task2\n” );

OS_EXIT_CRITICAL();

OSTimeDly(2);

OSMboxPost(AckMbox, (void*)1);

}

}

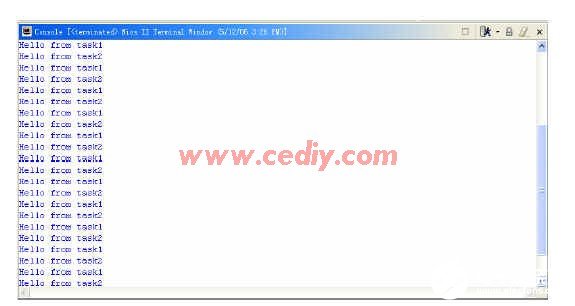

6、 選擇Run As 》 NIOS II Hardware (Run menu中)創建程序,下載它到試驗板中并運行。下載完成后,當執行這兩個任務時,任務一返回:“Hello from task1”;而任務二返回:“Hello from task2”,兩個任務之間互相調用。

得到測試結果如圖2:

圖2 MicroC/OS系統測試結果

從測試結果中可以看出,任務一和任務二被反復的調用,這與預期中執行的結果相同,說明系統能夠在FPGA中穩定運行。

四、結束語

本文介紹的基于FPGA的嵌入式系統設計達到了預期效果, CPU 本身是以軟核的方式實現, 其功能可根據需要進行定制, 非常靈活。嵌入式MicroC/OS-II 操作系統的32 位嵌入式微處理器進行核心控制,利用它強大的運算處理能力,不僅減少了系統所用的器件數量和系統的尺寸,更提高了系統的可靠性和靈活性。該設計為嵌入式系統設計提供了一條新思路,體現了FPGA的靈活性、高集成性等特性,大大降低了成本,縮短了開發時間。

責任編輯:gt

電子發燒友App

電子發燒友App

評論