除法運算。很多人覺得不就是除法嘛,直接打上/即可,但是,FPGA是不能正確綜合這個除法器的,綜合的結果只是一個固定數值,而不像其他微處理器。可以這么說,用FPGA實現除法運算是比較麻煩的。

2020-06-17 10:17:27 6533

6533

代替,比如可以先用除法運算獲得整數部分,然后用求余運算獲得余數,再對余數進行運算。2、本例實現一個除法運算,所得上的整數部分送P1口顯示,小數部分送P0口顯示。3、實現方法,本例計算101除以2的結果

2012-03-22 10:47:30

51單片機中B寄存器是SFR,B寄存器僅在乘法、除法指令中為寄存器尋址,在其它指令中為直接尋址。那么它只有在乘除法時看做特殊功能寄存器,其他指令看做通用寄存器。但是直接尋址是訪問特殊功能寄存器的唯一方式,為什么B寄存器在乘除法指令中是寄存器尋址?

2019-01-01 09:45:47

使用c6678進行浮點除法運算的時間測試的時候(使用clock),發現(使用c6678evm板)運行時間很長,運算時間達到七百多個時鐘周期。請問是什么原因?c6678本身的浮點除法能達到什么樣的運算速度呢?

2018-06-21 13:49:31

您好:

不知道TI有沒有矩陣矢量算法庫,我現在想要實現復數矩陣間的加減乘除,開方,共軛等運算。如果有收費的,我也可以買。

謝謝!

2018-06-21 00:36:43

EP2C5T144中PLL_OUTn和PLL_OUTp輸出時鐘是否為相位相差180度?

2014-10-31 10:19:55

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8這三種芯片的區別,用哪種芯片較好?買哪種芯片的學習開發板較好? 謝謝大家的求解!!!

2013-07-21 19:46:34

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8這是三種芯片的區別,用哪種芯片較好?買哪種芯片的開發板較好?謝謝大家的求解啊!!!

2013-07-21 19:58:40

EP2S130F1508C4國宇航芯代理EP2S180F1508C5N國宇航芯代理EP2S130F1020C3N國宇航芯代理EP2S130F1020I4N國宇航芯代理EP2S130F1020C4國

2019-09-05 11:36:09

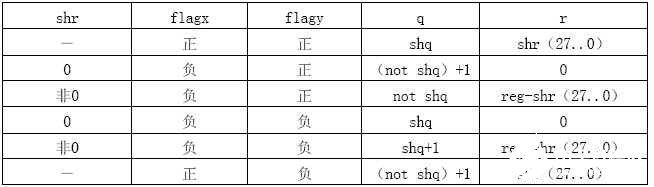

標志實現不可恢復的加-減除法運算,運行的結果存在R3中。如果要做有符號除法,首先應執行DIVS一次,從而得到商的符號位。然后多次執行DIVQ得到商。【 指令周期 】 2 + RW (DIVS) / 3

2009-09-21 09:26:57

實現兩個二進制除法運算,并在八個七段數碼管上進行顯示實現兩個二進制除法運算,并在八個七段數碼管上進行顯示實現兩個二進制除法運算,并在八個七段數碼管上進行顯示

2013-11-01 20:34:01

運算符1、算數操作運算符+、-、*、/、%加法:A+B, AB最好是同類型乘除:乘法在很多CPU中并不支持,乘除法能不用就不用,可能會使執行變差求模/求余數:n%m=res[0~(m-1)]求模

2021-12-24 06:13:41

倒位序算法分析實數蝶形運算算法的推導DIT FFT算法的基本思想分析

2021-04-26 06:03:57

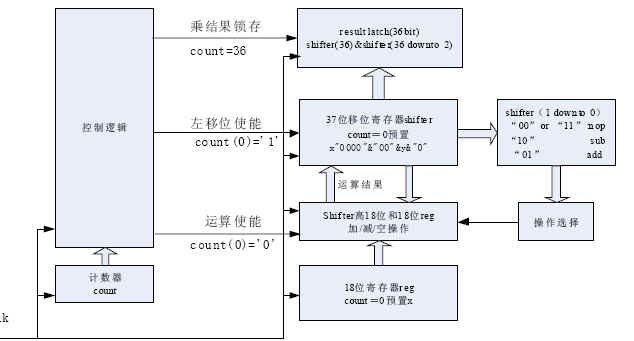

的要求和FPGA芯片設計的靈活性結合起來,采用Alter公司的CycloneⅡ系列FPGA芯片EP2C35F672C8,用VHDL語言編程,最后分別使用Quartus Ⅱ和Matlab軟件開發工具驗證實現

2010-05-28 13:38:38

在使用verilogHDL編程數據運算時使用了乘除運算不知道會出錯不,求指導

2020-05-27 14:20:31

] signal_b;需要注意一點,FPGA將所有有符號數視為二進制補碼形式,運算的結果同樣為補碼。再來看看除法器IP核配置界面。總共就兩頁,非常簡單。需要重點關注的有三個地方:1 算法實現結構

2018-08-13 09:27:32

`可以實現5位運算,有加減乘除平方開方倒數等`

2016-05-18 16:15:26

RISC有沒有乘除法指令呢?

2023-02-27 13:59:57

求助!STC12C5A60S2無法實現開平方算法(sqrt函數),以及atan2和asin怎么辦?我已經包含了相關的頭文件了,但是編譯通不過。

2020-05-20 09:07:38

本帖最后由 liuliwei25 于 2016-1-28 14:44 編輯

請問labview如何實現加減乘除的混合運算,如圖所示。謝謝

2016-01-28 14:29:47

的C51定點運算庫,在乘除相關指令方面,沒能充分運用中穎SH79/88/89/F51系列自帶的 16位X8位硬件乘法器 和 16位/8位硬件除法器,網上搜了一下,中穎SH79/88/89/F51系列有個

2011-11-22 19:26:19

為什么MCU中的除法運算要比乘法運算的效率低

2023-10-09 07:45:11

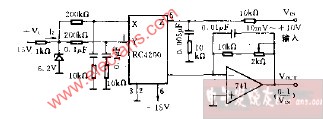

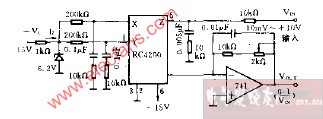

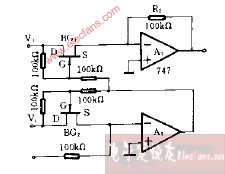

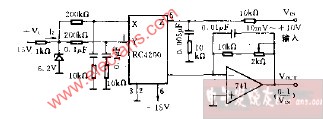

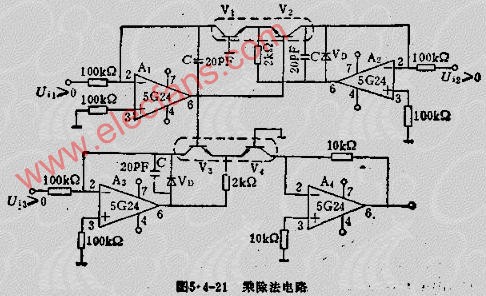

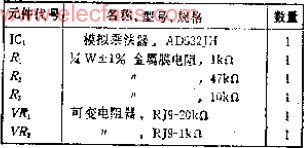

這個是論壇里的一個乘除法電路,但是我不能明白為什么這個電路可以實現U1*U3/U2,并且誤差很小。我自己搭建過一個乘除法電路,也是想實現U1*U2/U3,但是結果誤差比論壇里的這個電路大。求大神幫我

2019-12-28 17:06:07

最近,做項目時,需要使用開發運算,但是調用標準c庫的sqrt函數,發現該函數有2k多大小,當然執行時間也就很長了,根本不適合單片機的運算。故而,網上找了一個簡化的算法,編譯出來后,只有不到100字節

2021-11-24 08:07:47

它不需要浮點運算,也不需要乘除運算,因此可以很方便地運用到各種芯片上去。我們先來看看10進制下是如何手工計算開方的。先看下面兩個算式,x = 10*p + q(...

2021-07-15 07:03:45

本設計方案采用了一種改進的快速中值濾波算法,成功地在Altera公司的高性能Stratix II EP2S60上實現整個數字紅外圖像濾波,在保證實時性的同時,使得硬件體積大為縮減,大大降低了成本

2021-04-23 06:00:55

指令流水線的優化、針對寄存器分配進行的優化等。 ARM在硬件上不支持除法指令,編譯器是通過調用C庫函數來實現除法運算的,有許多不同類型的除法程序來適應不同的除數和被除數。但直接利用C庫函數中的標準

2011-07-14 14:48:47

的缺點,能做到真正意義上的實時權向量提取。在這些處理方式中一般采用標準Givens旋轉來實現QR分解或MQR分解,標準Givens旋轉包含開方和除法運算,保證足夠精度及穩定性的開方和除法運算的運算量相當大

2020-11-23 09:15:32

和fifo_dat aiQ可以發現兩者并不完全一樣,這時由于FPGA編程為定點數作造成的。4 結論該方法基于StratixⅡ系列的EP2S90 FPGA芯片實現了數字穩定校正功能,消除了發射信號的相位

2015-02-05 15:34:43

必須具備A/D轉換功能。采用專門的A/D轉換芯片,固然可實現輸出電壓的檢測,但電路變得復雜且成本偏高。經綜合考慮,本系統采用STC12C5A60S2單片機作為系統的主控制器。 STC12C5A60S2

2018-10-18 16:55:48

內部高速運算,本系統時鐘采用外部32 MHz晶振作為時鐘源。 STC12C5A60S2單片機最小系統由時鐘電路、復位電路組成,其電路如圖2所示。單片機最小系統實現按鍵輸入識別、顯示控制、PID算法

2018-09-30 16:26:35

高端Stratix II系列芯片,型號為:EP2S系列EP2S60-F1020C5, 具有邏輯單元60,440, RAM總數318024Kb,DSP blocks 36個,18-bit × 18-bit

2012-06-13 11:39:49

高端Stratix II系列芯片,型號為:EP2S系列EP2S60-F1020C5, 具有邏輯單元60,440, RAM總數318024Kb,DSP blocks 36個,18-bit × 18-bit

2012-06-13 12:01:23

太原市山西思軟IT實訓中心嵌入式學員和大家分享實數蝶形運算算法,如下。蝶形公式: X(K) = X‘(K) +X’(K+B)W PN , X(K+B) = X‘(K) -X’(K+B) W

2012-11-12 18:29:00

如何在ALTERA公司的Quartus II環境下用VHDL、Verilog HDL實現設計輸入,采用同步時鐘,成功編譯、綜合、適配和仿真,并下載到Stratix系列FPGA芯片EP1S25F780C5中。

2021-04-15 06:19:38

怎么用stm32進行開方運算

2019-10-09 04:35:58

了解或想開發無人機的朋友肯定繞不過姿態解算這茬,花點時間去了解它們原理并不難,這里提供兩個原理鏈接供大家參考:四元數表示旋轉的理解四旋翼姿態解算原理而在代碼實現方面,我這里寫好了姿態解算算法模塊供大家學習和參考。

2022-01-11 07:06:21

的四種單片機常用開方根算法: 對于擁有專門的乘除法指令的單片機,可采用以下兩種方法: 1、二分法 對于一個非負數n,它的平方根不會小于大于(n/2+1)(謝謝@linzhi-cs提醒)。在[0

2020-11-26 17:01:04

- 例程2,ADC濾波算法04 - 總結1us的誤差,足矣改變這個世界 ————CSDN根號301 - 為什么整數位移比乘除法高效??首先,整數位運算要比乘除法要高效。如果學過計算機組成...

2021-12-24 07:33:48

簡單給大家分析一下嵌入式C語言編程時用到的除法與移位。 除法土豪 除法在嵌入式微處理器里可算是一個消耗大戶,復雜的實現方式不僅占用了大師寶貴的計算時間而且精度有限情況下占用了大片的RAM。因此

2019-04-30 00:31:32

一起配置硬件除法器和硬件開方器。除法和開方是非常消耗時間的運算,而在電機控制算法中,乘除法和平方根運算在電機運算中使用頻率較高。為了提高MCU的工作效率,MM32SPIN2x了內嵌硬件32bit硬件

2018-11-30 09:23:40

編制程序實現計算器功能,包含加減乘除運算。

2016-04-15 22:38:06

小弟最近在用STM32F030C6T6芯片完成電機的SVPWM控制。現在發現算法中,運行速度很慢。打算將所有的除法運算改成移位運算。一般的,無符號數的右移幾位和除以2的幾次冪是等效的。但是,在STM32里面,有符號數的右移也和除法運算等效嗎?

2019-01-22 08:14:26

請問一下,我現在使用的TMS320F28069浮點芯片,我在進行算法計算時,直接采用浮點乘除法,如0.1234/9.3123這類的除法,這樣計算的效率和使用IQ格式進行計算有區別嗎?在實時性要求高的地方,使用IQ格式快還是直接采用/進行計算,謝謝。。。。。

2018-09-20 11:49:06

請問altera芯片EP2C5T144C8和C8N的區別? 謝謝

2012-03-30 22:37:06

Boot到ram中,則除法、開方、sin、cos的執行時間變成2倍了。加法和乘法運算都正常。想不通啊,急急急,求大俠指點~

2018-10-18 10:40:05

好不容易弄了一個四元數解算的四軸程序,但是四軸總會有抖動,想問問有沒有好的姿態解算算法

2019-04-11 06:36:20

六位四則運算計算器(8)算法實現加減乘除霧盈 2016-8-31 一、寫在前面今天來講計算模塊,這個模塊在我的計算器設計里不是核心項目,只是個計算功能。一般情況下,童鞋寫加減乘除運算都使

2016-09-01 09:03:33

在許多定點DSP芯片中,一般不提供單周期的除法指令;而在實際應用中,又常常要用到除法運算,因此如何利用簡單的指令來實現除法是一個非常重要的問題。本文對定點除法算法

2009-04-16 14:03:07 48

48 Stratix II EP2S60 DSP Development Board

The Stratix® II EP2S60 DSP development board

2010-04-07 10:54:27 51

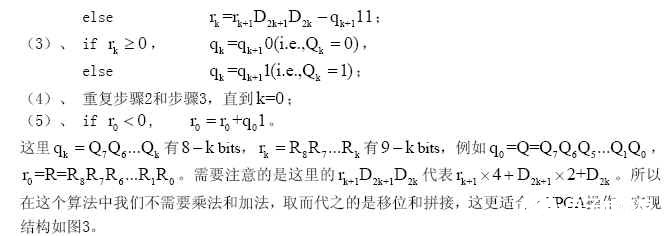

51 高精度的乘除法和開方等數學運算在FPGA實現中往往要消耗大量專用乘法器和邏輯資源。在資源敏感而計算時延要求較低的應用中,以處理時間換取資源的串行運算方法具有廣泛的應

2010-07-28 18:05:14 37

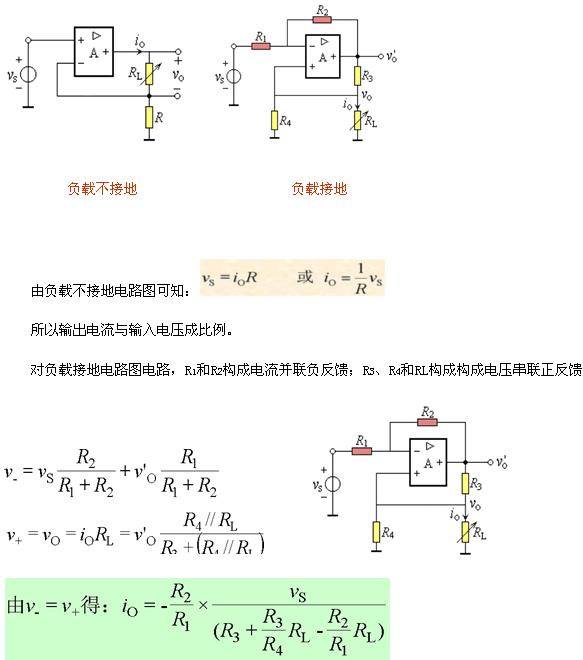

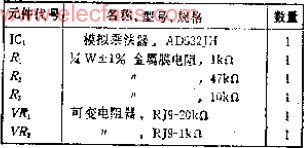

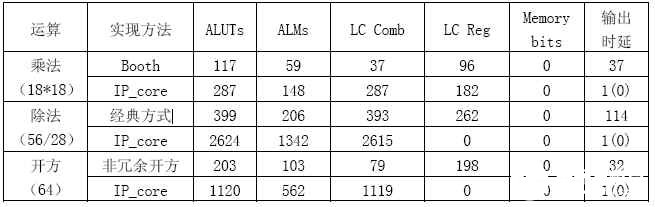

37 模擬乘法器在運算電路中的應用

8.6.1 乘法運算電路

8.6.2 除法運算電路

8.6.3 開方運算電路

2010-09-25 16:28:45 145

145 針對Altera Stratix IV EP4SGX360和EP4SGX530器件的電源參考設計,具體電路如下圖:

2010-12-12 10:37:52 64

64 針對Altera Stratix IV EP4SGX70和EP4SGX110器件的電源參考設計,電路圖如下:

2010-12-12 10:43:38 41

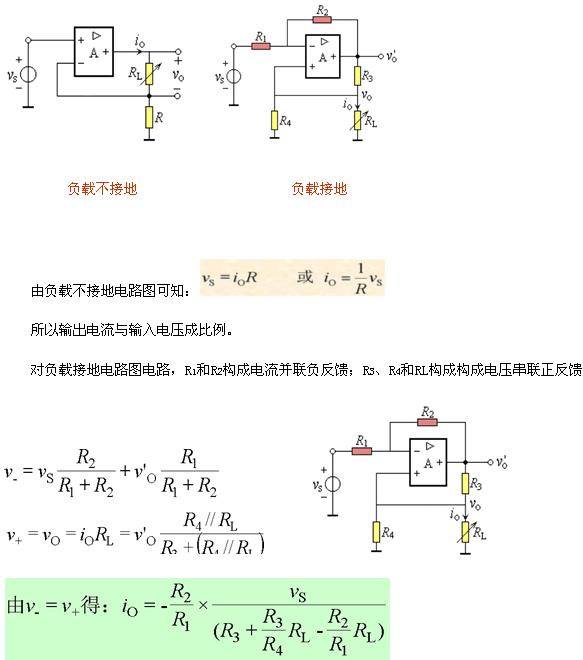

41 乘除運算電路

基本乘除運算電路,乘法電路

乘法器符號

2008-01-17 12:54:12 2705

2705

乘除運算電路圖

2009-07-17 11:26:22 445

445

除法運算電路圖

2009-07-17 11:26:48 4079

4079

乘除運算電路圖

2009-07-20 12:09:43 531

531

除法運算電路圖

2009-07-20 12:10:07 734

734

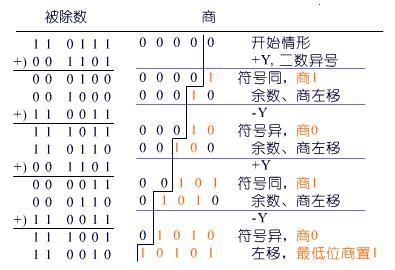

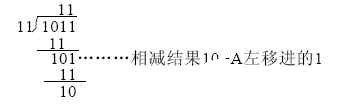

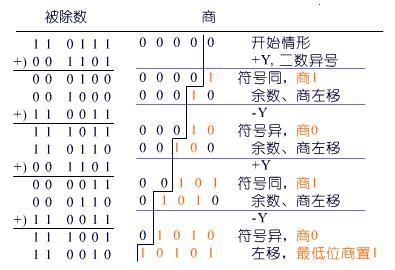

定點補碼一位除法的實現方案 與補碼乘法類似,也可以用補碼直接完成除法運算,即用 [X]補/[Y] 補 直接求得[X/Y]補 。補碼除法的規則比原碼除

2009-10-13 22:58:39 3040

3040

Altera推出業界密度最大的Stratix IV EP4SE820 FPGA

Altera宣布,40-nm Stratix IV E FPGA高端密度范圍增大到業界領先的820K邏輯單元(LE)。Stratix IV EP4SE820 FPGA是業界同類產品中密度最大

2009-11-11 16:50:00 838

838 原碼除法運算原理是什么? 兩個原碼表示的數相除時,商的符號由兩數的符號按位相加求得,商的數值部分由兩數的數值部分相除求得。 設有n位定

2010-04-13 11:15:45 11598

11598 二進制數值數據的編碼與運算算法

一、原碼、反碼、補碼的定義

1、原碼的定義

2、補碼的定義

2010-04-15 14:42:03 2561

2561 除法器對數運算電路的應用

由對數電路實現除法運算的數學原理是:

2010-04-24 16:07:27 2520

2520

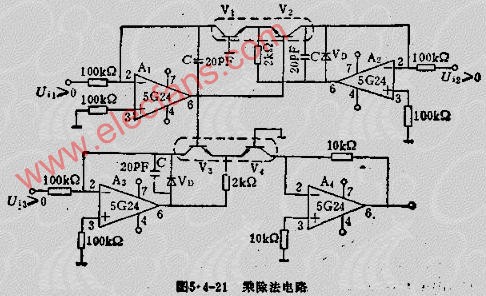

乘除法電路

圖5.4-21是乘除法運算實用電路之一。

1、A

2010-04-26 16:11:49 16251

16251

用于比率計算的除法運算電路

電路的功能

本電路是用X除輸入信號Z

2010-05-08 15:29:01 1619

1619

介紹一種在 8096 /96 系列單片機上實現的單精度 浮點數 快速除法。該算法采用了預估一修正的數值計算方法,并充分利用了16 位CPU 中的乘除法指令,計算速度快、精度高,有很強的實用

2011-06-03 16:47:06 93

93 FPGA實現鐵軌檢測算法設計_本文將闡述如何用乘法運算代替除法運算,以及如何使除法的次數最少化。

2011-10-05 16:37:19 10787

10787

該ALU采取層次化設計方法,由控制模塊、邏輯模塊、加減法模塊、乘法模塊和除法模塊組成,能實現32位有符號數和無符號數的加減乘除運算,另外還能實現9種邏輯運算、6種移位運算以

2012-02-09 15:24:55 80

80 基于FPGA的開方運算實現 ,的技術論文

2015-10-30 10:59:01 5

5 單片機實現開方,在沒有乘法指令的情況下。

2016-12-20 22:45:39 3

3 14.2 除法運算 因為ARM體系結構本身并不包含除法運算硬件,所以在ARM上實現除法是十分耗時的。ARM指令集中沒有直接提供除法匯編指令,當代碼中出現除法運算時,ARM編譯器會調用C庫函數(有符合

2017-10-17 17:22:29 5

5 本文采用Altera公司Stratix II系列的EP2S90F1508C3芯片,以Quartus II 8.1為開發環境[4],采用硬件描述語言VHDL進行SM3算法的FPGA實現。SM3算法實現

2017-11-24 15:33:59 2445

2445

為確保安全苛求系統中程序執行的正確性,研究人員將差錯控制理論用于對計算機指令進行編碼,但由于編碼大多涉及模運算,導致復雜度大量增加,應用于實時系統有困難。針對復雜度問題對delta碼的乘除法運算算法

2017-12-04 16:44:29 0

0 ,且通常無法在一個時鐘周期內完成。因此FPGA實現除法運算并不是一個“/”號可以解決的。 好在此類基本運算均有免費的IP核使用,本人使用的VIVADO 2016.4開發環境提供的divider gen IP核均采用AXI總線接口,已經不再支持native接口。

2018-05-18 01:15:00 4150

4150 單片機中的除法也是二進制的除法,和現實中數學的除法類似,是從被除數的高位開始,按位對除數進行相處取余的運算,得出的余數再和之后的被除數一起再進行新的相除取余的運算,直到除不盡為止,因為單片機中的除法是二進制的,每個步驟除出來的商最大只有1,所以我們實際編程時可以把每一步的除法看作減法運算。

2018-05-31 08:51:02 5618

5618

)。Stratix IV EP4SE820 FPGA是業界同類產品中密度最大、性能最好、功耗最低的FPGA。EP4SE820 FPGA非常適合各種需要大容量FPGA的高端數字應用,包括ASIC原型開發和仿真

2018-10-24 20:40:01 419

419 開方運算作為數字信號處理(DSP)領域內的一種基本運算,其基于現場可編程門列(FPGA)的工程實現具有較高的難度。本文分析比較了實現開方運算的牛頓-萊福森算法,逐次逼近算法,非冗余開方算法3種算法

2020-08-06 17:58:15 6

6 非平行多導體傳輸線串擾的快速計算算法

2021-06-18 11:15:25 7

7 、加減法、判斷和循環實現,因為它不需要浮點運算,也不需要乘除運算,因此可以很方便地運用到各種芯片上去。我們先來看看10進制下是如何手工計算開方的。先看下面兩個算式,x = 10*p + q (...

2021-11-11 13:36:10 1

1 匯編實現多字節乘除法乘法單片機的乘法本質是二進制的乘法,而乘法本身是通過加法實現的。多字節的乘法其實就是移位做加法。例如7x11,用二進制豎式表示如下圖:可以看到,其實就是判斷乘數的每一位是1還是

2021-11-15 17:21:03 18

18 最近,做項目時,需要使用開發運算,但是調用標準c庫的sqrt函數,發現該函數有2k多大小,當然執行時間也就很長了,根本不適合單片機的運算。故而,網上找了一個簡化的算法,編譯出來后,只有不到100字節

2021-11-16 15:51:01 7

7 FPGA中的硬件邏輯與軟件程序的區別,相信大家在做除法運算時會有深入體會。若其中一個操作數為常數,可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運算會占用較多的資源,電路結構復雜,且通常無法在一個時鐘周期內完成。因此FPGA實現除法運算并不是一個“/”號可以解決的。

2022-04-27 09:16:03 6098

6098 比調用乘除法子程序生成的代碼效率高。實際上,只要是乘以或除以一個整數,均可以想辦法用移位的方法得到結果,如: a =a* 9 可以改為: a =(a 3 )+a 采用運算量更小的表達式替換原來的表達式

2023-11-21 11:25:41 359

359

電子發燒友App

電子發燒友App

評論