一、概述

在常用的信號源及信號處理設計方案中,RC/LC振蕩電路頻率調整方便,但是它的工作頻率穩定度較低。頻率穩定度較低導致系統的工作穩定度降低,使其不適用于對精度要求較高的場合。晶振具有穩定且較高的頻率,其頻率穩定精度可達到10-6以上,但是它的頻率是固定不可調的。晶振不能很方便地產生各種頻率可變的信號。晶振加鎖相環(PLL)電路可結合晶振頻率穩定度高和鎖相環頻率可調的優點,但是輸出頻率只能成倍的變換,還是不能解決頻率可調的根本問題;頻率合成器則通過一排晶體振蕩器來產生的各種頻率的信號,通過開關進行頻率混合實現頻率合成,但外圍電路復雜,分辨率難以提高。

DDS(Direct Digital Frequency Synthesis)技術的出現無疑為我們提供了一種新的選擇。DDS技術采用晶振作為系統的時鐘,從而提高了輸出頻率的穩定性;頻率控制字及相位累加器的位數決定了頻率分辨率,其計算公式為 △f ?fclk/2N 。這里fclk為系統時鐘頻率;N為相位累加器的位數。隨N增大使得頻率分辨率提高;同時頻率控制字的可調整性使得系統輸出頻率非常容易調整。

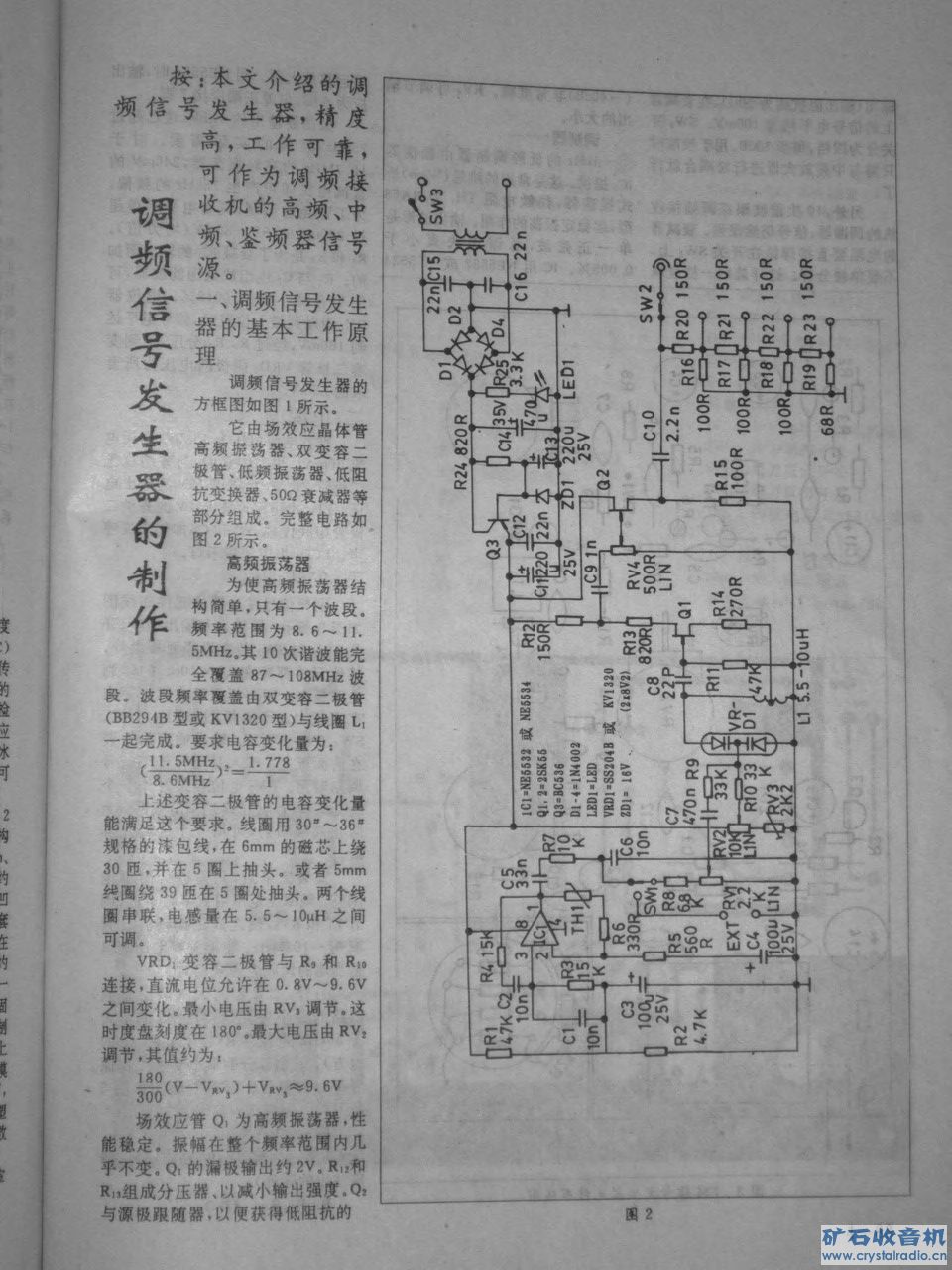

在此思想指導下,我們應用ALTERA公司的FPGA器件、QuartusⅡ開發環境和NIOS軟核等相關的開發工具,采用VHDL語言及SOPC設計思想,輔以必要的模擬與數字轉換電路,構成了一個基于DDS技術的數字調頻發生器,該設計解決了輸出頻率在精確度和可調性之間的矛盾。

二、功能說明

本系統由數字式點頻信號發生器、掃頻信號源和全數字調頻發生器三部分組成。

1、信號發生器

具有產生多種波形(如:正弦波、三角波、鋸齒波和方波4種波形)的功能。用鍵盤輸入選擇上述波形,并可進行相位連續切換。重復頻率可調,且相位連續調整,頻率步進間隔可擴,輸出波形幅度可調整,并具有實時顯示輸出波形頻率和幅度值的功能。

2、掃頻信號發生器

具有輸出正弦波掃頻信號的功能。用鍵盤輸入編輯生成掃頻信號,控制輸入上、下限及步進頻率,可進行隨時暫停,并具有掃頻延時回放功能。

3、全數字調頻發生器

對采樣信號進行全數字調頻,可以輸出具有原信號信息的調頻信號,把輸入的模擬信號幅度的變化轉化為載波頻率的變化,簡單的實現全數字調頻信號發生器。重復頻率可調,且相位連續調頻,頻率步進間隔可擴。

三、系統構成

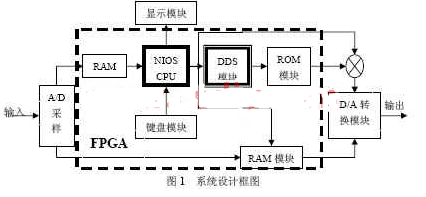

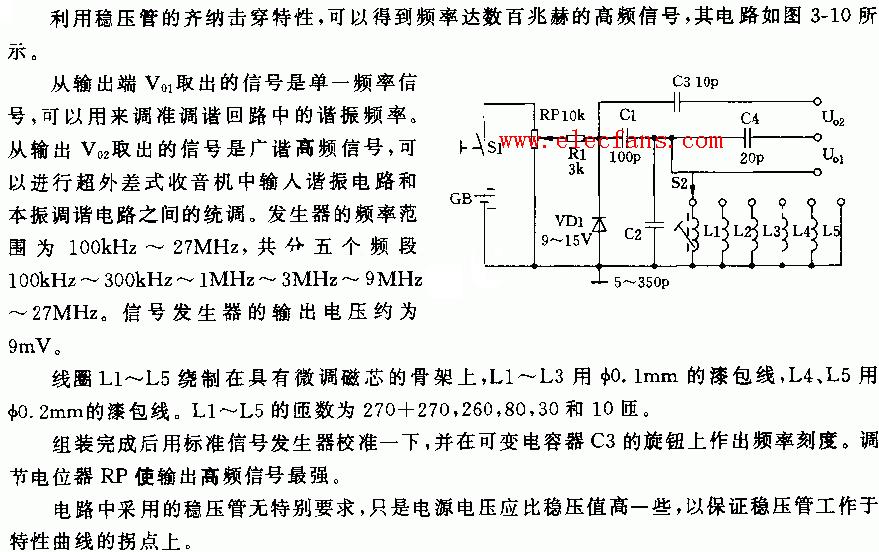

系統設計框圖如圖1所示:

四、設計描述

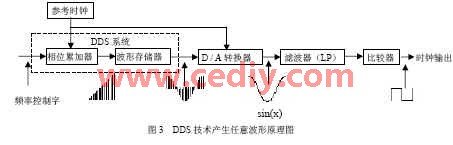

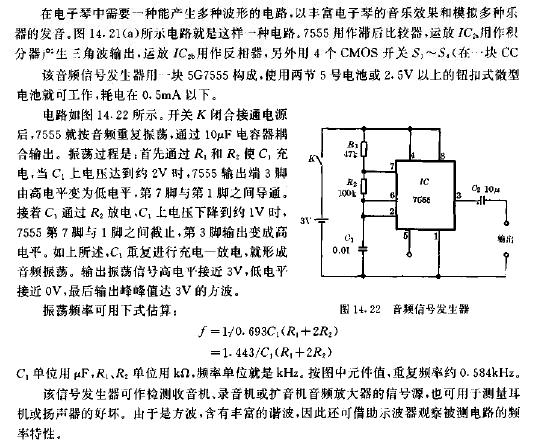

隨著電子技術的發展和大規模集成電路制作工藝的提高,DDS(Direct Digital Frequency Synthesis)技術的出現無疑為我們提供了一種選擇。但是DDS技術是否適合設計所要求的信號源,而屏蔽掉常規器件的缺點,我們可以通過對DDS技術的簡要介紹來解決這個問題。DDS技術產生任意波形原理圖如圖3所示:

如圖所示,DDS系統的參考時鐘由晶振產生,輸入的頻率控制字在參考時鐘控制下實現相位累加,截取相位累加器高位產生波形存儲器的讀數地址。由于波形存儲器類似一維向量表,僅需給地址便可取數據。那么將相位累加器輸出的相位高位作為輸入的地址,波形存儲器內部存儲的是每一個相位對應的幅度信息。每次訪問一個地址,就輸出一個幅度值數據。

根據相位與幅度的對應關系獲得幅值信息,將幅值信息送往D/A轉換器,再經過濾波器即可得到一定頻率的輸出信號。以固定的速度繞相位環旋轉的矢量導致了一個完整周期正弦波的輸出。如果向累加器輸入的頻率控制字改變時,矢量在相位環上的訪問速度會相應改變,則輸出信號的頻率也會改變,即可實現頻率可調。

由于兼有這三個方面的優勢,DDS技術便成為本次系統設計中信號產生部分的首選。

在本設計作品的實際過程中,我利用ALTERA提供的QuartusⅡ及NIOS在實際的硬件實現上做到高速無縫連接,并利用SOPC設計理念將PLD的最高度設計抽象,彌補了軟件和硬件同時集成的空白,由于SOPC Builder是把所有和處理器子系統相關的底層詳細資料集中到單個工具中,它具有直觀的圖形用戶接口及自動完成系統集成工作,可直觀地連接總線體系,分配從設備端的仲裁優先級,這樣就極大的方便了我們的軟硬件協同設計工作。

整個系統分為硬件和軟件兩個部分。

硬件部分包括:A/D轉換模塊、鍵盤顯示模塊和D/A轉換模塊,其中鍵盤顯示模塊采用開發板上所提供的四個按鍵、兩個七段數碼管、LED和LCD液晶顯示、A/D、D/A、DDS、RAM、ROM模塊;

軟件部分包括對鍵盤顯示及整個系統聯調的NIOS控制編程。

一、 硬件部分

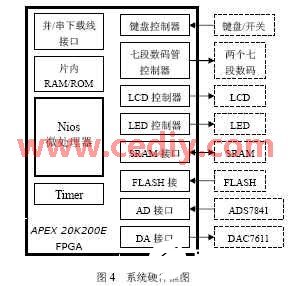

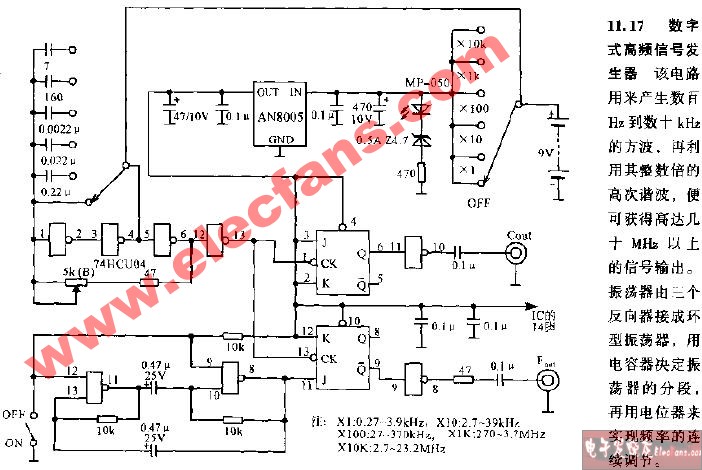

系統硬件框圖如圖4所示:

1、 鍵盤顯示模塊:

鍵盤模塊包括八鍵開關和四個按鍵。四個按鍵中功能分別為:功能切換鍵,加鍵,減鍵和確認鍵。

顯示模塊主要由七段數碼管、LED和LCD三部分組成。其中七段數碼管用于功能識別顯示,LED用于確認鍵識別,而主要的詳細數據及模式信息由LCD顯示實現。

2、 A/D、D/A轉換模塊:

A/D模塊所用器件是ADS7841,它是一個4通道、12位采樣的模擬/數字轉換器。D/A轉換模塊所用器件為DAC7611,它是工作在工業溫度范圍內的12位數字/模擬轉換器。

一幀12位數據完成D/A轉換需要12個CLK,而這12個CLK是由系統時鐘30分頻產生。系統時鐘為33.333MHz,經30分頻后所得的D/A轉換速率應為33.333MHz /30=1.1111 MHz。而訪問ROM表的時鐘頻率應與D/A轉換速率同步,所以輸出波形的頻率受到D/A轉換器的限制。如果一個周期訪問8個數值,則輸出模擬信號的頻率最高為1.1111 MHz /8=138887.5Hz,這是理論上的最大頻率值。如果采用高速并行D/A轉換器,轉換速率會大幅提高。而本次設計采用串行D/A轉換器的主要原因是因為其能應用于遠程串行通信系統。

3、DDS模塊:

(1)、相位累加器:相位累加器是DDS的核心部分,用于完成頻率控制字的相位累加,隨頻率控制字的改變進而實現調頻的功能。該功能用VHDL硬件描述語言編程實現

(2)、幅度調制:由ROM查表輸出的結果(10位)與幅度控制字(2位)通過一級乘法器實現,乘法器利用開發平臺內部的快速定制功能對生成的乘法器進行定制。并附加一級鎖存單元可以等到波形數據穩定后再向后級電路傳送,這樣就避免了毛刺的產生。

4、ROM、RAM存儲器模塊:

ROM存儲器實現任意波形數據的存儲,根據地址值從ROM表中查找出對應的數據,并將查表所得數據輸出到數字/模擬轉換模塊。存儲器不僅要有程序來對它進行控制,更為關鍵的是在其中存儲一個、二分之一或四分之一波形的數據。

RAM模塊用于信號的采集處理過程中,A/D轉換器完成對輸入模擬信號256個點的采樣,從A/D轉換器輸出的采樣數據個數為256個,所以RAM的地址位數應為8位

軟件部分

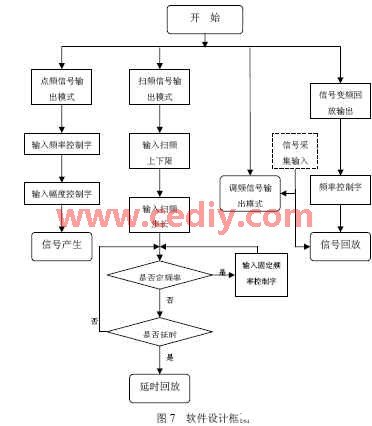

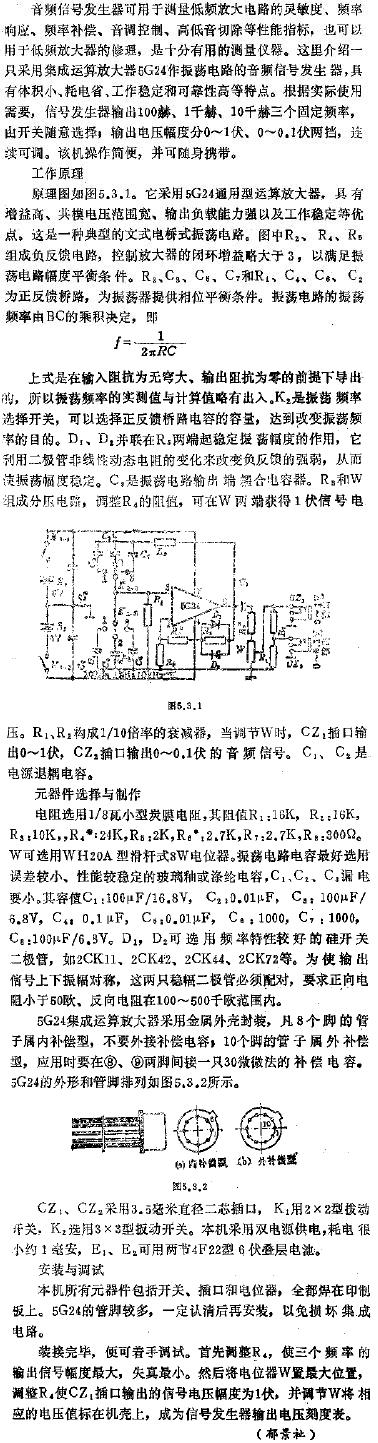

設計框圖如圖7所示:

1、 鍵盤顯示控制模塊:

利用NIOS實現鍵盤的過程中,由于設計板所提供的僅有四個的按鍵及八個開關。基本上,鍵盤顯示的控制部分均由PIO賦值及利用其固有的宏命令編制C語言加以實現。

2、 整個系統聯調的NIOS控制編程:

編制C程序實現鍵盤顯示模塊、DDS模塊及A/D、D/A轉換模塊的控制,其中大量采用了PIO賦值并利用條件語句進行判斷狀態,PIO送入不同的相應輸入字。

五、系統特點

根據實際測量指標,在頻率無論是低頻還是高頻都具有很好的頻率調整精度。其相對誤差的數學期望都在10-7數量級上,完全可以達到我們的信號發生器的功能指標,同時這樣的產品精度也是市場上類似產品所不能比擬的。由于對于晶振而言,其精度也就是10-7,由此,我們設計實現的信號源精度已經達到了針對晶振的精度極限。

在具體的設計實現過程中,我們強調抓住每個具體細節的穩定性。如在硬件乘法器方面,我們都在其后端加入了鎖存單元,利用邊緣觸發防止不定或過多毛刺的產生,從而實現了近乎理想的基于DDS理論的信號產生與處理功能。

六、總結

引入SOPC的設計理念,無疑就是一場IC革命的必然延續。就我們的設計而言,對基于SOPC理念的NIOS系統設計從掌握到充分的運用到實際設計過程中,大概不超過半個月的時間,這點就充分地體現了它的短開發周期優勢。

其次,對NIOS而言它是一種軟核處理器,因此其硬件可任意添加刪除,從而提高了整個系統的運行效果也降低了設計成本。同時對設計人員的技術要求可以大大降低。

再者,在我們的實際設計過程中由于需要大量的乘除運算,無疑利用類似于NIOS的微處理器很容易實現,可避免完全利用硬件描述語言編寫所出現的大量毛刺及工作量。

本文作者創新點:能夠利用FPGA器件參考DDS理論配合Nios軟核微處理器技術,設計實現多種波形數字幅度頻率可調的精確調頻發生器。該技術的創新點在于輸出的調頻信號頻率從0.0Hz—138887.5000Hz,最小步進可達到為0.0001Hz。在我們對頻率的測試結果中,無論是低頻還是高頻都具有很好的頻率調整精度。其相對誤差的數學期望都在10-7數量級上。因此就信號的頻率精度可靠性而言,與技術相比具有一定的優勢。

責任編輯:gt

電子發燒友App

電子發燒友App

評論