電子發燒友網核心提示: 根據ALTERA官方FAE(現場應用工程師)的強烈建議,請注意不要隨意帶電插拔JTAG下載接口,否則會損壞FPGA芯片的JTAG口信號管腳。 現象: 在排除了下載線的問題

2012-09-05 09:00:42 12784

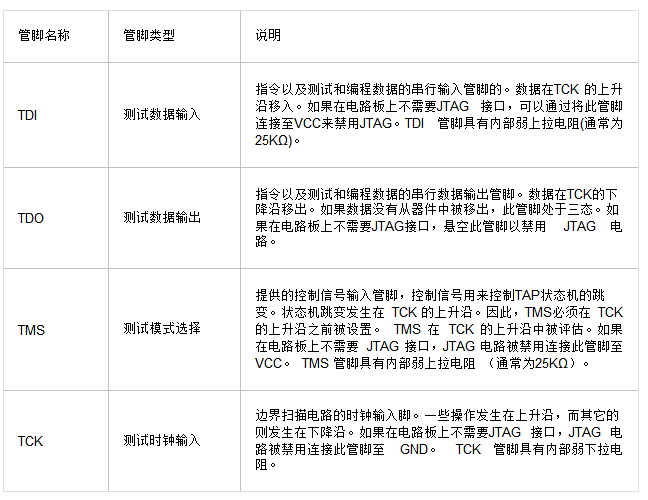

12784 ARM系列處理器正是通過JTAG 接口使用內部集成的ICE 功能, 并采用這種方式實現在線調試。此外CPLD、FPGA 等器件大多都可以使用JTAG 接口實現在線編程或下載。因此,JTAG 接口已經成為復雜芯片系統的必備接口, 在芯片測試、調試及實現其他特殊功能方面發揮著重要作用。

2018-10-16 08:11:00 5801

5801

調試,提示Incorrect clock value。按照網上的方法,已經試過下面的方法了:1.JTAG測了,對地和對電源,沒有短路;2.FPGA底部焊盤焊接3.燒寫器使用的是USB Blaster,用其他燒寫器也試過,不通各位大神,給支支招

2015-10-14 16:00:22

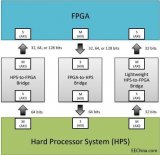

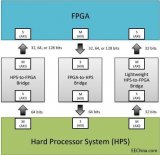

可編程邏輯(FPGA)與硬核處理器(HPS)之間互聯的結構

2021-04-02 06:03:40

在線調試方式大都是通過FPGA器件引出的JTAG接口,同時使用了一些FPGA片內固有的邏輯、存儲器或布線資源就能夠實現的。這些調試功能通常也只需要隨著用戶設計所生產的配置文件一同下載到目標FPGA器件中

2015-09-02 18:39:49

下載配置與調試接口電路設計FPGA是SRAM型結構,本身并不能固化程序。因此FPGA需要一片Flash結構的配置芯片來存儲邏輯配置信息,用于進行上電配置。以Altera公司的FPGA為例,配置芯片

2019-06-11 05:00:07

后,將電路板上電運行。然后把下載電纜接到JTAG接口上,在主機中運行Quartus II軟件,并打開Programmer編程器,單擊其中的“Auto Detect”按鈕進行FPGA下載鏈路自動檢測。若能正確檢測到FPGA,說明配置電路是正確連接的。

2012-08-12 11:52:54

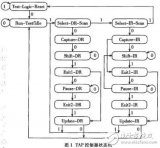

設計和制造技術的快速發展,JTAG越來越多的被用于電路的邊界掃描測試和可編程芯片的在線系統編程。(特權同學,版權所有)FPGA器件都支持JTAG進行在線配置,JTAG邊界掃描的基本原理如圖3.7所示

2019-01-30 02:34:52

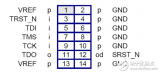

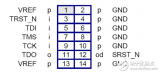

`JTAG電路設計規范`

2012-08-20 21:50:52

電路設計[FPGA]設計經驗

2012-05-23 19:49:45

電路設計[FPGA]設計經驗

2012-08-20 15:37:36

電路設計[FPGA]設計經驗

2019-01-03 14:19:28

嗨,我附上了JTAG鏈設計結構。請看一下。我想在單JTAG鏈中連接CPLD和FPGA。但是,在我的CPLD中,VCCAUX電壓網是1.8V_CPLD而FPGA Bank-0(VCCO_0)電壓網

2020-05-29 14:17:04

接收端鏈路均衡測試(Rx LEQ)進入環回模式進行誤碼率測試

2020-12-02 06:49:35

以下 JTAG 連接錯誤。

錯誤:連接失敗。

無法正確配置 JTAG 鏈(CCSProtocolPlugin)

錯誤:連接失敗。

2023-04-23 07:25:01

各位大神,小弟做FPGA不久,最近設計了一個XC3S1500的FPGA板子,經測試電源供電沒問題,但是JTAG鏈路建立不起來,初步懷疑是FPGA芯片和配置芯片(XCF08P)的VCCO不一致

2013-04-03 16:30:12

原諒我記憶力不好。。。花了好久弄明白的東西才十個小時不到就忘記了,所以趁現在記得趕緊記錄下來。本文內容:重建de1-soc中HPS-FPGA工程。 PS:原工程在http

2018-07-03 08:10:25

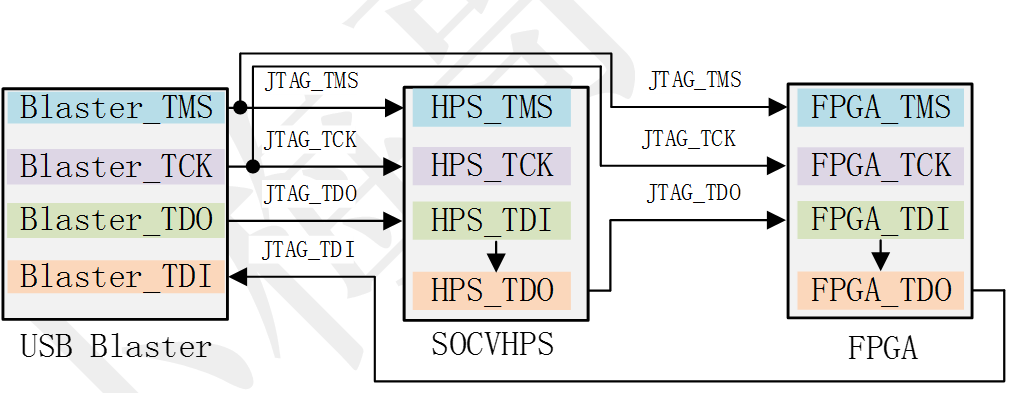

的FPGA或ARM處理器都有一些差異,但是同時兩者又有緊密的聯系。AC501-SoC開發板上的JTAG鏈同時連接了FPGA和HPS。使用時,僅需一個JTAG鏈路,就能同時調試FPGA和HPS。FPGA

2020-02-25 18:40:45

本文由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。Qsys系統和Linux應用程序之間通過一個名為hps_0.h的文件交互硬件信息,例如總線上添加

2020-02-16 18:41:59

循環以從閃存配置FPGA之后,兩個JTAG工具都無法看到JTAG鏈。“Initialize Chain”產生通用的帶鏈錯誤問題,同時加載匹配的項目文件并嘗試對flash進行編程會產生不匹配的ID錯誤

2019-05-24 14:11:46

由于Quartus?II15.0 Update 2及更早版本中的問題,用于將數據從HPS EMAC內核發送到FPGA內核的時鐘缺少時鐘分配。因此,這些HPS EMAC到FPGA路徑將不會進行時序分析。

2018-07-27 14:27:56

鏈路預算表用于計算Maxim工業、科學與醫療無線頻段(ISM-RF)產品(Tx、Rx、TRx)的鏈路性能,估算特定的射頻電路在幾種環境下的通信覆蓋范圍和鏈路裕量。該Excel?表格還可用于估算100MHz至10GHz載頻范圍的其它射頻系統的鏈路裕量。

2019-08-22 07:00:30

收到一條錯誤消息,指出JTAG電纜已拔下。FLASH可以自己編程而無需掃描鏈中的FPGA嗎?如果是這樣,我需要設置IMPACT軟件的特殊設置嗎?我該怎么做才能調試問題?謝謝!

2020-05-28 13:42:00

)。使用新PCB我遇到了以下問題:1.即使鏈中有2個器件(Flash和FPGA),JTAG也只檢測FPGA。2.我可以選擇修改JTAG鏈。這次我制作了硬件,使JTAG鏈中只有閃存。現在JTAG檢測到閃光燈并且

2020-06-10 10:20:24

通過FPGA器件本身間接的將數據燒錄到Flash等外部配置芯片中。另一種下載配置是將配置數據流直接下載到配置芯片中。由于JTAG方式靈活多用,尤其是在線調試非常快速便利,因此我們的FPGA核心板電路中就

2016-08-10 17:03:57

,希望在訪問并發上能支持較高的能力,同時可以控制精準度、實時調控、TPS直接壓測模式,甚至是大脈沖; 3、希望基于PTS完成全鏈路壓測,需要PTS能方便快捷的提供全局流量的模擬和構造能力; 4、對高可用

2018-01-30 14:13:04

我使用兩個獨立的位文件在JTAG鏈中配置了兩個FPGA。在這種情況下,完成總是設置為低,盡管影響說“程序成功”。我將完成引腳連接到LED,在那里我看不到LED發光。附加了日志文件。請提出解決方案

2019-05-22 10:32:24

大家好,我們將使用的 MCU 屬于 STM32U5 系列。調試探針將是 SEGGER J-Link Base。多個 MCU 使用典型的 JTAG 菊花鏈連接通過 JTAG 連接

2022-12-20 07:08:46

你好,我在JTAG鏈中有兩個器件 - xc7k160t和一些IR長度= 30的定制ASIC器件。我有以下情況:1.在Vivado 2016.4中 - 當ASIC處于RESET狀態時,我看到JTAG鏈

2020-06-05 15:39:32

海, 我的電路板由2個Kintex-7 fpga和兩個獨立的BPI閃光燈(微米級閃光燈)組成。如何使用單JTAG連接器(菊花鏈)progaram 2 fpga?theertha

2020-05-29 13:47:54

大家好,如果兩個FPGA連接在單個JTAG鏈中。那么DONE和INIT引腳的推薦連接是什么。兩個FPGA的INIT引腳(也是DONE引腳)是應該連接在一起還是應該分開?Xilinx是否為此推薦了任何

2019-01-10 11:00:55

接入調試端口,而不會干擾JTAG鏈路的邏輯。在微處理器碼調試期間獲得微處理器JTAG端口的全部控制,而能夠用JTAG調試工具。假如沒有測試工具連接到JTAG和編程接頭,則固件工程師除希望有到微處理器的鏈

2019-05-05 09:29:32

我有與FPGA初始化有關的問題,LED INIT改變狀態RED和GREEN。因為我無法配置JTAG鏈.....

2019-09-25 08:17:32

我自己的位文件下載到v5中,但是很失望地發現jtag鏈無法讀取FPGA的器件ID。 swothes sw6和sw3設置為11001010和00010101。和其他設置我需要配置?非常感謝 !

2019-08-16 09:13:46

多個 DSP、FPGA、CPLD 和其他邏輯器件,使得它們可以通過單個 JTAG 連接器進行控制。菊花鏈常用于具有多個 JTAG 器件的電路板,它可以將 TDI 和 TDO 引腳連接在一起以形成一個

2018-10-11 11:16:23

多片fpga組成jtag鏈的時候如何加載?

2023-08-11 09:10:26

移植到FPGA上,只有一個JTAG接口。再進行MCU調試的話,是采用其他擴展引腳定位為MCU的JTAG調試?還是使用FPGA的uart串口接口了?

2023-08-11 13:41:00

供了相應的Tcl程序包。有了這套工具,使用sld_virtual_jtag 和相應的Tcl命令,我們就可以構建自己的虛擬JTAG鏈路,并進行自定義的JTAG調試了。 一、 相關文件 后面的鏈接

2018-07-03 00:53:26

方法是通過發送Message,即DSP端程序執行時將日志信息以message方式發送到GPP,再由GPP來顯示。

4.另外一種方法是通過仿真器來調試DSP端程序,但是能不能同時調試GPP端程序呢,請各位達人給出一點建議,謝謝。

2018-06-21 20:16:33

本帖最后由 一只耳朵怪 于 2018-6-21 15:55 編輯

JTAG調試的下載器選用TI有配套的么?JTAG口在電路設計上可以如FPGA的JTAG口一樣設計為2.54間距的排針么

2018-06-21 04:41:08

本帖最后由 一只耳朵怪 于 2018-6-14 08:47 編輯

以前都是使用CCS3.3來進行調試的。現在由于想用新的片子,如F28377,所以準備升級下調試軟件平臺。先試試CCS4.12,但是發現不會設置同時調試兩個片子。有沒有知道的,來指導下,謝謝了。

2018-06-13 10:38:00

JTAG調試原理(推薦):ARM JTAG 調試原理

2009-05-27 08:59:49 21

21 JTAG調試原理(推薦):溫度循環監測儀

2009-05-27 10:38:59 54

54 JTAG調試原理(推薦):這篇文章主要介紹ARM JTAG調試的基本原理。基本的內容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介紹,在此基礎上,結合ARM7TDMI詳細介紹了的JTAG調試原

2009-05-27 10:44:50 147

147 這篇文章主要介紹ARM JTAG調試的基本原理。基本的內容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介紹,在此基礎上,結合ARM7TDMI詳細介紹了的JTAG調試原理。這篇文章主要是

2009-07-14 23:19:49 82

82 JTAG電路設計規范:本技術設計規范根據國家標準和原郵電部標準以及國際標準IEEE STD 1149.1 系列標準編制而成。

目前,使用的芯片中越來越多的CPU、EPLD、FPGA、DSP 以及一些

2009-09-19 07:40:57 93

93 嵌入式JTAG調試方法步驟

嵌入式系統JTAG調試步驟1. 將PC與調試器Multi-ICE用并口連接;調試器與開發板用14或20針的JTAG線連接。2. 依次打開調試器

2010-03-01 16:24:20 34

34 目前通訊電子產品的芯片、單板、系統的復雜度不斷提高,物理尺寸卻在不斷縮小,JTAG電路的設計也隨之成為關系到單板可測性、穩定性和可靠性的重要因素。 JTAG測試接口在集成

2010-08-02 16:42:07 0

0 JTAG技術是一種嵌入式調試技術,芯片內部封裝了專門的測試電路TAP(測試訪問口),通過專用的JTAG測試工具對內部節點進行測試和控制,目前大多數ARM器件支持JTAG

2008-08-24 13:10:39 8144

8144

JTAG調試快速入門

提要:本文介紹 AVR Studio Debug:調試運行方式及QuickWatch實時查看變量的數值。

以下的degug方式,英文版來自 AVR St

2008-10-31 21:58:10 2055

2055

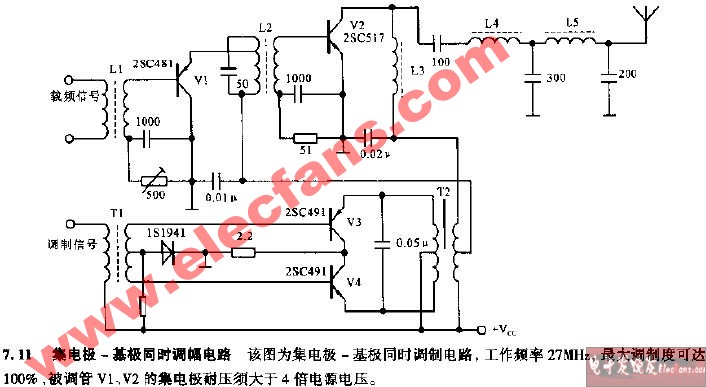

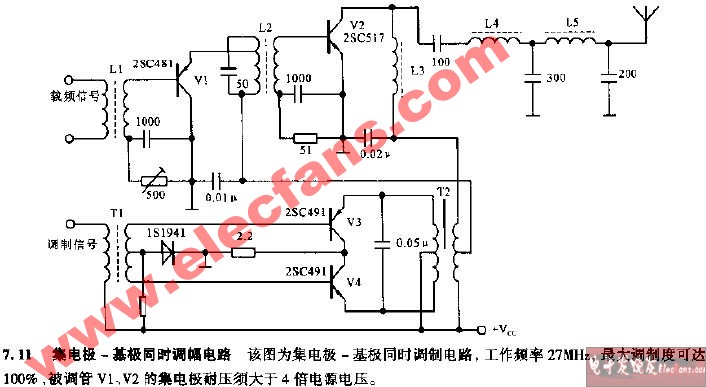

集成極-基極同時調幅電路

2009-03-19 20:17:30 649

649

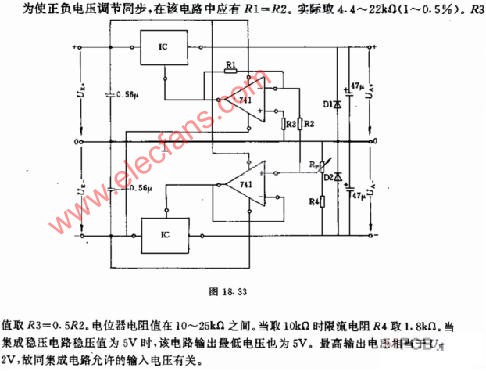

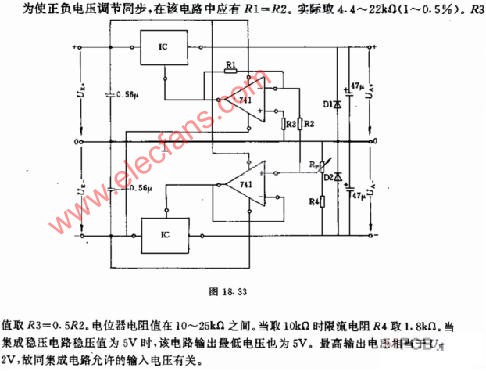

正負電壓可同時調節的穩壓電路圖

2009-05-13 21:34:43 3366

3366

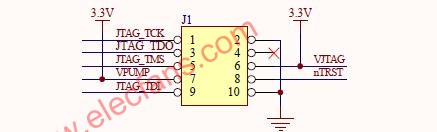

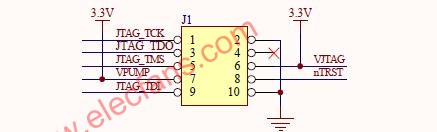

JTAG調試接口電路

注:VPUMP和VJTAG需要接3.

2010-03-17 09:25:56 2554

2554

基于JTAG仿真器的調試是目前ARM開發中采用最多的一種方式。大多數ARM設計采用了片上JTAG接口,并將其作為測試、調試方法的重要組成。

JTAG仿真器通過ARM芯片的JTAG邊界掃描

2010-06-30 15:20:03 3001

3001

本內容提供了ARM JTAG調試頭和Altera下載線合并電路 詳細列舉了電路原理圖

2011-03-31 17:19:22 209

209 隨著 FPGA 的設計速度、尺寸和復雜度明顯增長,使得整個設計流程中的實時驗證和調試成為當前FPGA 系統的關鍵部分。獲得FPGA 內部信號有限、FPGA 封裝和印刷電路板(PCB)電氣噪聲,這一

2011-06-10 15:42:28 28

28 ARM處理器采用一種基于JTAG的ARM的內核調試通道,它具有典型的ICE功能,基于ARM的包含有Embedded ICE(嵌入式在線仿真器)模塊的系統芯片通過JTAG端口與主計算機連接。

2011-08-16 09:51:08 2370

2370

這篇文章主要介紹ARM JTAG調試的基本原理。基本的內容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介紹,在此基礎上,結合ARM7TDMI詳細介紹了的JTAG調試原理。 這篇文章主要是總結了

2011-11-15 17:35:39 0

0 Altera JTAG下載和調試接口電路圖如下圖所示:

2012-08-15 14:25:22 13966

13966

電子發燒友網站提供《H-JTAG調試軟件下載.exe》資料免費下載

2012-12-18 13:15:34 57

57 在調試FPGA電路時要遵循必須的原則和技巧,才能降低調試時間,防止誤操作損壞電路。通常情況下,參考以下步驟執行 FPGA硬件系統的調試。 1、在焊接硬件電路前,首先要測試電路板

2013-01-16 11:59:58 4665

4665 基于FPGA的慣性平臺測試保護電路設計..

2016-01-04 17:03:55 7

7 IAR+H_JTAG調試FLASH說明及例程。

2016-02-18 15:11:44 4

4 ARM JTAG 調試原理對于了解jtag結構由很好的幫助。

2016-03-10 14:08:48 10

10 H-JTAG 用戶使用手冊簡單介紹了 H-JTAG 和 H-FLASHER 的基本使用和配置,手冊同時也提供了一

些簡單的例子供用戶參考

2016-05-03 15:15:08 6

6 電路設計[FPGA]設計經驗,有需要的下來看看

2016-05-20 11:16:35 46

46 基于FPGA的串口通信電路設計

2017-01-24 17:30:13 33

33 的橋接的,難道FPGA內部有專用的電路去實現這一功能嗎? 其實不是的。FPGA內部并沒有設計(預留)專用的電路去實現JTAG到Flash的轉換,在我們通過JTAG燒寫Flash時,電腦其實是先要預下載

2017-02-08 02:40:11 6513

6513

DSP和FPGA的HDLC協議通訊電路設計

2017-10-19 14:46:11 7

7 , FPGA)進行遠端升級,本文提出了一種基于XVC (Xilinx visual cable)協議,通過以太網,利用ARM 微控制器控制FPGA 的JTAG 接口對其進行遠程更新與調試的方法。該方案附加電路少,易于拓展,同時也提高了更新可靠性。

2017-11-16 20:13:02 12514

12514

JTAG(JointTestActionGroup,聯合測試行動小組)是一種國際標準測試協議,主要用于芯片內部測試及對系統進行仿真、調試,JTAG技術是一種嵌入式調試技術,它在芯片內部封裝了專門

2018-01-11 09:45:50 28818

28818

為了能夠實現HPS與FPGA之間的通信接口,衍生出了AXI bridge協議。AXI bridge協議能夠處理帶寬適應和時鐘控制,支持HPS與FPGA之間雙向的邏輯和數據交互。

2018-05-02 17:30:00 6627

6627

如何在預加載器中調試HPS SDRAM

2018-06-20 00:44:00 3023

3023

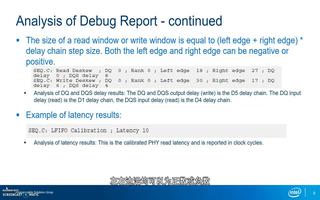

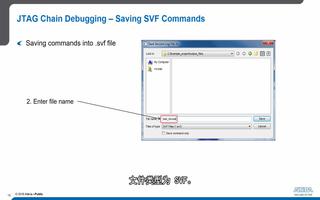

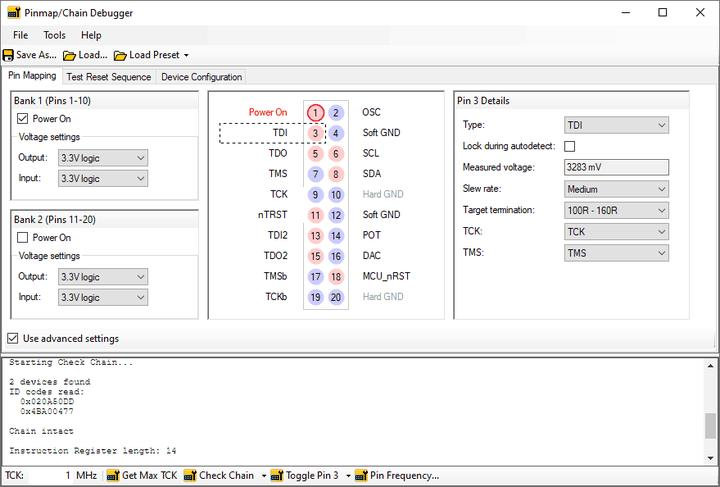

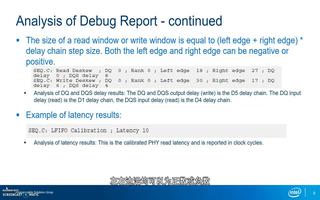

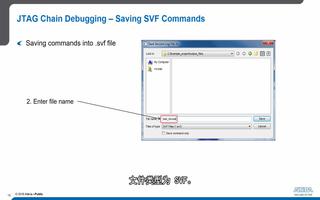

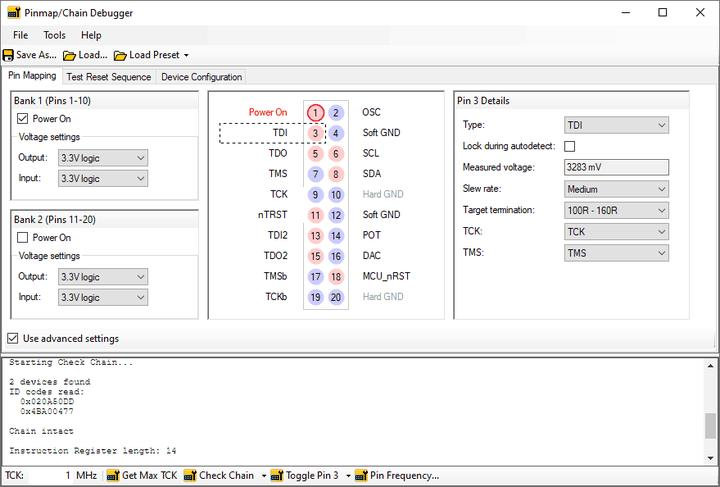

JTAG 鏈調試程序工具

2018-06-20 01:00:00 3687

3687

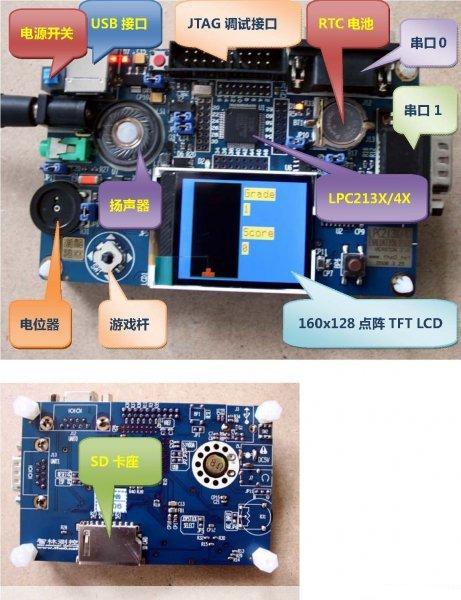

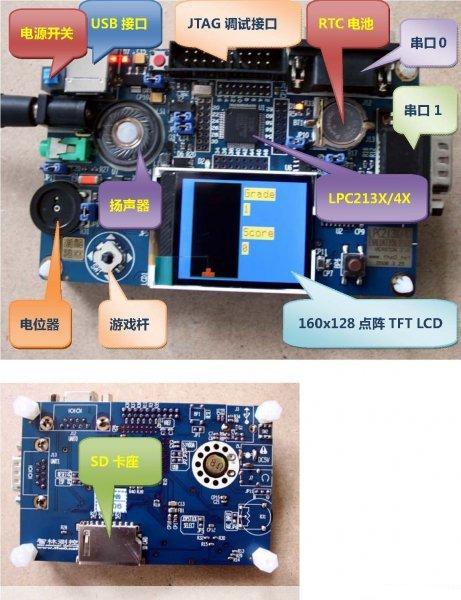

本文檔的主要內容詳細介紹的是FPGA教程之FPGA硬件最小系統設計的詳細資料說明包括了:1.FPGA最小系統概念以及硬件系統的構成,2.FPGA主芯片電路設計,3.JTAG下載與調試接口,4.高速

2019-04-04 17:18:48 101

101 中國大學MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-08-06 06:08:00 3083

3083 產品名稱:Jtag調試小板

2019-11-13 09:53:10 2071

2071

對Xilinx ZYNQ-SOC處理器的調試。JTAG-HS3可通過Xilinx 2x7連接器鏈接到目標板上,同時該產品所有的Xilinx開發工具,包括iMPACT?,ChipScope?和EDK。

2019-11-13 17:12:33 5009

5009

本文檔的主要內容詳細介紹的是FPGA的硬件電路設計教程和FPGA平臺資料簡介包括了:FPGA技術概述;主流FPGA器件介紹;VIRTEX-5 FPGA電路設計;V4LX160 FPGA平臺介紹;

2020-07-06 18:11:22 158

158 JTAG是Joint Test Action Group的縮寫,是IEEE 1149.1標準。使用JTAG的優點:JTAG的建立使得集成電路固定在PCB上,只通過邊界掃描便可以被測試。

2020-08-27 14:18:48 2860

2860 本文檔的主要內容詳細介紹的是FPGA JTAG工具設計的教程說明。

2020-12-31 17:30:55 18

18 賽靈思公司的FPGA芯片具有IEEE 1149.1/1532協議所規定的JTAG接口,只要FPGA上電,不論模式選擇管腳M[1:0] 的電平,都可用采用該配置模式。JTAG模式不需要額外的掉電

2020-12-31 17:30:55 13

13 開發板(在本文中將其簡稱為“FPGA開發板”)和專用 JTAG 調試器(在本文中將其簡稱為“JTAG 調試器”)。

2021-03-23 10:00:28 41

41 利用FPGA的在系統下載或重新配置功能,可以在電路設計和調試時改變整個電路的硬件邏輯關系,而不需要改變印制電路板的結構。

2021-05-12 10:46:10 25

25 FPGA CPLD數字電路設計經驗分享.(電源技術發展怎么樣)-FPGA CPLD數字電路設計經驗分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51 使用Jtag Master調試FPGA程序時用到tcl語言,通過編寫tcl腳本,可以實現對FPGA的讀寫,為調試FPGA程序帶來極大的便利,下面對FPGA調試過程中常用的tcl語法進行介紹,并通過tcl讀FIFO的例子,說明tcl在實際工程中的應用。

2022-02-19 19:44:34 2272

2272 對FPGA進行上板調試時,使用最多的是SignalTap,但SignalTap主要用來抓取信號時序,當需要發送信號到FPGA時,Jtag Master可以發揮很好的作用,可以通過Jtag Master對FPGA進行讀寫測試

2022-02-16 16:21:36 1900

1900

實用電子電路設計與調試數字電路教材資料免費下載。

2022-04-07 14:46:38 26

26 JTAG鏈調試器(JTAG Chain Debugger),隨XJTAG的安裝包一起安裝,是一個功能強大的工具,旨在幫助您解決JTAG鏈的問題。

2023-07-19 14:41:07 319

319

因為目前軟件的限制,RISCV的邏輯不能同時共用JTAG,所以如果想要同時去調試邏輯和RISCV的話,可以通過RISCV的soft Jtag來實現。soft Jtag就是通過GPIO來實現的軟件

2024-02-23 16:16:12 110

110

電子發燒友App

電子發燒友App

評論