FPGA在嵌入式測試系統(tǒng)中的優(yōu)勢是什么?FPGA在嵌入式測試系統(tǒng)中的不足是什么?

2021-05-06 07:19:22

gdb對嵌入式軟件的調(diào)試模式有哪幾種?在VIM中如何實現(xiàn)對嵌入式軟件的調(diào)試?

2021-04-27 06:04:38

和實時系統(tǒng)的關(guān)鍵特性,并探討在選擇或開發(fā)硬件和軟件組件的基礎(chǔ)上開發(fā)高效嵌入式系統(tǒng)的解決方案,同時詳細說明嵌入式系統(tǒng)和實時系統(tǒng)開發(fā)所特有的關(guān)鍵工藝技術(shù)。

2019-07-11 07:53:14

和實時系統(tǒng)的關(guān)鍵特性,并探討在選擇或開發(fā)硬件和軟件組件的基礎(chǔ)上開發(fā)高效嵌入式系統(tǒng)的解決方案,同時詳細說明嵌入式系統(tǒng)和實時系統(tǒng)開發(fā)所特有的關(guān)鍵工藝技術(shù)。

2019-08-23 06:45:41

嵌入式系統(tǒng)固件的開發(fā)與調(diào)試主要學(xué)習(xí)? ? 嵌入式系統(tǒng)的質(zhì)量屬性(quality attributes)? ? 嵌入式系統(tǒng)的設(shè)計與開發(fā)? ? 嵌入式系統(tǒng)的類型? ? 嵌入式系統(tǒng)中的時間管理與調(diào)度

2021-12-14 07:26:04

。2.專用性強。嵌入式系統(tǒng)的個性化很強,其中的軟件系統(tǒng)和硬件的結(jié)合非常緊密,一般要針對硬件進行系統(tǒng)的移植,即使在同一品牌、同一系列的產(chǎn)品中也需要根據(jù)系統(tǒng)硬件的變化和增減不斷進行修改。同時針對不同的任務(wù)

2016-04-23 14:18:59

嵌入式系統(tǒng)和組件技術(shù)嵌入式系統(tǒng)組件的設(shè)計原則面向嵌入式組件的系統(tǒng)開發(fā)過程

2021-04-23 06:08:06

本文通過對uclinux和eCos的對比,分析和總結(jié)了嵌入式操作系統(tǒng)應(yīng)用中的若干重要問題,歸納出嵌入式系統(tǒng)開發(fā)中操作系統(tǒng)的選型依據(jù)。

2021-04-25 07:50:01

嵌入式開發(fā)板中有幾大類接口呢?嵌入式系統(tǒng)開發(fā)中的串行接口有何作用?嵌入式系統(tǒng)開發(fā)中的USB接口有何作用?

2021-12-27 07:57:15

嵌入式系統(tǒng)開發(fā)上期回顧嵌入式系統(tǒng)開發(fā)工具(一)文件編程Linux文件(二)進程線程編程(三)TCP/UDP上期回顧嵌入式系統(tǒng)開發(fā)小白學(xué)習(xí)筆記(10)嵌入式系統(tǒng)開發(fā)工具(一)文件編程Linux文件(1

2021-12-22 06:37:50

嵌入式系統(tǒng)開發(fā)流程有沒有可以提升可靠性的技巧 ?

2021-03-06 08:18:45

嵌入式系統(tǒng)開發(fā)環(huán)境主要包括:集成開發(fā)工具交叉編譯器批處理文件makefileLink Script調(diào)試工具下載工具其它工具(Offline Tools)模擬器版本控制工具接下來分別講解以上各個工具

2021-11-08 06:09:02

# 嵌入式系統(tǒng)開發(fā)的基礎(chǔ)知識(2)版權(quán)聲明:未經(jīng)博主允許,所有轉(zhuǎn)載皆算侵。 準(zhǔn)備結(jié)合“全國計算機等級考試三級嵌入式系統(tǒng)開發(fā)技術(shù)考試大綱”,將各部分內(nèi)容進行簡單的匯總,供大家進行閱讀,尤其針對要進行

2021-12-22 06:13:49

一、嵌入式系統(tǒng)開發(fā)的基礎(chǔ)知識1.嵌入式系統(tǒng)的特點、分類、發(fā)展與應(yīng)用,熟悉嵌入式系統(tǒng)的邏輯組成。(1)特點:專用性隱蔽性(嵌入式系統(tǒng)是被包裝在內(nèi)部)資源受限(要求小型化、輕型化、低功耗及低成本,因此

2021-09-09 06:50:15

些是任何仿真器都無法再現(xiàn)的。 3、嵌入式系統(tǒng)開發(fā)工具的差異 目前嵌入式系統(tǒng)應(yīng)用開發(fā)工具種類繁多,彼此之間有很多不同。在開發(fā)產(chǎn)品之前,不僅要考慮所使用的嵌入式操作系統(tǒng)的性能,還要考慮開發(fā)工具的性能

2017-06-25 09:47:45

些是任何仿真器都無法再現(xiàn)的。 3、嵌入式系統(tǒng)開發(fā)工具的差異 目前嵌入式系統(tǒng)應(yīng)用開發(fā)工具種類繁多,彼此之間有很多不同。在開發(fā)產(chǎn)品之前,不僅要考慮所使用的嵌入式操作系統(tǒng)的性能,還要考慮開發(fā)工具的性能和開發(fā)人員過去使用的平臺。協(xié)調(diào)開發(fā)小組人員使用平臺間的差異,就可能需要很長時間。

2017-06-18 10:33:54

本文詳細闡述了在嵌入式系統(tǒng)開發(fā)中嵌入式處理器、嵌入式操作系統(tǒng)、調(diào)試器、仿真器以及開發(fā)人員的技術(shù)水平和結(jié)構(gòu)比例等組成要素的選擇原則,并且使用一個具體的實例來進一步分析說明。

2021-04-28 06:26:47

/S架構(gòu)網(wǎng)絡(luò)通信系統(tǒng)的設(shè)計,熟悉HTML,Javascript等Web編程技術(shù)及實現(xiàn)方法。 五:數(shù)據(jù)結(jié)構(gòu)與算法 數(shù)據(jù)結(jié)構(gòu)及算法在嵌入式底層驅(qū)動、通信協(xié)議、及各種引擎開發(fā)中會得到大量應(yīng)用,對其掌握

2016-08-25 15:38:09

嵌入式Linux系統(tǒng)開發(fā)學(xué)習(xí)步驟 嵌入式Linux系統(tǒng)開發(fā)學(xué)習(xí)步驟。 最近在嵌入式論壇上經(jīng)常遇到一些嵌入式linux初學(xué)者在詢問:嵌入式Linux如何入門?嵌入式Linux開發(fā)都需要學(xué)習(xí)什么?等等

2017-08-13 16:04:09

對Linux應(yīng)用開發(fā)的理解和代碼調(diào)試的能力。 四:Linux網(wǎng)絡(luò)編程 計算機網(wǎng)絡(luò)在嵌入式Linux系統(tǒng)應(yīng)用開發(fā)過程中使用非常廣泛,通過Linux網(wǎng)絡(luò)發(fā)展、TCP/IP協(xié)議、socket編程、TCP網(wǎng)絡(luò)

2017-06-18 10:31:50

訪問控制等重要知識,主要提升對Linux應(yīng)用開發(fā)的理解和代碼調(diào)試的能力。 四:Linux網(wǎng)絡(luò)編程 計算機網(wǎng)絡(luò)在嵌入式Linux系統(tǒng)應(yīng)用開發(fā)過程中使用非常廣泛,通過Linux網(wǎng)絡(luò)發(fā)展、TCP/IP

2015-11-25 17:23:50

書可以幫助具備計算機基礎(chǔ)知識的開發(fā)者迅速進入嵌入式系統(tǒng)開發(fā)領(lǐng)域。希望本書能夠幫助讀者更好地理解嵌入式 Linux 系統(tǒng),并且參與到嵌入式 Linux 系統(tǒng)開發(fā)中來。主要內(nèi)容本書以嵌入式 Linux

2017-02-25 20:47:26

本文主要介紹了嵌入式Linux系統(tǒng)開發(fā)教程及案例分析。

2018-10-16 15:52:12

開發(fā)人員 應(yīng)用程序開發(fā)人員的工作是在嵌入式系統(tǒng)開發(fā)平臺上,編寫應(yīng)用程序。這類人員是嵌入式系統(tǒng)應(yīng)用開發(fā)的主力。產(chǎn)品的設(shè)計和功能的實現(xiàn)都是由他們來完成的。他們常常困惑于不知如何使產(chǎn)品有新的創(chuàng)意,而不是如何去

2017-06-23 11:04:42

開發(fā)人員 應(yīng)用程序開發(fā)人員的工作是在嵌入式系統(tǒng)開發(fā)平臺上,編寫應(yīng)用程序。這類人員是嵌入式系統(tǒng)應(yīng)用開發(fā)的主力。產(chǎn)品的設(shè)計和功能的實現(xiàn)都是由他們來完成的。他們常常困惑于不知如何使產(chǎn)品有新的創(chuàng)意,而不是如何去

2017-07-03 18:46:52

;這些都是對嵌入式系統(tǒng)研發(fā)人員的最高要求。 2、編程能力 對嵌入式系統(tǒng)開發(fā)人員的基本要求是掌握匯編語言、C或C++語言和Java語言。要和硬件打交道,匯編語言和C語言是必須掌握的。在程序調(diào)試過程中也

2017-06-15 13:10:44

都是對嵌入式系統(tǒng)研發(fā)人員的最高要求。 2、編程能力 對嵌入式系統(tǒng)開發(fā)人員的基本要求是掌握匯編語言、C或C++語言和Java語言。要和硬件打交道,匯編語言和C語言是必須掌握的。在程序調(diào)試過程中也一樣會

2017-06-23 10:44:58

、ACK/NACK、Data及Stop以圖塊方式顯示于軟件中進行解碼。使用孕龍邏輯分析儀可針對嵌入式系統(tǒng)中的接腳進行測量,以確保每一個元件的動作正常。另外搭配特殊總線模組更能夠針對總線進行解碼,方便工程師在

2010-04-26 14:31:15

孕龍PC-Based邏輯分析儀是基于PC機使用的、專門分析IC數(shù)字信號的便攜式邏輯分析儀,相對于臺式邏輯分析儀和示波器而,基于PC機的PC-Based邏輯分析儀更由于其價格低、分析全面、分析能力強等

2015-08-05 17:30:06

嵌入式開發(fā)板開發(fā)流程有哪些呢?SOC系統(tǒng)開發(fā)流程有哪些呢?嵌入式開發(fā)板開發(fā)與SOC系統(tǒng)開發(fā)有哪些不同之處呢?

2021-12-27 07:55:18

分析儀在嵌入式系統(tǒng)的研發(fā)過程量測當(dāng)中,是占有極大的關(guān)鍵地位,但是在目前市場整個產(chǎn)品研發(fā)當(dāng)中,示波器和邏輯分析儀其實是要相輔相成的,如此在產(chǎn)品的研發(fā)時間才會更加快速,也才會更加縮短產(chǎn)品的上市時間,進而為公司

2015-08-06 13:49:11

主要用來測試以微處理器為核心的數(shù)字系統(tǒng),在硬件電路、嵌入式系統(tǒng)和監(jiān)控軟件的研制和調(diào)試過程中,都是一個必備的優(yōu)秀工具。邏輯分析儀具有豐富的觸發(fā)條件,不管被測系統(tǒng)多么復(fù)雜,邏輯分析儀都能準(zhǔn)確地找到那些隱蔽

2017-08-07 10:27:22

發(fā)生了“什么”事件。定時分析通常用波形顯示數(shù)據(jù),狀態(tài)分析通常用列表顯示數(shù)據(jù)。小結(jié)邏輯分析儀主要用來測試以微處理器為核心的數(shù)字系統(tǒng),在硬件電路、嵌入式系統(tǒng)和監(jiān)控軟件

2017-08-18 10:06:38

了邏輯分析儀在EDA教學(xué)中的應(yīng)用,通過OLA2032B邏輯分析儀調(diào)試基于FPGA的LCD顯示控制設(shè)計方案的實驗。在測試的過程中,我們可以發(fā)現(xiàn)邏輯分析儀在基礎(chǔ)教學(xué)中起著很重要的作用,比示波器更適合調(diào)試

2017-10-19 09:07:43

`編輯推薦 Linux是一個成熟而穩(wěn)定的開放源代碼操作系統(tǒng),將Linux植入嵌入式設(shè)備具有眾多的優(yōu)點。 《ARM嵌入式Linux系統(tǒng)開發(fā)從入門到精通》通俗易懂,可作為高等院校電子類、電氣類、控制

2017-10-31 13:36:35

大量讀者好評的“Linux典藏大系”中的《ARM嵌入式Linux系統(tǒng)開發(fā)詳解》的第2版。《Linux典藏大系:ARM嵌入式Linux系統(tǒng)開發(fā)詳解(第2版)》由淺入深,全面、系統(tǒng)地介紹了基于ARM

2018-09-14 08:57:17

ELA-500嵌入式邏輯分析儀是用于調(diào)試硬件相關(guān)問題的組件。

調(diào)試信號從正在調(diào)試的IP連接到ELA-500,ELA-500將信號與目標(biāo)值進行比較并驅(qū)動操作。有一個可選的跟蹤功能,可用于在任何時間點生成調(diào)試信號的歷史記錄。

2023-08-02 08:30:37

ELA-600嵌入式邏輯分析儀是用于調(diào)試硬件相關(guān)問題的組件。

調(diào)試信號從被調(diào)試的IP連接到ELA-600,ELA-600將信號與目標(biāo)值進行比較并驅(qū)動操作。有一個可選的跟蹤功能,可用于在任何時間點生成調(diào)試信號的歷史記錄。

ELA-600可以被配置為跟蹤到集成SRAM或通過ATBv4接口。

2023-08-02 10:22:10

如何用Python語言去控制單片機呢?Python在實時嵌入式系統(tǒng)開發(fā)中有何作用?

2021-11-10 06:42:48

TLA系列邏輯分析儀說明書應(yīng)用:硬件調(diào)試和校驗處理器/總線高度和校驗嵌入式軟件集成,調(diào)試和校驗[hide]TLA系列邏輯分析儀說明書.pdf[/hide] [此貼子已經(jīng)被作者于2009-12-14 11:47:42編輯過]

2009-12-14 11:47:03

本帖最后由 eehome 于 2013-1-5 09:46 編輯

arm9 s3c2440 嵌入式系統(tǒng)開發(fā):www.quickembed.com在尋找嵌入式系統(tǒng)整體解決方案嗎?需要專業(yè)

2012-04-17 15:28:29

arm嵌入式系統(tǒng)開發(fā)

2018-05-09 09:59:15

、圖表2所示;另一種就是利用嵌入式邏輯分析儀,在設(shè)計中插入邏輯分析儀,利用JTAG邊緣數(shù)據(jù)掃描和開發(fā)工具完成數(shù)據(jù)交互。嵌入式邏輯分析儀的原理相當(dāng)與在FPGA中開辟一個環(huán)形存儲器,如圖表3、圖表4,存儲器

2019-12-04 10:30:42

AES有哪些應(yīng)用實例?嵌入式邏輯分析儀是如何加速SoPC設(shè)計的?

2021-04-26 06:40:55

交叉開發(fā)嵌入式系統(tǒng)開發(fā)不同于通用PC系統(tǒng)的開發(fā)。通用PC系統(tǒng)擁有強勁的處理器、充裕的內(nèi)存和硬盤,且有鼠標(biāo)鍵盤輸入,顯示屏查看,是理想的開發(fā)載體,因此PC程序也就直接在PC上開發(fā)。而嵌入式系統(tǒng)往往資源

2021-08-11 08:12:57

使用泰克混合信號示波器 調(diào)試混合信號嵌入式設(shè)計使用泰克混合信號示波器調(diào)試混合信號嵌入式設(shè)計引言當(dāng)前的嵌入式設(shè)計工程師面臨著系統(tǒng)復(fù)雜程度日益提高的挑戰(zhàn)。典型的嵌入式設(shè)計可能會包括各種模擬信號、高速

2008-11-26 09:56:14

了邏輯分析儀的成本且便于攜帶。重點闡述硬件電路部分的設(shè)計。關(guān)鍵詞 邏輯分析儀;USB接口;FPGA;FIFO傳輸邏輯分析儀是數(shù)字設(shè)計驗證與調(diào)試過程中應(yīng)用廣泛的工具,其能夠檢驗數(shù)字電路是否正常工作,并幫助

2019-06-18 07:56:45

系統(tǒng)開發(fā)工程師是嵌入式工程領(lǐng)域的專家,既需要有一定的嵌入式軟件開發(fā)經(jīng)驗又需要嵌入式硬件開發(fā)經(jīng)驗,熟悉ARM或其他微處理器架構(gòu)或可編程邏輯器件的使用等,當(dāng)然還要有軟件項目的一般開發(fā)流程經(jīng)驗。 二:工作

2021-09-09 10:43:19

程序執(zhí)行的實時性、 可靠性,并減少開發(fā)時間,保障軟件質(zhì)量。 6.嵌入式系統(tǒng)開發(fā)需要開發(fā)工具和環(huán)境。 由于其本身不具備自舉開發(fā)能力, 即使設(shè)計完成以后用戶通常也是不能對其中的程序功能進行修改的,必須有

2017-07-07 09:44:22

市場預(yù)測機構(gòu)EMF在對900多名嵌入式系統(tǒng)開發(fā)人員進行調(diào)研后指出,超過50%的嵌入式設(shè)計比預(yù)期時間晚上市,而平均延遲高達4個月;在已發(fā)布的產(chǎn)品中,有近30%的設(shè)計未達到預(yù)期的功能和指標(biāo)。由此可見,隨著嵌入式

2019-05-14 06:12:38

標(biāo)準(zhǔn)化,而且將UML分析建模的構(gòu)建方法和相應(yīng)的集成和測試策略結(jié)合在一起,完全可以實現(xiàn)系統(tǒng)分析、設(shè)計和制作、測試分別由不同的項目成員在統(tǒng)一、一貫的方式下完成,這將會使高質(zhì)量的嵌入式系統(tǒng)的開發(fā)變得更為容易.

2019-07-18 07:47:42

我們在進行嵌入式系統(tǒng)開發(fā)調(diào)試時,受限于嵌入式芯片資源和性能,一般采用遠程調(diào)試。在調(diào)試嵌入式底層代碼時,gdbserver 無法運行,我們該怎么調(diào)試底層代碼呢?J-LINK、ST-LINK

2021-12-17 06:32:49

邏輯分析儀探頭的負荷模型請問如何使用邏輯分析儀來探測高速數(shù)字系統(tǒng)?

2021-04-13 06:03:19

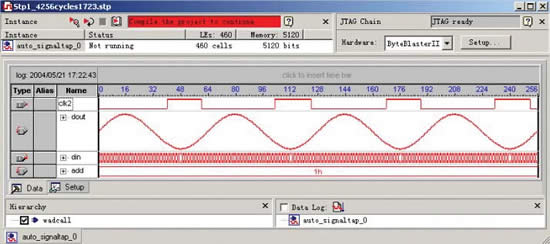

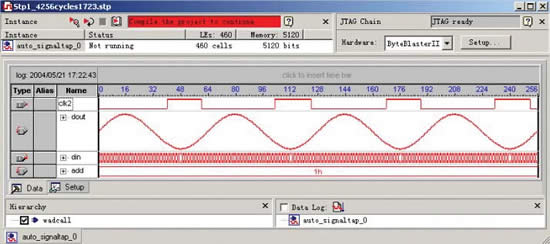

本文將介紹SignalTap II邏輯分析儀的主要特點和使用流程,并以一個實例介紹該分析儀具體的操作方法和步驟。

2021-04-29 06:12:52

復(fù)雜高速嵌入式系統(tǒng)的設(shè)計、開發(fā)、測試和調(diào)試面臨著新的挑戰(zhàn),如何利用最新的邏輯分析儀功能解決這些棘手問題?

2021-04-14 06:00:07

如何對嵌入式系統(tǒng)開發(fā)板進行配置呢?如何在嵌入式系統(tǒng)開發(fā)板中安裝SSH服務(wù)呢?

2021-12-27 07:43:30

推動FPGA調(diào)試技術(shù)改變的原因是什么外部邏輯分析儀受到的限制是什么如何用內(nèi)部邏輯分析儀調(diào)試FPGA

2021-04-30 06:44:08

在日益激烈的競爭中,系統(tǒng)的開發(fā)周期顯得尤為重要,但開發(fā)時間與系統(tǒng)安全性、可靠性又有一定沖突,如果仍然使用傳統(tǒng)的編寫代碼的模式,顯然有些不妥。本文介紹一種基于Matlab/RTW實現(xiàn)實時仿真與嵌入式系統(tǒng)開發(fā)的方法。方法所涉及的開發(fā)環(huán)境如下:

2020-03-06 07:20:36

ARM CoreSight ELA-600嵌入式邏輯分析儀提供對ARM IP和第三方IP的低電平信號可見性。

當(dāng)與處理器一起使用時,它提供對加載、存儲、推測性獲取、緩存活動和事務(wù)生命周期的可見

2023-08-12 06:51:59

`單片機開發(fā)工程師和電子愛好者,每天都要和各種各樣的數(shù)字電路打交道。在制作調(diào)試電路時除了使用萬用表、示波器等工具,邏輯分析儀也是必不可少的。 邏輯分析儀是利用時鐘從測試設(shè)備上采集和顯示數(shù)字信號的儀器

2012-03-22 13:35:46

一、常見的ARM嵌入式系統(tǒng)開發(fā)環(huán)境配置:1、編譯器/匯編器2、指令系統(tǒng)模擬器3、在線仿真器或調(diào)試探測器4、目標(biāo)開發(fā)板5、跟蹤捕捉儀6、嵌入式操作系統(tǒng)ARM嵌入式系統(tǒng)C編譯器:ARM公司,keil公司

2021-10-27 08:06:17

什么是uCLinux嵌入式系統(tǒng)開發(fā)環(huán)境?我們該怎么設(shè)計?

2019-08-13 07:39:19

探頭在邏輯分析儀中作用是什么?邏輯分析儀由那幾部分組成?

2021-05-07 06:57:28

常用的主流嵌入式開發(fā)技術(shù)新型嵌入式系統(tǒng)開發(fā)的模式有哪幾種

2021-04-27 06:48:05

我在ITjob培訓(xùn)網(wǎng)上找到的課程大綱,覺得作為嵌入式系統(tǒng)開發(fā)的學(xué)習(xí)步驟,按部就班地去施行和學(xué)習(xí),到不失為一種好的學(xué)習(xí)方法:)就算是作為參考也是有很好的價值的! 隨著現(xiàn)代社會信息化進程的加快,嵌入式系...

2021-12-22 07:29:37

ARM開發(fā)板(初期買2410足夠),學(xué)驅(qū)動開發(fā)啥的。學(xué)完了以后,做幾個驅(qū)動,就可以做項目了。更多資源: http://www.superedu.com.cn/xuexi/jdsp/?op321嵌入式Linux系統(tǒng)開發(fā)技術(shù)詳解--基于ARM(完整版).pdf (9.82 MB )

2020-05-12 00:59:33

`嵌入式linux系統(tǒng)開發(fā)全面解析pdf`

2017-04-17 12:12:14

求大神詳細介紹一下FPGA嵌入式系統(tǒng)開發(fā)過程中的XBD文件設(shè)計

2021-05-06 08:19:58

邏輯分析儀是常用的電子儀器之一,主要應(yīng)用于做數(shù)字電路測試,FPGA調(diào)試,CPU/DSP調(diào)試,數(shù)字IQ/IF分析,無線通信/雷達接收機測試等場合。邏輯分析儀由模塊和計算機組成(當(dāng)然還有探頭),模塊負責(zé)

2019-06-28 07:51:30

在一起。嵌入式軟件對代碼大小、運行效率、可靠性、可維護性、實時性,以及與整個系統(tǒng)的銜接、協(xié)調(diào)、同步方面都有著自身特殊的限制和要求。嵌入式系統(tǒng)開發(fā)中,最常碰到的就是定制化和調(diào)試兩大問題。為了有效地進行嵌入式系統(tǒng)開發(fā)

2011-12-08 10:12:40

深入了解邏輯分析儀入門手冊引言與許多電子測試和測量工具一樣,邏輯分析儀是一種針對特定類型問題的解決方案。它是一種通用工具,可以幫助您調(diào)試數(shù)字硬件、檢驗設(shè)計和調(diào)試嵌入式軟件。對設(shè)計數(shù)字電路的工程師來說

2009-11-19 11:40:22

電子書-嵌入式應(yīng)用系統(tǒng)開發(fā)典型實例系列(共三本)ARM嵌入式應(yīng)用系統(tǒng)開發(fā)典型實例 PDF格式DSP嵌入式應(yīng)用系統(tǒng)開發(fā)典型實例 PDG格式FPGA嵌入式應(yīng)用系統(tǒng)開發(fā)典型實例 PDF格式

2011-05-16 11:23:26

電子書分享《FPGA嵌入式應(yīng)用系統(tǒng)開發(fā)典型實例》資料來自網(wǎng)絡(luò)資源

2019-07-02 21:34:37

I2C 是嵌入式領(lǐng)域最常用的串行通信接口之一,讀寫時序較復(fù)雜,調(diào)試時常因時序問題導(dǎo)致通訊不暢。 1、示波器和邏輯分析儀測試信號波形與邏輯 調(diào)試時將示波器和邏輯分析儀的探頭同時連接MCU

2017-10-19 09:11:23

第10章 SignalTapⅡ嵌入式邏輯分析儀的使用 96頁 1.9M

2016-09-27 08:48:04

主要是用來量測數(shù)字信號的,基于嵌入式系統(tǒng)的發(fā)展前景,用邏輯分析儀來作為量測儀器肯定會比用示波器要好。另外,由于我們是做IC設(shè)計出身的,非常了解工程師們需要什么樣的邏輯分析儀。”從一開始,孕龍科技就在

2010-04-26 14:32:24

納睿達科技有限公司誠招“FPGA工程師、嵌入式系統(tǒng)開發(fā)工程師”【FPGA工程師】學(xué)歷要求:研究生 工作經(jīng)驗:不限 崗位職責(zé):1、主要從事設(shè)備產(chǎn)品中的FPGA的設(shè)計、開發(fā),按流程、規(guī)范完成所承擔(dān)

2018-01-13 14:17:35

基于LabVIEW的嵌入式瞬態(tài)記錄分析儀的軟件如何去設(shè)計?

2021-04-27 06:05:42

請問一下怎么實現(xiàn)嵌入式電網(wǎng)分析儀中雙CPU間的通信?

2021-06-03 06:10:11

從規(guī)范完善的開發(fā)周期到嚴(yán)格執(zhí)行和系統(tǒng)檢查,開發(fā)高可靠性嵌入式系統(tǒng)的技術(shù)有許多種。那么有沒有易操作且可以長久使用的嵌入式系統(tǒng)開發(fā)技巧呢?

2021-04-12 07:12:56

本文介紹了可編程邏輯器件開發(fā)工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個具體的設(shè)計實例,詳細介紹使用SignalTap II對FPGA調(diào)試的具體方法和步驟。關(guān)鍵字 : S

2009-11-01 14:49:39 45

45 介紹了大規(guī)模可編程邏輯器件開發(fā)工具Quartus II中嵌入式邏輯分析儀Signal Tap II的基本用法;并結(jié)合一個具體的應(yīng)用實例來說明了Signal Tap II在系統(tǒng)硬件調(diào)試過程中的優(yōu)點及其強大功能

2010-08-06 16:35:44 28

28 摘 要 :本文介紹了可編程邏輯器件開發(fā)工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個具體的設(shè)計實例,詳細介紹使用SignalTap II對FPGA調(diào)試的具體方

2009-06-20 10:42:18 1366

1366

使用邏輯分析儀調(diào)試時序問題

在今天的數(shù)字世界,嵌入式系統(tǒng)比以往任何時候都更為復(fù)雜。使用速度更快、功耗更低的設(shè)備和功能更強大的電路,

2009-08-26 12:09:14 1389

1389

邏輯分析儀自1973年問世以來,在短短幾十年的時間內(nèi)得到了迅速的發(fā)展。傳統(tǒng)邏輯分析儀利用芯片的引腳對信號采樣,并送到顯示部分對系統(tǒng)進行分析,但對于無引腳的封裝類型,傳統(tǒng)邏輯分析儀很難有效的監(jiān)測系統(tǒng)內(nèi)部信號。而在FPGA測試中,嵌入式邏輯分析儀(ELA

2011-03-15 14:52:53 38

38 嵌入式開發(fā)調(diào)試中,開發(fā)人員的調(diào)試手段包括斷點、觸發(fā)和跟蹤三種。在線調(diào)試器(I(、I))與邏輯分析儀(IA)協(xié)調(diào)工作,為調(diào)試新一代嵌入式處理器的開發(fā)人員提供了上述三種調(diào)試手段。

2011-11-07 15:58:09 33

33 本文主要介紹了嵌入式Linux系統(tǒng)開發(fā)教程及案例分析。

2018-06-05 12:00:00 7

7

電子發(fā)燒友App

電子發(fā)燒友App

評論