1 引言

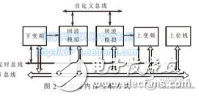

在基站的模擬測(cè)試系統(tǒng)中,終端控制子系統(tǒng)負(fù)責(zé)生成上行測(cè)試數(shù)據(jù)并將其發(fā)送到被測(cè)基帶板,測(cè)試基帶板上行接收的功能及性能;同時(shí)根據(jù)后臺(tái)控制采集下行發(fā)射的基帶數(shù)據(jù)并送后臺(tái)進(jìn)行分析,測(cè)試其發(fā)射功能。而FPGA部分屬于終端控制子系統(tǒng)的前臺(tái)部分,負(fù)責(zé)IQ數(shù)據(jù)的發(fā)送及采集,基帶測(cè)試板的功能主要在這里面實(shí)現(xiàn)。

整個(gè)系統(tǒng)的速率瓶頸在網(wǎng)口上,由于基帶數(shù)據(jù)速率很高,每根邏輯天線的數(shù)據(jù)數(shù)率達(dá)122.88Mbps,而FTP傳輸數(shù)據(jù)的速率遠(yuǎn)遠(yuǎn)不夠,故采用FPGA將高速基帶數(shù)據(jù)緩存在板上的SDRAM中,可以很好的解決速率相差很大的接口問題。同時(shí)其開發(fā)周期較短,系統(tǒng)易于維護(hù)和擴(kuò)展,無需改動(dòng)硬件設(shè)計(jì)。

2 方案技術(shù)要點(diǎn)

2.1 基帶測(cè)試板概述

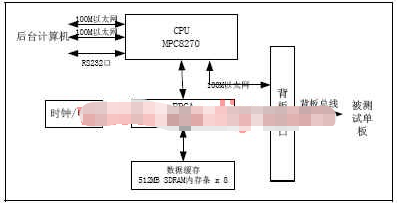

2.1.1 CPU模塊

CPU模塊是基帶測(cè)試板的控制中心,實(shí)現(xiàn):

? 和后臺(tái)計(jì)算機(jī)通訊

? 加載FPGA

? 總體控制基帶測(cè)試板的工作

CPU模塊的核心是MOTOROLA 的POWER QUICC II系列的 MPC8270處理器。CPU的60X BUS外掛:

? 16Mx64 SDRAM。

? 8Mx16 FLASH。存儲(chǔ)FPGA數(shù)據(jù)和應(yīng)用程序。

? 512Kx8 FLASH。作為BOOT ROM,存儲(chǔ)BOOT程序和VxWorks操作系統(tǒng)。

? FPGA的CPU接口。

CPU通過PHY芯片,實(shí)現(xiàn)3個(gè)以太網(wǎng)口,其中2個(gè)用來和后臺(tái)通訊一個(gè)和主控板通信。

2.1.2 FPGA模塊

FPGA模塊是基帶測(cè)試板的拓?fù)渲行墓?jié)點(diǎn),實(shí)現(xiàn):

? 將后臺(tái)生成的上行測(cè)試數(shù)據(jù)寫入SDRAM,并按CPU配置的圖樣發(fā)送到指定的發(fā)射端口。

? 根據(jù)CPU的配置,采集特定時(shí)間段的接收端口的數(shù)據(jù),完成之后通過CPU送給后臺(tái)PC進(jìn)行處理

? 和CPU模塊通訊

? SDRAM的讀寫控制

FPGA模塊的核心是1片F(xiàn)PGA芯片,主要外部接口包括:

? CPU接口。用來和MPC8270通訊。

? LVDS接口。用來和背板接口模塊的LVDS器件通訊。

? SDRAM接口。用來和數(shù)據(jù)緩存模塊的內(nèi)存條通訊。SDRAM時(shí)鐘由時(shí)鐘電源模塊提供。

? 測(cè)試用接口。

2.1.3 數(shù)據(jù)緩存模塊

數(shù)據(jù)緩存模塊由8條512MB SDRAM內(nèi)存條構(gòu)成4GB的大容量存儲(chǔ)器,用來緩存天線數(shù)據(jù)。8片內(nèi)存條的16根片選信號(hào)由FPGA分別提供;其它信號(hào),包括地址、數(shù)據(jù)、字節(jié)使能、時(shí)鐘等共用。

2.1.4 時(shí)鐘電源模塊

時(shí)鐘電源模塊為基帶測(cè)試板的其它模塊提供電源和各個(gè)時(shí)鐘信號(hào)。

? FPGA時(shí)鐘:100MHz

? MPC8270時(shí)鐘:100MHz

? 以太網(wǎng)時(shí)鐘:25MHz

3 本方案中FPGA的設(shè)計(jì)思路

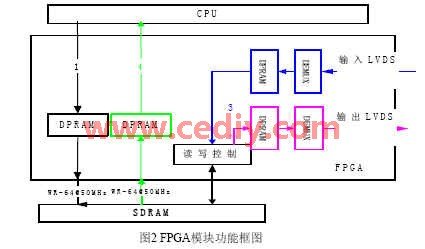

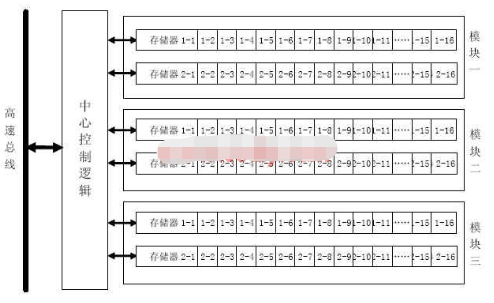

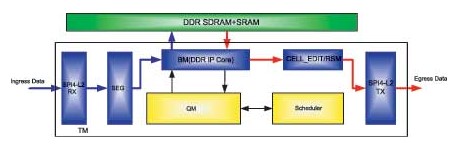

我們將整個(gè)FPGA主要分為4個(gè)大的模塊:發(fā)送處理模塊,接收處理模塊,時(shí)鐘/寄存器模塊,SDRAM控制模塊。FPGA的上下行接收模塊功能框圖如圖2:

上面的處理包括4個(gè)過程如下:

1. 將CPU寫入到DPRAM中的數(shù)據(jù)寫入SDRAM,此過程反復(fù)執(zhí)行,所有數(shù)據(jù)寫完為止;

2. 按照CPU配置的發(fā)送圖樣,連續(xù)從SDRAM相應(yīng)地址中讀取數(shù)據(jù),經(jīng)過復(fù)用后發(fā)送到發(fā)送端口;

3. 按照CPU配置將接收端口的數(shù)據(jù)進(jìn)行解復(fù)用,然后通過DPRAM將數(shù)據(jù)存入SDRAM.

4. 數(shù)據(jù)采集完成后,將緩存在SDRAM中的數(shù)據(jù)通過DPRAM上報(bào)給CPU;

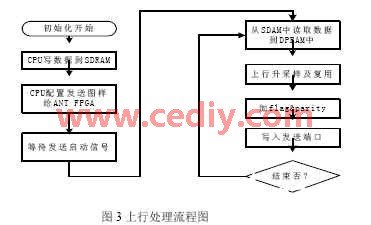

3.1 發(fā)送處理模塊

發(fā)送處理模塊主要包括上面處理過程1,2。其完整的流程如下圖3:

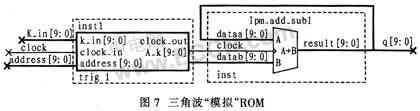

發(fā)送模塊主要處理將后臺(tái)生成的上行測(cè)試數(shù)據(jù)發(fā)射出去,送到被測(cè)基帶板,故發(fā)送處理模塊需要按照被測(cè)基帶板上行接收的格式進(jìn)行復(fù)用。上行處理過程是:先從SDRAM中讀出數(shù)據(jù)緩存在雙口RAM中,然后對(duì)其進(jìn)行升采樣(簡(jiǎn)單重復(fù))及復(fù)用操作,最后加flag和parity bit后,由原來的下行發(fā)送端口送出。在循環(huán)發(fā)送上行數(shù)據(jù)前,與CPU配合,要將后臺(tái)生成好的數(shù)據(jù)寫入SDRAM中;另,在將數(shù)據(jù)從SDRAM中讀取到DPRAM中時(shí),需要按照CPU配置的發(fā)送圖樣(即數(shù)據(jù)塊的發(fā)送順序)進(jìn)行。其中發(fā)送圖樣可以靈活配置,具體實(shí)現(xiàn)可以采用乒乓DPRAM的方法。

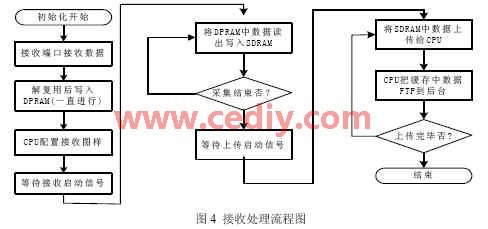

3.2 接收處理模塊

接收模塊包括處理過程3,4。圖4是采集數(shù)據(jù)上報(bào)的流程圖:

接收處理模塊完成的主要功能是根據(jù)CPU配置的數(shù)據(jù)采集范圍(若干幀),在SFN等于配置的開始SFN時(shí),將來自被測(cè)基帶板的若干幀下行發(fā)射數(shù)據(jù)采集到SDRAM中緩存;采集完成之后,再上報(bào)給CPU,最后由CPU將緩存數(shù)據(jù)上報(bào)給后臺(tái)進(jìn)行分析。

3.3 時(shí)鐘/寄存器模塊

時(shí)鐘/寄存器模塊根據(jù)輸入的16chip時(shí)鐘和從時(shí)鐘板送來的串行幀號(hào),產(chǎn)生內(nèi)部其他模塊使用各種時(shí)鐘、幀信號(hào)。板內(nèi)時(shí)鐘與16chip時(shí)鐘上升沿對(duì)齊。幀信號(hào)周期為10ms,是負(fù)脈沖,寬度為1/16chip,在1chip上升沿變化。提供寄存器接口,由CPU控制,提供告警中斷等。本模塊還根據(jù)輸入的100Mhz時(shí)鐘產(chǎn)生外接SDRAM用的時(shí)鐘。

3.4 SDRAM控制

主要根據(jù)發(fā)送采集等模塊的狀態(tài)來控制SDRAM控制器的輸出,產(chǎn)生SDRAM需要的/CS、/RAS、/CAS、/WE等各種控制信號(hào),從而對(duì)SDRAM進(jìn)行操作。

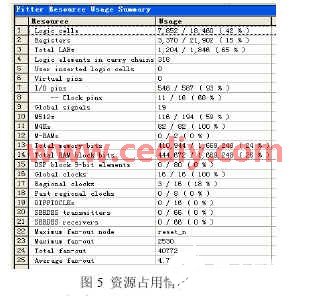

4 器件說明

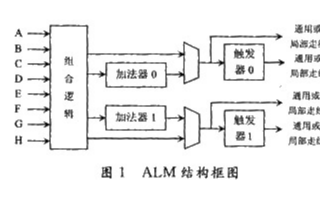

綜合考慮速度和資源,F(xiàn)PGA芯片我們選用了Altera公司Stratix系列的EP1S20F780C7。這個(gè)芯片是780Pin FineLine BGA封裝,最多可用IO587個(gè),具有邏輯單元18460個(gè),內(nèi)部有194個(gè)塊M512 RAM、82個(gè)塊M4K RAM、2個(gè)塊M4Kx144 RAM (可靈活配置為不同的數(shù)據(jù)口寬,但是容量不變)。Stratix系列內(nèi)核采用1.5V供電,IO支持1.5V/1.8V/2.5V/3.3V多種接口標(biāo)準(zhǔn),支持高速外部存儲(chǔ)器接口,包括ZBT,QDRSDRAM,DDRSDRAM,F(xiàn)CRAM和SDRAM。為了與單板其他部分配合,我們IO選用了3.3V供電。圖5顯示該芯片能夠滿足需求。

5 結(jié)論

實(shí)踐結(jié)果證明,該方案設(shè)計(jì)的基帶測(cè)試系統(tǒng)能夠同時(shí)采集和發(fā)送12個(gè)邏輯天線的數(shù)據(jù),完全能夠滿足測(cè)試的需要。

本設(shè)計(jì)充分利用了FPGA并行處理多路信號(hào)和處理高速數(shù)據(jù)的能力,通過對(duì)SDRAM的控制來實(shí)現(xiàn)速率相差很大的后臺(tái)與測(cè)試環(huán)境之間的數(shù)據(jù)交換。不失一般性,該設(shè)計(jì)的思路也可以推廣到其他測(cè)試和應(yīng)用場(chǎng)合。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論