基于FPGA和DDS的信號源設計

1 引言

直接數字頻率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽樣定理理論和現代器件生產技術發展的一種新的頻率合成技

2010-02-21 09:15:21 1833

1833

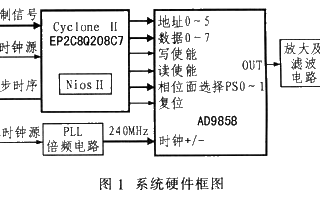

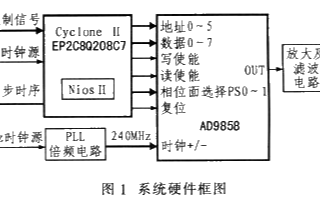

基于FPGA 芯片EP3C16Q240C8N 的片上可編程系統,該系統可用于實現IFFT運算和接口模塊,利用可嵌入到此FPGA 芯片的NiosII 軟核處理器來實現數據傳輸和控制。

2015-02-03 15:08:23 1185

1185

一般的雷達信號源實現主要有三種方式:第一種方式是采用DDS和MCU控制器件結合的方式;第二種是DDS、MCU控制器件和FPGA等可編程器件結合的方式:第三種是由FPGA等可編程器件實現DDS的方式。第一種方式利用專用DDS器件可以產生具有較好的雜散抑制和諧波抑制性能的雷達波形。

2020-07-27 08:50:28 3381

3381

一般的雷達信號源實現主要有三種方式:第一種方式是采用DDS和MCU控制器件結合的方式;第二種是DDS、MCU控制器件和FPGA等可編程器件結合的方式:第三種是由FPGA等可編程器件實現DDS的方式。第一種方式利用專用DDS器件可以產生具有較好的雜散抑制和諧波抑制性能的雷達波形。

2020-12-01 10:13:20 1323

1323

本人畢業設計初學FPGA和使用DDS,想用AD9832芯片產生一個正弦波,但是不知道DDS的芯片控制字應該怎么寫入?在網上搜到這樣一份編程示例的解釋文件,http

2017-05-18 16:12:02

DDS專用芯片與基于FPGA的DDS的區別什么地方,優勢在哪?關于DDS選型,DAC的位數影響DDS的什么性能,怎么選擇合適DAC位數?AD995X系列與AD991x系列那個相噪性能雜散好?輸出約20MHz的時鐘,希望能推薦一款相噪和雜散性能好的芯片。

2018-08-06 09:13:36

300MHz,雙路正交輸出)DDS芯片,以及兩片AD8009高速運算放大器組成(可輸出較大幅度的高速信號,放大倍數可調,Vpp最高可達10V),可以滿足用戶對于高速信號產生的要求,用戶可以借助FPGA核心模塊板

2013-01-27 19:07:26

FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現

2012-08-11 18:10:11

` 本帖最后由 明德揚吳老師 于 2020-6-15 11:27 編輯

基于FPGA的DDS信號發生器設計信號發生器是一種能提供各種頻率、輸出電平的電信號的設備,又稱信號源或振蕩器。其在各種電信

2020-06-15 11:25:38

一個LUT,一個觸發器和相關的相關邏輯。LE是FLEX/ACEX芯片實現邏輯的最基本結構(altera其他系列,如APEX的結構與此基本相同,具體請參閱數據手冊)三.查找表結構的FPGA邏輯實現原理我

2012-04-28 14:57:28

。但是,要想做個稱職的電子工程師,這點技能是必須有的,對于我們電路板上所使用到的每一顆芯片,我們都必須至少是通讀過他們的器件手冊。(特權同學,版權所有)我們的FPGA器件選擇的是Altera公司

2019-04-15 02:21:50

AD9434 LVDS 可以和FPGA EP4CGX50的LVDS端口直接連接嗎?還是要加電壓轉換芯片,EP4CGX50的BANK電壓是2.5V,而AD9434的電壓是1.8V的,謝謝,麻煩幫我解答下!

2023-12-13 09:19:23

2A15, Excalibur? EPXA1, Stratix? II EP2S15, Stratix EP1S10, Cyclone?, Cyclone II, FLEX 10K?, FLEX? 10KA, FLEX

2012-08-15 12:30:03

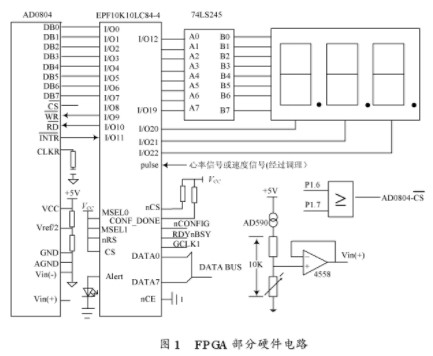

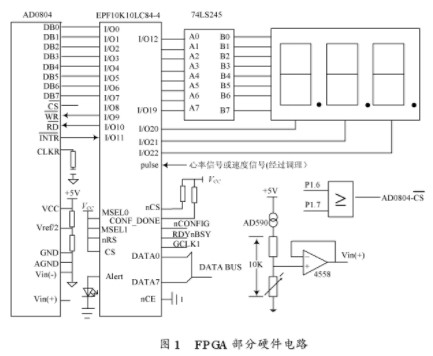

需要實現整數和半整數頻率合成;輸出頻率范圍為1KHz-999.5KHz,步進頻率為0.5KHz。FPGA芯片選用的是FLEX 10K系列的EPF10K10LC84-4,40MHz的有源晶振,LCD1602顯示小妹實在是太菜了,看了幾日還在門外徘徊,不知大神們是否有心情,求賜教~

2014-03-30 13:51:03

發生器。函數信號發生器的實現方法通常是采用分立元件或單片專用集成芯片,但其頻率不高,穩定性較差,且不易調試,開發和使用上都受到較大限制。隨著可編程邏輯器件(FPGA)的不斷發展,直接頻率合成(DDS)技術

2012-05-12 23:01:54

芯片的可編程性和實現方案易改動的特點,提出了一種基于FPGA和DDS技術的任意波形發生器設計方案。目前任意波形發生器的設計還在進行中。本文只給出實驗階段的三相正弦波的產生代碼和仿真波形,產生的并不是任意波形了。DDS設計要求:頻率分辨率

2015-05-30 10:50:36

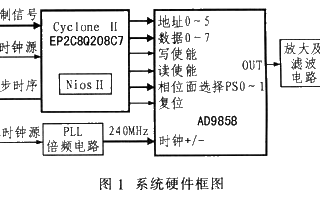

信息顯示在LCD液晶顯示屏上。各硬件模塊之間的協調工作通過嵌入式軟核處理器NiosⅡ用編程實現控制。本設計所搭建的LCD12864控制器是通過編程實現的IP核。關鍵詞:DDS;FPGA技術;順序存儲;NiosⅡ;IP核

2019-06-21 07:10:53

本文主要介紹了采用直接數字頻率合成DDS芯片實現正弦信號輸出,并完成調頻,調幅功能。它采用美國模擬器件公司(AD公司)的芯片AD9851,并用AT89C51單片機對其控制,首先從DDS芯片的輸出,經

2021-07-21 07:14:36

基于FPGA 的DDS 調頻信號的研究與實現

2012-08-17 11:41:11

),它采用數字電路合成所需波形,具有精度高、產生信號信噪性能好、頻率分辨率高、轉換速度快等優點。本文設計的掃頻信號源是基于DDS技術,并在Altera公司的EP2C20上實現邏輯綜合、布局布線、時序

2019-07-04 07:42:59

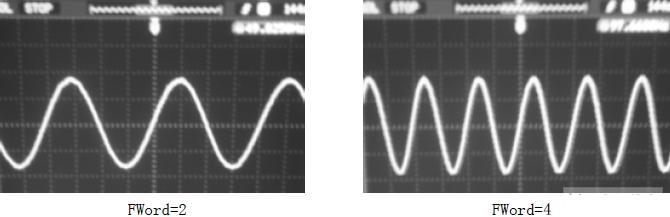

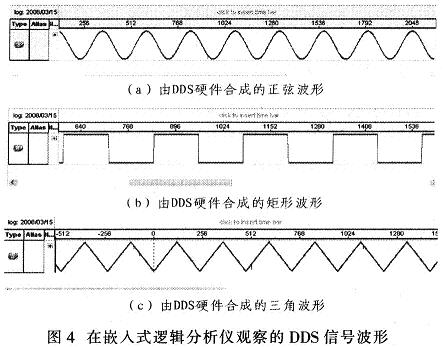

相彼此相位保持120o 的相位關系,證明輸出三相波 形的相位是正確的。在實際應用中,通過改變頻率控制字的大小就可以改變輸出頻率。本文利用FLEX10K 器件,設計了相應的三相正弦DDS 電路,對實驗

2018-10-18 16:29:13

如何利用DDS去實現任意信號波形的產生?怎樣設計信號源硬件電路?

2021-04-07 06:16:32

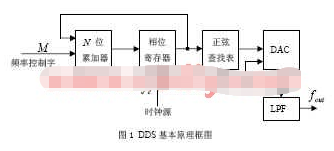

DDS電路的工作原理是什么如何利用FPGA和DDS技術實現正弦信號發生器的設計

2021-04-28 06:35:23

ACEX 1K具有什么特點DDS電路工作原理是什么如何利用FPGA設計DDS電路?

2021-04-30 06:49:37

DDS的工作原理和基本結構基于FPGA的DDS信號發生器的設計如何建立頂層模塊?

2021-04-09 06:46:42

介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進行直接數字頻率合成的VHDL源程序。

2021-04-30 06:29:00

本文主要討論使用FLEX10K系列FPGA來實現信道編碼的功能。

2021-06-07 06:00:58

如何利用FPGA實現濾波及抗干擾?怎么利用FPGA器件來設計抗干擾電路?

2021-05-08 08:01:10

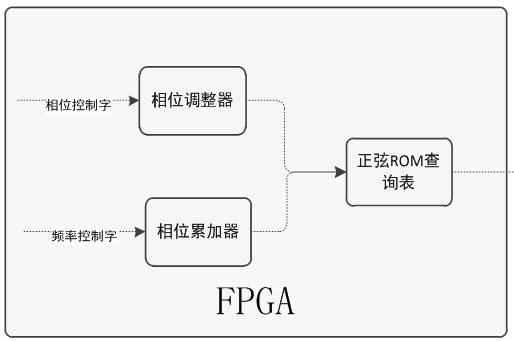

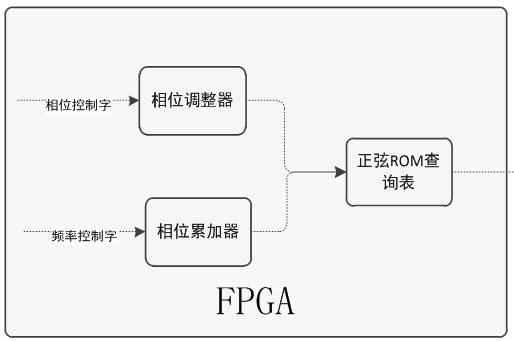

本文在討論DDS的基礎上,介紹利用FPGA設計的基于DDS的信號發生器。

2021-05-06 09:54:10

介紹了DDS的發展歷史及其兩種實現方法的特點,論述了DDS的基本原理,并提出一種基于FPGA的DDS信號發生器的設計方法,使DDS信號發生器具有調頻、調相的功能,最后對其性能進行了分析。實驗表明該系統具有設計合理、可靠性高、結構簡單等特點,具有很好的實用價值。

2021-05-11 06:58:58

用高性能的FPGA器件設計符合自己需要的DDS電路有什么好的解決辦法嗎?

2021-04-08 06:23:09

想要產生一個BPSK的調制信號,載波900MHz,基帶用FPGA產生,建議用什么DDS芯片呢?有沒有好的推薦電路呢?

2018-11-09 09:15:35

利用DDS信號產生50M~250M的線性調頻波,但是輸出雜散太大,需要濾波。請教有什么好的濾波方案。是否可以做一個帶通的濾波器,有源還是無源的好。求濾波器設計電路,謝謝

2015-11-28 10:13:28

如何利用單片機AT89C52對FLEX10K系列FPGA中的EPF10K10進行在線并行配置?

2021-04-29 06:19:03

自行設計的基于FPGA芯片的解決方案DDS技術的實現依賴于高速、高性能的數字器件。可編程邏輯器件以其速度高、規模在、可編程,以及有強大EDA軟件支持等特性,十分適合實現DDS技術。Altera是著名

2011-07-13 14:13:56

Altera FLEX/ACEX芯片結構是如何構成的?Intel XScale PXA270處理器的系統存儲器接口怎樣去設計?Linux下的ACEX1K50設備驅動是如何實現的?

2021-04-30 06:44:14

想要使用DDS芯片實現兩個或多個不同頻率(幅度相位相同)信號的混合,DDS能直接實現嗎?還是需要混頻器來實現?DDS芯片單個通道能實現兩個或多個頻率疊加嗎?DDS線性掃描的作用是?

2018-09-20 14:45:30

AD9434 LVDS 可以和FPGA EP4CGX50的LVDS端口直接連接嗎?還是要加電壓轉換芯片,EP4CGX50的BANK電壓是2.5V,而AD9434的電壓是1.8V的,謝謝,麻煩幫我解答下!

2018-08-16 07:52:40

如何通過添加一個簡單的RC電路至FPGA或CPLD 的LVDS輸入來實現模數轉換器?請問怎么實現低頻率(DC至1K Hz)和高頻率(高達50K Hz)ADC?

2021-04-15 06:29:55

不想再單獨使用模擬乘法器進行調制,可否直接使用dds進行am調制。

我希望對1k和40k進行am調制,使用mcu和一個dds實現

2023-11-16 07:53:12

西安交通大學電信學院 周俊峰 陳濤摘要:介紹了Altera公司的即FPGA器件ACEXEPlK50的主要特點,給出了由ACEXEPlK50實現直接數字頻率合成的工作原理、設計思路、電路結構和改進優化

2019-06-18 06:05:34

一般的雷達信號源實現主要有三種方式:第一種方式是采用DDS和MCU控制器件結合的方式;第二種是DDS、MCU控制器件和FPGA等可編程器件結合的方式:第三種是由FPGA等可編程器件實現DDS的方式

2020-11-24 06:39:52

基FPGA Cyclone II_EP2C5 EP2C8的頻率計

基FPGA_Cyclone_II_EP2C5/EP2C8的頻率計

功能描述:按4*4鍵盤上的1,2,3...號按鍵可依次測出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 介紹用自制小健盤(4X4)輸入所要求的榆出頻率值,用89C51單片微機控制直接數字頻率合成器DDS實現跳頻的過程、及單片橄機拉制系統的硬件結構、軟件設計和采用DDS專用芯片AD

2008-12-05 14:23:52 38

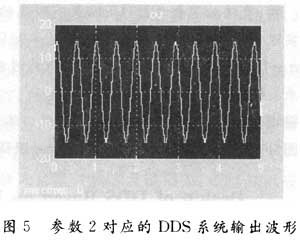

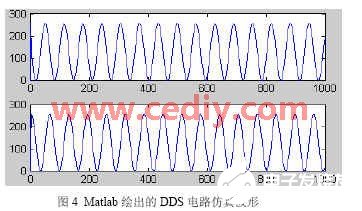

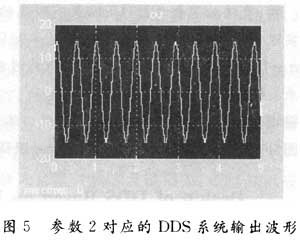

38 本文從DDS 基本原理出發,利用FPGA 來實現DDS 調頻信號的產生,重點介紹了其原理和電路設計,并給出了FPGA 設計的仿真和實驗,實驗結果表明該設計是行之有效的。直接數字頻率

2009-06-26 17:29:09 70

70 本文用FPGA 設計并實現了JTAG(即節點測試動作群)接口電路。首先介紹了JTAG 的定義和引腳的定義;闡述了JTAG 的結構,特點和工作原理;然后在Altera FLEX10K100 系列芯片上完成了硬件

2009-07-08 15:18:15 10

10 用DDS技術設計HDTV選臺電路:首先闡述了直接數字式頻率合成DDS技術的基本原理,重點介紹了DDS單片集成電路AD9852的特點與功能,并利用它設計實現了一個HDTV選臺電路。【關鍵詞】

2009-08-21 22:33:43 22

22 在介紹DDS 芯片STEL-1479 和PIC16C73A 單片機的基礎上,設計了一種利用單片機控制DDS 芯片實現的中波頻率合成器。進行了詳細的硬件和軟件設計,給出了具體的硬件電路及軟件流程。

2009-09-03 09:16:06 17

17 根據軟件無線電的思想,以FPGA 器件為核心實現了OQPSK 的解調,大部分功能由FPGA 內部資源來實現。整個設計以Altera 公司可編程邏輯芯片FLEX 10K 系列芯片為核心實現OQPSK 解調器,具有

2009-09-08 14:21:15 38

38 EP4CE10F17C8N,Cyclone IV FPGA設備,INTEL/ALTERAEP4CE10F17C8N,Cyclone IV FPGA設備,INTEL

2023-02-20 17:00:57

EP4CE10F17I7N,Cyclone IV FPGA設備,INTEL/ALTERAEP4CE10F17I7N,Cyclone IV FPGA設備,INTEL

2023-02-20 17:03:19

、Arria? GX、Cyclone?、Cyclone II、FLEX? 10K(包括FLEX 10KE和FLEX 10KA)、Mercury?、Stratix?、Stra

2023-03-07 18:54:42

提出了一種基于FPGA 實現QPSK 調制器的方法。以FPGA 實現DDS,通過對DDS 信號輸出相位的控制實現調相。仿真結果表明方案是可行的。

2009-12-18 11:57:08 66

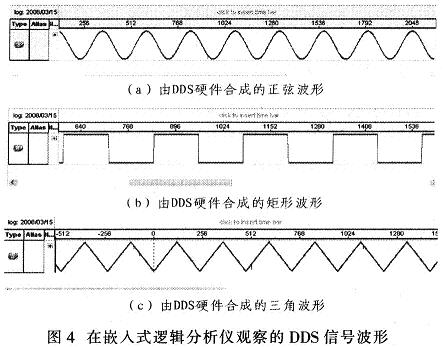

66 基于FPGA的DDS信號源設計與實現

利用DDS和 FPGA 技術設計一種信號發生器.介紹了該信號發生器的工作原理、 設計思路及實現方法.在 FPGA 器件上實現了基于 DDS技

2010-02-11 08:48:05 223

223 直接數字頻率合成是一種新的頻率合成技術,介紹了利用Altera的FPGA器件實現直接數字頻率合成器的工作原理和電路設計方法,并利用FLEX器件實現了DDS電路。

2010-08-09 15:02:25 61

61 討論了DDS 技術的基本組成結構、工作原理和特點,并給出對DDS 技術相關的頻譜雜散性改善方法,介紹了FLEX6016 器件,并詳細討論了FLEX6016器件在DDS 技術實現時具體應用中所涉

2010-08-13 17:27:31 24

24 摘 要: 本文利用FPGA完成了8路同步話音及16路異步數據的復接與分接過程,并且實現了復接前的幀同步捕獲和利用DDS對時鐘源進行分頻得到所需時鐘的過程。該設計

2009-06-20 13:38:43 565

565

摘要:介紹了利用Altera的FPGA器件(ACEX EP1K50)實現直接數字頻率合成器的工作原理、設計思想、電路結構和改進優化方法。

關鍵詞:直接數字

2009-06-20 13:53:19 603

603

摘要: 介紹了DDFS的原理和Altera公司的FPGA器件ACEX 1K的主要特點,給出了用ACEX 1K系列器件EP1K10TC144-1實現數字頻率合成器的工作原理、設計思路、電路結構和仿真結

2009-06-20 14:02:25 844

844

基于DSP Builder的DDS設計及其FPGA實現

直接數字合成器,是采用數字技術的一種新型頻率合成技術,他通過控制頻率、相位增量的步長,產生各種不同頻率的信號。他具

2010-01-14 09:43:55 1292

1292

基于模型的DDS芯片設計與實現

0 引言

1971 年,美國學者J.Tierncy.C.M.Rader 和B. Gold 應用全數字技術,從相位概念出 發給出了直接合成波形的

2010-01-20 11:23:13 1302

1302

文中提出一種基于FPGA的DDS信號發生器。信號發生電路采用直接數字頻率合成技術,即DDS(Direct Digital Frequency Synth-esis)。它是以全數字技術,從相位概念出發,直接合成所需波形的一種新的

2011-07-16 10:24:22 1678

1678

討論一種基于DSP系統,利用FPGA設計接口通過DDS芯片產生MSK調制的方法,使用該方案的硬件電路簡潔且易于實現調制器的小型化。

2012-02-09 15:14:46 11

11 首先介紹了采用直接數字頻率合成(DDS)技術的正弦信號發生器的基本原理和采用FPGA實現DDS信號發生器的基本方法,然后結合DDS的原理分析了采用DDS方法實現的正弦信號發生器的優缺點

2012-11-26 16:23:32 49

49 ,LB0 以ALTERA 公司的CycloneⅢ系列FPGA EP3C10E144C8 為核心器件,板載串行配置芯片EPCS4、 32M 的SDRAM 以及50M晶振,板上接口豐富。

2015-12-24 18:32:39 38

38 LB0 以ALTERA 公司的CycloneⅢ系列FPGA EP3C10E144C8 為核心器件,板載串行配置芯片EPCS4、 32M 的SDRAM 以及50M晶振,板上接口豐富。電路原理圖

2015-12-24 18:33:04 29

29 利用現場可編程門陣列(FPGA)設計并實現直接數字頻率合成器(DDS)。結合DDS 的結構和原理,給出系統設計方法,并推導得到參考頻率與輸出頻率間的關系。DDS 具有高穩定度,高分辨率和高轉換速度,同時利用Altera 公司FPGA 內的Nios 軟核設置和顯示輸出頻率,方便且集成度高。

2016-04-01 16:14:19 24

24 針對常規的MSK調制電路存在的不足,利用DDS原理進行 MSK調制 選用DDS專

用芯片AD9850 和DSP芯片TMS320C6711B組成調制電路,此調制電路所用元器件數較少,可與共他部分電路公用DSP芯片,繃率分辮率達到。.03Hz.試臉表明,用此調制電路能得到較德定的MSK調制波形.

2016-10-25 18:04:42 20

20 詳細介紹了直接數字頻率合成器(DDS)的工作原理、基本結構。在參考DDS 相關文獻的基礎上,提出了符合結構的DDS 設計方案,利用DDS 技術設計了一種高頻率精度的多波形信號發生器,此設計基于可編程邏輯器件FPGA,采用Max+PlusⅡ開發平臺,由Verilog_HDL 編程實現。

2016-11-22 14:35:13 0

0 頻率分辨率、對硬件要求低、可編程全數字化便于單片集 成、有利于降低成本、提高可靠性并便于生產等優點。本文根據實際需要,設計出符合特定需要的三相正弦DDS電路,通過實驗證明,利用FPGA合成DDS是一個較好的解決方法,具有良好的實用性和靈活性。

2017-11-23 11:28:45 1723

1723 )及嵌入式處理器(ARM)于單片可編程邏輯器件上,實現了RISC和FPGA的完美結合。本文使用EPXA10芯片,利用片上的ARM微處理器對MPEG-2傳輸流進行解碼,得到必要的解碼參數,實現了將傳輸流分成視頻流和音頻流的解復用。

2020-01-15 08:08:00 1872

1872

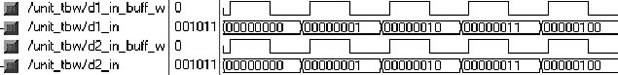

根據課題要求,設計FPGA部分硬件電路如圖1所示。FPGA芯片選用Altera公司的中檔器件FLEX-EPF10K10LC84-4,他是基于SRAM LUT結構的FPGA器件。根據傳送數據的方式

2019-08-21 08:01:00 4908

4908

在FPGA上設計一個DDS模塊,在DE0 開發板上運行,在FPGA芯片內部合成出數字波形即可。

2018-12-08 09:18:25 1923

1923

本文檔的主要內容詳細介紹的是FPGA教程之ALTERA的CPLD與FPGA器件的詳細資料說明主要內容包括了:一、Altera器件一般介紹,二、MAX 7000 系列器件,三、FLEX10K系列器件,四、邊界掃描測試

2019-02-27 17:27:31 15

15 利用ADISim DDS來仿真DDS產品的頻譜特性。

2019-07-15 06:13:00 3586

3586 本文檔的主要內容詳細介紹的是DDS的FPGA實現電路原理圖免費下載。

2020-10-22 12:07:17 26

26 本文討論了基于FPGA芯片的直接數字頻率合成器(DDS)的設計方法。因為DDS 的實現依賴于高速、高性能的數字器件,使用現場可編程器件FPGA,利用其高速、高性能及可重構性的特性,就能根據需要方便地實現各種不同頻率的信號輸出。

2021-03-02 17:11:32 35

35 論述了DDS的基本原理,給出了利用FPGA實現基于DDS的2ASK/2FSK信號發生器的設計方法,重點介紹了其原理和電路,最后給出了基于.FPGA設計的實驗結果.

2021-03-24 09:12:00 19

19 DDS基于FPGA的DDSSPI系統結構功能實現:在SPI接口下掛接上DDS模塊,通過單片機向FPGA發送頻率字實現任意頻率正弦波的波形,并通過DAC模塊輸出單片機部分通過按鍵輸入待產生的信號頻率

2021-12-01 17:36:17 9

9 Gate Array)是在PAL、GAL等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。FPGA設計不是簡單的芯片研究,主要是利用 FPGA 的模式進行其他行業產

2021-12-29 19:40:35 7

7 電子發燒友網站提供《FPGA通用板Altera EP4CE10開源.zip》資料免費下載

2022-08-09 09:29:38 32

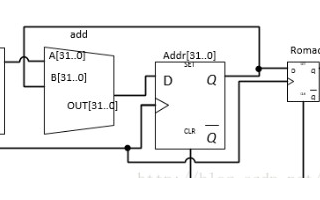

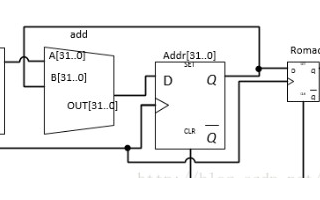

32 上圖就是DDS的的FPGA實現框圖,完整的DDS還應該在外面有DAC和低通濾波器的,然而很多時候我們是不需要這兩個的,因為上圖的DDS輸出的信號就在數字域,凡是數學域的信號都可以用它參與處理了,所以正弦ROM查找表出來后的信號可以直接給到其他的邏輯使用。

2023-06-28 10:36:48 933

933

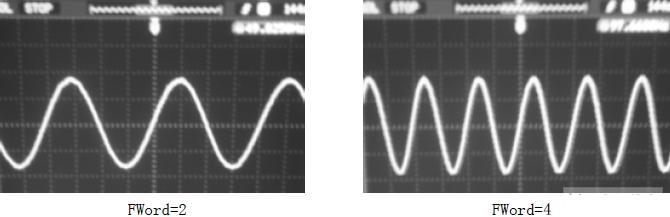

![]() 可見,通過設定相位累加器位數、頻率控制字和基準時鐘的值,就可以產生任一頻率的輸出。DDS的頻率分辨率為:

可見,通過設定相位累加器位數、頻率控制字和基準時鐘的值,就可以產生任一頻率的輸出。DDS的頻率分辨率為: ![]() 由于基準時鐘一般固定,因此相位累加器的位數就決定了頻率分辨率,位數越多,分辨率越高。

由于基準時鐘一般固定,因此相位累加器的位數就決定了頻率分辨率,位數越多,分辨率越高。![]() 直線成偶對稱,基于此可以將ROM表減少至原來的1/2,再利用左半周期內,波形對于

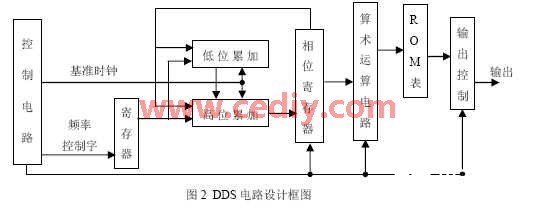

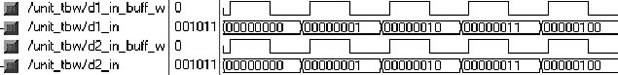

直線成偶對稱,基于此可以將ROM表減少至原來的1/2,再利用左半周期內,波形對于![]() 成奇對稱,進一步將ROM表減至最初的1/4,因此可以通過一個正弦碼表的前1/4周期就可以變換得到正弦和余弦的整個周期碼表。這樣就節省了3/4的資源。DDS電路的電路結構設計如圖2所示。

成奇對稱,進一步將ROM表減至最初的1/4,因此可以通過一個正弦碼表的前1/4周期就可以變換得到正弦和余弦的整個周期碼表。這樣就節省了3/4的資源。DDS電路的電路結構設計如圖2所示。

![]()

電子發燒友App

電子發燒友App

評論