本文介紹的FPGA一體化高級設計方法是通過發揮 FPGA 主機的可再編程功能實現的。所有應用的層和接口以及功能設計本身都自動包含在 FPGA 系統中

2011-12-20 09:57:09 794

794 51單片機里的煙霧傳感器功能設計怎么做????

2023-11-07 06:44:57

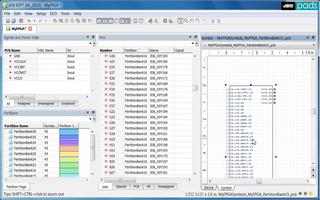

元件和符號生成由于 FPGA 器件自身的性質,因此需要不同的符號生成流程方法。在項目生命周期內,FPGA 邏輯通常要更改數次,而符號必須與這些更改保持一致。該高級 PADS 模塊功能強大,不僅可讓您輕松

2018-09-20 11:11:16

FPGA中的I_O時序優化設計在數字系統的同步接口設計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種FPGA中的IPO時序優化設計的方案, 切實有效的解決了IPO接口中的時序同步問題。

2012-08-12 11:57:59

1.FPGA功能設計上圖所示的是FPGA圖像處理基板的邏輯功能框圖,圖中左側是背板接頭,FPGA與背板接頭相連的信號主要包括8路3.125G高速數據通道、1路1.3G高速雙向數據通道、2路時鐘信號

2021-11-10 08:06:26

ATE有一定的優勢,對FPGA測試有一定的使用價值。FPGA可重復配置和測試系統結構概述系統框圖如圖1所示。圖1 可重復配置測試系統結構框圖系統功能的實現包括軟件和硬件兩部分。硬件部分包含PCI橋接

2020-05-14 07:00:00

FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般如圖1-10所示,包括電路功能設計、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后仿真

2021-07-23 09:12:07

FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現

2012-08-11 18:10:11

,不需要設計人員承擔投片風險和費用,設計人員只需在自己的實驗室里通過相關的軟硬件環境來完成芯片的最終功能設計,所以,FPGA 的資金投入小,節省了許多潛在的花費。? 用戶可以反復地編程、擦除、使用或者

2018-09-05 09:32:29

FPGA的時序優化高級研修班通知通過設立四大專題,幫助工程師更加深入理解FPGA時序,并掌握時序約束和優化的方法。1.FPGA靜態時序分析2.FPGA異步電路處理方法3.FPGA時序約束方法4.FPGA時序優化方法

2013-03-27 15:20:27

FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般如圖1-10所示,包括電路功能設計、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后

2020-11-30 16:22:59

在于把高云器件支持的所有功能和特性完美地 呈現出來。 時序收斂可以保證用戶設計滿足某個特定的時序需求,這部分主要描述 時序需求、時序約束以及時序優化的方法。

2022-09-29 06:12:02

-7所示,包括電路設計、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后仿真、板級仿真以及芯片編程與調試等主要步驟。1. 電路設計在系統設計之前,首先要進行的是方案論證、系統設計和FPGA芯片選擇等

2015-11-30 15:28:41

EDA技術具有什么特征?FPGA是什么原理?FPGA設計應用及優化策略基于VHDL的FPGA系統行為級設計

2021-04-15 06:33:58

各位大神,小弟最近在做一個項目,由于之前選用的FPGA資源不夠,現在需要將程序的資源占用率降下來。經過我的冥思苦想,也找不到好的方法,不知道各位大神平時工作中降低資源利用率的方法有哪些?求助啊!!!!

2015-04-04 00:32:57

`FPGA面積優化1.對于速度要求不是很高的情況下,我們可以把流水線設計成迭代的形式,從而重復利用FPGA功能相同的資源。2.對于控制邏輯小于共享邏輯時,控制邏輯資源可以用來復用,例如FIR濾波器

2014-12-04 13:52:40

本項目是基于FPGA設計的溫度檢測工程:該項目主要實現的功能是對溫度傳感器DS18B20的溫度值進行讀取,并且將讀取到的溫度值數據在數碼管上和PC上顯示出來。 一、硬件與架構設計本項目中用到的設備

2019-12-26 11:06:20

E— 最低的功耗,通過最低的成本實現較高的功能性■ Cyclone IV GX— 最低的功耗,集成了 3.125 Gbps 收發器的最低成本的 FPGA1 Cyclone IV E 器件可以在 1.0

2017-11-13 11:22:50

的優化變得異常復雜,如何定位性能問題出在哪個方面,是性能優化的一大難題, 從系統入手,闡述由于系統軟、硬件配置不當可能造成的性能問題,并且探討檢測系統故障和優化性能的一般方法和流程。一、CPU性能評估

2019-07-22 06:48:03

TDS筆功能原理及電解器檢測方法

2022-01-07 07:28:35

多個。器件之間一般有電路導線(引腳)連接。已知每種器件一般有多個可能發生的故障(稱為故障模式或失效模式),并且通過已有積累的測試知識,獲得了每種故障模式發生的概率、及其對應的檢測方式(即功能檢測編碼

2016-05-22 11:13:32

項目名稱:基于鋯石A4 FPGA開發板的邏輯電路模擬與檢測裝置試用計劃:試用計劃:1.收集相關資料構建開發環境2.掌握程序的編譯與下載方法3.驗證例程并學習其設計方法4.利用開發板實現典型的邏輯芯片

2017-07-25 10:47:04

無論從微觀到宏觀、從延長電池壽命到減少全球變暖的溫室效應等等,各種不同因素都在迅速推動系統設計人員關注節能問題。一項有關設計優先考慮事項的最新調查指出,大部分工程師已把功耗排在首位,或者是將其緊跟在性能、密度和成本之后。在功耗方面,FPGA帶來了獨特的挑戰。為什么要設計優化FPGA功耗?

2019-08-08 07:39:45

本文闡述了Spartan-3 FPGA針對DSP而優化的特性,并通過實現示例分析了它們在性能和成本上的優勢。

2019-10-18 07:11:35

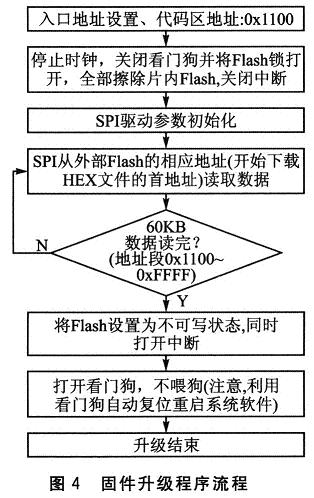

方案如圖4所示。這是一個功能正確的應用實現方案,但沒有進行任何性能優化或為充分利用FPGA架構的功能進行考慮。因此該代碼在SDAccel中編譯完成后,在Alpha Data卡上運行得到的最大吞吐量僅為

2019-06-19 07:27:40

在數字接收機的各種參數中,頻率是最重要的參數之一,它能反映接收機的功能和用途、以及頻譜寬度等重要指標。傳統的順序測頻技術一般通過對接收機頻帶的掃描,對頻域進行連續取樣。該方法原理簡單,技術成熟,但是

2019-09-19 07:39:03

其在設計思路和編程風格等方面也存在差異,這些差異會對系統綜合后的電路整體性能產生重要的影響。在VHDL語言電路優化設計當中,優化問題主要包括面積優化和速度優化。面積優化是指CPLD/FPGA的資源

2019-06-18 07:45:03

FPGA中的專用雙端口塊存儲器資源,天生的FIFO模塊,其存取速度可以達到100 MHz以上,完全滿足實際使用的需求。 FPGA芯片的電平判定檢測功能在后面的FPGA檢測方法中有具體說明。2.3 DSP

2018-08-15 09:43:14

系統功能設計(末尾附文件)本系統由STM32F103C8T6單片機核心板、霍爾傳感器、LCD1602液晶、電機驅動及電源組成。1、通過霍爾傳感器檢測單位時間內電機上磁鐵經過的次數,也就是轉動的圈數

2021-09-07 06:30:08

文章目錄1 簡介2 緒論2.1 課題背景與目的3 系統設計3.1 智能飲水機功能設計3.1.1 智能飲水機的按鍵功能:3.1.2 智能飲水機的顯示功能:3.2 系統架構3.3 軟件部分3.3.1

2021-11-19 08:33:21

本文以精品路線速率1GB目標優化為出發點,系統性地從基礎優化、覆蓋、調度、Rank、MCS等方面概述了精品路線的速率優化方法,并以寧波電信進行了試點研究應用,精品路線速率由950mbps左右最高優化至1.2gbps,優化效果顯著,具有很強的推廣價值和借鑒意義。

2021-03-01 06:42:46

如何去實現RK3288開發板支持雙網口的功能設計呢?

2022-03-04 07:16:14

基于STM32的頻率控制器具有哪些功能呢?如何去實現一種基于STM32頻率控制器的功能設計呢?

2022-01-25 07:18:24

隨著可編程技術的不斷發展,FPGA被廣泛應用于電子設計的各個領域。新的設計思想和設計方法也被不斷的提出和應用,如FPGA的動態部分重構技術。所謂動態重構是指對于時序變化的數字邏輯系統,其時序邏輯

2019-09-20 07:15:52

如何用TIMER1輸入捕獲功能設計的頻率計?

2022-01-24 06:02:27

程序實現的功能一致;(2)有效原則:優化后要比優化前運行速度快或占用存儲空間小,或二者兼有;(3)經濟原則:優化程序要付出較小的代價,取得較好的結果。二、算法優化方法1.系統優化(1)編譯器優化等級配置(-O0/-O1/-O2/-O3)(2)流水線多線程結構(pipeline)2.算法優化(需要

2021-12-21 06:54:14

內容提要1 軟件體系結構及設計過程2 DBAS 總體設計3 DBAS 功能概要設計4 DBAS詳細設計5 DBAS 安全框架設計6 DBAS 實施的過程及內容DBAS功能設計包括應用軟件中的數據庫

2021-07-05 08:04:46

PIC16F145X,XC8:我有一個重要的功能:UIT88T函數(UTI8YT,UIT88T,UIT88T,UIT88T**);這個函數可以在PIC運行期間一直優化重要功能調用;不知道是否有一些

2019-01-14 09:52:08

如何利用雙焊盤檢測電阻去優化高電流檢測精度?

2021-05-06 09:21:34

大家好,我想檢查FPGA功能和I / O引腳功能在我的主板上使用“Selftest application”。在我的Selftest應用程序中,我可以使用哪些方法來檢查這些?請提供一些想法。謝謝

2019-04-01 12:33:26

要畢業了,畢設是完全沒學過的FPGA課題,求助各位大哥幫幫忙,要求:了解并掌握LFMCW雷達的工作原理、用途及優缺點;了解常用的雷達目標檢測方法,選取其中一種完成其Verilog實現,并用FPGA

2018-04-08 23:48:36

設計低功率電路同時實現可接受的性能是一個困難的任務。在 RF 頻段這么做更是迅猛地提高了挑戰性。今天,幾乎每一樣東西都有無線連接能力,因此 RF 功率測量正在迅速變成必要功能。這篇文章著重介紹多種準確測量 RF 信號電平的有用方法,以優化這些無線系統的性能。本文討論滿足各種不同應用需求的優化方法。

2019-07-22 07:53:11

親愛的每一個人, 我對fpga編程有疑問..如果我想使用另一個fpga來做它(例如編程fpga2我將使用fpga1),除了jtag之外,我可能需要從fpga1獲取額外的引腳( TDI,TDO,TMS

2019-03-22 06:03:59

目錄一、電源優化方法1.1 功能禁用1.2 動態功耗管理 (Dynamic Power Management)1.3 頻率縮放1.4 時鐘門控1.5 使用PL加速二、四大功耗域及PMU2.1 電池

2021-11-12 08:36:14

織機選色器的功能設計織機選色控制器是一個可以編程的順序控制器。它有兩個工作狀態:編程狀態和運行狀態。編程狀態的主程序的功能為更新顯示器上顯示的內容、用戶鍵入編輯相應的用戶程序。鍵盤有MOD、TAB

2011-04-21 09:22:28

user 21ic在2013-8-26發表了一篇文章《LMP91000 在電化學傳感器電極故障檢測中的應用》,我看了之后不能確定是LMP91000芯片本身就有故障檢測功能,還是需要通過設計外圍電路才能實現?我們現在在開發2017年的新產品用到這個芯片,現在急需確定如何實現這個功能?

2019-05-09 15:04:44

您好,我希望有人可以幫我確定我是否有可能做的事情。我在兩塊PCB上有兩個Artix-7 FPGA(參見下面的簡單草圖;我將左側FPGA稱為“FPGA1”,將右側FPGA稱為“FPGA2”)。我將數據

2020-08-28 06:22:25

每一版本都提供了完整的FPGA設計流程,并且專門針對特定的用戶群體(工程師)和特定領域的設計方法及設計環境要求進行了優化。那大家知道賽靈思ISE? 設計套件11.1版對FPGA有什么優化作用嗎?

2019-07-30 06:52:50

FPGA怎么選擇?針對功耗和I/O而優化的FPGA介紹

2021-05-06 09:20:34

主要講解了fpga設計、方法和實現。這本書略去了不太必要的理論、推測未來的技術、過時工藝的細節,用簡明、扼要的方式描述fpga中的關鍵技術。主要內容包括:設計速度高、體積小、功耗低的體系結構方法

2012-03-01 14:59:23

網站前臺功能設計與實現

(1) 了解電子商務網站前臺功能設計的方法。

(2) 能夠分析網站前臺的功能構成。

(3) 熟悉網上購物的業務流程。

2009-04-28 17:00:17 0

0 主要描述了一種基于FPGA利用Verilog HDL實現的反正切函數計算的優化算法。反正切函數的計算在相位檢測,偏振光檢測等檢測系統有重要的應用。討論了泰勒展開式法和直接LUT查找表

2010-08-06 14:50:38 24

24 使用AVR 定時/計數器的PWM功能設計要點作者:馬潮老師 / 整理:armok / 2005-01-17/ www.1cnz.cn 取自《M128》上。供參考。一、定時/計數器PWM設計

2010-12-12 11:40:48 75

75 手持設備中的FM功能設計與實現

介紹如何在嵌入式系統中實現調頻收音功能,重點闡述NXP公司的FM芯片TEA5760的工作原理、硬軟件設計及要點,并給出了測

2009-03-29 15:11:14 1778

1778

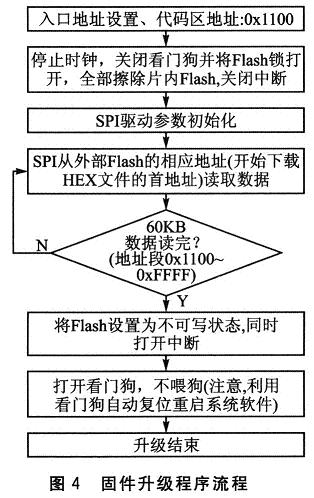

MSP43F149系列單片機的IAP功能設計

TI公司的MSP430系列單片機是具有很高實用性價值的產品,在許多領域得到廣泛的應用,特別是它的超級低功耗特性,是目前所有其他

2010-03-11 11:50:37 970

970

為準確捕捉行波到達時間,使高壓輸電線路故障測距達到實用化水平,本文提出一種基于FPGA 的行波波頭捕捉方法。結合GPS 高精度時鐘系統和專用行波傳感器,本方法完全采用FPGA 來記

2011-05-27 18:17:18 33

33 如果用戶希望在自己設計的電路(如:FPGA、MCU等)增加三電平輸入,檢測方法有三種:

2012-10-09 11:41:04 1628

1628

為了滿足對隨機數性能有一定要求的系統能夠實時檢測隨機數性能的需求,提出了一種基于FPGA的隨機數性能檢測設計方案。根據NIST的測試標準,采用基于統計的方法,在FPGA內部實現了

2013-07-24 16:52:06 45

45 基于FPGA的SM3算法優化設計與實現的論文

2015-10-29 17:16:51 4

4 高級FPGA設計 結構、實現和優化,適合于FPGA的進階學習。

2016-05-11 16:40:55 15

15 高級FPGA設計 結構、實現和優化,適合于學習FPGA的進階學習。

2016-05-11 16:40:55 14

14 基于熵方法的計算機網絡脆弱性檢測和優化_吳杏

2017-01-07 18:56:13 0

0 基于FPGA的可堆疊存儲陣列設計與優化

2017-01-07 21:28:58 0

0 基于FPGA的高速固態存儲器優化設計_楊玉華

2017-01-13 21:40:36 1

1 基于FPGA/CPLD的UART功能設計

2017-01-23 20:45:37 30

30 參加 ?FPGA? 功率優化班,將幫助您創建更高電源效率的 ?FPGA? 設計。通過本課程的學習,將有助于您的設計滿足更小型化的 ?FPGA? 器件,降低 ?FPGA? 功耗,或在更低的溫度下運行

2017-02-09 06:24:11 167

167 線性系統的H_2_H_故障檢測優化方法設計_盧娟

2017-03-15 10:52:03 0

0 TMS470單片機的高溫RS485串行通信功能設計

2017-08-31 10:22:35 7

7 資源、速度和功耗是FPGA設計中的三大關鍵因素。隨著工藝水平的發展和系統性能的提升,低功耗成為一些產品的目標之一。功耗也隨之受到越來越多的系統工程師和FPGA工程師的關注。Xilinx新一代開發工具Vivado針對功耗方面有一套完備的方法和策略,本文將介紹如何利用Vivado進行功耗分析和優化。

2017-11-18 03:11:50 4873

4873 ,分析了算法的時間復雜度。實驗結果表明,該方法可有效減少數據信息損失,具有迭代次數少、收斂速度快等優點,可有效提高入侵檢測樣本數據的優化效率。

2018-02-26 10:29:42 0

0 吃能垃圾箱檢測功能部分

2018-05-13 09:57:06 4

4 控制功能設計1:輸入快充檢測

2018-08-17 01:11:00 5916

5916 了解如何利用Xilinx成本優化的FPGA和SoC產品組合的最新增強功能。

2018-11-28 06:20:00 2086

2086 高層次的設計可以讓設計以更簡潔的方法捕捉,從而讓錯誤更少,調試更輕松。然而,這種方法最受詬病的是對性能的犧牲。在復雜的 FPGA 設計上實現高性能,往往需要手動優化 RTL 代碼,這也意味著

2018-12-16 11:19:28 1435

1435

FPGA I/O 優化功能提供了自動化 FPGA 符號生成流程,該流程與原理圖設計和 PCB 設計相集成,可節省大量創建 PCB 設計的時間,同時提高原理圖符號的總體質量和準確性。

2019-05-20 06:16:00 2844

2844

與 FPGA 軟件工具進行自動雙向信息交換可提供由供應商規則驅動的“設計即正確”的 I/O 分配,從而實現快速、無誤的優化流程。其包括了最新的器件支持,并且可提前訪問尚未發布的 FPGA 供應商器件。

2019-05-16 06:13:00 3380

3380

本文檔的主要內容詳細介紹的是單片機的定時和計數功能設計的詳細資料說明包括了:1.定時/計數器的功能,2.與定時/計數器有關的寄存器,3.定時/計數器工作方式,4.定時器的應用

2019-05-20 08:00:00 4

4 本文檔的主要內容詳細介紹的是TMS320F28335和FPGA1板卡接口的PCB詳細資料說明

2020-03-21 14:38:27 33

33 本案例介紹了如何使用Silexica的SLX FPGA優化人臉檢測數據中心的OpenCL AI內核。 引言 FPGA正越來越多地被用作數據中心的協處理器。這一轉變背后的驅動力是利用FPGA的并行特性

2021-05-08 14:55:09 1710

1710

WiFi物聯網智能插座電源功能設計包括三部分:具體功能說明如下所示:AC 220V轉DC 5V,將交流電變為直流電;DC 5V轉DC 3.3V,實現MCU供電和WiFi模塊供電;DC 5V轉DC 5V,隔離作用,實現電耗檢測模塊和繼電器模塊的供電。

2021-11-05 20:21:02 10

10 聲明:本文檔來源于EasyFlash的倉庫,原作者armink。因github上圖片顯示緩慢,我轉載到了CSDN。文檔鏈接:EasyFlash V4.0 ENV 功能設計與實現EasyFlash

2021-11-06 09:35:58 3

3 FPGA是可重新編程的器件,因此系統設計人員可以不斷開發、測試和實施對現有功能的優化,或者引入全新的功能,無需等待下一代系統。而且,由于FPGA的算法不斷發展,可以適應各種變化,在PC生命周期內持續優化新功能。

2022-10-26 15:23:29 462

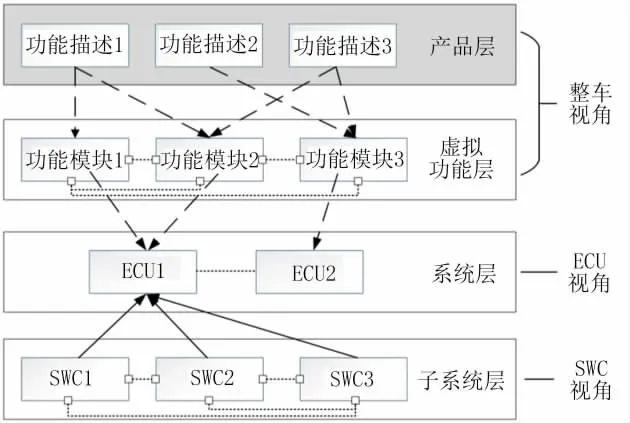

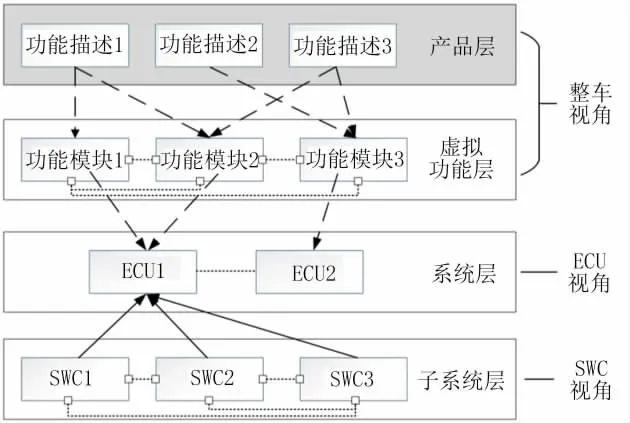

462 的基于文檔的功能設計方式,已不足以滿足現階段功能開發需求。本文結合項目實踐案例,基于Enterprise Architect(以下簡稱:EA) 工具對SOA(Service Oriented Architecture,面向服務架構) 架構功能設計方法進行應用和探索。

2023-05-06 16:53:50 622

622

設備的計劃運行時間來自于設備的班次模式,“生產日歷“模塊描述設備的計劃作息時間。關于“生產日歷”的功能設計和實現,請參閱前文“MES工單管理功能設計和實現”中關于“工廠建模”中的詳細描述,其功能完全相同,此處不再贅述。

2023-05-25 15:21:19 609

609

電子發燒友App

電子發燒友App

評論