本系統采用基于FPGA與DSP協同工作進行視頻處理的方案,實現視頻采集、處理到傳輸的整個過程。

2014-10-23 15:35:49 6040

6040

DSP+FPGA架構的最大特點是結構靈活、有較強的通用性、適合于模塊化設計,從而能夠提高算法效率,同時其開發周期短、系統易于維護和升級,適合于實時視頻圖像處理。

2015-02-03 15:20:47 1166

1166

新一代紅外成像導引系統須具備高精度、處理速度快、實時性強且反應時間短等特點,這便要求圖像處理計算機能滿足圖像處理中大數據量、復雜運算、實時性強、高傳輸率和穩定可靠等要求。文中從工作原理、硬件及軟件3個方面介紹了基于DSP和FPGA芯片的紅外信息數據處理系統設計方法。

2015-07-30 14:43:57 503

503

什么是DSP圖像處理系統?DSP圖像處理系統中信號完整性的問題是什么?有哪些解決方案?

2021-06-01 06:40:35

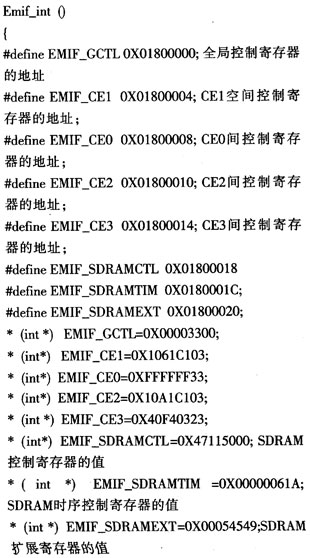

本人剛入門FPGA,不知道如何實現FPGA+DSP,FPGA+ARM接口設計,網上查詢有的說FPGA+DSP可以通過EMIF,IP核實現,FPGA+ARM可以通過SPI,有沒有具體硬件參考的?

2016-08-27 11:30:26

,生命周期縮短。實現功能強、性能指標高、抗干擾能力強、工作穩定可靠、體積小、功耗低、結構緊湊合理符合彈載要求的導引頭信號處理器已經勢在必行。過去單一采用DSP處理器搭建信號處理器已經不能滿足要求

2019-08-30 06:31:29

方法。本系統的主要工作是通過基于FPGA的嵌入式系統,實現數據采集、數據存儲、LCD顯示、USB數據傳輸和數據處理,完成光 纖微擾動傳感的擾動識別和定位功能。1 系統結構和硬件設計1.1 系統結構

2020-09-04 09:56:23

針對遙感系統的工作環境特點、待處理信號的頻譜特征以及系統信噪比等要求,綜合比較多種信號采集系統方案的優缺點,本文提出了一種基于FPGA的激光多普勒測振計信號采集與處理系統的設計方案,該方案可以實現光

2019-06-24 07:16:30

方法。本系統的主要工作是通過基于FPGA的嵌入式系統,實現數據采集、數據存儲、LCD顯示、USB數據傳輸和數據處理,完成光 纖微擾動傳感的擾動識別和定位功能。1 系統結構和硬件設計1.1 系統結構

2020-08-31 18:54:17

方式和控制結構比較復雜,難以用純硬件實現。因此,實時信號處理系統是對運算速度要求高、運算種類多的綜合性信息處理系統。1 信號處理系統的類型與常用處理機結構根據信號處理系統在構成、處理能力以及計算問題到

2015-06-01 11:47:36

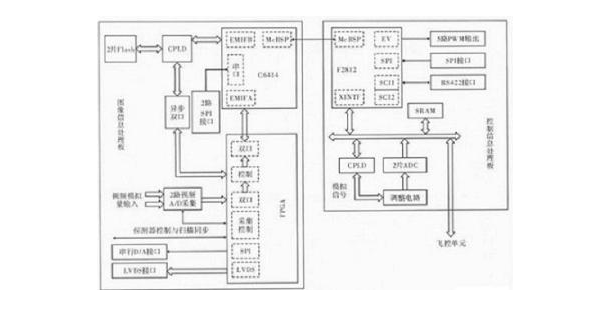

本系統采用基于FPGA與DSP協同工作進行視頻處理的方案,實現視頻采集、處理到傳輸的整個過程。實時視頻圖像處理中,低層的預處理算法處理的數據量大,對處理速度要求高,但算法相對比較簡單,適合于用

2019-07-01 07:38:06

的軟硬件結構,使得DSP具有較高的數字運算處理速度和較寬的動態范圍,可以高效實時地實現卷積、相關、窗口、FFT等需要進行大量數據乘法和加法的運算[1].DSP特有的數字信號處理優勢使其在數據通信、圖像處理

2011-03-06 22:28:27

為解決高速數字圖像處理系統和實時性相沖突的要求,設計了以多DSP(數字信號處理器TMS320C6416)和現場可編程門陣列(FPGA)相結合的實時圖像處理系統。重點介紹了該系統的硬件資源選擇、基本組

2021-04-28 06:14:48

DSP技術廣泛應用于各個領域,但傳統的數字信號處理器由于以順序方式工作使得數據處理速度較低,且在功能重構及應用目標的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實現數字信號處理系統,具有很強的實時性和靈活性,因此利用FPGA實現數字信號處理成為數字信號處理領域的一種新的趨勢。

2019-10-17 08:12:27

單片FPGA圖像預處理系統的設計與實現采用單片FPGA設計與實現圖像處理系統的方法,并對系統硬件進行了分析和設計,對FPGA內電路模塊進行了VHDL建模,在FPGA開發平臺ISE4.1上實現了

2009-09-19 09:26:14

,有利于方位識別引信的實現。文中在采用FPGA+DSP架構的基礎上,實現一種具有8象限方位識別能力的引信信號處理機。

2020-04-20 07:24:20

,數字信號處理與數字圖像處理沒有太大區別),就意味著可以用FPGA做硬件設計來實現DSP芯片的功能,當然,相比較專業的DSP芯片 成本太高,因此你也沒必要選擇FPGA+DSP,就選擇DSP芯片,算法...

2021-07-28 09:16:02

在信號處理系統中一般采用數據采集卡實現數據采集,采用微機軟件處理的方法實現數據處理,采用PC機實現數據管理。由于PC機的CPU采用的是馮?諾依曼存儲器結構,并不適用于數字信號的運算,若完全使用PC機

2018-12-17 11:29:06

彈載信息處理系統是一種實時嵌入式數字處理系統,用于對彈載導引系統接收信號進行分析處理,實現對目標信號的檢測、截獲和跟蹤以及目標信息的提取,是彈載雷達導引系統的關鍵組成部分。

2019-09-19 07:07:17

基于DSP的圖像處理系統的應用研究摘要 本文介紹了一種基于FPGA+DSP結構的具有通用性、可擴充性的高速數字圖像處理系統硬件平臺。重點介紹了以高速數字信號處理器TMS320DM642

2012-12-19 11:05:08

本系統采用基于FPGA與DSP協同工作進行視頻處理的方案,實現視頻采集、處理到傳輸的整個過程。 實時視頻圖像處理中,低層的預處理算法處理的數據量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-28 08:10:26

數據量特別大、運算復雜,單純依靠通用PC很難達到實時性要求,不能滿足現行高速三維圖像處理應用。 本系統中,采用FPGA實現底層的信號預處理算法,其處理數據量很大,處理速度高,但算法結構相對

2019-06-24 06:11:03

圖像數據處理的工作原理是什么?基于FPGA+DSP的圖像處理系統待如何去設計?

2021-06-02 06:54:28

本系統采用基于FPGA與DSP協同工作進行視頻處理的方案,實現視頻采集、處理到傳輸的整個過程。 實時視頻圖像處理中,低層的預處理算法處理的數據量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-19 06:12:05

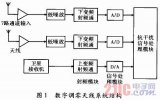

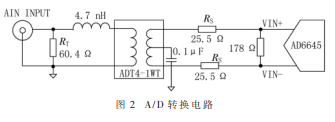

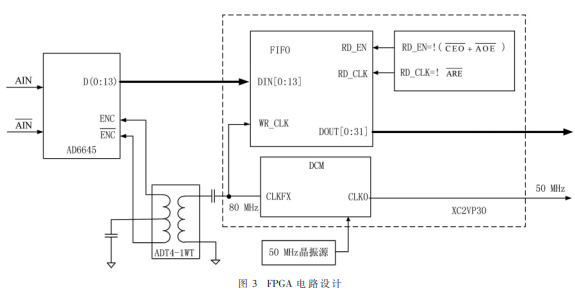

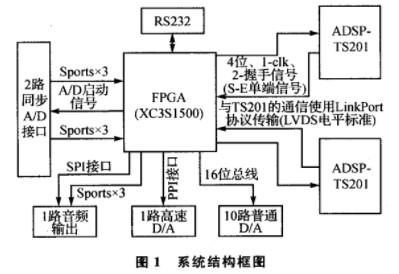

基于FPGA和DSP的光纖傳感信號實時處理系統。2. 系統組成與硬件流程圖圖1 系統結構框圖2.1 A/D前端處理電路及A/D采樣模塊探測器對光纖輸入的光脈沖序列進行光電轉換,通過濾波器實現波分解復用,再對信號

2021-07-05 11:23:33

FIFO,最后由FPGA和PCI9656聯合將數據傳輸到CPCI總線,完成串行信號的處理。6 結語本文介紹了一種基于PFGA的多DSP并行處理系統的設計,重點對DSP并行結構設計進行了分析,并介紹了

2019-05-21 05:00:19

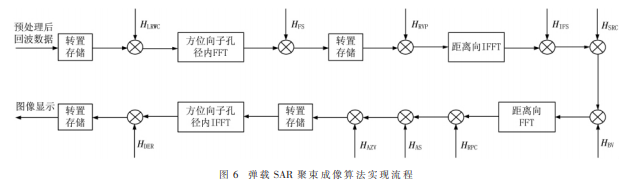

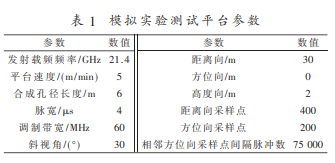

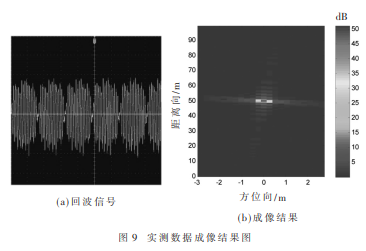

內部大容量存儲資源,采用乒乓結構進行流型運算,提高FFT運算速度,同時保證結果的準確性;對實際硬件進行了FFT運算測試,測試結果證明了系統的可行性和正確性,并且利用該硬件系統成功完成了星載SAR實時成像

2009-06-14 00:19:55

基于C55x DSP核芯片實現基帶信號處理系統的設計

2020-12-21 06:19:01

向下的設計方法,探討了數字集成系統的系統級設計和寄存器傳輸級設計,描述了數字集成系統的高層次綜合方法。最后本文描述了數字信號處理系統結構的實現方法,指出常見的高速、實時信號處理系統的四種結構:由于

2017-11-28 11:32:15

彈載信息處理系統是一種實時嵌入式數字處理系統,用于對彈載導引系統接收信號進行分析處理,實現對目標信號的檢測、截獲和跟蹤以及目標信息的提取,是彈載雷達導引系統的關鍵組成部分。隨著軍事技術的發展,未來

2019-08-29 06:07:24

,生命周期縮短。實現功能強、性能指標高、抗干擾能力強、工作穩定可靠、體積小、功耗低、結構緊湊合理符合彈載要求的導引頭信號處理器已經勢在必行。過去單一采用DSP處理器搭建信號處理器已經不能滿足要求.FPGA+DSP的導引頭信號處理結構成為當前以及未來一段時間的主流。

2019-11-06 08:34:27

隨著紅外探測技術迅猛的發展,當今紅外實時圖像處理系統所要處理的數據量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA硬件架構進行較為復雜的圖像處理算法運算時,有時就顯得有些捉襟見肘了

2019-11-08 06:31:26

所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。

2019-10-16 07:14:00

本文設計了一套基于DSP的陣列聲波信號采集與處理系統,此系統將作為正在研制的陣列聲波測井儀中的一部分,應用于油田勘探中。

2021-05-31 06:26:35

本文闡述了基于信號處理和嵌入式應用的音頻處理系統的設計和實現。

2021-06-08 07:07:19

,生命周期縮短。實現功能強、性能指標高、抗干擾能力強、工作穩定可靠、體積小、功耗低、結構緊湊合理符合彈載要求的導引頭信號處理器已經勢在必行。過去單一采用DSP處理器搭建信號處理器已經不能滿足要求.FPGA+DSP的導引頭信號處理結構成為當前以及未來一段時間的主流。

2019-08-19 06:38:12

隨著圖像處理技術及傳感器技術的不斷發展,高清數字圖像取代模擬圖像成為一種趨勢。設計了一種基于HD-SDI技術的高清圖像處理系統,可通過FPGA+DSP架構對1080P全高清圖像進行采集和字符疊加,并

2021-06-01 07:03:16

隨著紅外探測技術迅猛的發展,當今紅外實時圖像處理系統所要處理的數據量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA硬件架構進行較為復雜的圖像處理算法運算時,有時就顯得有些捉襟見肘了

2019-08-23 08:29:27

您好:由于最近我們要開發彩超中的后端彩色多普勒信號處理系統,現在對應用于醫療成像的DSP器件也有一定的了解,也仔細看了貴公司提供的醫療應用解決方案中推薦的DSP,但是,介于我們這邊具體的系統要求

2020-06-15 13:32:45

基于VxWorks的多DSP并行處理系統的實現

2009-03-29 12:31:18 17

17 介紹了基于距澎多普勒算法的成像處理器方位向處理,并針對機載合成孔徑雷達(SAR)實時成像探討了采用DSP并行計算技術實現方位壓縮的原理和結果。

2009-05-08 16:57:12 30

30 根據電力監控系統的要求,提出一種基于FPGA技術的多路交流信號采集與處理系統的設計方法。分析整個系統的結構,并討論FPGA內部硬件資源的劃分和軟件的設計方案,以及各個功能

2009-05-16 14:47:58 27

27 設計了一種基于FPGA 和DSP 的光纖信號實時處理系統,介紹了系統的硬件組成和工作原理。該系統采用FPGA 實現數據的高速采集和邏輯控制,用DSP 實現傳感信號的全數字解調,分析了載

2009-06-19 11:17:43 24

24 本文介紹了腦電信號處理的兩種基本方法及其優缺點, 分析了DSP 尤其是TMS320LF2407 的主要特點,闡述了基于TMS320LF2407DSP 的16 通道腦電信號處理系統的硬件和軟件的實現方法。

2009-08-31 08:32:11 43

43 本文研究了基于DSP 的語音信號處理系統,分析了TI 公司的信號處理器TMS320VC5402 與音頻模擬芯片TLC320AC01(以下簡稱AC01)的結構特點,描述了兩者之間的多通道緩沖串口的硬件

2009-12-14 11:17:13 73

73 介紹了一種基于FPGA+DSP 的數據采集與處理平臺,給出了系統實現的總體方案,并闡述了各部分硬件電路的設計。重點對FPGA 內部各主要功能模塊做了詳細闡述,對各個模塊的設計方法

2009-12-19 15:59:16 34

34 為了滿足干涉超光譜復原處理系統對數據及實時性要求,本文提出了一種基于多ADSP-TS101 的FPGA+DSP[1]的并行圖像處理系統的解決方案,并給出了具體硬件實現。目前,該系統能夠滿

2010-01-06 15:31:32 8

8 基于DSP和DSP/BIOS的實時雷達信號采集與處理系統:介紹了一種在實時操作系統DSP和DSP/BIOS 平臺下的雷達信號實時采集" 處理與傳輸系統的設計和實現! 利用Tms320c6416DSP強大的數據處理

2010-01-16 16:59:46 25

25 針對SAR信號仿真系統高速實時數據處理和傳輸的要求,本文設計并實現了基于雙DSP結構的高性能實時信號處理板。該板使用兩片TMS320C6416作為信號處理核心和數據流控制中心,使用PCI

2010-08-05 15:02:57 21

21 基于DSP的圖象采集與處理系統的設計

圖像處理系統的一個關鍵問題就是數據量龐大,數據處理相關性高,實時實現比較困難。即使采用高速單片機也無法

2009-04-22 20:01:19 820

820

基于雙DSP的實時圖像處理系統

介紹了基于雙DSP的實時圖像處理系統。該系統通過兩片TMS320C6201作為系統計算中心,通過可重構成的FPGA計算系統獲得系

2009-12-08 14:25:35 1009

1009

基于DSP+FPGA+ASIC的實時圖像處理系統

1.引言

隨著紅外焦平面陣列技術的快速發展,紅外成像系統實現了高幀頻、高分辨率、高可靠性及微型化,在目標跟蹤

2010-01-13 10:39:49 1115

1115

摘要:根據星載SAR成像算法的原理,提出了一種用FPGA實現該成像處理器的有效方法,該處理器的體系結構由算法直接映射而來,同時根據算法內在的時間關系將流水處理和并行處理相結合,從而極大地減少了處理時間,根據算法各運算對數據的精度要求不同,將浮點運算和定

2011-02-27 12:55:50 64

64 介紹了一種用于數字化雙功能多普勒超聲成像儀中以單片FPGA 實現的實時、多任務、高速信號處理系統,該系統承擔著動態濾波、多普勒解調、包絡檢波、FFT 變換、數據壓縮、數據選通等

2011-09-14 15:18:43 143

143 文中給出了一種信號處理系統的硬件實現方案。首先概述GPS自適應調零天線的系統結構,然后給出信號處理系統的硬件設計思路及其功能模塊的實現,最后通過實測數據驗證硬件模塊可以

2011-11-30 16:47:07 80

80 在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統

2012-07-05 15:01:40 7272

7272

基于FPGA的雷達信號處理系統設計的論文

2015-10-30 10:38:12 6

6 基于FPGA+DSP實時圖像采集處理系統設計

2017-01-03 11:41:35 9

9 高效機載SAR實時成像處理系統設計_楊磊

2017-01-07 16:00:43 1

1 基于雙DSP和雙FPGA的高速圖像處理系統設計_吳雷

2017-03-16 09:28:51 2

2 基于DSP_FPGA的LFMCW雷達測距信號處理系統設計_陳林軍

2017-03-19 19:07:17 4

4 基于FPGA的軟硬件協同實時紙病圖像處理系統_齊璐

2017-03-19 19:07:17 0

0 基于FPGA和DSP的高速圖像處理系統

2017-10-19 13:43:31 19

19 基于DSP的數字信號采集處理系統設計

2017-10-19 15:10:22 25

25 基于DSP和FPGA的模塊化實時圖像處理系統設計

2017-10-23 14:09:42 9

9 基于雙DSP的全方位視覺圖像處理系統硬件設計與研究

2017-10-23 14:16:16 11

11 的更新速度加快,生命周期縮短。實現功能強、性能指標高、抗干擾能力強、工作穩定可靠、體積小、功耗低、結構緊湊合理符合彈載要求的導引頭信號處理器已經勢在必行。過去單一采用DSP處理器搭建信號處理器已經不能滿足要求.FPGA+D

2017-10-25 16:52:12 1

1 所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-26 15:44:56 2

2 的實時性和靈活性,因此利用FPGA實現數字信號處理成為數字信號處理領域的一種新的趨勢。 以往基于FPGA的數字信號處理系統的模型及算法采用VHDL或VerilogHDL等硬件描述語言描述。但這些硬件描述語言往往比較復雜,而采用Altera公司推出的專門

2017-10-31 10:37:23 0

0 隨著紅外探測技術迅猛的發展,當今紅外實時圖像處理系統所要處理的數據量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA硬件架構進行較為復雜的圖像處理算法運算時,有時就顯得有些捉襟見肘

2017-10-31 11:02:41 0

0 所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-31 17:00:34 12

12 在振動信號采集和處理系統設計中,信號的處理時間與可靠性決定著系統應用的可行性。本文設計了一種基于FPGA的振動信號采集處理系統,該系統通過振動信號采集電路、抗混疊濾波電路、AD采樣電路將電荷信號轉化

2017-11-18 05:26:02 3148

3148

為解決高速數字圖像處理系統和實時性相沖突的要求,設計了以多DSP(數字信號處理器TMS320C6416)和現場可編程門陣列(FPGA)相結合的實時圖像處理系統。重點介紹了該系統的硬件資源選擇、基本組

2017-11-18 12:34:02 4034

4034

針對GPS抗干擾問題,常用手段是在信號處理系統中采用自適應調零算法來實現抗干擾。結合該算法文中給出了一種信號處理系統的硬件實現方案。首先概述GPS自適應調零天線的系統結構,然后給出信號處理系統的硬件設計思路及其功能模塊的實現,最后通過實測數據驗證硬件模塊可以滿足自適應調零算法的要求。

2017-11-24 16:19:35 2066

2066

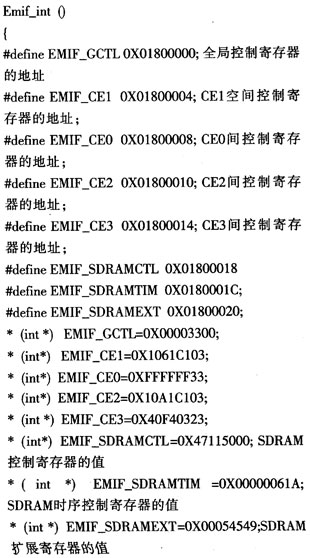

FPGA+DSP的數字硬件系統正好結合了兩者的優點,兼顧了速度和靈活性。本文以導引頭信號處理系統為例說明FPGA+DSP系統中FPGA的關鍵技術。

2019-01-08 08:36:00 2449

2449

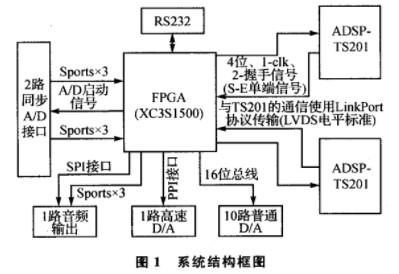

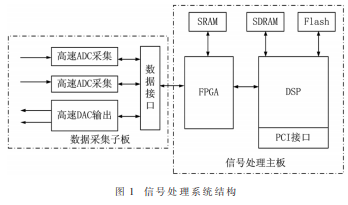

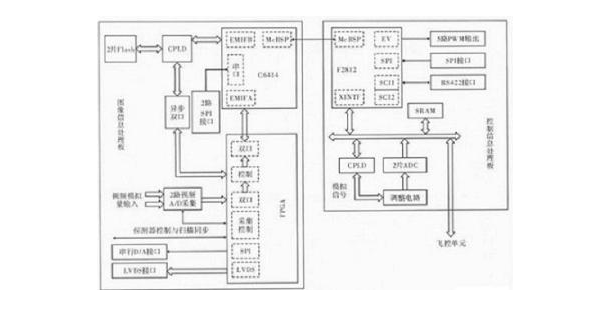

本系統以FPGA作為高性能實時信號處理系統的數據采集和控制中心,2片DSP為數據處理中心,主要包括4個功能模塊——數據采集模塊、FPGA數據控制模塊、DSP處理模塊和通信模塊,系統結構框圖如圖1所示。

2019-04-23 08:29:00 3426

3426

高速中頻采樣信號處理平臺在實際應用中有很大的前景,提出采用FPGA+DSP的處理結構,結合高性能A/D和D/A處理芯片,設計了一個通用處理平臺,并對其主要性能進行了測試。

2018-10-18 16:36:48 4637

4637

大,運算簡單,但是要求運算速率高,可以用FPGA硬件來處理,上層所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。CMOS實際采集的是光線束

2018-10-22 22:00:01 392

392 設計了一套高速線陣CCD信號采集系統,采用FPGA+DSP的數字處理方案,能滿足光信號的實時識別和處理,可用于研究靜態和動態小粒子的光散射彩虹特性。

2019-11-21 17:32:39 24

24 系統的體系結構,并基于FPGA實現了原型系統.該體系結構可以自主完成星載SAR實時成像,并具有良好的可擴展性.利用模擬信號源和高速數據記錄儀對原型系統驗證,1個信號處理單元在50MHz工作頻率下,約11s內完成16384×16384個樣本的星載雷達原始數據的成像處理,用4個信號處理單元就可達到為

2021-01-22 14:29:28 23

23 本文提出了一種用FPGA實現星載合成孔徑雷達實時成像處理器的方法,用來實現星載SAR的CS算法(或RMA算法).該實時成像處理器由7片Xilinx公司的商業FI:‘GA實現,其中4片作為并行的處理

2021-02-05 15:22:46 14

14 ,使用~tera的Quartus II軟件,完成了其中的核心模塊——F盯算法的硬件實現,提高了處理速度;并運用DSP處理器,設計了一個基于FPGA的實時數字圖像處理系統.文中給出了系統的硬件電路和軟件算法模塊.仿真和調試結果表明:用FPGA與高速數字信

2021-02-05 15:54:00 139

139 該文在闡述了灰度圖像順序形態變換的基礎上,介紹了順序形態變換硬件實現的圖像處理系統.該系統采用DSP+FPGA的框架結構,利用FPGA的可重構特性將其中一片FPGA作為協處理器可以實現不同的圖像處理

2021-04-01 11:21:46 8

8 基于FPGA+DSP彈載SAR信號處理系統設計

2021-12-27 18:58:51 21

21 摘要:針對GPS抗干擾問題,常用手段是在信號處理系統中采用自適應調零算法來實現抗干擾。結合該算法文中給出了一種信號處理系統的硬件實現方案。首先概述GPS自適應調零天線的系統結構,然后給出信號處理系統的硬件設計思路及其功能模塊的實現,最后通過實測數據驗證硬件模塊可以滿足自適應調零算法的要求。

2022-10-13 15:43:22 2

2

電子發燒友App

電子發燒友App

評論