互聯網絡蓬勃發展的今天,在網絡入侵檢測系統(NIDS)中,大部分的網絡入侵檢測設備幾乎都依賴于一些基于特征碼檢測的字符串匹配算法,而字符串匹配算法的實現幾乎都是由軟件來實現的。目前應用比較成功的實例有,Snort軟件使用字符串匹配算法對包含特征碼的數據包進行檢測。但是軟件在內容字節流中進行搜索匹配時,需要在不同的處理單元中/內搬移或讀取數據,這對于高速實現線速(OC-48)的檢測系統來說,帶來了很大的處理負荷。因此,如果采用硬件在數據包進入內存之前實現字符串匹配這一功能,將大大減少后端軟件操作的處理負載。

基于IXP2400和FPGA的系統結構

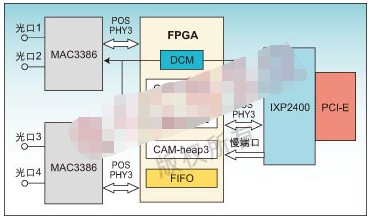

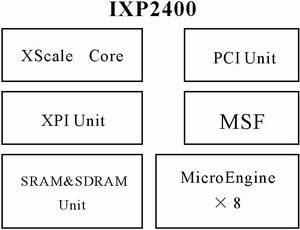

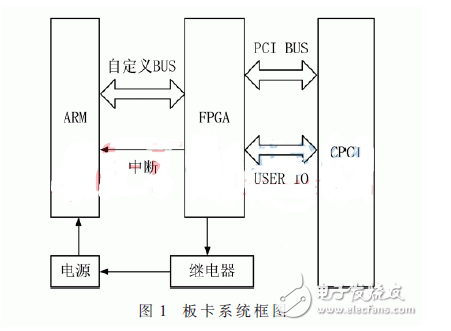

IXP2400是英特爾公司推出的第二代網絡處理器芯片,大量應用于寬帶接入、防火墻、NIDS和負載均衡等系統中,它能滿足OC-48網絡線速的處理要求。玉衡銥達公司設計開發的骨干網絡監控系統采用了IXP2400作為數據包主處理器,FPGA作為協處理器的硬件架構來實現,系統結構框圖如圖1所示。

如圖1所示,系統外接了4個千兆光口,用以接收和發送數據包,它是整個監控系統和骨干網絡的交際通道。光口數據包通過光模塊進入PMC-Sierra公司的MAC3386芯片。接收數據包時,以太網幀數據包從千兆光口進入MAC3386,MAC3386對數據包進行解碼后通過POS PHY3接口進入FPGA的FIFO單元,同時對進入FPGA的數據包進行模式字符串(Pattern-String)的匹配操作,處理后的數據包通過POS PHY3接口傳輸到IXP2400的MSF單元進行下一步的處理。發送時,FPGA只需要將IXP2400發送來的數據包通過POS PHY3接口傳輸給MAC3386,MAC3386對數據包進行編碼后發送給光模塊,光模塊通過光口將數據包發送出去。IXP2400提供了一組數據總線來訪問外部設備寄存器,IXP2400中稱之為慢端口(Slow Port)。在這里,和FPGA相連的慢端口總線的一部分功能是作為寫入FPGA的模式字符串通道。

圖1:基于IXP2400和FPGA的系統結構示意圖。

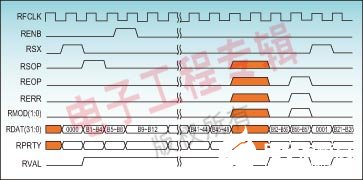

POS PHY3是一種標準化的網絡傳輸接口,接口數據傳輸速率為2.5Gbps,最大支持OC-48的傳輸速率接口。POS PHY3包括接收和發送兩組32位總線,工作頻率為104MHz,峰值吞吐率為3.2Gbps。支持2.5Gbps數據包的全雙工操作。POS PHY3接口接收時序圖如圖2所示。

圖2:POS PHY3接口接收邏輯時序圖。

該時序圖描述了POS PHY3接口接收數據包時,數據流在POS PHY3總線上的傳輸方式和相關的控制信號關系。關于更進一步的詳細描述可以參考POS PHY3接口標準文檔。

系統采用時鐘同步設計,在時鐘上升沿進行數據采樣,與FPGA相連的MAC3386、IXP2400的工作時鐘由FPGA的DCM單元提供,可以保證數據采集的同步和穩定性。

CAM的設計

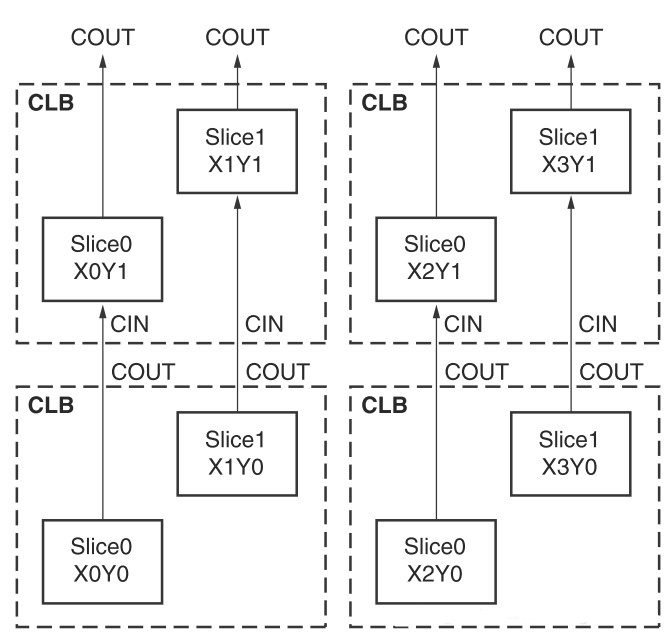

本設計中,由于要實現幾路32B的模式字符串匹配,需要占用大量的RAM存儲單元,同時還得為數據包緩存FIFO保留一定的存儲單元,綜合幾家FPGA芯片廠商RAM的存儲容量,決定選用賽靈思的Virtex2或Virtex Pro系列的FPGA芯片,因為對于相同規模的邏輯資源和寄存器資源來說, Virtex2或Virtex Pro系列的FPGA芯片的RAM容量比其他廠商都要多幾倍。

FPGA中,與RAM存儲單元相關的資源有三類:Block RAM、LUT、寄存器。這三類資源可以通過配置和粘合邏輯(Glue Logic)實現為不同類型和位寬大小的單端口/雙端口RAM、ROM、CAM、FIFO等。FPGA中CAM的實現和配置非常靈活,CAM是實現模式字符串模式匹配的核心資源。

CAM即內容可尋址存儲器。CAM這種存儲器在其每個存儲單元都包含了一個內嵌的比較邏輯,CAM基于內容尋址,通過硬件電路并行查找,實現快速匹配。一般來說在一個時鐘周期內,寫入CAM的待比較數據和其內部存儲的每一個數據進行比較,并返回與端口數據相同的內部數據存儲的地址和是否匹配的標識符。CAM的這種并行處理特性使得它在數據分選領域倍受青睞,被廣泛應用在以太網網址搜尋、路由器中的地址交換表、高速數據處理等方面。

CAM對于高速的數據包模式字符串匹配查找操作來說,我們需要足夠快的時間來完成,如果按照POS PHY3接口標準來說,必須保證寄存器建立(Setup)時間和CAM一次查找匹配時間之和小于1個周期10ns(一般情況下,FPGA設計中的保持(Hold Up)時間都可以滿足,可以不予考慮)。根據FPGA芯片廠商數據手冊提供的性能基準數據,我們配置CAM存儲器選用的資源是Block RAM,配置的地址匹配類型選擇的是非編碼地址的多匹配方式(Multi Match Unencoded),選用該項配置的CAM32_32完成一次匹配查找的操作時間為7ns左右,CAM32_32的配置大小是32位位寬,32個存儲單元的地址深度。

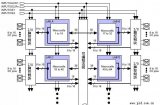

對于POS PHY3的接口標準來說,數據傳輸操作周期為10ns,根據性能基準數據,我們因此除去寄存器的建立時間(<2ns),完成一次CAM匹配操作是完全可以和POS PHY3的接口標準相匹配的。根據數據包在POS PHY3接口的傳輸字節情況和實際設計需要,我們設計了一個CAM-heap來完成數據包的一路32B模式字符串的匹配操作。一個CAM-heap是由4個相同結構和配置的CAM32_32組成。CAM32_32是根據設計需要由自己配置定義的,其配置端口示意圖如圖3所示。

圖3:CAM32_32端口示意圖。

模式字符串匹配實現過程

在NIDS檢測系統中,先將協議解碼后的域值與事先精心提取的攻擊特征(規則)提取相應的字段,即模式字符串,然后從數據包包頭和凈載荷中進行查找匹配模式字符串,從中發現潛在的攻擊行為。基于模式字符串的模式匹配是一項傳統而成熟的入侵檢測技術,提供了很高的準確性與廣泛性。例如:目前網絡應用中大部分使用了一種被稱為智能隧道(Smart Tunnel)的技術,其特點是:服務端(或接收端)沒有綁定任何固定的端口,客戶端(或發起端)可以自行使用任意隨機端口連接服務器,如P2P(點到點)應用(如各種P2P 下載工具、IP電話等)、IMS(實時消息系統 如MSN、Yahoo Pager)、網絡在線游戲等。他們避開了防火墻、NIDS 產品。但是我們可以通過上層的協議識別和動態分析網絡報文中包含的協議特征,發現其所在協議,提取相關的幾段模式字符串,然后遞交給模式字符串模式匹配引擎(FPGA)進行處理。

模式字符串匹配過程可以用紙帶傳輸的過程來進行描述。假設一條紙帶上附有數據包的全部內容(abcd..xyz0123456789.。.),從包頭sop字段ABCD開始一直到包結束eop字段,依次單個字符的向前流動,有一個匹配字符串xyz0123456789模板和該數據包進行匹配。當字符串的流入模板長度等于模式匹配字符串長度后就進行比較,數據包字符串每向前流進一個字符,模式匹配字符串就和數據包流入的字符串匹配一次,直到數據包最后的字符串流入模板,查找結束。如果字符串流入直至流出過程中,數據包中存在與模板字符串相同的序列,則說明匹配成功,否則沒有模板匹配字符串。上例中,當流入模板的數據包字符串為xyz0123456789時,則指示該匹配成功。

MAC3386傳輸數據包給FPGA與紙帶傳輸數據包類似,只不過在POS PHY3接口傳輸數據包時是每周期4字符/字節。FPGA進行模式字符串匹配時,在CAM-heap中每周期進行一次4個輸入字符串的匹配操作。采用并行操作的原理,使用4個CAM模塊一個周期進行4個字符/字節的匹配操作。

舉例說明4個CAM單元的操作關系:假設輸入數據包的某段內容是ABCD EFGH IJKL,要匹配的模式字符串是CD EFGH IJ,先將要匹配的模式字符串按照一定規則寫入4個CAM單元中。數據包傳輸FPGA時第一個周期傳入的是ABCD,第二個周期傳入的是EFGH,第三個周期傳入的是IJKL,在第二個周期到來后,開始進行字符串的匹配操作。

第二個周期進行匹配時,CAM1輸入待匹配的字符串是ABCD(匹配失敗);CAM2輸入待匹配的字符串是BCDE (匹配失敗);CAM3輸入待匹配的字符串是CDEF(匹配成功);CAM4輸入待匹配的字符串是DEFG(匹配成功),所有的匹配地址都保存于寄存器中。

第三個周期進行匹配時,CAM1輸入待匹配的字符串是EFGH(匹配成功);CAM2輸入待匹配的字符串是FGHI(匹配成功);CAM3輸入待匹配的字符串是GHIJ(匹配成功);CAM4輸入待匹配的字符串是HIJL(匹配失敗)。所有的匹配地址都保存于寄存器中。

因為我們匹配是8個字符的字符串,因此在第二個周期CAM3匹配成功后,到第三個周期CAM3的匹配成功,根據一定的邏輯關系和算匹配地址中匹配情況,就可以知道該字符串是否匹配成功。

我們把完成一個標準模式字符串匹配的4個CAM稱之為一個CAM-heap,一個CAM-heap完成一路字符串的匹配查找。如果一個完整的數據包都流經模式字符串模板后,綜合每周期保存匹配地址的寄存器的結果,就可以知道流入的字符串是否和模式字符串匹配。在進行模式字符串的匹配之前,需要先將模式字符串進行4字節的分段,不同段的4個字節寫入不同的CAM單元和不同CAM單元的不同地址中。因為一個CAM-heap可以完成一路字符串的匹配查找,因此我們可以設計幾個CAM-heap并行操作來完成幾路模式字符串的匹配。匹配的模式字符串路數需要根據所選FPGA芯片RAM資源大小來決定。

FPGA的設計實現

模式字符串的FPGA輸入是通過IXP2400的慢端口來寫入的。在接收數據包之前,FPGA譯碼慢端口控制信號,通過IXP2400的慢端口接收模式字符串并寫入FPGA的ROM中。要匹配的模式字符串接收完畢后,設置CAM寫使能信號WE,將幾路模式字符串按照一定格式分別寫入不同的CAM單元中,然后進行下一步的字符串匹配操作。

接收的數據包按照數據流的先后順序寫入FPGA的FIFO中,先入先出。模式字符串匹配完成后,在FIFO出口端添加一個模式字符串的匹配標識頭,來描述該數據包與模式字符串的匹配情況(包括與哪一個數據包匹配還是幾個同時匹配,還是沒有匹配),該匹配標識頭添加在數據包頭,作為數據包內容的一部分發送給IXP2400。IXP2400在接收數據包時,對接收的數據包頭進行解碼,便可知道該數據包的模式字符串模式的匹配情況,以便進行下一步的動作。

從模式字符串匹配實現過程來看,數據包的流入過程和匹配過程是同時進行的,也就是模式字符串匹配過程的時間開銷隱藏在數據包的接收階段,接收完畢,模式字符串匹配結束。數據包只有在接收完畢后,才能決定發送什么樣的數據包字符串匹配標識頭,因此數據包在FPGA芯片中的延時為數據包的輸入延時,按照網絡傳輸最大數據包為1,514B計算,則數據包的最大延時為1514/4=379個周期,按照10ns一個周期計算延時為3.79um。

FPGA芯片的配置模式靈活,包括主串模式、從串模式、并行的SelectMap模式和邊界掃描JTAG模式。經過配置后的FPGA芯片就可以正常工作了。但是基于SRAM的FPGA芯片掉電后,配置文件會自動丟失,因此需要為FPGA芯片配置一塊閃存PROM來保存FPGA的下載文件,這樣掉電后的FPGA以后也能正常工作。

本文小結

本文講述了一種使用FPGA的CAM資源快速實現模式字符串的匹配查找方法,使用在線速(OC-48)的網絡監控系統中,大大減少了后端軟件操作的處理負載。系統設計時,選用的FPGA型號為Virtex2的XC2V2000-5,使用了FPGA中大量的Block RAM存儲單元來構造CAM,采用了并行的設計思想,OC-48處理了3路模式字符串的模式匹配。經過工程實際測試,FPGA模塊很好地實現了3路模式字符串的模式匹配功能,達到了系統的設計要求。

責任編輯:gt

電子發燒友App

電子發燒友App

評論