引言

繼USB協議公布后,USB憑借其占用系統資源少、廉價、通用、可熱插拔等優點,成為通用的串行接口總線。當前,絕大部分計算機外圍設備(如打印機、MP3、移動硬盤等)均采用USB接口。但隨著 USB接口應用的普及,基于USBl.x和USB2.O規范的USB接口逐漸暴露其缺點。由于USB總線是主從式結構,且設備的主從特性在設備設計時就已經固定,這樣就很不利于設備間點對點的數據傳輸。這種以計算機為核心的數據傳輸結構,非常不利于USB總線在嵌入式行業的應用,因為這些設備一般都要求具有與計算機通信的USB設備功能,同時也要求具有連接其他USB設備的主機功能。為了解決這一問題,USB OTG規范作為USB2.O規范的補充出臺了。本文介紹一款USB OTG IP核的設計與實現,該設備控制器可作為IP核用于SoC系統中,完成與主機控制器的通信,并能與普通的USB從設備進行通信。

1 USB OTG的工作原理

OTGl.Oa補充規范對USB2.O進行的最重要擴展是其更具節能性、電源管理,并允許設備以主機和外設2種形式工作。OTG有兩種設備類型:兩用 OTG設備(dual—role 0TG device)和外設式OTG設備(peripher一al_only 0TG device)。兩用0TG設備完全符合USB2.O規范,同時提供有限的主機能力和一個Mini—AB插座,支持主機流通協議(IIost Negotiation Protocol,HNP)”。,且同外設式OTG設備一樣支持事務請求協議(SessionRequest Protocol,SRP)。當作為主機工作時,兩用0TG設備可在總線上提供8 mA的電流,而以往標準主機則需要提供100~500 mA的電流。2個兩用OTG設備連接在一起時可交替以主機和從機的方式工作,這個特點兼容了現有USB規范主機/外設的結構模型。OTG主機負責初始化數據通信,比如總線復位、獲取各種USB描述符和配置設備。這些配置完成后,2個OTG設備便可分別以主機和從機方式傳輸信息,2個設備主從角色交換的過程由主機流通協議定義。

2 IP設計原理和IP模塊設計

USB 0TG控制器芯片按結構分類,通常分為以下2種:

①專為USB OTG設計的芯片。這類芯片集成了微控制器,是完全按照協議設計的,而不是在舊的結構上增加功能。其結構不同于其他常用控制芯片,開發者需要較長的學習時間,但是它能夠達到最優化。

②需要外部微處理器的接口芯片。有些USB控制器只處理USB通信,而且必須由外部微處理器來控制。這種實現接口的標準組件使得使用者可以在各種不同類型的微控制器中選擇一種最適合的微控制器,通過使用已有的結構和減少固件上的投資來縮短開發時間,減少開發風險和費用。但由于外接一個處理器,增加了電路的復雜性。

本文設計的USB OTG IP核采用第2種方式,所采用的處理器是Nios。根據對USB OTG規范的理解,USB0TG控制器應該具有以下的功能:HNP和SRP協議的實現,主機工作模式和設備工作模式。系統結構框圖如圖1所示。

UTMI+接口需要外接一個符合USB 2.0 UTMI+協議的收發器。該芯片用作USB2.O接口的模擬前端,處理由USB2.O接口發出的高速和模擬信號,對其發出的用NRZI方式編碼的數據進行解碼、位填充等,并將串行數據轉換成并行數據;反之,該芯片對由本控制器發出的并行數據通過其內部的差分驅動電路進行串行化、位填充和NRZI編碼,并輸出到USB電纜上。該接口模塊主要用于緩存發送和接收的數據,確保與外圍收發芯片的無縫結合,以及掛起、恢復和復位的檢測。

OTG控制器實現USB OTG補充協議的功能。該模塊主要負責HNP、SRP的硬件實現,以及連接狀態的檢測。

主機控制器實現IP核工作在主機模式的功能。該模塊主要產生掛起、恢復、復位信號,主動發送get_descip—tor、set_address、 set_configuration等標準請求,并把請求變成對應的USB數據包格式(比如TOKEN包加入PID、地址、端點和5位的CRC校驗碼等);隔固定的時間向從設備發送SOF標志,并根據配置的結果產生對應的主機中斷。

設備控制器實現IP核工作在設備模式的功能。該模塊主要負責接收標準的USB請求,比如接收SOF標志、IN標志、OUT標志等,并根據這些請求作出正確的響應以及檢測復位、掛起信號。

控制狀態寄存器完成對IP核控制器內部狀態的設置。它分成2種類型:一種是基本的控制狀態寄存器,比如控制狀態寄存器(指定USB的速率模式、掛起模式、連接狀態、主從模式),設備地址寄存器(存放主機分配給USB設備的地址),中斷屏蔽寄存器(使能對應中斷)和中斷源寄存器(Nios控制器通過讀此寄存器來判斷中斷類型);另一種是端點寄存器控制狀態寄存器,如中斷源寄存器、中斷屏蔽寄存器、緩沖區的指針寄存器和大小寄存器,模塊中實現時根據輸入的地址和讀寫信號來對某一個寄存器進行相應的讀寫操作。

存儲器接口實現IP核內部數據與Nios控制器數據的之間的仲裁。當Nios控制器和IP核內部同時對外部存儲器SRAM進行讀寫訪問時,必須對它們進行數據的仲裁。默認的優先級為IP核內部數據優先級高于Nios控制器的數據優先級。

Nios控制器接口實現USB IP核與外部微控制器(Nios)的數據通信。該接口符合Avalon總線規范,通過輸入地址的最高位來判斷Nios是對內部寄存器進行訪問還是對 SRAM存儲器進行訪問,并完成地址、數據和相關信號的處理。

3 USB OTG IP核的特性討論

3.1 連接狀態的檢測

當上電復位后進入空閑狀態,開始USB會話。首先需要等待一段時間(最多50 ms),OTG控制器會檢測輸入ID線的電平,以確定自己是A設備還是B設備,高電平表示B設備,低電平表示A設備。對于A設備,IP核會等待電源線 Vbus上的電平上升到符合USB會話的4.4 V最低電平要求,具體的操作就是通過UTMI+接口的DrvVbus信號控制PHY對Vbus電源線充電,以提供USB總線工作用的電源;對于B設備,則根據是否正在作SRP請求而實現SRP協議或者進入數據傳輸。當Vbus電源線上的電平滿足要求時,A設備等待B設備連入USB總線。作為主機的A設備的 DpPulldown和Dm—Pulldown在開始會話后始終保持高電平狀態,如果B設備沒有連上,則2條USB數據線DP和DM呈現SE0狀態;而當 B設備連上USB總線時,DP和DM會呈現J態或者K態。根據這一特點,A設備就可以判斷出是否有B設備連入USB總線。

3.2 SRP協議的實現

當設備進入SRP協議實現時,B設備等待SRP操作的初始條件,即通過UTMI+接口的DischrgVbus信號加速SRP條件的滿足。當初始條件都滿足后,B設備通過UTMI+接口的信號XcvrSelect、TermSelect、DpPulldown和DmPulldown實現對PHY的控制,使之向DP線上發出驅動脈沖。持續5~10 ms后,B設備又通過UTMI+接口的信號ChrgVbus控制PHY向Vbus上發出驅動脈沖,該驅動脈沖需要持續足夠長的時間以使Vbus電源線被充電到2.1 V。驅動完成后,回到空閑狀態,進而等待A設備對SRP作出響應。如果A設備識別到了B設備的SRP,則會開始USB會話,否則本次SRP失敗。

3.3 HNP協議的實現

不妨假設A設備當前處于主機狀態,而B設備處于從設備狀態。此時,B設備需要通過HNP取得USB主機地位,過程如下:A設備通過發出掛起命令使得USB 總線準備進入掛起狀態。B設備首先由數據傳輸狀態準備進入掛起狀態。這時,B設備需要檢查是否有HNP請求,如果有則開始等待A設備連接,否則正常地進入掛起狀態。B設備在等待A設備配置時,A設備尚未完全進入掛起狀態,當它進入掛起狀態的同時會檢查是否有B設備的斷開中斷。如果有,則說明B設備正在進行 HNP操作,并且已經進入了等待A設備配置狀態,接著A設備進入設備工作狀態,從而使自己變為從設備。B設備檢測到A設備的連接后,對USB總線進行復位,同時開始對A設備進行復位操作。B設備進入主機模式工作,而A設備則進入從設備模式工作。在B設備作為主機完成了對USB總線的使用后,再一次通過 HNP將USB主機地位還給A設備,操作過程類似。

4 系統功能仿真

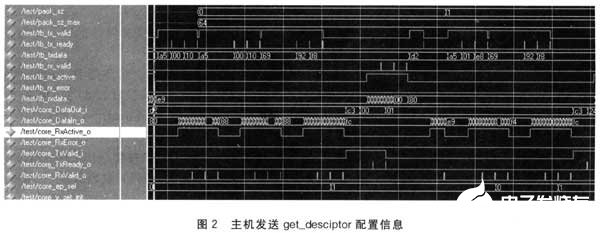

本設計采用硬件描述語言Verilog HDL完成RTL(寄存器傳輸級)的描述。寄存器傳輸級是指在數字系統設計時,可以將數字系統簡單地看作是寄存器和寄存器之間的組合邏輯 (cornbinational logic)。本設計使用Mentor公司的設計仿真軟件ModelSimSE進行功能仿真。應用Verilog HDL語言搭建測試平臺,通過仿真工具,設計者對各設計層次的設計模塊進行仿真,以確定這些設計模塊的功能和邏輯關系是否滿足設計要求。

在設計的驗證階段,將包含該設計的2個USB OTG IP核直連,并讓這2個IP核工作在不同的工作狀態,即一個工作在A設備模式,另一個工作在B設備模式。這樣,A設備就可以作為B設備的激勵源,通過A設備發出一系列測試信號,比如向B設備發出復位信號以及SRP和HNP協議請求,發送SOF標志信號和配置信息等。然后觀察B設備是否對這些命令或者信號做出正確的響應。通過這樣的程序來驗證該IP核是否具有雙功能和對USB協議的支持情況。仿真的部分結果如圖2所示。

5 FPGA驗證

FPGA是一種可編程邏輯器件,可進行多次編程操作,使器件根據不同的需求實現不同的功能。隨著微電子技術的發展,FPGA的性能不斷提高,很多設計已經完全可以由FPGA來完成。目前,在ASIC設計中一個重要的驗證手段就是通過FPGA進行硬件仿真,以保證設計的可靠性。FPGA芯片是整個驗證系統的核心,它包含了USB OTG IP核和相關的控制模塊。因為用Verilog語言來實現控制模塊的功能,所以將它和USB OTG IP核一起綜合然后下載到FPGA中進行測試。

FPGA選用AItera公司的Cyclone系列芯片,具體型號是EPlCl2Q240C8;物理層模擬部分選用Philips公司的產品 ISPl301;存儲器SRAM選用ISSI公司的IS63LVl024—12J。復位電路用來產生上電復位信號,也可以在系統正常工作時,通過按鍵開關產生復位信號。此復位信號提供給USB IP核作為系統復位。系統的布局布線采用的是Altera公司的QHartusII 6.0。

驗證過程分成2個部分來分別驗證主機模式和設備模式。當USB 0TG IP核工作在主機模式時,直接用U盤與IP核進行連接,通過編寫的底層驅動可以識別出U盤。在完成對U盤的驅動后,成功地進行了數據傳輸,最后正確地斷開連接。當IP核工作在設備模式時,IP核作為USB從設備接入電腦主機的USB接口。通過安裝新的驅動,電腦主機可以識別出該USB設備,完成對該設備的驅動后,同樣可以正確地進行數據傳輸,并安全地移除該設備。驗證的結果表明,該USB 0TG IP核的主機和從設備功能均能正常工作,達到了預期的設計要求。

結語

FPGA驗證的結果表明,USB OTG IP核在功能和時序上符合USB2.0標準和OTGl.Oa補充規范的協議要求,具備了主機功能和設備功能,達到了設計的預期目標。另外,完成的USB OTG IP核支持UTMI+接口,可以廣泛應用于包含USB功能的SoC開發。

責任編輯:gt

電子發燒友App

電子發燒友App

評論