您是否曾想在您的 FPGA 設計中使用先進的視頻壓縮技術,卻發現實現起來太過復雜?現在您無需成為一名視頻專家就能在您的系統中使用視頻壓縮。賽靈思新推出的 MPEG-4“ target=”_blank“》MPEG-4 編碼器/解碼器核可以幫助您滿足視頻壓縮需求。

2020-12-24 00:00:00 1230

1230 在其業內領先的低成本Cyclone TM FPGA系列和Nios軟核嵌入式處理器成功的基礎上,Altera現在推出了第二代產品系列。Cyclone II器件為用戶提供更高的邏輯密度和新增硬件性能,比

2019-07-18 07:43:25

我想做一個裝置,配置是這樣:編碼器安裝在滾輪的一端,一個傳感器,當傳感器觸發on時,對編碼器反饋的脈沖進行采集,傳感器off時停止采集,然后把得到的脈沖數傳給計算機,請問資深專業人士,有什么方法去實現這樣的功能,或者有什么樣的電路板可以實現這樣的功能,謝謝。

2014-01-17 23:55:37

編碼器的原理是什么?編碼器可分為哪幾類?編碼器是如何進行接線的?編碼器軟件四倍頻技術是什么?

2021-08-04 06:08:39

編碼器是什么?編碼器工作原理是什么?

2021-10-19 09:59:08

編碼器模式的實現編碼器模式默認使用定時器的通道1和通道2,通道3和通道4不能使用。以下為編碼器模式的配置,編碼器線數為1024,檢測雙通道的上升沿。 HAL_TIM_Encoder_Start

2021-08-16 08:12:54

我最近在做一個旋轉式倒立擺,用32正交解碼是出現了一些問題,編碼器初位置正轉沒問題,反轉就會出現程序卡死,求大神幫忙啊

2017-02-18 11:13:09

編碼器是什么?編碼器主要分為哪幾種?編碼器測速的大致原理是什么?

2021-06-30 07:48:39

編碼器的實現 H.264視頻編碼器的實現有多種方法,不過大部分都是進行移植、優化的操作。H.264代碼要在DSP的軟件平臺CCS環境下運行,需要注意幾個問題:如配置文件、庫文件的改動、數據類型

2011-08-10 14:54:09

的應用 增量型編碼器與絕對型編碼器區別 1、角度測量 汽車駕駛模擬器,對方向盤旋轉角度的測量選用光電編碼器作為傳感器。重力測量儀,采用光電編碼器,把他的轉軸與重力測量儀中補償旋鈕軸相連,扭轉角度儀,利用

2017-11-24 19:00:47

編碼器的工作原理是什么?如何通過波形得出正反轉的判據呢?編碼器的程序結構如何實現?

2021-10-14 06:36:49

DTMF 解碼器原理

2023-10-27 08:29:53

AE400系列E1接口音頻編解碼器,是采用先進數字處理芯片,使用先進的FPGA、數字編解碼轉換和時鐘恢復技術方法設計的。適用于廣播節目源傳輸的設備。音頻編碼器是將輸入的立體聲音頻信號或AES數字音頻

2011-03-02 20:51:53

H.264解碼器中CABAC硬件加速器怎么實現?

2021-06-07 06:48:58

HCTL-2020 解碼器及其在多關節機器人運動控制中的應用編碼器位置檢測通道的擴展是多軸運動控制系統開發中經常遇到的技術問題。該文詳細介紹了HCTL -2020 解碼器的工作原理,設計了它與DSP

2009-12-17 16:12:31

為什么要用編碼器?STM32編碼器的原理是什么?

2021-11-24 07:32:10

;encode.h" int main(void) {u16 count;//編碼器計數delay_init();//延時函數初始化uart_init(115200);//串口初始化

2018-07-02 02:52:21

正交編碼解碼的原理是什么?STM32正交編碼器怎么進行測速?

2021-11-16 08:04:07

、XviD、MPEG、QuickTime 等,只要使用 VideoInspector 載入需要測試的影片,程序馬上就能告訴您該影片是由何種視頻以及音頻編碼方式組成,當計算機缺少該解碼器時,程序會自動開啟解碼器下載功能,按下載后即可連接到解碼器下載網頁。

2009-03-02 10:35:58

【用途 應用】 編碼解碼器【性能 參數】 采用28PIN5x5x0.9mm的QFN封裝,WM8731是一款適合于語音應用的CODEC(編碼解碼器),它能為自身的MIC(麥克風)輸入提供偏置電壓,內部

2018-05-07 13:53:57

本節知識我們講解如何用FPGA建立正交解碼器正交解碼器FPGA是最適合建立正交解碼器。正交信號是什么? 正交信號是兩個信號產生相位差90度。機械系統中,它們被用來確定軸(或旋轉)運動。這里是一軸

2012-03-15 09:29:46

本帖最后由 松山歸人 于 2021-5-28 10:58 編輯

大家好!特邀趙云老師為大家講解增量型編碼器與絕對型編碼器的原理與分類希望對大家學習有所幫助,請持續關注,我們會繼續更新!配套講解文本見附件:

2021-05-28 10:52:37

為什么要用電機驅動?TB6612電機驅動怎么實現?為什么要用電機編碼器?電機編碼器怎么使用?

2021-10-20 07:36:53

光柵編碼器可分為兩大類,一是旋轉編碼器,用于轉角、轉速的測量;二是直尺型編碼器,用于直線位移、運動速度的測量。在旋轉編碼器中,又可分為絕對式編碼器和增量式編碼器。

2019-10-18 09:03:30

根據維特比解碼器數據表,硬編碼不能進行擦除(外部穿孔)(即僅對軟編碼有效)。如果我有硬輸入,我將如何解碼呢?我已經在解碼器之前解析了我的數據。我現在需要知道的是,如果我有一個硬輸入,我將如何使我

2019-03-14 10:19:54

概述:CS98100是一款用于DVD視盤機上的內置有TV編碼器的整合型解碼器。該芯片支持MPEG1/MPEG2解碼,支持AC-3和DTS音頻格式解碼。可將輸入的節目復用碼流進行解碼,并直接輸出模擬的視頻信號和音頻串行數據。該芯片采用+3.3V與+1.8V兩組供電方式,其封裝為208腳LQFP形式。

2021-05-17 06:36:42

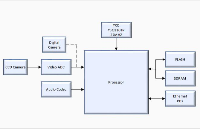

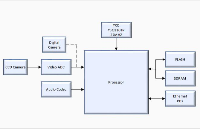

的電磁兼容(EMC)。電源。位置解碼和/或數字協議主站的信號處理。 圖2:工業驅動器/變頻器上位置反饋接口模塊的簡化方框圖具有RS-485或RS-422接口的增量型數字HTL/TTL編碼器和絕對型

2018-09-05 16:07:42

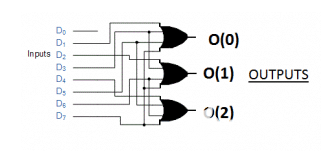

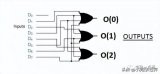

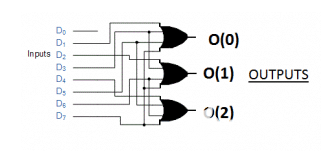

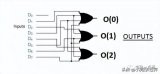

介紹FPGA開發板上組合邏輯電路的實現,這些實例包括在數字邏輯設計課程中所熟知的部分中規模集成電路:優先編碼器、多路復用器以及加法器,最后還將介紹算術邏輯單元ALU的實現。優先編碼器實驗原理在數字系統中

2022-08-04 17:39:32

描述 TIDEP0036 參考設計演示了如何在 TMS320C6657 器件上輕松運行經 TI 優化的 Opus 編碼器/解碼器。由于 Opus 支持各類比特率、幀大小和采樣率且均延遲極低,因而

2022-09-22 06:32:42

有沒有大佬弄過 基于FPGA的BISS-C協議編碼器解碼,想問一下該怎么搞,有償,或者有沒有現成的產品可以幫忙解碼?

2023-05-23 17:17:13

基于HAL庫的編碼器模式怎么實現?

2021-11-16 08:57:27

編碼器實現指標分析LDPC碼編碼器實現編碼器方案驗證與優缺點分析

2021-04-30 06:08:10

描述TIDEP0036 參考設計演示了如何在 TMS320C6657 器件上輕松運行經 TI 優化的 Opus 編碼器/解碼器。由于 Opus 支持各類比特率、幀大小和采樣率且均延遲極低,因而適用于

2018-08-20 06:02:22

如何使用編碼器接口實現定位?

2022-02-11 07:32:50

您好!如何使用PSoC Creator中的塊構建NRZI解碼器和編碼器。當做

2019-09-10 09:26:54

JpegDecInit error openmax_il/source/decoder/codec_jpeg.c:1045

在那個線程中,NXP TechSupport 回復了這個

我想知道如何修改包 gstreamer 以支持使用 VPU 的 jpeg 解碼器和編碼器

2023-04-23 11:29:41

增量型編碼器的工作原理是什么?誤碼脈沖產生的原因及其濾除方法是什么?

2021-04-29 06:09:49

如何利用旋轉編碼器實現計數?

2022-01-21 07:28:40

紅外遙控解碼器的電路原理是什么?如何去制作紅外遙控解碼器?其步驟流程是怎樣的?

2021-04-19 07:00:14

大家好。我需要為 ADAT 協議實現編碼器/解碼器,我不知道某些 STM32 MCU 是否能夠做到這一點。正如您在圖像中看到的那樣,編碼器必須接收四個 I2S 流并將它們編碼為 ADAT 協議

2022-12-13 06:03:37

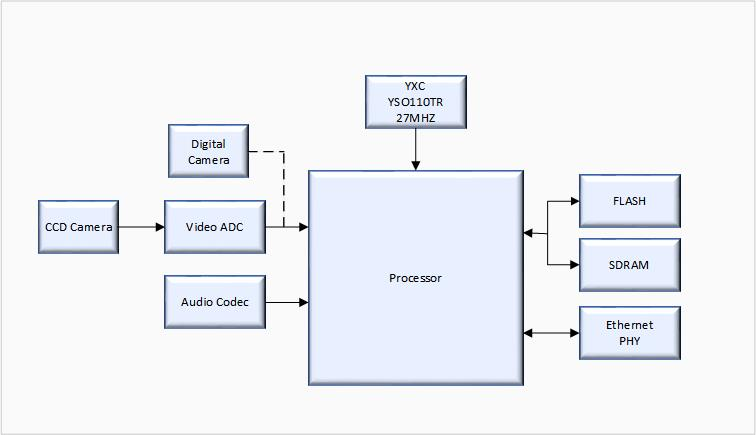

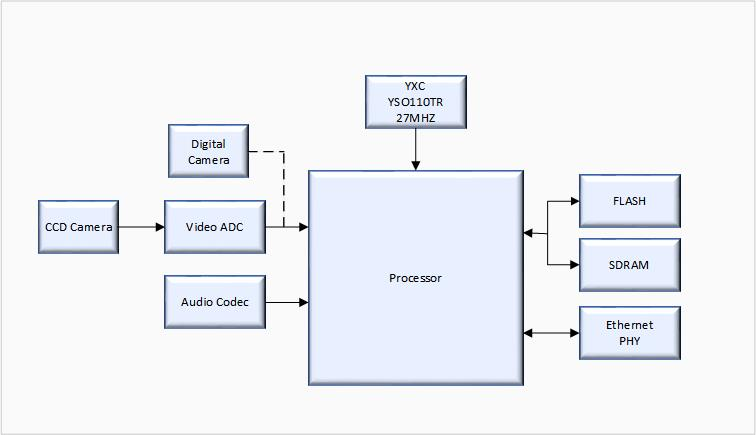

筆者針對市場客戶的需求,設計并實現了一款以TVP5150為視頻輸入解碼器、以PCMl801為音頻輸入采集電路、以TMS320DM642型DSP為核心處理器的多路視頻采集兼壓縮處理PCI板卡,并將其應用于構建高穩定性、高魯棒性的多媒體數字監控系統,取得了較好的社會效益和經濟效益。

2021-06-08 06:56:13

編碼器 的小型經濟型-低、中分辨率型 E6A2-C 產品介紹:小型編碼器■適應定位的需要。備有帶原點輸出(Z相)型。■外徑φ25的尺寸,備有分辨率500P/R的產品。 增量型 旋轉式編碼器 的小型經濟型

2021-11-12 14:46:17

歐姆龍E6A2編碼器☆Φ25的小型經濟型。☆低、中分辨率型。☆電壓:5-12V或12-24V。☆輸出信號:A相☆輸出形式:集電極、電壓歐姆龍E6B2編碼器 ☆外型尺寸:Ф40*30。 ☆軸徑:Ф6

2021-11-06 15:44:49

我們想將 H264 編碼器解碼器添加到我們現有的 g-streamer 構建中,作為我們 Linux 5.10 yocto 構建的一部分。如何修改作為 yocto 構建一部分的 G-streamer

2023-03-17 06:20:29

你好,這是我的版本的正交解碼器與按鈕開關自定義組件(QudDeCysw),它被設計用于將旋轉軸編碼器連接到PSoC4和PSoC5。已經創建了在有限或耗盡UDB/PLD空間的項目中節省硬件資源的必要性

2018-12-28 15:34:33

本文實現了ffmpeg解碼器到龍芯3B的移植,并針對龍芯3B實現了對向量擴展指令支持的特點,對ffmpeg解碼器進行了手工向量化。

2021-06-02 06:57:33

我想實現這樣的效果:先讀取編碼器上的角度值,然后連續發相位相差90度的脈沖去改變角度值(也就是用程序控制編碼器的旋鈕)并且不斷讀取編碼器上的值,我是用PCI-6221(37Pin)采集卡的,求各位大神幫幫忙。。。。。

2013-07-22 17:25:38

本文針對旋轉編碼器在工業現場中的應用,基于LPCI768硬件平臺,設計出一種旋轉編碼器采集模塊,該模塊內部具有高精度分析、整形、解碼電路,可同時對2路編碼器輸入信號進行分析、解碼。

2021-05-21 06:47:35

基于Linux的系統框架和集成開發環境怎么搭建?怎么實現基于IPP的嵌入式音頻解碼器的設計?

2021-06-04 07:03:18

在進入關于編碼器和解碼器的現實之前,讓我們對復用進行簡要的思考。通常我們會在需要將一些輸入信號一次一個地加載到一個單獨負載的應用程序中。選擇輸入信號中的一個輸入信號的過程稱為多路復用。這種操作

2020-09-01 17:48:10

求推薦mp3解碼器,能同時實現mp3的解碼和dac功能的芯片,像VS105

2016-01-06 17:54:07

為傳感器產生的信號時,就通過另一個I/O口向解碼器的單片機發送一組編碼,而解碼器的單片機則首先判斷當前準備接收的數據是編碼器發送的編碼還是解碼寫入器發送的解碼。當判斷是解碼寫入器發送的解碼時,解碼器

2011-08-19 09:57:50

良好的聲音質量,語音編碼和解碼免費Speex音頻編解碼器的微控制器

2020-05-29 11:52:03

嗨,我需要一個支持以下ipcores的xilinx fpga:mpeg-4編碼器,UART和SPI。我還需要一個支持UART和mpeg-4的解碼器。我猜他們中的大多數都支持UART和SPI內核,但不

2019-01-18 17:11:03

本帖最后由 一只耳朵怪 于 2018-5-31 10:56 編輯

在8168中按照官方描述應當是支持16CHD1視頻采集和編碼的。而實際在內部只有3個硬件編解碼器。請問如何才能實現編碼器的復用

2018-05-31 03:48:39

,不宜實現小型化。增量式光電編碼器不具有計數和接口電路,一般輸出A、B、Z脈沖信號,價格較低,在實際工程中比較常用。文中設計了一個基于FPGA的簡單且精度高的接口電路,其結構簡單、性能可靠。具有濾波

2019-06-10 05:00:08

基FPGA Cyclone II_EP2C5 EP2C8的頻率計

基FPGA_Cyclone_II_EP2C5/EP2C8的頻率計

功能描述:按4*4鍵盤上的1,2,3...號按鍵可依次測出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 什么是音頻編解碼器?

編解碼器(編碼器/解碼器)轉換成模擬信號的數字碼流,另一個相同的編解碼器轉換為數字流回到成模擬信

2009-05-03 23:48:59 3870

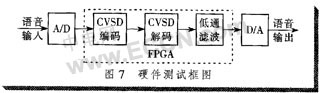

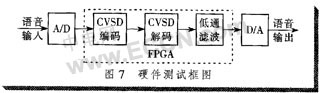

3870 基于FPGA的32Kbit/s CVSD語音編解碼器的實現

64 Kbit/s的A律或μ律的對數壓擴PCM編碼在大容量的光纖通信系統和數字微波系統中已得到廣泛應用,但由于占用較大的傳輸帶寬

2010-01-12 09:52:15 729

729

本系統采用經濟型的Cyclone II FPGA芯片作為核心,基于Nios II軟核處理器,采用軟硬件結合的方式設計數碼相框并實現。

2013-01-08 11:07:15 4283

4283

800Mbps準循環LDPC碼編碼器的FPGA實現

2016-05-09 10:59:26 37

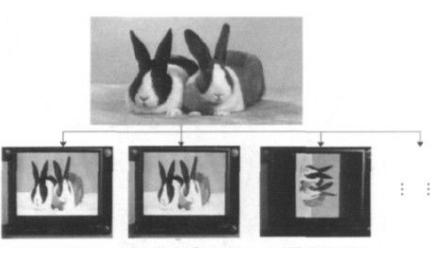

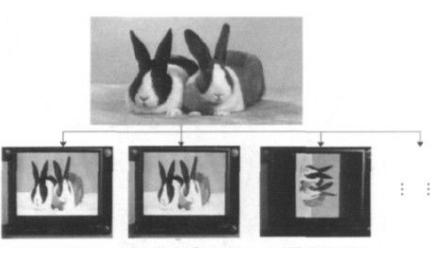

37 基于FPGA的經濟型MPEG2運動圖像編碼器IP核設計

2016-08-30 15:10:14 9

9 一種高速卷積編解碼器的FPGA實現

2017-02-07 15:05:00 19

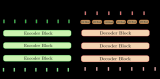

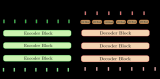

19 在本文中,利用自編碼神經網絡的編碼器對輸入數據進行編碼,所得到隱含層的輸出數據稱為原始數據的編碼;該編碼數據經過自編碼神經網絡的解碼器實現數據解碼,從而恢復原始輸入數據。下面參照圖1所示的自編碼神經網絡結構,介紹自編碼神經網絡的前向計算過程,首先計算隱含層n個神經元的輸出如式(1):

2018-04-18 08:58:10 4397

4397

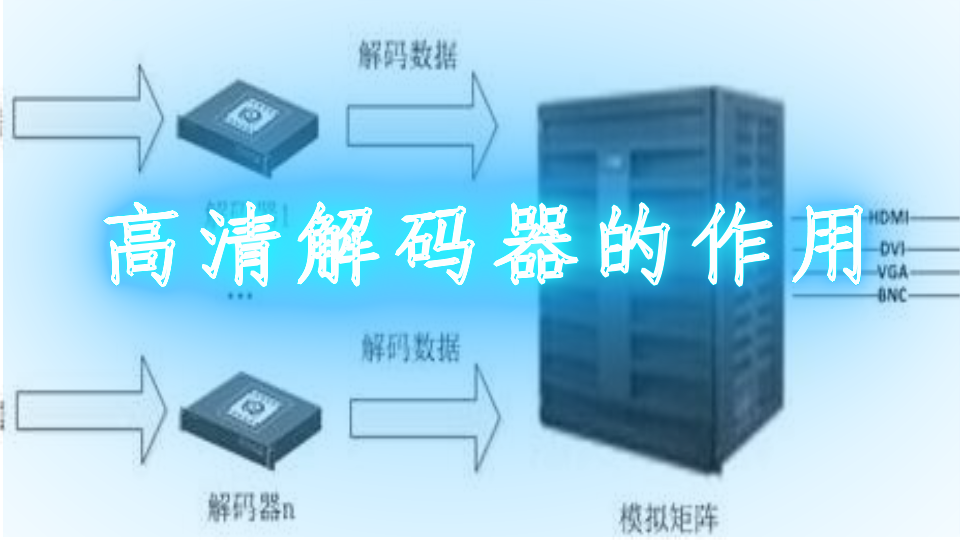

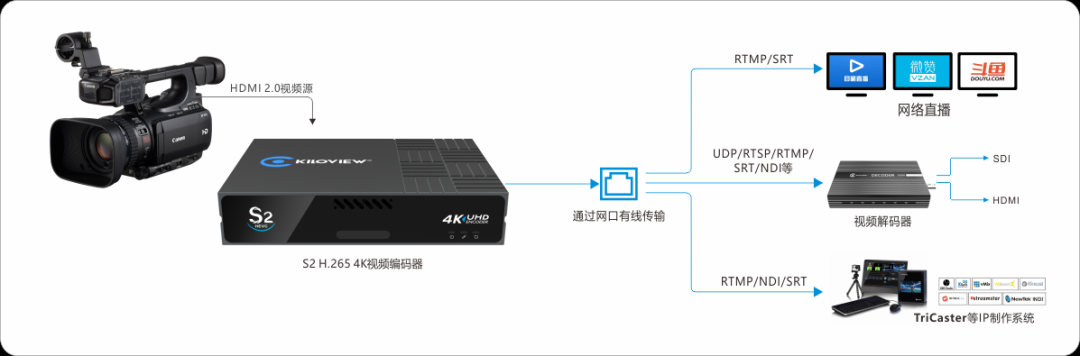

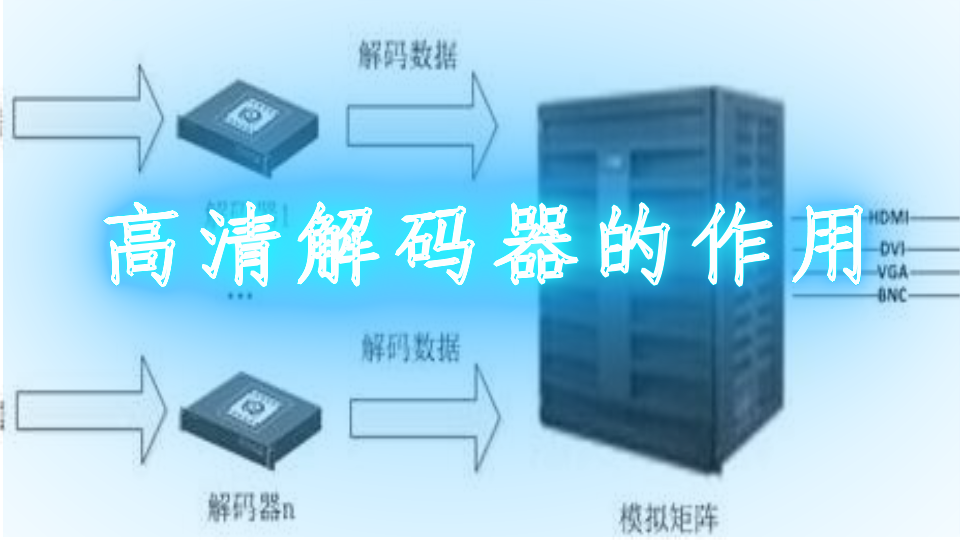

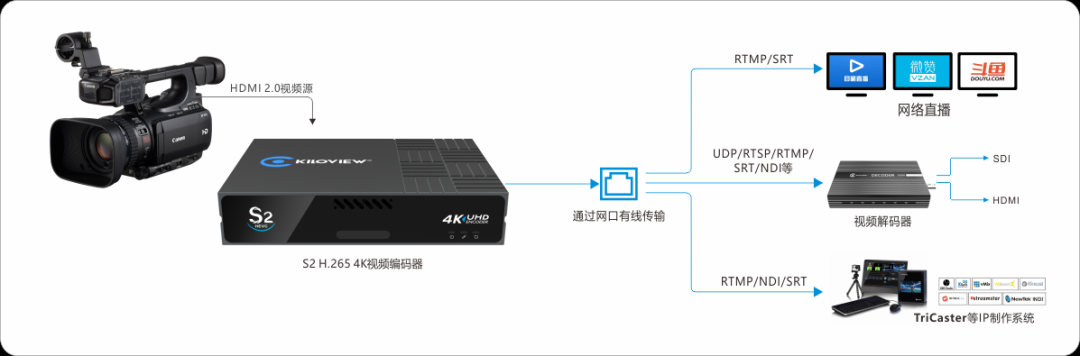

編碼器指的是對視頻信號進行壓縮,解碼器主要是將壓縮的視頻信號進行解壓縮。目前做直播的很多都是采用的編碼器,客戶端可以采用解碼器或軟件播放器解碼。

2018-08-02 17:23:49 33564

33564 高清解碼器(xunwei)的主要作用在于接收前端高清編碼圖像或網絡攝像頭信號并解碼,然后通過自身的各種視頻輸出接口,如HDMI、DVI、SDI、VGA、BNC輸出顯示到顯示設備上。編碼器和解碼器

2018-12-10 15:47:43 12046

12046

繼非常成功的第一代Cyclone?設備系列之后,Altera?Cyclone II FPGA將低成本的FPGA密度范圍擴展到68416個邏輯元件(LES),并提供多達622個可用I/O管腳和多達

2019-03-25 08:00:00 14

14 極性編碼器/解碼器軟IP核心支持極性編碼和解碼。極性代碼是可配置的,可以逐塊使用。

注:在本文檔中,塊是編碼器或解碼器處理的原子數據單元的通用術語。代碼字是編碼塊的特定形式,在討論用于生成代碼

2019-05-05 08:00:00 5

5 解碼器、MG300媒體網關均支持解碼NDI|HX2。 下面我們來介紹如何使用視頻解碼器解碼NDI|HX2的視頻流,下圖是E1-NDI編碼器和D300解碼器使用NDI|HX2傳輸連接示意圖: 編碼器和解碼器

2020-11-04 11:22:40 1861

1861 RTMP Server是RTMP/HLS流媒體服務器,通過RTMP Server服務功能可以將視頻編碼器可以直接將視頻流通過RTMP傳輸到解碼器進行解碼和輸出,無需RTMP中轉平臺。(在局域網內延遲

2021-02-23 14:27:17 2300

2300 視頻處理芯片IP的領先提供商Allegro DVT今天發布了其D3x0和E2x0解碼器和編碼器IP的新版本,其采樣大小擴展至12位,色度采樣從4:2:0和4:2:2增至4:4:4。 包括云游戲和汽車

2021-10-20 16:23:27 1138

1138 AD938A:雙HDMI接收機,多格式HDTV視頻解碼器和RGB圖形編碼器

2021-04-30 18:29:41 3

3 ,在常見端到端翻譯模型的基礎上,利用代碼抽象語法樹將源代碼的結構信息嵌入到編碼器解碼器翻譯模型中,提出一種基于結構感知的雙編碼器解碼器模型,該模型綜合考慮源代碼的序列信息與代碼內部的結構特性。在真實數據集

2021-05-26 15:38:38 5

5 編碼器和解碼器是組合邏輯電路,在其中,主要借助布爾代數實現組合邏輯。今天就大家了解一下編碼器和解碼器電路,分別從定義,工作原理,應用,真值表幾個方面講述一下。

2022-11-03 09:22:57 4878

4878

電子發燒友網站提供《PyTorch教程10.6之編碼器-解碼器架構.pdf》資料免費下載

2023-06-05 18:12:48 0

0 電子發燒友網站提供《PyTorch教程10.7之用于機器翻譯的編碼器-解碼器Seq2Seq.pdf》資料免費下載

2023-06-05 18:14:16 0

0 10.6. 編碼器-解碼器架構? Colab [火炬]在 Colab 中打開筆記本 Colab [mxnet] Open the notebook in Colab Colab [jax

2023-06-05 15:44:27 515

515

序列組成,我們通常依賴編碼器-解碼器架構(第10.6 節)。在本節中,我們將演示編碼器-解碼器架構在機器翻譯任務中的應用,其中編碼器和解碼器均作為 RNN 實現(

Cho等人,2014

2023-06-05 15:44:28 498

498

與基于 RNN 的編碼器-解碼器模型類似,基于 transformer 的編碼器-解碼器模型由一個編碼器和一個解碼器組成,且其編碼器和解碼器均由 殘差注意力模塊 (residual attention blocks) 堆疊而成。

2023-06-11 14:17:34 1145

1145

? Vaswani 等人在其名作 Attention is all you need 中首創了?基于 transformer?的編碼器-解碼器模型,如今已成為自然語言處理 (natural

2023-06-12 17:08:11 407

407

基于 transformer 的編碼器-解碼器模型是 表征學習 和 模型架構 這兩個領域多年研究成果的結晶。本文簡要介紹了神經編碼器-解碼器模型的歷史,更多背景知識,建議讀者閱讀

2023-06-16 16:53:21 432

432

基于 transformer 的編碼器-解碼器模型是 表征學習 和 模型架構 這兩個領域多年研究成果的結晶。本文簡要介紹了神經編碼器-解碼器模型的歷史,更多背景知識,建議讀者閱讀

2023-06-20 15:42:00 429

429

編碼器和解碼器是組合邏輯電路,在其中,主要借助布爾代數實現組合邏輯。今天就大家了解一下編碼器和解碼器電路,分別從定義,工作原理,應用,真值表幾個方面講述一下。

2023-07-14 09:07:18 1530

1530

視頻解碼器和視頻編碼器在數字通訊、音視頻壓縮領域有著廣泛的應用。視頻編碼器作為視頻源的發送端,若接收端如果是?PC?機或顯示設備就需要通過解碼器進行解碼播放。

2023-08-14 14:38:42 829

829

視頻解碼器和視頻編碼器是數字信號處理中常用的設備,它們在數據的傳輸和轉換中發揮著重要作用。

2023-08-23 09:40:01 379

379

視頻解碼器和視頻編碼器是數字信號處理中常用的設備,它們在數據的傳輸和轉換中發揮著重要作用。

2023-08-28 11:31:26 330

330

電子發燒友網站提供《LDPC編碼器解碼器產品簡介(v2.0).pdf》資料免費下載

2023-09-13 15:21:48 2

2 解碼器/編碼器?DIP164.75~5.25V封裝:DIP16_19.3X6.4MM

2022-08-19 15:57:42 2

2 解碼器/編碼器DIP164.75~5.25V封裝:DIP16_19.3X6.4MM

2022-08-19 15:57:49 0

0 (Autoencoder),它是一種無監督學習的神經網絡模型。自動編碼器由兩部分組成:編碼器和解碼器。編碼器負責將輸入數據轉換為低維表示,解碼器則將低維表示映射回原始輸入空間。這種結構能夠通過編碼器的特征提取和表示能力來壓縮原始數據并保持盡可

2024-01-23 10:58:07 415

415 編碼器和視頻解碼器,編碼器實現對攝錄的視頻進行壓縮,解碼器對接收到的壓縮視頻解壓縮。 視頻編解碼器是視頻傳輸

2022-07-25 10:31:24

電子發燒友App

電子發燒友App

評論