目前ASIC設計的規(guī)模在不斷擴大、復雜度在不斷增加,與此同時,日益激烈的競爭使得今天的電子產(chǎn)品市場對產(chǎn)品進入市場的時間極為敏感。如何提高驗證的效率已成為一個巨大的挑戰(zhàn)。當前對ASIC設計者開放的3個主要驗證選擇是仿真(emulation)、模擬(simulation)和FPGA原型(prototypes)開發(fā)。隨著FPGA的門數(shù)越來越高,功能越來越強大,使其成為了ASIC驗證的強有力工具。

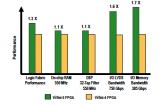

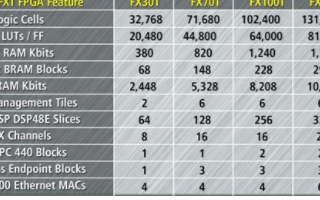

Virtex-5 LX系列是Xilinx公司推出的新一代65nm工藝FPGA。它與上一代90 nm的FPGA相比,速度平均提高30%,容量增加65%;同時動態(tài)功耗降低35%,靜態(tài)功耗保持同樣低,使用面積減小45%。Virtex-5 LX系列還通過性能優(yōu)化的IP模塊擁有了550 MHz時鐘技術。高性能的SelectIO特性,提供了到667 Mbps DDR2SDRAM和1 200 Mbps QDR II SRAM等外部存儲器的最快連接。

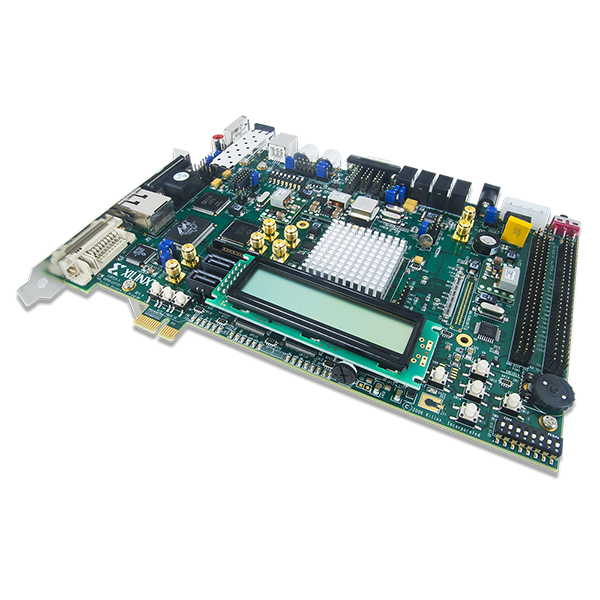

本文基于Virtex-5 LX110驗證平臺的設計,探索了高性能FPGA硬件系統(tǒng)設計的一般性方法及流程,以提高FPGA的系統(tǒng)性能。

1 系統(tǒng)設計實現(xiàn)

利用FPGA可以很好地對ASIC的功能進行驗證。通過常年對AISC原型驗證平臺的設計和測試發(fā)現(xiàn),對于某些ASIC,特別是用于通信領域的ASIC,如果能夠在原型驗證階段就可以在實際環(huán)境中對其性能進行嚴格的評估,對其采用的算法進行驗證,便能夠很好地保證芯片的性能,從而加快產(chǎn)品的上市時間。利用通用的FPGA驗證平臺,例如DiniGroup,其價格昂貴且與系統(tǒng)進行互聯(lián)也比較困難,不滿足對系統(tǒng)進行現(xiàn)場測試的高度集成性和便攜性的要求。解決這一問題的最好方法就是,根據(jù)需求直接將FPGA集成到系統(tǒng)當中,設計出適用于現(xiàn)場評估測試的單板驗證平臺。

1.1 系統(tǒng)資源評估

(1)FPGA資源

Virtex-5 LX110包含17 280個Slice,110 592個log—ic cell,12個DCM和6個PLL;提供高達800個I/O引腳,23個I/O板塊,其中每個I/O都可設置成差分輸出。LX110支持多種I/O類型,需要根據(jù)系統(tǒng)不同模塊的輸入/輸出特性選擇合適的I/O類型,并將所用到的I/O進行合理的布局規(guī)劃。各種不同I/0類型的電氣特性約束嚴格限制了引腳位置的指定,同時I/O引腳的引出位置影響到BGA封裝的板級走線,因此需要綜合考慮以便對I/O引腳資源進行合理的劃分。

(2)時鐘分布

系統(tǒng)中的時鐘信號通常是串擾和EMI問題的根源,因此需要對其進行合理的規(guī)劃。時鐘信號的完整性是保證系統(tǒng)正常工作的重要因素,在仿真中特別需要關注。利用FPGA提供的DCM資源可以減少系統(tǒng)所需的時鐘信號器件,從而減少板級時鐘網(wǎng)絡。PCB布線時應注意將時鐘信號和數(shù)據(jù)信號進行隔離,以避免串擾的產(chǎn)生。

(3)FPGA配置模塊

設計合理、適用的FPGA配置方案。Virtex-5提供的配置模式多達8種,本設計選用Xilinx公司提供的PROM配置芯片,通過JTAG接口將配置文件寫入PROM中,系統(tǒng)上電后FPGA和PROM按所設定的配置模式將配置文件從PROM下載到FPGA里,利用FPOA+PROM的組合可以有效地簡化配置電路設計。此外還可以通過JTAG接口對FPGA進行在線配置。

(4)模數(shù)轉換模塊

系統(tǒng)集成高速雙路模數(shù)轉換器,支持高達105 Msps的采樣速率,每路10位輸出。

(5)I/O接口模塊

系統(tǒng)為各種不同的I/O類型提供了相應的接口,支持LVCMOS33、LVCMOS25、LVDS_25類型的I/O。

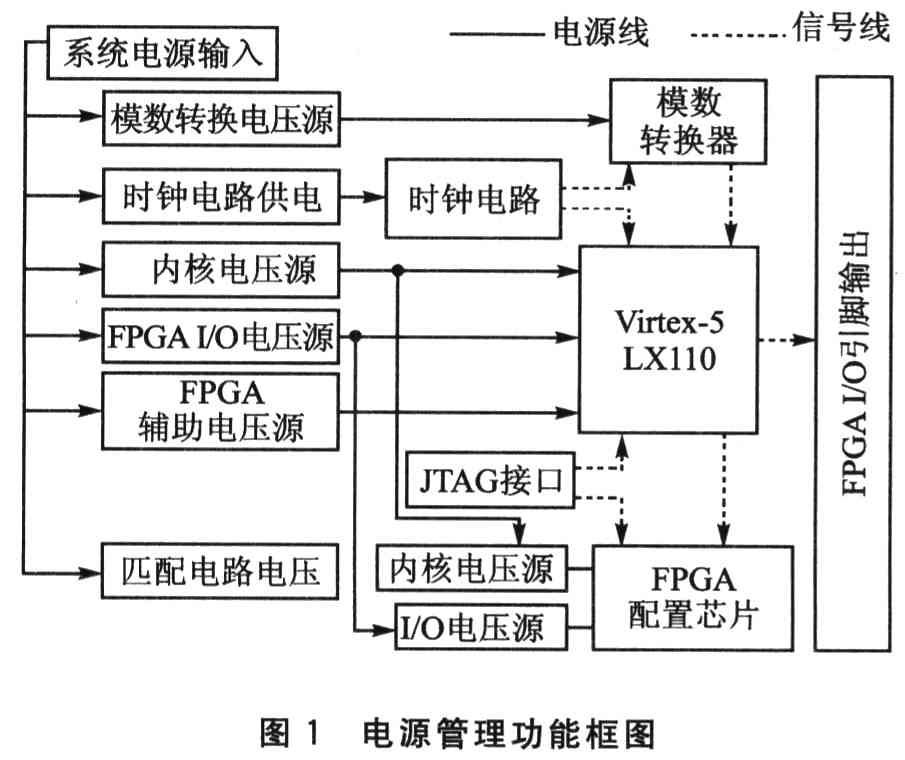

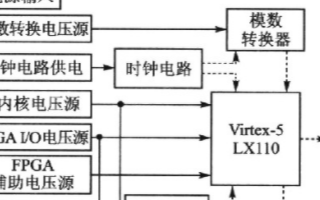

(6)電源管理模塊

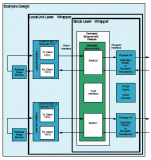

FPGA所需電源主要有3個:內核電壓(VCCINT)、I/O電壓(VCCO)、輔助電路電壓(VCCAUX)。其他如A/D電壓、FPGA配置芯片電源(內核電壓和I/O電壓)、板級所需的時鐘電路供電及指示燈供電電壓,總共需提供8個電源。系統(tǒng)功能框圖如圖1所示。

1.2 原理圖符號生成

FPGA的可定制特性需要按特定應用進行原理圖符號生成。首先,從特殊用途引腳的指定開始,例如電源、地引腳、參考電壓引腳以及配置引腳等。只有對這些引腳的正確指定才能保證PCB布板及走線的正確連接。下一步是將邏輯I/0和封裝形式連接起來,可以利用FPGA的設計開發(fā)環(huán)境來指定,然后導入到PCB布板環(huán)境中。在FPGA的設計開發(fā)環(huán)境中,用戶可以利用圖形界面對引腳進行指定,然后在實現(xiàn)過程中,F(xiàn)PGA布局布線工具能自動地對引腳進行指定。在FPGA的設計開發(fā)環(huán)境中,能夠進行DRC檢驗以保證引腳的合法性。

接下來為FPGA創(chuàng)建結構化的原理圖符號。由于FPGA本身I/0的復雜性和可配置性,將整個FPGA分割為多個子模塊能夠有效地減輕設計的復雜度,也便于管理和檢查。圖2顯示了利用Mentor Dxdesigner’原理圖符號生成向導生成模塊化原理圖符號的設計過程。原理圖符號生成之后就可以在原理圖設計環(huán)境進行原理圖的設計,指定各個模塊的連接關系。

1.3 PCB疊層定義

對。PCB疊層、材料和尺寸的設計需要考慮以下因素:

◆走線層的數(shù)量需要考慮到封裝特性、設計所用的I/()數(shù)目以及間距;

◆芯片互聯(lián)線的數(shù)據(jù)傳輸速率,信號的上升、下降時間對PCB材料、尺寸以及走線方式和制板工藝的限制;

◆元件所需的不同供電和參考電壓,對電源層的規(guī)劃和設計;

◆成本問題(利用盲孔、盲埋孔、微通孔等工藝能有效地減少疊層數(shù)目,以達到降低成本的目的)。

該設計中,與FPGA互聯(lián)的信號線約為130條,包括配置電路信號線、時鐘信號線及其他I/O信號。選用上下兩個走線層。考慮到多個電源供電,設置2個電源平面、2個地平面。整個PCB采用6層板結構設計,信號層目標阻抗50 Q。

利用HyperLnyx疊層設計如圖3所示。

1.4 散熱管理

FPGA支持的速率越高,本身的資源密度越大,因此要關注應用中的散熱管理問題。對FPGA的功率消耗進行估計,以決定是否需要散熱系統(tǒng)。

XPower Estimater是一款基于Excel的軟件,通過對設計資源的利用,包括邏輯資源、DCM、PLL、I/0類型、觸發(fā)率(toggling rate),以及其他與FPGA設計密切相關的信息,對FPGA的功耗進行估算。圖4為利用XPE進行設計功耗估算的截圖。

1.5 信號完整性分析

在時域和頻域對設計的連接拓撲結構(PCB疊層、驅動端、接收端、連接器、通孔等等)進行信號完整性分析,目的是要評估和減小信號從驅動端到接收端的反射、串擾以及EMI/EMC等問題。通過仿真分析得到的約束形式能有效指導PCB布局布線工具進行l(wèi)ayout設計。進行信號完整性分析,首先要確定與FPGA相接的外圍器件的I/O特性及其約束,進而對FPGA采用何種I/0類型以及端接匹配機制有一個大致的了解,然后是通過仿真對采用的I/O類型及端接電路的各個參數(shù)進行定義及優(yōu)化。

(1)前仿真

S1分析一般主要從高速信號、對時序要求較高的信號、走線最長的信號、負載最多的信號開始,因為這些信號線通常最容易引起SI問題。確定關鍵信號在仿真環(huán)境中建立起相應的拓撲模型。

通過仿真能定義出最長連接走線以及其他滿足噪聲裕量(匹配電路、端接方式等)的網(wǎng)絡屬性。確定FPGA驅動緩沖特性,例如I/O標準、驅動能力以及回轉率,使信號完整性問題、EMI/EMC問題最小化,同樣也對接收端I/0屬性進行定義。進行串擾仿真以保證相鄰走線不會引起串擾問題。定義端節(jié)匹配方式。

圖5、6是對時鐘網(wǎng)絡匹配前和匹配后進行的仿真圖形對比。

通過前期的大量仿真分析可以很好地保證設計的成功率。

(2)后仿真

在PCB Layout完成之后還需要對整個布好的PCB板進行仿真,后仿真更強調對串擾和EMI的分析,如圖7所示。只要任何一個網(wǎng)絡不滿足設計需求,就需要對該網(wǎng)絡進行修改,設計新的走線路徑,直至滿足設計需求。

1.6 電源分布系統(tǒng)(PDS)設計

PDS分析的目的,是要評估數(shù)字器件所需的瞬態(tài)電流,以提供一條良好的供電路徑。電流路徑中的寄生電感是導致供電網(wǎng)絡設計失敗的根源(例如地彈噪聲)。一種可能的情況是,IC信號應當發(fā)生翻轉時卻沒有翻轉;另一種更常見的情況是引起系統(tǒng)抖動(Jitter)變大,從而導致時序錯誤。在兩種情況中,都將造成系統(tǒng)工作不正常或者超出設計規(guī)范定義的范圍。

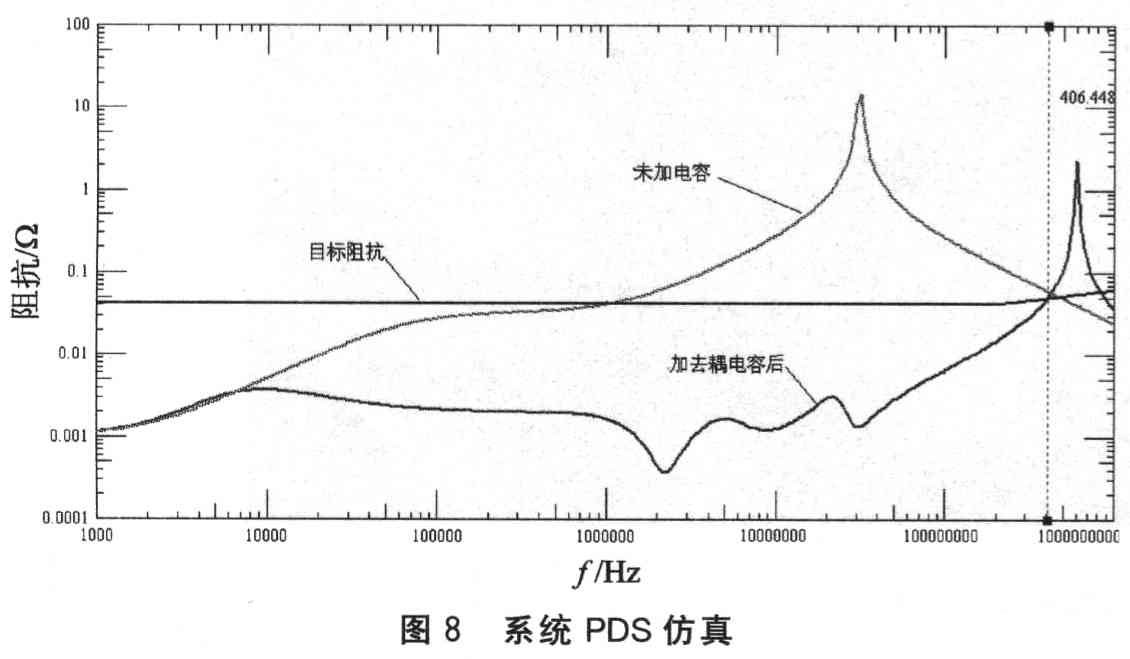

首先檢驗FPGA的靜態(tài)和瞬態(tài)電流需求,瞬態(tài)電流由設計的時鐘域、DCM利用率、開關邏輯數(shù)目以及同時翻轉輸出(SimuItaneous Switch Output,SSO)等因素決定,靜態(tài)和瞬態(tài)電流的大小可以利用XPE或XPower來取得。設計滿足需求的電源去耦網(wǎng)絡,并通過仿真確定所需電容值及其數(shù)量,同樣,電容在板上的擺放位置對PDS的影響也很重要。圖8表明了調整前后電源層阻抗的仿真結果。通過對電源去耦網(wǎng)絡的悉心設計,可以有效降低FPGA工作頻率范圍內的電源阻抗。阻抗越低,意味著系統(tǒng)對瞬態(tài)電流的需求越能及時做出反應,因此也越能減小電源的供電噪聲。

圖8是對電源VCCO對地的頻率一阻抗曲線的仿真圖。通過對電源去耦網(wǎng)絡的設計,可以保證在400 MHz的范圍內,電源阻抗值是小于目標阻抗的。

1.7 可測試性設計

隨著布線密度的增加,很難對PCB的每個信號都進行物理連接檢測,特別是對于BGA封裝的芯片。另外,對高速信號添加測試點還會導致信號路徑阻抗不連續(xù),引起反射,從而使信號完整性降低。為解決這一矛盾,在設計中首先對FPGA和與其相連的外圍電路的每個信號連接生成了一個測試設計,利用FPGA的邏輯資源對FPGA獲取到的輸入信號與期望的信號值進行比較,對所得的結果通過JTAG端口或者其他外圍顯示電路(如LED)顯示輸出。

2 結 論

本文對驗證平臺硬件設計中的FPGA相關分析進行了詳盡描述。目的是通過設計流程前期的大量分析和仿真,將FPGA在整個設計系統(tǒng)的工作特性以及系統(tǒng)環(huán)境對FPGA的影響作用進行模擬,得出的結果轉化為設計約束導人至PCB Layout的環(huán)境中,能有效地提高一次設計成功的機率。按照此流程設計的Virtex-5驗證平臺工作正常,達到了預期的設計目的。

責任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論