在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4 平臺

2011-10-21 16:13:51 1270

1270

針對不同類型的器件,Xilinx公司提供的全局時鐘網絡在數量、性能等方面略有區別,下面以Virtex-4系列芯片為例,簡單介紹FPGA全局時鐘網絡結構。

2013-11-28 18:49:00 12149

12149

器件中選型。Xllinx公司的主流器件有Spartan-3E、Spartan-3A、Virtex-4LX、Virtex-4 SX、Virtex-4 FX、Virtex-5 LX、Virtex

2020-11-19 15:39:56 4945

4945

數字信號的輸入和輸出。對于在FPGA器件內實現的任何時序邏輯應用,失去了時鐘信號便意味著信號的傳輸將處于停滯狀態。時鐘信號的重要性可見一斑。(特權同學,版權所有)圖3.6 理想時鐘波形FPGA器件

2019-04-12 01:15:50

FPGA實現高速FFT處理器的設計介紹了采用Xilinx公司的Virtex - II系列FPGA設計高速FFT處理器的實現方法及技巧。充分利用Virtex - II芯片的硬件資源,減少復雜邏輯,采用

2012-08-12 11:49:01

, Inc.) 日前宣布隆重推出EasyPath-6FPGA,該產品為高性能 FPGA 進入量產器件提供了六周內即可實現的總成本最低、風險最小的的解決方案,在所有FPGA降低成本解決方案中轉入量產時間

2012-08-11 18:17:16

VIRTEX-4 - Tri-Mode Embedded Ethernet MAC Wrapper v4.4 - Xilinx, Inc

2022-11-04 17:22:44

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

親愛的社區成員,我正在實施XAPP861中推薦的8x過采樣和數據恢復單元(DRU),以便在Virtex-4 FPGA上進行異步串行數據恢復。我通過3米DVI電纜接收了160bbps的8b10b編碼流

2020-06-18 16:00:28

我們正在使用Virtex-4 ML423平臺。是否有可能駕駛LVDS接頭接口(文檔UG087.pdf中沒有12),電壓不同于2.5伏?在ISE中,我在所需的端口上設置LVCMOS12,但我在LVDS

2019-08-14 08:45:01

嗨,我對Virtex-4中BRAM的工作頻率有疑問。如果有人知道BRAM的最大工作頻率是多少?提前致謝以上來自于谷歌翻譯以下為原文hi, I have a question about

2018-10-10 11:53:12

嗨,我使用Virtex6 LX75T和4個高速DAC設計了一塊電路板。我將每個DAC連接到一個FPGA io Bank,我使用MRCC引腳作為MMCM(差分)的時鐘輸入,4個引腳用于片外反饋。不幸

2020-06-16 10:06:19

嗨,我需要Virtex-4器件“xc4vfx12”的門數值。如果有任何公式,我們可以用它來計算設備的可用門數。 CLBS,切片和其他資源,請告訴我。感謝致敬,的Sandip

2020-06-18 07:02:27

大家好,我正在研究包括3個不同時鐘域的設計。我已經閱讀了這個帖子,我發現與virtex-II和virtex-4相比,virtex-5在MTBF中是最差的。對于較低和實用的MTBF,我沒有在同步器鏈

2020-06-12 09:27:03

嗨,XilinxIDF站點表明IDF僅支持Virtex-4,Virtex-5,Spartan-6和7系列FPGA。我可以在Xilinx Virtex-6 FPGA上使用IDF嗎?有沒有人嘗試過使用IDF和Virtex-6 FPGA?謝謝,季米特里斯

2020-07-08 15:56:53

親愛的先生,我們已經在我們的定制設計板上組裝了Virtex-4 FPGA BGA封裝,組裝后我們進行物理檢查時檢查所有電源接地之間是否短路。請告訴我們調試此問題的任何過程并刪除簡短。 FPGA的穩壓器電路與FPGA IC隔離問候薩蒂亞

2020-06-19 07:42:07

的bitgen以及SEM IP內核可以做到這一點,但據我所知它們不能與virtex-4一起使用。有沒有其他方法來估計virtex-4器件(XQR4VS??X55??)的基本位,以及我們如何計算同一器件的軟

2019-02-26 10:24:45

連接的設備及其相應的設備ID。 現在,為了配置FPGA器件,我找到了Virtex-4系列的步驟,但它們恰好與Spartan 3E的步驟略有不同。那么,任何人都可以讓我知道Spartan 3E系列FPGA

2019-06-12 09:45:38

Xilinx Virtex-II Pro 和 Virtex-II Pro X 器件能提供集成 PowerPC 內置技術的 FPGA,也是第一個能提供支持從 622 Mbps 到 10.3125

2013-09-06 16:28:27

本帖最后由 mr.pengyongche 于 2013-4-30 02:56 編輯

Xilinx Virtex-4 ML403嵌入開發平臺原理圖[url=www.0404.cc]

2012-08-17 09:12:44

描述 PMP9408 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現電流

2022-09-21 07:56:06

描述PMP9408 參考設計提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發器 (MGT) 供電時所需的所有電源軌。它利用一個 PMBus 接口來實現電流

2018-08-29 08:42:24

Virtex-4 XC4VFX12)。之后,我想將它移植到新平臺(即Virtex-5 XC5VFX70T),但我的ISE Foundation 10.1安裝不支持這個FPGA。我錯過了什么嗎? ISE

2018-11-15 11:30:24

你好,什么是運行EDK,Xilinx編程ML410或Virtex-4的最佳或至少可接受的要求?至于CPU速度,內存和磁盤容量?我現有的系統運行EDK樣品需要45分鐘以上!問候,Ramsin

2020-06-02 15:10:59

713.17 IOB寄存器和鎖存器723.18 實現操作符及產生模塊773.18.1 DSP48中運算符實現和模型生成(Virtex-4和Virtex-5器件)773.18.2 在乘法器中操作符實現

2012-04-24 09:18:46

是對時鐘相位的控制精度相對較差。 在通訊領域里,用光纖傳輸高速數據是一個比較常用的解決方案。A1tera公司的StatixⅡGX和StatixⅢGX系列[1],Xllinx公司的Virtex-4

2012-02-22 13:58:51

為什么推出Virtex-5LXT FPGA平臺和IP解決方案?如何打造一個適用于星形系統和網狀系統的串行背板結構接口FPGA?

2021-04-29 06:18:31

提供 Virtex-4、Virtex-5、Virtex-6 、Virtex-7、 Kintex-7ZYNQ-7000系列等.. ALTERA優勢產品系列:Stratix、 Arria、 Cyclone、 MAX、 Agilex系列等二手FPGA 貨真價實

2019-07-28 17:47:39

嗨, 我正在開發一種設計,我們的主板有1個virtex5 fpga和9個從屬卡,每個都有1個V5 fpga。我想同步所有9個從卡的操作。我還希望主卡和從卡之間的數據傳輸速率為300-400Mbps

2019-01-30 06:52:36

元件的輸出是輸入時鐘延遲所得。延遲時間取決于延遲元件在延遲鏈路中的位置。這種延遲體現為針對原始時鐘的相位改變或相移,這就是所謂的“數字相移”。圖1所示的即為Virtex-4器件中的典型DCM模塊。根據

2020-04-25 07:00:00

當我使用Actel FPGA中實現的簡單擦洗保護Virtex4SX55時遇到問題。如果我選擇“-g ReadBack”和“-g persist”選項,則Virtex4SX55中的程序將被Actel

2020-06-19 10:36:59

嗨,我想知道Virtex-6 FPGA可以預期多少時鐘抖動。我已經閱讀了有關Virtex-6 FPGA的所有文檔,但沒有找到數值。我發現的唯一的事情是它具有低抖動但不低或數值。

2020-06-12 14:56:20

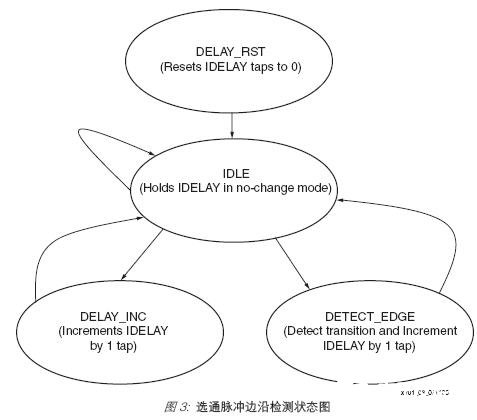

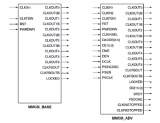

的IDDR方法在Virtex-4和Virtex-5 FPGA中,賽靈思將其ILOGIC模塊直接放置在I/O驅動器和接收器的后面。該模塊包括4個存儲元件寄存器和1個可編程絕對延遲元件。Virtex-4

2010-12-29 15:17:55

你好, 我做了一個關于回讀virtex-4 FPGA的項目。 我想只使用沒有.msk文件的CRC-32進行CRC校驗,當然,我只回讀MGT,CLB,IOB,DSP,CLK。無論FPGA工作與否,我認為這些都不可變。這是正確的?并告訴怎么做? 非常感謝!

2020-06-08 08:48:59

Clock Manager,數字時鐘管理器)和Mulplier(乘法器)。其中CLB是FPGA具有可編程能力的主要承擔者,Virtex-5的一個 slice的主要組成單元包括4個6輸入查找表、4個

2018-10-18 16:29:45

知道我在Virtex-4上執行此操作時,為什么它會引用Virtex II?我是否需要指定不同于文件中的XmYn位置或其他XmYn位置而不是嘗試指定SLICE?我不清楚X和Y是否直接對應于R和C,或者網格

2020-05-27 07:57:19

在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

Virtex-5 器件的輸入端實現邊沿對齊。要實現直接時鐘控制讀數據采集方法,這一點非常關鍵。所有合理的板設計工具都可以在可接受的容錯范圍內輕松滿足這些布線長度。時序分析本 Virtex-5 QDR II

2019-04-22 07:00:07

嗨,我正在嘗試從FPGA向另一個設備輸出一個時鐘信號(10MHz)來驅動一個50歐姆的端接負載。我試著用DDR來輸出這個時鐘。我從主振蕩器時鐘輸入(50MHz)到virtex板生成此信號。我使用DCM以5來獲得10Mhz。然后我把它運行到DDR。到目前為止,我沒有運氣。有人可以給我指點嗎?謝謝。

2020-06-15 08:40:22

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-27 06:43:47

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-29 09:16:36

我們如何使用Virtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = [1 2 3 45 6 7 8 9 1 4 5 232 1]

2020-05-29 14:41:56

我是VHDL和FPGA的新手。我有Virtex-4板,125 MHz時鐘。我需要為模數轉換(ADC)模塊生成31.25 MHz(分頻125 MHz×4)的串行時鐘(SCLK)。任何人都可以幫助

2020-05-25 08:53:55

我有一臺Memec Virtex-4 FX12 LC開發板,并希望使用u***對電路板進行編程。是否可以使用Platform Cable USB II編程器對電路板進行編程?謝謝,雨果

2019-09-27 07:28:35

使用STARTUP_VIRTEX4原語來控制CCLK和DONE信號。在生成比特流時,我使用了“-g DONE_cycle:KEEP”選項。根據我對閃存和Virtex-4之間接口的測量,這部分設計工作正常。我完全

2020-05-29 10:14:55

你好,我正在嘗試做一個簡單的顯示應用程序來測試Virtex-4 VSK上的LCD。此應用程序在16x2 LCD上顯示單行文本。除了micrlaze,bram / bram ctrls,lmb

2020-06-02 06:59:50

嗨,大家好!我正在使用帶有Virtex-4的Nallatech Xtreme DSP套件,我需要使用DIME clock_A為ADC和DCA供電,以實現ADC / DAC的全時鐘控制。但是沒有準備

2019-09-19 10:58:49

存儲器接口生成器(MIG)解決方案---Virtex-4 存儲器接口和Virtex-II Pro存儲器解決方案 Virtex-4? FPGAs solve

2009-10-24 12:02:14

#438。我發現Xilinx回答記錄23873,這似乎是一個類似于我所看到的問題。我對提議的解決方案有些警惕,它使用4個BUFGMUX作為2:1時鐘多路復用器,然后是基于常規邏輯的最終4:1輸出多路復用

2018-09-29 14:50:00

嗨,我即將使用Virtex-4QV設備(XQR4VFX140)開始一個新項目。雖然我對使用DDR2 / DDR3 SDRAM的Xilinx MIG有一些經驗,但我發現MIG IP不支持VIRTEX-4QV器件。那可能是另類?如何將DDR2 SDRAM與此FPGA連接?彌敦道

2020-04-02 06:08:46

近年來,隨著FPGA技術的發展,支持重構的FPGA器件新品迭現。Xilinx、Altera、Lattice的FPGA器件都是SRAM查找表結構。Xilinx支持模塊化動態部分重構的器件族有

2011-05-27 10:23:28

時鐘線的簡單方法來為FPGA外部的時鐘供電。使用Virtex-6,我聽說有一個新的“高性能”時鐘(HPC),具有低抖動,用于將時鐘直接從MMCM轉發到IO。在計時資源用戶指南(第34頁)中,有人說

2020-06-10 16:36:37

標志著進入第三周期。等效時間采樣技術的原理作用及采用FPGA器件實現系統的設計圖4 波形仿真在第一個周期中從CLK 的第一個上升沿開始計時同時對CLK 進行分頻可以得到CLK_ADC_OUT 時鐘信號

2020-10-21 16:43:20

大家好我想使用Xilinx的Virtex-4芯片學習VHDL FPGA編程,以便:1.真正學習貿易(我是初學者,想在真實芯片上進行FPGA編程)。2.開發我自己的片上系統,這將成為實驗設備的一部分

2018-09-28 16:54:33

你好。我是韓國LCD& Video Enginner使用各種Xilinx FPGA。我想看看Virtex-4 Video Starter Kit CD。如何收到Virtex-4視頻入門套件

2020-06-12 16:17:40

鎖定信號的上升沿是否與virtex-4 FPGA中DCM生成時鐘的上升沿對齊?

2020-07-13 09:50:56

/fpga_sys_planner.htmVirtex-5 FXT, Virtex-5 LX, Virtex-5 LXT, Virtex-5 SXT, Virtex-4 FX, Virtex-4 LX, Virtex-4 SX

2013-03-14 11:49:58

賽靈思多平臺Virtex-4 FPGA的性能及應用

賽靈思(Xilinx)的Virtex-4現場可編程門陣列(FPGA)是首款基于ASMBL(Advanced Silicon Modular Block)架構的多平臺FPGA系列。通過采用不同的平臺(LX、FX

2009-06-26 08:11:39 41

41 一種FPGA時鐘網絡中鎖相環的實現方案:摘 要:本文闡述了用于FPGA 的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探

2009-08-08 09:07:22 25

25 Xilinx公司的Virtex-5 FXT FPGA器件在業界率先集成了嵌入式PowerPC 440處理器模塊、高速RocketIO GTX收發器和專用XtremeDSP 處理能力。作為65nm Virtex-5系列的第四款平臺,Virtex-5 FXT提供了極高的

2009-11-24 11:17:22 32

32 FPGA, PowerPC, Virtex-4, 開發平臺,嵌入式系統,通信,數字視頻, 微處理器摘要:Xilinx公司的Virtex-4 ML403嵌入開發平臺是入門級的開發環境,它采用Xilinx的器件XC4VFX12-FF668-10C,支持多個時鐘源

2009-11-24 11:33:00 85

85 Virtex-4 FPGA應用指南

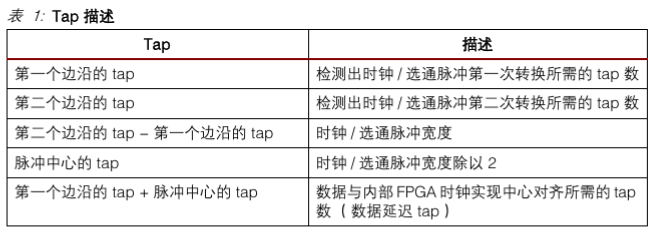

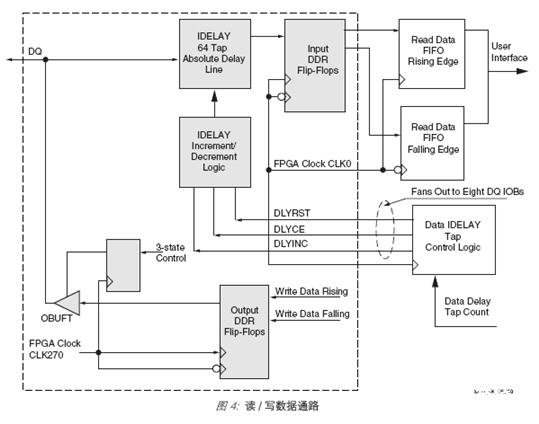

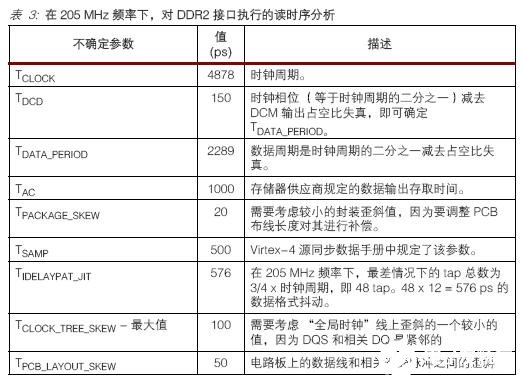

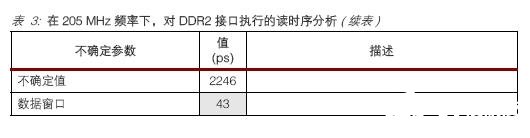

使用Virtex-4器件的DDR2控制器(267MHz及以上)

DDR2SDRAM器件提供了比DDRSDRAM指標所要求的更好的新功能,并允許DDR2器件以666Mb/s的數據

2010-05-13 14:14:26 39

39 Virtex-4 系列應用指南

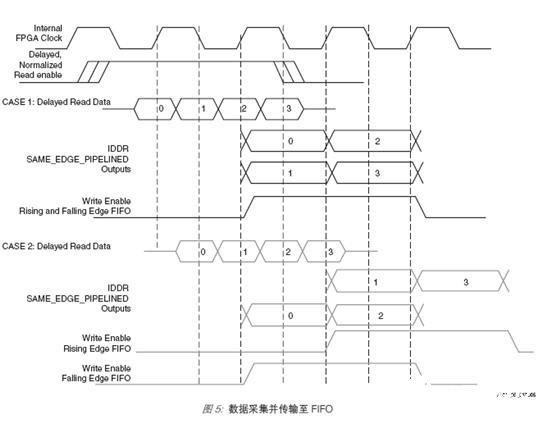

利用直接時鐘控制技術實現存儲器接口數據采集

本應用指南介紹了在 VirtexTM-4 器件中實現存儲器接口的直接時鐘控制數據采集

2010-05-13 14:16:59 22

22 重點設計并實現了863項目“南海深水區動力環境立體檢測技術研發”中5頻段微波輻射計的數據處理與控制系統,以Xilinx公司Virtex-4系列FPGA為核心,包括數據采集、AGC自動增益控制、

2010-07-28 16:12:45 29

29 本文闡述了用于FPGA的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探討了FPGA時鐘網絡中鎖相環的實現方案。

2010-08-06 16:08:45 12

12 Virtex-6 FPGA ML605開發評估技術方案

Virtex-6 FPGA是Xilinx公司的目標設計平臺,提供集成的軟件和硬件,有利于設計集中力量進性產品創新. Virtex-6系列包括LXT, SXT和HXT子系列,適

2010-04-22 18:07:58 3615

3615

Virtex-7 2000T FPGA的容量是市場同類最大28nm器件的2倍,而且比賽靈思最大型Virtex-6 FPGA大2.5倍。雖然2000T由4個切片組成,但它仍然保持著傳統FPGA的使用模式,設計人員可通過賽靈思工具流程

2011-10-26 09:11:30 2795

2795 Xilinx Virtex-4 LX160/200 開發工具套件提供了讓設計師加速產品上市的完整硬件環境。本套件針對 Xilinx 創新的 Virtex-4 Platform FPGA 系列,為設計的開發和測試提供了穩定的平臺。

2012-01-17 14:08:38 2293

2293

Xilinx 的 Virtex-4 系列將高級硅片組合模塊 (ASMBL) 架構與種類繁多的靈活功能相結合,大大提高了可編程邏輯設計能力,從而成為替代 ASIC 技術的強有力產品。Virtex-4 FPGA 由 LX、FX 和 SX 三

2012-01-17 16:14:24 6

6 The PPC405 Virtex-4 is a wrapper around the Virtex-4PowerPC 405 Processor Block primitive.

2012-02-10 16:57:58 38

38 PLL),再到Virtex-6基于PLL的新型混合模式時鐘管理器MMCM(Mixed-Mode Clock Manager),實現了最低的抖動和抖動濾波,為高性能的FPGA設計提供更高性能的時鐘管理功能。

2017-02-11 09:14:01 1030

1030

本文主要介紹利用FPGA的自身的特性實現隨機數發生器,在Virtex-II Pro開發板上用ChipScope觀察隨機數序列,以及在PCIe4Base(基于Virtex-4 FPGA)上實現。

2017-02-11 16:26:11 12113

12113

介紹一種采用FPGA(現場可編程門陣列電路)實現SDH(同步數字體系)設備時鐘芯片設計技術,硬件主要由1 個FPGA 和1 個高精度溫補時鐘組成.通過該技術,可以在FPGA 中實現需要專用芯片才能實現的時鐘芯片各種功能,而且輸入時鐘數量對比專用芯片更加靈活,實現該功能的成本降低三分之一.

2017-11-21 09:59:00 1840

1840

賽靈思Virtex? UltraScale ? All Programmable FPGA 是高端FPGA 系列的擴展,可支持1Tbps 系統的實現。Virtex UltraScale 系列具有

2017-11-18 04:15:03 1797

1797

樹結構 針對不同類型的器件,Xilinx公司提供的全局時鐘網絡在數量、性能等方面略有區別,下面以Virtex-4系列芯片為例,簡單介紹FPGA全局時鐘網絡結構。

2017-11-22 07:09:36 8891

8891

在本視頻中,了解Xilinx采用高帶寬存儲器(HBM)和CCIX技術的16nm Virtex UltraScale + FPGA的功能和存儲器帶寬。

2018-11-27 06:20:00 3624

3624 Virtex?-6 FPGA內置支持PCIExpress?Gen2兼容接口。

本視頻介紹了在ML605評估套件上運行的用于PCI Express技術的Virtex-6 FPGA集成模塊的三個演示。

2018-11-22 06:30:00 2820

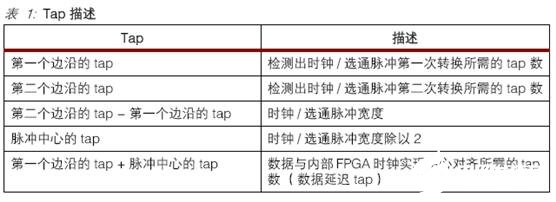

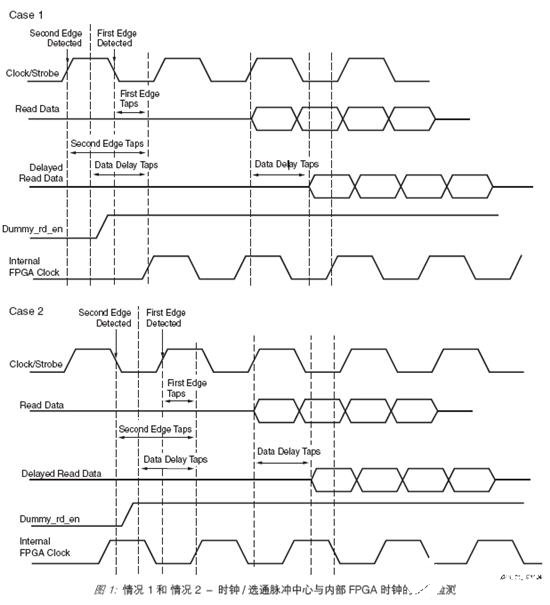

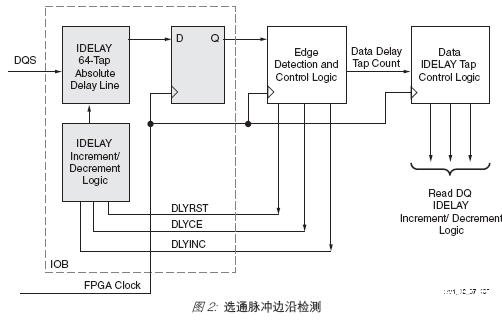

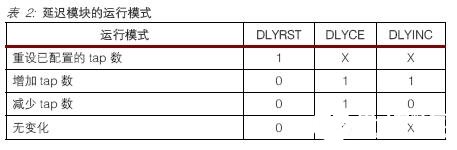

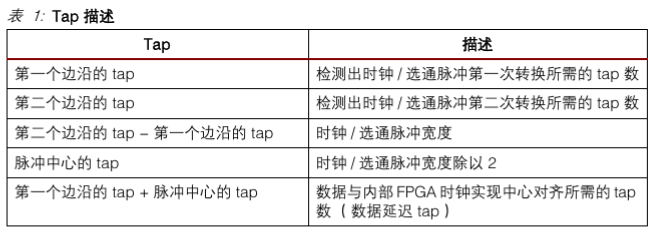

2820 大多數存儲器接口都是源同步接口,從外部存儲器器件傳出的數據和時鐘/ 選通脈沖是邊沿對齊的。在 Virtex-4 器件采集這一數據,需要延遲時鐘/ 選通脈沖或數據。利用直接時鐘控制技術,數據經延遲

2020-04-11 09:55:08 743

743

xilinx公司推出的兩種新Virtex-4 FPGA器件LX60和SX35.LX60是邏輯最佳LX平臺的第二個器件,SX35是DSP最佳SX平臺的第一個器件.和今年六月份提供的Virtex-4 LX25一起,Xilinx公司現在可提供三種革命性的FPGA系列.

2020-09-10 08:47:00 1846

1846 Virtex-4、Virtex-5和Spartan-3系列器件增加和修改了一些與配置有關的專用引腳,這些專用引腳如下。

2021-01-06 17:13:52 14

14 本節介紹0.80 mm和1.00 mm間距倒裝芯片細間距BGA封裝中Virtex-4設備的引腳。Virtex-4設備僅在高性能倒裝芯片BGA封裝中提供,這些封裝經過優化設計,可改善信號完整性和抖動

2021-01-25 08:00:00 4

4 本應用指南描述了在 Virtex?-4 XC4VLX25 FF668 -10C 器件中實現的 DDR SDRAM 控制器。該實現運用了直接時鐘控制技術來實現數據采集,并采用自動校準電路來調整數據線上的延遲。

2021-03-26 14:42:41 4

4 對于一個設計項目來說,全局時鐘(或同步時鐘)是最簡單和最可預測的時鐘。只要可能就應盡量在設計項目中采用全局時鐘。FPGA都具有專門的全局時鐘引腳,它直接連到器件中的每一個寄存器。這種全局時鐘提供器件中最短的時鐘到輸出的延時。

2021-04-24 09:39:07 5827

5827

介紹了eMMC 芯片的技術特點、工作原理,以及控制器的設計方案。該設計基于Xilinx公司的Virtex-6系列FPGA芯片,實現了控制器的設計方案,并給出了仿真結果,驗證了該設計方案的可行性。此外,該設計均采用硬件邏輯實現,具有速度快、通用性強、可靠性高的特點。

2021-10-15 18:00:24 5

5

電子發燒友App

電子發燒友App

評論