在這篇文章里,我們就繼續來討論一下 FPGA 的進階學習路線。和入門路線不同,我想從入行和職業發展的角度,分析一下專業的 FPGA 開發者需要具備哪些技術能力,以及如何進一步的提升自己這些方面的能力。所以如果你有興趣從事 FPGA 這個行業、亦或是正在尋找這方面的工作,或者已經入行一段時間,并且希望明確今后今年的發展方向,那么這篇文章應該會對你有所幫助。

和初學者相比,專業的 FPGA 工程師需要掌握更多的技能和知識。對此我歸納了四個方面,分別是 FPGA 相關的高級技巧、領域相關的知識、以及職業芯片工程師必須具備的硬實力和軟實力。我也會介紹一些書籍和學習資料,希望能對你的學習有所幫助。

RTL 設計的高級開發技巧

掌握基礎知識之后,就需要繼續學習 FPGA 以及數字電路設計相關的一些高級技巧。這部分的內容有很多,主要包含設計、驗證、以及一些 FPGA 約束和優化的技巧和方法。

這里的設計指的是邏輯設計,也就是使用 RTL 語言實現一些相對復雜一點的模塊或者系統,以及在這個實現過程中使用到的一些技巧。在本文也暫時不討論高層次綜合(HLS)的內容,也就是使用 C 語言或者 Python 等高級語言對 FPGA 進行編程。關于 HLS 的相關內容,可以看我之前的文章《高層次綜合:解鎖 FPGA 廣闊應用的最后一塊拼圖》。

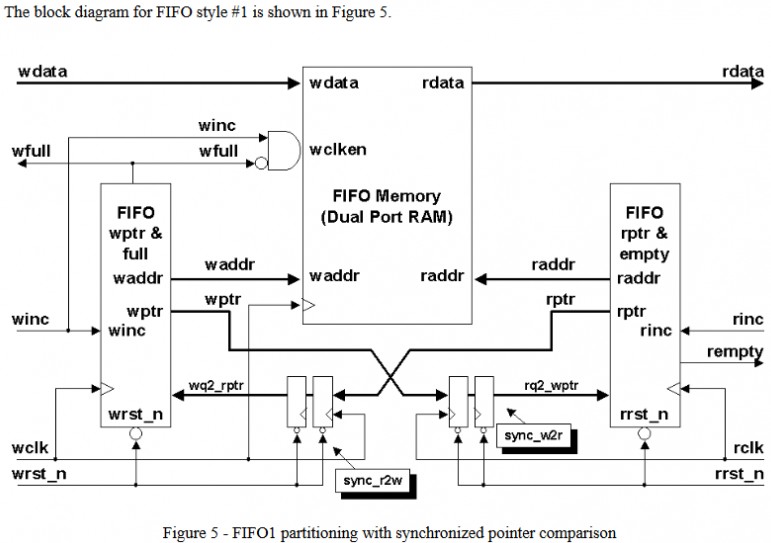

對于 RTL 設計,一個在面試中非常常見的問題,就是信號的跨時鐘域處理。比如在跨時鐘域的時候,怎么處理一位信號、怎么處理多位不相關的信號、怎么處理多位的總線信號、怎么處理復位、怎么處理脈沖,從快時鐘域到慢時鐘域怎么辦,反過來怎么辦等等一大堆。這類問題的集大成者就是 FIFO 的設計,特別是異步 FIFO 的設計,以及它的一系列變種問題。

一種異步 FIFO 的架構框圖

關于跨時鐘域和 FIFO 的問題,推薦讀者朋友們仔細研究一下 Clifford Cummings 這位大神的幾篇文章,他的文章非常全面的討論了上面說的所有問題,我也會把其中的代表作分享到知識星球里。

?

Clifford Cummings

事實上,Cummings 作為 Verilog 語言的協議制定參與者,他還寫了很多文章,詳細探討了各種和數字電路相關的問題,比如如何寫出好的可綜合的 RTL 代碼、狀態機怎么寫、UVM 和驗證相關的問題、還有很多 SystemVerilog 和 Verilog 的細節討論。

對于進階的朋友,我覺得這本書也有一定借鑒價值,名叫《FPGA 設計實戰演練 – 高級技巧篇》。這里面介紹了一些常見的 FPGA 設計的技巧和方法,比如前面說的時鐘域處理、還有如何進行速度和面積的互換和優化等等。

?

值得注意的是,雖然在面試時常問跨時鐘域處理這類的問題,但在實際的工程項目中是基本不可能讓你從頭寫一個跨時鐘處理模塊或者 FIFO 的,這些功能早就被封裝成一個個現成的模塊了,直接調用就可以。

但這并不是所謂的“面試造火箭,工作擰螺絲”,前面介紹的這些高級技巧,更多的是在鍛煉我們的思維方式和設計習慣。只有知道這些,才有可能在面對一個實際問題的時候,知道怎么根據需求去分析、設計和實現,并且得到最優化的結果。

驗證的高級技巧

再來簡單說一下驗證。之前的文章里提到過,驗證是一個非常復雜的領域。比如在下面的這張 Mentor 的圖片里就顯示,在一個芯片項目里,平均而言至少會有超過一半的時間花在驗證上,有的甚至占 60%~70%。以我自己的經驗來說,這個比例會更高。

?

驗證之所以復雜而且耗時,是因為我們必須盡可能多的檢查到所有可能的設計功能和狀態。驗證里有一個“功能覆蓋率”的概念,就是用來量化這個過程的。比如對于一個加法電路,a+b=c,我們肯定希望驗證到:a 和 b 取所有值的時候,結果 c 的值都正確。如果 a 和 b 都是一位十進制數,也就是從 0 到 9 之間隨機選取,那么就有 10x10=100 種可能。但是如果 a 和 b 都是四位十進制數,那么就有 10000x10000=1 億種可能,當然這還是非常簡單的情況。

對于更加復雜的設計,比如多個數相加、相乘,或者在一些特定領域的邏輯功能、比如 AI 或者網絡應用等等,我們很難通過仿真驗證到所有可能的狀態,甚至不可能覆蓋所有可能的設計狀態。

為了解決這個問題,就需要科學的制定驗證計劃,同時使用一些進階的驗證方法學,比如業界常用的隨機約束、UVM 或者形式化方法,來幫助我們構建更加高效的驗證環境。

?

一個基本的 UVM 驗證環境示意圖

很多芯片公司其實都有設計工程師和驗證工程師的分工,但這并不代表做芯片設計的人不需要知道驗證。事實上,那些優秀的芯片設計者同時也是優秀的驗證者,他們可能不會用 UVM 或者形式化驗證方法,但肯定會熟練掌握隨機約束、參考模型建模、自動化測試、還有斷言等等常用的驗證技術,這也應該是我們應該努力的方向。

FPGA 的約束和優化設計

除了設計和驗證之外,FPGA 相關的優化和約束也是進階學習的重要內容。這里主要包括對時序、面積、功耗的約束和優化。比如,存在多個時鐘的時候怎么寫時序約束,怎么進行時序分析,怎么劃分固定的設計區域,怎么預估設計的功耗等等。這個過程可能會貫穿整個 FPGA 項目的開發周期,而且一些常見的 ASIC 約束方法并不一定會適用于 FPGA 設計。

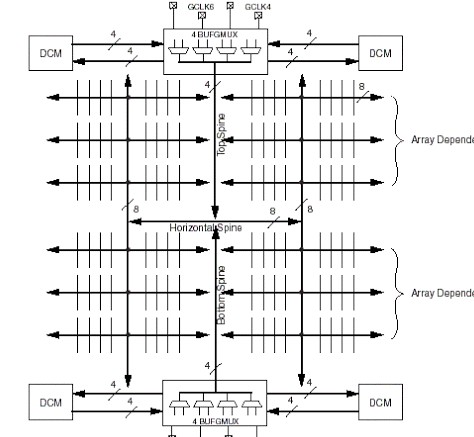

拿 FPGA 低功耗設計舉例,門控時鐘就不一定適合于 FPGA。這是由于 FPGA 里的時鐘網絡是固定的,因此只能關閉固定的時鐘樹或者分支。如果需要做門控時鐘,就必須控制某些特定的 clock buffer,且要同時確定這些 clock buffer 可以被邏輯控制。更重要的是,我們還需要確保這個時鐘驅動的邏輯都位于這個時鐘樹的“勢力范圍”之內,這就需要在布局布線時設置想要的位置約束。由此可見,門控時鐘這個在 ASIC 設計里常見的低功耗設計方法,在 FPGA 設計里是困難且繁瑣的。

FPGA 時鐘樹示意圖

領域相關的知識

進階學習路線的第二部分內容,就是領域專用的知識,也就是 Domain Specific Knowledge。我們之所以要學習這部分內容,是因為 FPGA 并不是單獨存在的,它需要被應用在某些具體的領域和場景里。

比如,FPGA 目前的一個很火的應用領域就是數據中心里的智能網卡。關于智能網卡的內容在之前已經說過很多了,包括微軟、阿里、騰訊、京東、字節等等很多互聯網公司都在布局這方面的技術。智能網卡的本質,就是使用把一些原本在 CPU 里運行的應用,卸載到 FPGA 里執行,這可以是網絡協議棧、一些虛擬化的功能、或者是和 AI 相關的功能等等。

?

這里面就涉及到了很多領域專用的知識,比如計算機網絡、網絡功能虛擬化 NFV、軟件定義網絡 SDN,還有一些其他的虛擬化技術比如 Virtio、OVS 等。

此外,領域相關的知識還包括各種高速接口協議和總線相關的內容。比如 PCIe、DDR、HBM、以太網、收發器等,還有各種各樣的總線協議。這些和 FPGA 也有非常密切的關系,在實際的求職應聘時也是重要的加分項。

在學習這些內容的時候,我個人建議還是結合目標職位或者項目的需求來,有目的的去學習,而不是想著一上來就一口吃個胖子。比如我就對使用 FPGA 進行高清視頻處理相關的內容不太了解,因為我并不做這個方向,但我大概知道怎么構建知識圖譜,并由此去一步步學習,這樣其實就可以了。

職業技能相關的能力

FPGA 進階學習路線的第三點,就是職業工程師需要具備的一些硬實力。比如,企業里幾乎全部的開發環境都是在 Linux 系統里完成的,而且大部分時候沒有圖形界面。所以除了常用的那些 EDA 工具之外,還特別需要我們熟練掌握 Linux 的一些基本命令。此外還應該掌握至少一種腳本語言,比如 Tcl、Perl、Makefile、Python 等等。這能極大的提升我們的工作效率,這也是芯片工程師必備的技能。

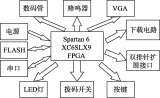

此外,作為 FPGA 工程師,硬件調試的能力也是不可或缺的。一個在職業工程師日常工作中非常常見的場景,就是使用和調試各種各樣的 FPGA 板卡,比如拿來一個全新的板卡,從頭開始用它進行開發。

這就要求我們會看板卡的原理圖、知道怎么寫各種約束,怎么使用板子上的各種資源等等。此外,當設計出錯時,怎么去進行硬件調試,還有怎么設計一些有用的邏輯功能來方便硬件測試,比如各種狀態寄存器等等。那么對于某些專業領域,比如在網絡領域,可能還需要知道怎么進行流量測試,比如 DPDK 的使用、配置,還有一些測試儀器的使用、一些常見的網絡分析工具(如 wireshark)的使用等等。

總體來說,這些職業工程師需要具備的硬實力,可能在上學期間不一定都能接觸到。這就需要我們在工作中不斷實踐和總結,才能把這些技能一點一點積累起來。

職業人士的軟實力

除了硬實力之外,軟實力的培養也至關重要,這包括溝通、時間管理、團隊協作、領導力,還有不斷學習的能力等等。

不管是芯片還是其他工程領域,絕大部分項目都是由很多團隊一起協作完成的,因此如何與不同團隊的成員溝通項目內容,如何制定項目規劃、把握項目進度,以及遇到難題應該如何著手去解決,都是職業工程師幾乎天天遇到的問題。

事實上,不管你從事或者打算從事什么職業,我們都應該從現在開始培養自己的各種軟實力。比如多與人溝通,積極參加各種活動,或者像我在之前的文章《分享是程序員的必備素質》里提到的,不斷分享自己學習和工作中的各種心得體會。這些肯定都會對我們今后的職業生涯大有幫助。

小結

在今天的文章里,我們梳理了一下作為一個職業的 FPGA 工程師需要具備哪些能力,一共有四個部分,分別是和 FPGA 相關的高級開發技巧、各種領域專用的知識、還有芯片工程師必備的硬實力和軟實力。針對每部分內容,我們也都深入的了解了如何去學習和提升自己的這些能力。

事實上,這里提到的各種專業內容只是我們日常工作中的一部分,它們可能會隨著技術的發展而不斷變化,甚至被各種新技術所取代。所以最重要的是,培養自己不斷學習的能力,不斷嘗試新技術、新工具,努力跳出自己的舒適圈,只有這樣才能一直保持自己的競爭力,從而實現更好的人生價值。

? ? ? ?責任編輯:pj

電子發燒友App

電子發燒友App

評論