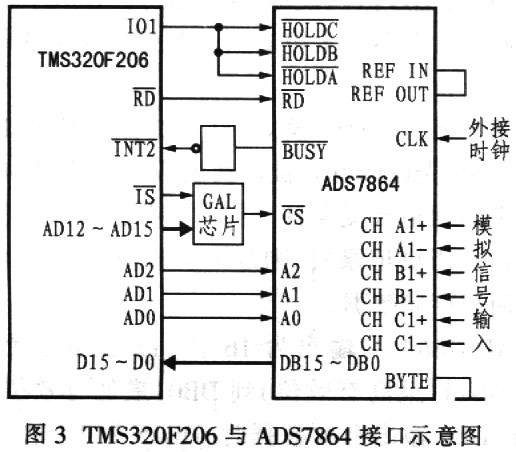

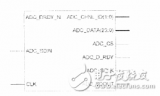

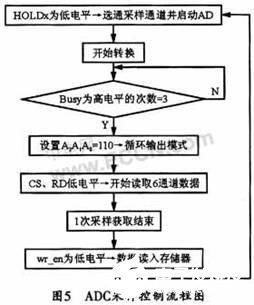

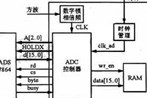

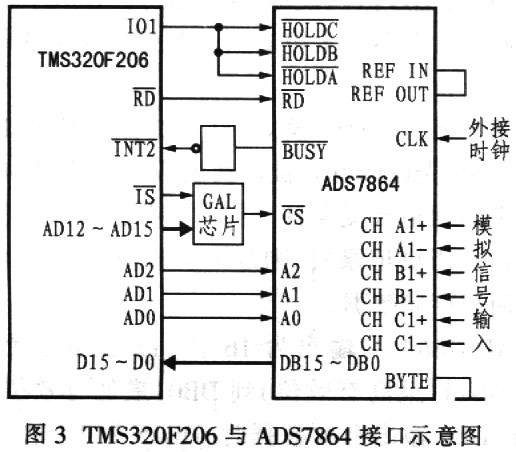

為了解決這些不足,可在數據采樣部分采用高速A/D轉換芯片ADS7864,即在數據采集的控制部分則利用FPGA(可編程邏輯器件)直接控制ADS7864對模擬信號進行采樣。然后將轉換好的12位二進制

2011-10-25 16:18:49 1916

1916

本文利用ADS1298芯片的高精度,以FPGA為主控制芯片,通過將工頻陷波、帶通濾波等模擬部分轉移到數字側,在保證性能的前提下簡化腦電信號放大與調理的模擬電路,實現便攜式腦電信號的采集。##本系統

2014-01-25 10:42:31 4887

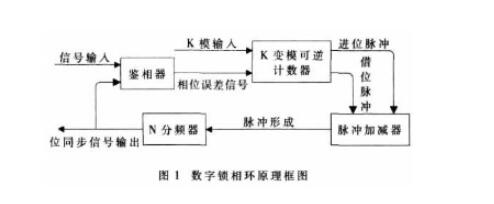

4887 的問題進行了討論。 引言 鎖相環(PLL)技術在眾多領域得到了廣泛的應用。如信號處理,調制解調,時鐘同步,倍頻,頻率綜合等都應用到了鎖相環技術。傳統的鎖相環由模擬電路實現,而全數字鎖相環(DPLL)與傳統的模擬電路實現的PLL相比,具有精度高

2018-10-25 09:17:13 8237

8237 ADS7864 - 500kHz, 12-Bit, 6-Channel Simultaneous Sampling ANALOG-TO-DIGITAL CONVERTER - Burr-Brown Corporation

2022-11-04 17:22:44

EVAL MODULE FOR ADS7864M

2023-03-30 11:46:47

畢業設計是做電能質量監測系統,主要是用s3c2410做的,要添加一個ADS7864設備采集電能,然后顯示出來,如何驅動ADs7864呢?有做過這個的社友嗎?是不是驅動了就可以顯示呢?

2012-03-24 12:44:22

該文章是完全原創,用最簡潔的語言講清楚FPGA實現負反饋的精要。震撼!FPGA實現負反饋控制純數字鎖相環!.zip (225.26 KB )

2019-04-30 04:50:41

可現在遇到一個問題,系統的晶振是40M,可我需要一個160M的輸出信號,怎么才能在FPGA內部實現倍頻呢?我看了它的說明書,上面說可以實現倍頻,有PLL功能可是卻沒有具體的說明怎么實現倍頻,用什么方法實現,能實現多少倍頻?用軟件實現,還是硬件實現?不知道大俠們是怎么實現倍頻的,能否告知一二?

2013-12-04 22:31:39

)設計交通燈控制電路 采用可編程器件(FPGA/CPLD)設計數字鐘 基于VHDL建模實現FSK的調制與解調 數字鎖相環法位同步信號 基于FPGA的碼速調整電路的建模與設計 基于VHDL或

2012-02-10 10:40:31

本帖最后由 1154286643 于 2015-11-2 17:30 編輯

哪位大哥會光電編碼器倍頻的啊?用于伺服電機的,現在要實現一個十倍頻以上的電路,A相信號超前B相90度,用FPGA

2015-11-02 14:04:27

請問各位,有誰知道有什么鎖相放大芯片不,常規的是利用乘法器加濾波器來完成鎖相放大的,我做了一個,但信號不是很好,雜波嚴重。有誰做過相關電路嗎?(百度:)鎖相放大器是一種對交變信號進行相敏檢波的放大器

2013-04-20 21:01:19

第十七章IP核之PLL實驗PLL的英文全稱是Phase Locked Loop,即鎖相環,是一種反饋控制電路。PLL對時鐘網絡進行系統級的時鐘管理和偏移控制,具有時鐘倍頻、分頻、相位偏移和可編程

2022-01-18 09:23:55

的時鐘芯片CDCE421A,無源晶振30M無源晶振輸入,30MLVDS輸出,用于產生AD的低抖動時鐘。 AD的電源使用1.8V,電源使用LDO轉為1.8V后分為模擬電和數字電,兩者之間使用電感隔離

2018-11-13 15:09:03

Actel FPGA PLL鎖相環的最大能達到幾倍頻幾分頻?我在網上查了一下有人說是20倍頻,10分頻,但是我沒有在芯片手冊里面找到資料,想要確認一下。

2014-12-04 11:25:15

DEMO BOARD FOR ADS7864

2023-03-30 11:47:20

,目前我主要是負責數字鎖相鎖相放大器的研究工作,同時采用DSP芯片做了前期的工作,其他部分已近基本做好。目需要集成在一起,還需要RAM芯片等實現相應的算法,經過對比,我覺得該板能夠很好的代替目前實驗組采用的多控制芯片的設計,簡化外圍。希望能得到這款板子進行設計,謝謝。

2015-07-01 02:21:16

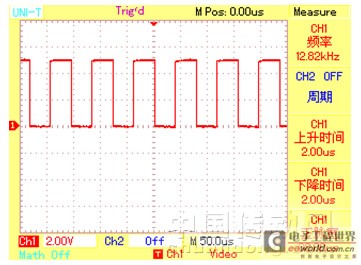

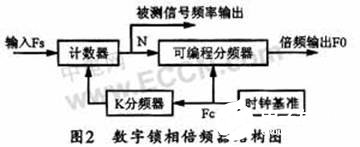

摘 要:提出了一種基于FPGA的任意鎖相倍頻算法。通過對倍頻系統總體結構的分析,提出了實現該算法的原理及其具體的設計方法,同時提供了一個基于FPGA器件完成的設計實例。仿真和實測結果表明了該算法的正確性及可實現性,并在實際的項目中驗證了該算法的良好性能。

2013-12-04 22:29:00

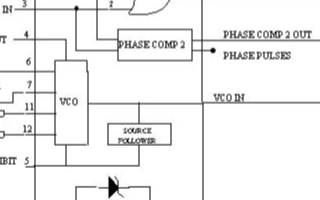

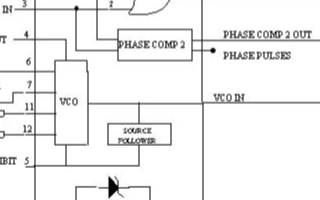

。傳統的鎖相環各個部件都是由模擬電路實現的,一般包括鑒相器(PD)、環路濾波器(LF)、壓控振蕩器(VCO)三個環路基本部件。 隨著數字技術的發展,全數字鎖相環ADPLL(AllDigital

2010-03-16 10:56:10

FPGA(可編程邏輯器件)直接控制ADS7864對模擬信號進行采樣。然后將轉換好的12位二進制數據迅速存儲到FPGA內部的存儲器中。為了提高諧波測量的精度,還可采用硬件描述語言VHDL來設計數字鎖相

2021-07-01 08:30:00

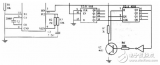

波,另1路用于再生能耗調節制動電流。三相換相PWM經驅動電路控制電機的換相,這3路PWM只用于換相不進行調制,由斬波環節進行調制。電機繞組電流經求偏、放大、濾波通過A/D(ADS7864)轉換進人

2016-02-01 14:44:30

本帖最后由 eehome 于 2013-1-5 09:44 編輯

基于FPGA的數字鎖相放大器的設計與研究

2012-11-22 11:30:17

HDL硬件描述語言對優化前后的算法進行了編碼實現。仿真和實驗結果表明,優化后的數字三相鎖相環大大節省了FPGA的資源,并能快速、準確地鎖定相位,具有良好的性能。關鍵詞:FPGA;三相鎖相環;乘法復用;CORDIC

2019-06-27 07:02:23

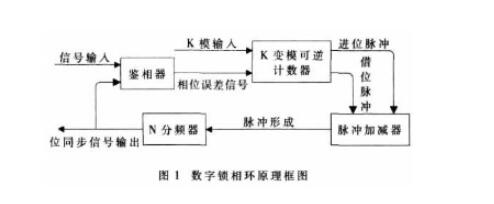

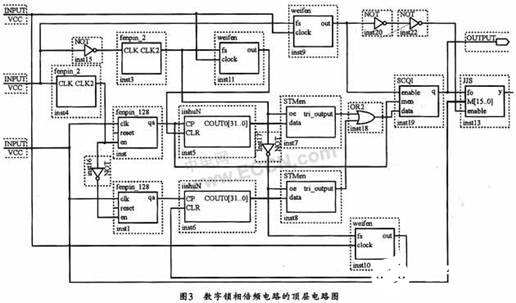

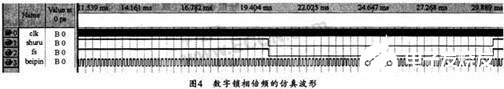

隨著集成電路技術的不斷進步,數字化應用逐漸普及,在數字通信、電力系統自動化等方面越來越多地運用了數字鎖相環。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實現、省資源。本文綜合以上考慮,在一片FPGA中以Quartus II為平臺用VHDL實現了一個全數字鎖相環功能模塊,構成了片內鎖相環。

2019-10-10 06:12:52

通過對平均值相位差計原理的分析和程序設計、仿真,用FPGA芯片實現了一個高精度、寬頻率范圍的相位差計。該測量方法的最大優點是系統電路簡單,不需要鎖相環,占用的邏輯資源少,選用低端FPGA芯片完全能滿足要求,大大提高了被測信號的頻率范圍及測量精度,具有一定的應用價值。

2021-05-10 06:04:50

FPGA芯片是由哪些部分組成的?如何去實現一種基于FPGA芯片的可重構數字電路設計?

2021-11-05 08:38:57

鎖相環是什么工作原理?如何采用FPGA與頻率綜合器ADF4111相結合的方法實現數字鎖相式頻率源的設計?

2021-04-14 07:00:20

全數字鎖相環由那幾部分組成?數字鎖相環的原理是什么?如何采用VHDL實現全數字鎖相環電路的設計?

2021-05-07 06:14:44

鎖相環是倍頻電路的主要實現方式,直接決定倍頻的成敗。傳統的鎖相環各個部件都是由模擬電路實現的。

2019-10-18 08:01:28

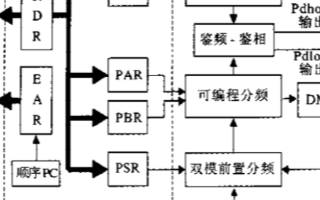

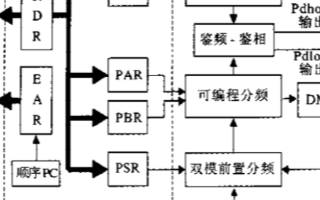

數字鎖相環頻率合成系統的工作原理CPU控制數字鎖相環頻率合成系統FPGA實現

2021-04-09 06:20:37

現在要做FPGA控制ADS8344E這個芯片,實現A/D轉換。可是看完時序圖之后不知道該怎么下手,特別是需要延時的地方,應該用狀態機實現延時還是其他方法?請各位前輩不吝賜教。

2016-11-23 22:23:29

本文介紹了電荷泵鎖相環電路鎖定檢測的基本原理,通過分析影響鎖相環數字鎖定電路的關鍵因子,推導出相位誤差的計算公式。并以CDCE72010 為例子,通過實驗驗證了不合理的電路設計或外圍電路參數是如何影響電荷泵鎖相環芯片數字鎖定指示的準確性。

2021-04-20 06:00:37

請教一下大神鎖相環是如何實現倍頻的?

2023-04-24 10:15:39

ADS7864與TMS320VC5402連接的時候,busy、rd、cs等控制信號需要進行電平轉換嗎?如果用74lvc4245電平轉換的話,dir引腳的高電平是3.3v還是5v,dir接dsp上

2019-05-23 10:56:49

根據ADS7864的手冊,HOLDX引腳拉低啟動一次轉換,這里所說的轉換應該可以說成是采樣。但是,AD內部開始一次新的轉換時,BUSY引腳電平變低。這里所說的轉換不應該說是采樣了。是不是先是采樣,然后才是轉換,也就是說HOLDX的下降沿先于BUSY的下降沿?兩個下降沿之間的時間間隔是固定的嗎?

2019-06-13 07:24:30

想要解決的問題是:我們之前用的是ad630在鎖相的,對于一個4khz的有用信號,我們是通過輸入8khz(二倍頻率)的方波作為參考信號來提取二次諧波信號的。現在,想要實現的就是,用同頻率的方波作為參考信號,來鎖相,提取得到其二倍頻的信號。有哪些芯片可以實現該功能呢?期待您的回復。萬分感謝。

2018-09-19 10:01:30

看了ADS7864的手冊,采樣開始是通過將HOLDX引腳拉低引起的,那么采樣結束是不是要將HOLDX引腳拉高啊?采樣時間(決定采多少個點)是不是就是下降沿與上升沿之間的間隔?

2019-06-14 10:48:06

和各路倍頻的脈沖寬度由時鐘控制,倍頻后的脈沖寬度均勻一致。 運用FPGA實現4倍頻、鑒相電路,采用全數字反饋電路的設計方法,由于倍頻、鑒相電路設計在同一芯片上,一方面,FPGA門電路高數量較大,時鐘頻率

2019-06-10 05:00:08

The ADS7864 is a dual 12-bit, 500kHz Analog-to-Digital (A/D) converter with 6 fully differential

2008-04-09 11:17:57 25

25 ads7864中文資料是德州儀器(TI)公司Burr-Brown產品部推出的快速六通道全差分輸入的雙12位A/D轉換器。它能以500kHz的采樣率同時進行六通道信號采樣,特別適用于馬達控制和電力監控

2008-04-09 11:23:35 71

71 智能全數字鎖相環的設計

摘要: 在FPGA片內實現全數字

2008-08-14 22:12:51 56

56 智能全數字鎖相環的設計:在FPGA片內實現全數字鎖相環用途極廣。本文在集成數字鎖相環74297的基礎上進行改進,設計了鎖相狀態檢測電路,配合CPU對環路濾波參數進行動態智能配

2009-06-25 23:32:57 72

72 基于FPGA的全數字鎖相環設計:

2009-06-26 17:30:59 141

141 一種FPGA時鐘網絡中鎖相環的實現方案:摘 要:本文闡述了用于FPGA 的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探

2009-08-08 09:07:22 25

25 采用AT89C2051 單片機設計了一種單片鎖相倍頻電路,利用片內定時器和數字算法實現了對輸入信號的同步鎖相和倍頻,并輸出倍頻信號。實驗結果驗證了設計的正確性。

2009-09-14 15:04:16 80

80 The ADS7864 is a dual 12-bit, 500kHz analog-to-digital (A/D) converter with 6 fully differential

2010-06-01 16:16:12 15

15 ADS7864M E

2010-06-01 16:20:23 79

79 鎖相環被廣泛應用于電力系統的測量和控制中。介紹了一種新型的基于比例積分控制邏輯的全數字鎖相環。通過對其數學模型的分析,闡述了該鎖相環的各項性能指標與設計參數的

2010-07-02 16:54:10 30

30

鎖相型倍頻器

2009-04-11 10:27:15 781

781

摘要: 在FPGA片內實現全數字鎖相環用途極廣。本文在集成數字鎖相環74297的基礎上進行改進,設計了鎖相狀態檢測電路,配合CPU對環路濾波參數進行動態智

2009-06-20 12:39:32 1408

1408

不帶鎖相環的倍頻器

2009-09-17 16:11:00 857

857

12位A/D轉換器ADS7864在電網諧波分析儀中的應用

ADS7864是Burr-Brown公司開發的12位6通道A/D轉換器,介紹了ADS7864的工作原理、內部結構、工作模式及編程

2009-10-25 09:45:06 2040

2040

寬頻帶數字鎖相環的設計及基于FPGA的實現數字鎖相環(DPLL)技術在數字通信、無線電電子學等眾多領域得到了極為廣泛的應用。與傳統的模擬電路實現的

2009-11-23 21:00:58 1187

1187

有源電力濾波器中鎖相倍頻電路的實現

有源電力濾波器(Active Power Filter, APF)是一種動態抑制諧波和補償無功的電力電子裝置。鎖相倍頻電路是有源電

2009-12-03 10:24:22 1786

1786

基于fpga的鎖相環位同步提取電路

該電路如圖所示,它由雙相高頻時鐘

2010-10-08 12:00:23 1483

1483

FPGA 中的DLL 是一種很好的資源,特別是較高頻率的時候,應用較廣。它可以對時鐘進行倍頻、鎖相等操作。通過設計掌握DLL 的各種應用:倍頻,分頻,鎖相,以及移相的操作,編程演示

2011-05-11 09:38:54 0

0 頻率跟蹤的 鎖相環電路 由專用鎖相芯片CD4046和分頻芯片CD4040組成,以實現工頻信號的鎖相倍頻,分頻比為1/64。在工頻信號恰好為50 Hz的情況下,該電路的鎖相倍頻頻率為5064=3 200 Hz,相

2011-10-26 11:17:47 8574

8574

鎖相環英文為PLL,即PLL鎖相環。可以分為模擬鎖相環和數字鎖相環。兩種分類的鎖相環原理有較大區別,通過不同的鎖相環電路實現不同的功能。

2011-10-26 12:40:28

本文介紹了鎖相環集成電路CD4046 的內部結構功能及特點,并給出在高倍鎖相倍頻器中的應用。

2011-11-11 15:52:35 420

420 紹了數字倍頻電路的工作原理,分析了倍頻器產生誤差的原因,然后給出用VHDL語言來實現數字倍頻器的方法,并用Max+plusII通過仿真進行了驗證。

2011-12-07 13:47:30 70

70 基于FPGA的數字鎖相環設計與實現技術論文

2015-10-30 10:38:35 9

9 Xilinx FPGA工程例子源碼:用FPGA實現數字鎖相環

2016-06-07 15:07:45 37

37 ADS7864

2017-03-04 17:52:58 1

1 一、設計目標 基于鎖相環的理論,以載波恢復環為依托搭建數字鎖相環平臺,并在FPGA中實現鎖相環的基本功能。 在FPGA中實現鎖相環的自動增益控制,鎖定檢測,鎖定時間、失鎖時間的統計計算,多普勒頻偏

2017-10-16 11:36:45 18

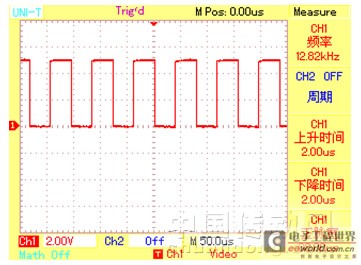

18 環技術設計了倍頻電路。首先論述了鎖相環的基本原理和環路濾波器的參數設計方法,然后利用ADS軟件對鎖相環的環路濾波器進行了設計和仿真。最后,將設計的環路濾波器應用于實際電路,并給出了測試結果。

2017-12-07 14:46:47 12

12 DSP(數字信號處理器)、ASIC(專用集成電路)和FPGA(現場可編程門陣列)三種不同方式完成。[2]采用FPGA的方式適合與對速率要求較高的可編程環境,本設計使用Xilinx公司Spartan3E的FPGA通過對TI的ADS1256芯片控制并完成模數轉換功能。

2017-12-21 09:47:45 4806

4806

本文主要介紹了數字移相器的設計電路圖大全(移相電路/倍頻電路/AD5227/鎖相環)。移相器廣泛應用于各種電路,但由于在放大器中的偏差以及電容公差,通常很難實現電路精確控制所需的精確移相。電路利用

2018-05-10 09:31:18 28540

28540

模塊或者IP核,然后組合起來就可以實現一個簡單的功能。全數字鎖相環(DPLL)就是其中一個典型的例子。然而DPLL在應用時存在很多缺陷,例如鎖相時間長、捕捉帶窄等。為了避免這些缺點,本文設計了一種全新的相位跟蹤倍頻系統,有效地改善了DPLL的這些指標,并在項目中得到了良好的應用。

2018-07-31 10:51:41 2287

2287

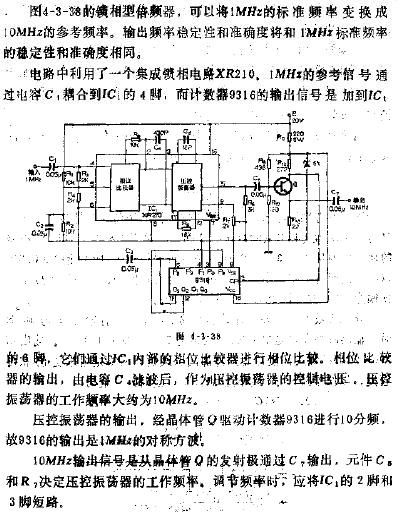

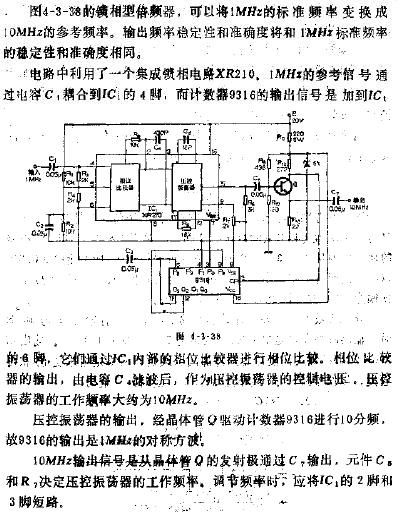

關鍵詞:9316 , 倍頻器 如圖所示為鎖相型倍頻電路。該電路可以將1MHz的標準頻率變換成10MHz的參考頻率。輸出頻率穩定性和準確度將和1MHz標準頻率的穩定性和準確度相同。電路中使用的鎖相

2018-09-28 09:41:01 716

716 大規模的數字系統已經可以通過可編程邏輯電路來實現單片集成,即用一個芯片完成整個數字系統的設計。因此將CPU控制的數字鎖相環頻率合成系統集成在一塊可編程邏輯芯片中實現已經成為可能。本系統由多個可編程的數字分頻器、數字鑒頻-鑒相器以及協調控制工作的CPU組成。

2020-03-11 10:30:58 918

918

隨著集成電路技術的不斷進步,數字化應用逐漸普及,在數字通信、電力系統自動化等方面越來越多地運用了數字鎖相環。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實現、省資源。本文綜合以上考慮,在一片FPGA中以Quartus II為平臺用VHDL實現了一個全數字鎖相環功能模塊,構成了片內鎖相環。

2020-07-16 09:16:08 2465

2465

鎖相環路是一種反饋控制電路,簡稱鎖相環( PLL)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤, 所以鎖相環通常

2020-08-06 17:58:25 24

24 本文提出了一種適用范圍廣泛的全數字鎖相環(ADPLL)實現方法.在鎖相環輸入頻率未知的情況下,實現鎖相鎖頻功能。本文從全數字鎖相環的基本實現方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 65

65 本文提出了一種適用范圍廣泛的全數字鎖相環(ADPLL)實現方法.在鎖相環輸入頻率未知的情況下,實現鎖相鎖頻功能。本文從全數字鎖相環的基本實現方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 18

18 鎖相環路誕生于20世紀30年代。近年來,鎖相技術在通信、航天、測量、電視、原子能、電機控制等領域,能夠高性能地完成信號的提取、信號的跟蹤與同步,模擬和數字通信的調制與解調、頻率合成、濾波等功能

2021-03-31 11:59:11 4204

4204

電子發燒友網為你提供數字鎖相電路的設計與實現資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-17 08:44:20 4

4 基于FPGA的寬頻帶數字鎖相環的設計與實現簡介說明。

2021-06-01 09:41:14 26

26 基于FPGA的高性能全數字鎖相環

2021-06-08 11:09:01 45

45 PLL鎖相環倍頻是一種用于改變輸入信號頻率的技術,它可以將輸入信號的頻率放大或縮小,以達到某種特定的目的。

2023-02-14 15:56:35 1939

1939 模擬鎖相環和數字鎖相環的主要區別在于它們的控制方式不同。模擬鎖相環是通過模擬電路來控制頻率和相位,而數字鎖相環是通過數字信號處理技術來控制頻率和相位。此外,模擬鎖相環的精度較低,而數字鎖相環的精度較高。

2023-02-15 13:47:53 3623

3623 pll鎖相環倍頻的原理? PLL鎖相環倍頻是一種重要的時鐘信號處理技術,廣泛應用于數字系統、通信系統、計算機等領域,具有高可靠性、高精度、快速跟蹤等優點。PLL鎖相環倍頻的原理涉及到鎖相環,倍頻

2023-09-02 14:59:24 1508

1508 pll倍頻最大倍數? PLL倍頻是一種常見的電路設計技術,通常用于將信號的頻率提高到需要的倍數。PLL倍頻的實現原理比較復雜,通常需要使用精密的電路元件、時鐘信號以及數字信號處理器。本文將詳細介紹

2023-09-02 14:59:30 811

811 鎖相環是如何實現倍頻的?? 鎖相環(Phase Locked Loop, PLL)是一種電路,用于穩定和恢復輸入信號的相位和頻率。它可以廣泛應用于通信、計算機、音頻等領域中。其中一個重要的應用就是

2023-09-02 14:59:37 1594

1594 鎖相環倍頻器鎖在基頻怎么辦?? 鎖相環倍頻器是一種基于相位鎖定原理的電子設備,它能夠將輸入信號的頻率倍增。然而,有時候鎖相環倍頻器會鎖在基頻上,導致無法達到所要求的倍頻效果。這時候,我們需要采取一些

2023-09-02 15:12:31 369

369 用FPGA的鎖相環PLL給外圍芯片提供時鐘 FPGA鎖相環PLL(Phase-Locked Loop)是一種廣泛使用的時鐘管理電路,可以對輸入時鐘信號進行精確控制和提高穩定性,以滿足各種應用場

2023-09-02 15:12:34 1319

1319 數字電路如何實現倍頻?? 數字電路是由數字電子器件以及邏輯門電路組成,可以用于處理數字信號或數字數據。其中最基本的電子器件有晶體管、二極管等,而邏輯門電路包括了與門、或門、非門、異或門等。在數字電路

2023-09-18 10:37:43 3084

3084 、無線通信、數據轉換、模擬信號處理等眾多應用領域。然而,頻繁的開關PLL的電源可能對其造成不良影響。 PLL芯片是由多個模擬電路和數字電路組成的。在PLL芯片中,鎖相環控制器是最重要的組成部分。這個控制器包含一個相位檢測器

2023-10-30 10:16:40 267

267 fpga和數字ic區別 FPGA(現場可編程邏輯門陣列)和數字IC(集成電路)在設計、功能、應用等方面存在顯著的區別。 FPGA和數字IC在設計上有不同的特點。FPGA是一種可以重構電路的芯片

2024-03-14 18:08:23 340

340

![]()

![]()

電子發燒友App

電子發燒友App

評論