這次我們來講一下Linux進(jìn)程通信中重要的通信方式:共享內(nèi)存作為Linux軟件開發(fā)攻城獅,進(jìn)程間通信是必須熟練掌握的重要技能,而共享內(nèi)存是在程序開發(fā)中常用的也是重要的一種進(jìn)程間通信方式。

2023-04-26 17:14:47 560

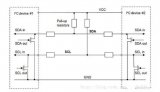

560 IIC總線的FPGA實(shí)現(xiàn)原理及過程 IIC總線概述 IIC開發(fā)于1982年,當(dāng)時(shí)是為了給電視機(jī)內(nèi)的CPU和外圍芯片提供更簡易的互連方式。電視機(jī)是早的嵌入式系統(tǒng)之一,而初的嵌入系統(tǒng)是使用內(nèi)存映射

2023-05-15 02:35:01 1519

1519

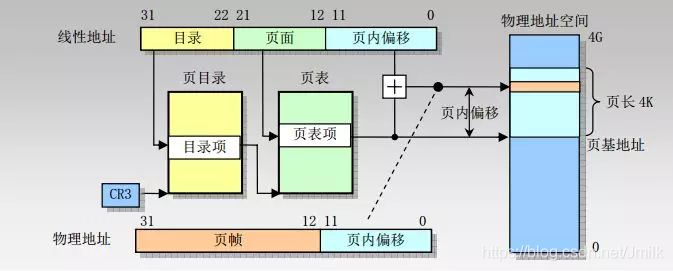

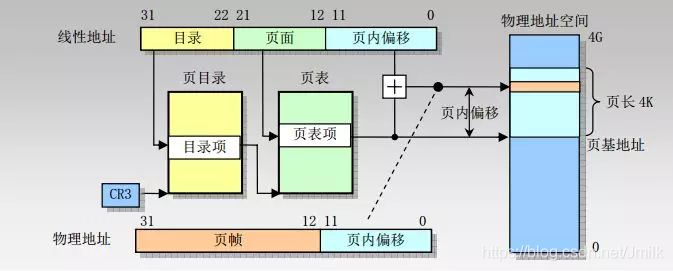

虛擬內(nèi)存技術(shù)是操作系統(tǒng)實(shí)現(xiàn)的一種高效的物理內(nèi)存管理方式

2023-08-10 12:57:02 557

557

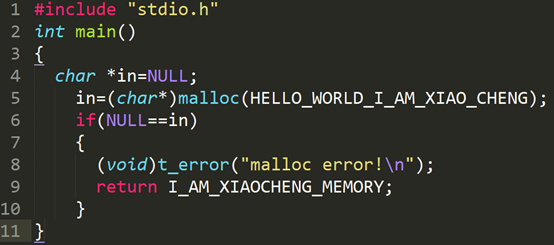

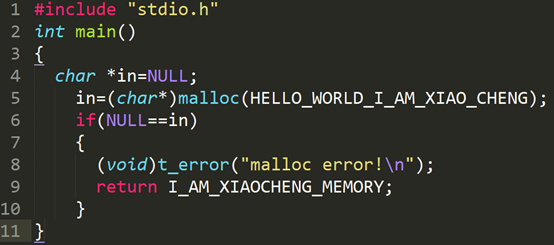

C語言程序設(shè)計(jì)中,動態(tài)內(nèi)存分配如何實(shí)現(xiàn),需要注意哪些問題?

2023-09-28 16:53:41 803

803 的解密算法解密后,加載到內(nèi)部RAM運(yùn)行?這樣,只要將編譯好的程序經(jīng)過一定的加密算法處理后,再燒寫到SPIFLASH中,就算別人能夠讀出程序也沒什么作用。有沒有這種功能或者實(shí)現(xiàn)方式?

2018-10-22 09:17:04

本帖最后由 發(fā)燒友LV 于 2014-12-29 20:13 編輯

在FPGA中實(shí)現(xiàn)PID算法,面臨著小數(shù)的計(jì)算,請問大家一般是怎么處理的?

2014-12-03 21:59:29

本帖最后由 eehome 于 2013-1-5 09:47 編輯

fpga實(shí)現(xiàn)spi接口FPGA實(shí)現(xiàn)SPI接口(包括主機(jī)和從機(jī)程序)

2012-08-11 18:07:40

FPGA實(shí)現(xiàn)SPI的程序實(shí)例

2012-08-11 17:59:52

FPGA(Field-Programmable Gate Array,現(xiàn)場可編程門陣列)是一種特殊的集成電路,其內(nèi)部結(jié)構(gòu)由大量的可配置邏輯塊和互連線組成。FPGA可以通過編程來實(shí)現(xiàn)各種數(shù)字系統(tǒng)功能

2024-01-26 10:03:55

PHY是什么意思?FPGA實(shí)現(xiàn)網(wǎng)口通信主要有哪幾種方式?

2022-02-22 07:57:17

1. 如何實(shí)現(xiàn)FPGA局部動態(tài)加載。2. pcie部分不變,實(shí)現(xiàn)部分程序加載。3. 目前是通過JTAG線,通過PCIE加載的FPGA程序。4. 現(xiàn)在是想通過更改bin文件,不通過JTAG的方式加載。

2021-03-08 09:32:33

現(xiàn)場可編程門陣列(FPGA)作為專用集成電路(ASIC)領(lǐng)域的一種半定制電路,可以根據(jù)設(shè)計(jì)的需要靈活實(shí)現(xiàn)各種接口或者總線的輸出,在設(shè)備端的通信產(chǎn)品中已得到越來越廣泛的使用。1 FPGA 常用配置方式

2019-07-12 07:00:09

現(xiàn)場可編程門陣列(FPGA)作為專用集成電路(ASIC)領(lǐng)域的一種半定制電路,可以根據(jù)設(shè)計(jì)的需要靈活實(shí)現(xiàn)各種接口或者總線的輸出,在設(shè)備端的通信產(chǎn)品中已得到越來越廣泛的使用。FPGA

2019-06-14 06:00:00

,要是考慮多種配置模式,可以采用跳線設(shè)計(jì)。讓配置方式在跳線中切換,上拉電阻的阻值可以采用10K一般在做FPGA實(shí)驗(yàn)板的時(shí)候,用AS+JTAG方式,這樣可以用JTAG方式調(diào)試,而最后程序已經(jīng)調(diào)試無誤了后

2017-11-22 09:37:02

,調(diào)試結(jié)束后正式運(yùn)行時(shí)一般是將配置數(shù)據(jù)放在串行PROM中,上電時(shí)向FPGA加載邏輯。但對于系統(tǒng)實(shí)際運(yùn)行還有一些更快更靈活的配置方式,可以縮短FPGA的重構(gòu)時(shí)間,實(shí)現(xiàn)靈活重構(gòu)。如ALTERA公司的FPGA

2011-05-27 10:22:59

fpga如何控制內(nèi)存條

2014-12-02 09:41:51

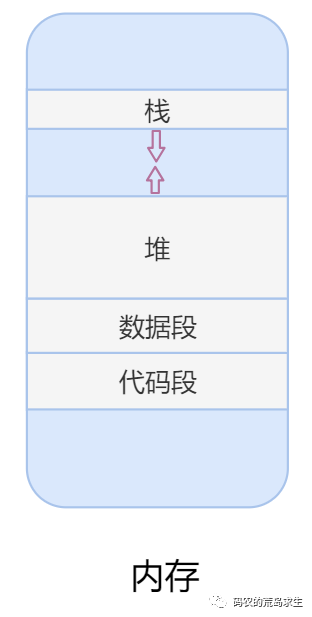

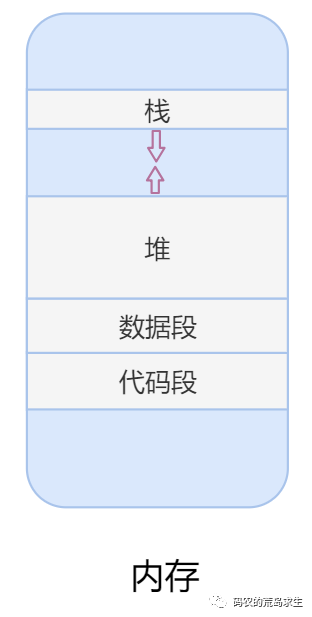

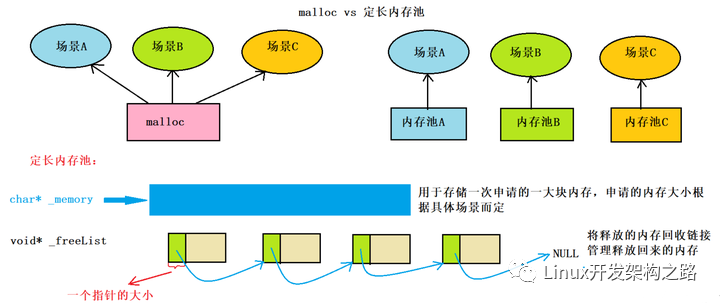

內(nèi)存管理程序結(jié)構(gòu)內(nèi)存分配方式內(nèi)存管理函數(shù)mallocrealloccallocmemsetfree堆和棧的區(qū)別管理方式不同空間大小不同是否產(chǎn)生碎片增長方向不同分配方式不同分配效率不同程序結(jié)構(gòu)棧區(qū)堆區(qū)

2021-12-17 07:15:05

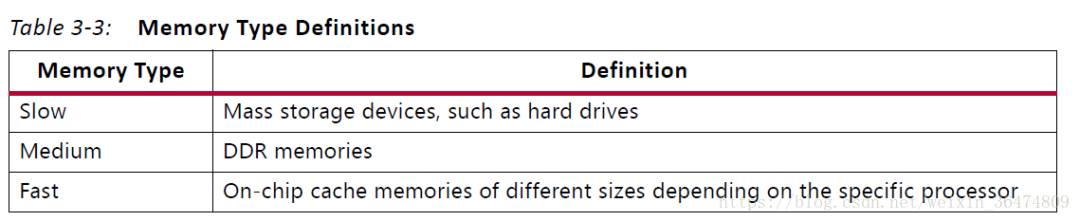

x86上的應(yīng)用開啟cache獲取內(nèi)存視圖1、內(nèi)存1.1程序局部性原理程序一旦編譯裝載進(jìn)內(nèi)存中,它的地址就確定了。也就是說,CPU 大多數(shù)時(shí)間在訪問相同或者與此相鄰的地址,換句話說就是:CPU 大多數(shù)時(shí)間在執(zhí)行相同的指令或者與此相鄰的指令。這就是大名鼎鼎的程序局部性原理。2、內(nèi)存的結(jié)構(gòu)特性從專業(yè)角度講,內(nèi)存

2022-01-12 08:05:03

的程序可以根據(jù)需要有選擇的加載時(shí)不能采用這種方法。本文實(shí)現(xiàn)了一種基于外部處理器的加載方法,速度快,而且可以根據(jù)設(shè)置給FPGA加載相應(yīng)的程序。對于 公司的 FPGA芯片,有五種加載方式:JTAG模式,串行從

2019-12-10 17:42:18

1.ARM有六類指令集:跳轉(zhuǎn)指令、數(shù)據(jù)處理指令、程序狀態(tài)寄存器傳輸指令、Load/Store指令、協(xié)處理器指令、異常中斷產(chǎn)生指令2.ARM中實(shí)現(xiàn)程序跳轉(zhuǎn)的方式有兩種:1).通過跳轉(zhuǎn)指令2).直接向

2022-04-27 09:26:06

存儲器工具包,可幫助您測試FPGA設(shè)備中IP的實(shí)現(xiàn)。

有關(guān)Altera支持的最大速度,請參閱外部存儲器接口規(guī)格估計(jì)器頁面FPGA。

2023-09-26 07:38:12

這個(gè)驅(qū)動程序是Beaglebone與FPGA通訊的程序,基于GPMC方式。 原作者是chenzhufly。

2014-10-22 18:42:48

和主機(jī)依賴性),內(nèi)存分解的概念到目前為止還沒有成功實(shí)現(xiàn)。CAMEL為大型存儲系統(tǒng)提供世界上第一個(gè)CXL解決方案框架,可以在大數(shù)據(jù)應(yīng)用程序(如機(jī)器學(xué)習(xí),內(nèi)存數(shù)據(jù)庫和現(xiàn)實(shí)圖形分析)中實(shí)現(xiàn)出色的性能。CAMEL

2022-11-15 11:14:59

中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。FPGA的開發(fā)相對于傳統(tǒng)PC、單片機(jī)的開發(fā)有很大不同。FPGA以并行運(yùn)算為主,以硬件描述語言來實(shí)現(xiàn);相比于

2018-09-03 09:17:44

LabVIEW 程序的內(nèi)存的優(yōu)化一. VI 在內(nèi)存中的結(jié)構(gòu) 打開一個(gè)VI的屬性面板(VI Properties),其中

2009-07-13 17:57:03

采用同步方式。使用RAM_STYLE屬性可以強(qiáng)制規(guī)定使用哪種方法實(shí)現(xiàn)RAM。Xilinx FPGA的內(nèi)存接口具有如下特性:支持任意大小的深度和數(shù)據(jù)寬度(綜合時(shí)會使用一個(gè)或多個(gè)RAM原語實(shí)現(xiàn));單端、偽

2020-09-29 09:40:40

大家好,最近剛接觸FPGA不久 現(xiàn)在手上有一塊xilinx SP3E開發(fā)板,簡單的設(shè)計(jì)了一個(gè)流水燈的程序 通過JTAG下載方式 直接下到FPGA里 板子可以運(yùn)行 因?yàn)橄?b class="flag-6" style="color: red">實(shí)現(xiàn)斷電后重啟板子自動

2014-10-11 11:16:08

這幾天一直對FPGA的程序下載方式感到疑惑,特別是關(guān)于SPI的下載以及多個(gè)芯片的程序下載控制。先說說單片下載問題。以Xilinx的下載方式為例,通常我們做實(shí)驗(yàn)、自己學(xué)習(xí)的時(shí)候都是以JTAG模式下載

2017-09-20 21:29:07

1. 現(xiàn)有一塊xc7vx690tffg芯片。2. 之前寫的fpga程序都是通過在vivado上JTAG線的方式,將mcs文件燒寫到flash中,現(xiàn)聽說部分加載fpga程序,可以直接更改上位機(jī)程序里的bin文件方式就可部分加載fpga程序,更為方便快捷,還請問部分加載技術(shù)該如何實(shí)現(xiàn)。

2021-03-01 10:45:28

在ARM+FPGA的架構(gòu)中,想通過串口燒寫FPGA程序,硬件如何實(shí)現(xiàn),各位大神請幫幫忙。

2018-05-15 22:33:16

的劃分,單片機(jī)啟動等知識點(diǎn)。flash中包括指令,常量,經(jīng)初始化的變量ram中包括局部變量,未初始化的變量,堆區(qū),棧區(qū)單片機(jī)的運(yùn)行不同與pc,由于硬件資源的限制,不會把程序段全部加載到內(nèi)存中執(zhí)行,而是

2022-01-17 06:39:24

FPGA中接口的連接方式。 ??也許很多FPGA工程師對SystemVerilog并不是很了解,因?yàn)橐郧暗?b class="flag-6" style="color: red">FPGA開發(fā)工具是不支持SystemVerilog的,導(dǎo)致大家都是用VHDL或者Verilog來

2021-01-08 17:23:22

存儲設(shè)備中,是實(shí)現(xiàn)模塊功能的定義,而Labview FPGA的程序編譯是實(shí)現(xiàn)背板上FPGA與模塊I/O的通信,作用對象是機(jī)箱背板的FPGA。我們最終在NI CompactRIO機(jī)箱中使用的只是熱插拔I/O模塊的I/O口,是通過Labview FPGA對機(jī)箱背板的FPGA進(jìn)行編程實(shí)現(xiàn)I/O模塊的操作。

2017-09-23 16:55:58

存儲設(shè)備.基于FPGA的SATA主機(jī)控制器特性如下:1. 支持SATA 1(1.5Gbps)、SATA 2(3Gbps)以及SATA 3(6Gbps)2. 符合SATA Rev 3.0規(guī)范3. 實(shí)現(xiàn)

2015-11-11 15:06:39

單片機(jī)BootLoader的通用實(shí)現(xiàn)方式(備份升級,永不掛機(jī))背景介紹實(shí)現(xiàn)方式背景介紹當(dāng)我們在進(jìn)行Linux下進(jìn)行C語言程序開發(fā)時(shí),由于C語言指針和內(nèi)存的靈活性,經(jīng)常會出現(xiàn)段錯(cuò)誤導(dǎo)致程序異常結(jié)束,本文提供一種段錯(cuò)誤問題的一種分析排查與解決思路。實(shí)現(xiàn)方式...

2021-07-21 06:55:18

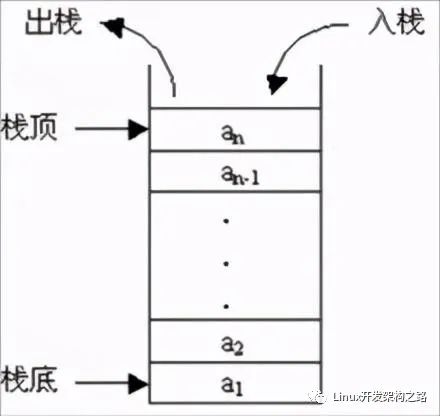

目錄一、堆區(qū)(HEAP)二、棧區(qū)(STACK)三、堆棧的區(qū)別四、內(nèi)存分配的方式五、堆棧溢出六、總結(jié)一、堆區(qū)(HEAP)堆區(qū)(HEAP):一般由程序員分配釋放, 若程序員不釋放,程序結(jié)束時(shí)可能由OS

2021-11-24 06:29:48

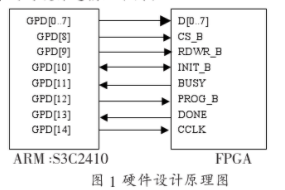

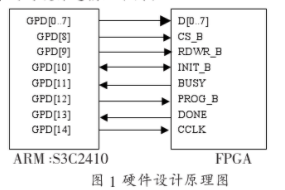

ARM跟FPGA通信,要采用8位地址總線、8位數(shù)據(jù)總線、讀寫控制線,怎么實(shí)現(xiàn),地址總線是要映射到FPGA的內(nèi)部還是直接ARM的內(nèi)存空間?最好有ARM端簡單的C程序描述下,謝謝。

2022-11-22 14:58:26

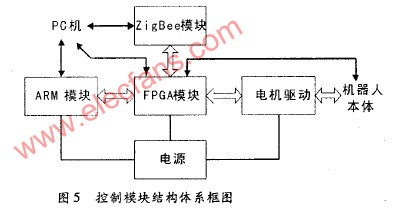

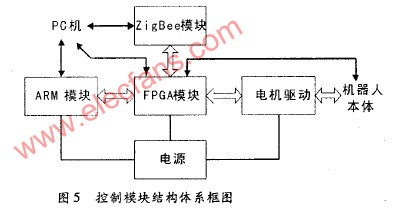

狀態(tài)機(jī)如圖4所示。圖 4 TCP狀態(tài)機(jī)的FPGA實(shí)現(xiàn)采用模塊化、自頂向下的方式進(jìn)行FPGA程序設(shè)計(jì),即頂層Top模塊作為總控部分,下一層分為時(shí)鐘生成、數(shù)據(jù)控制和W5500控制三大模塊,即如下圖5所示

2018-08-07 10:10:25

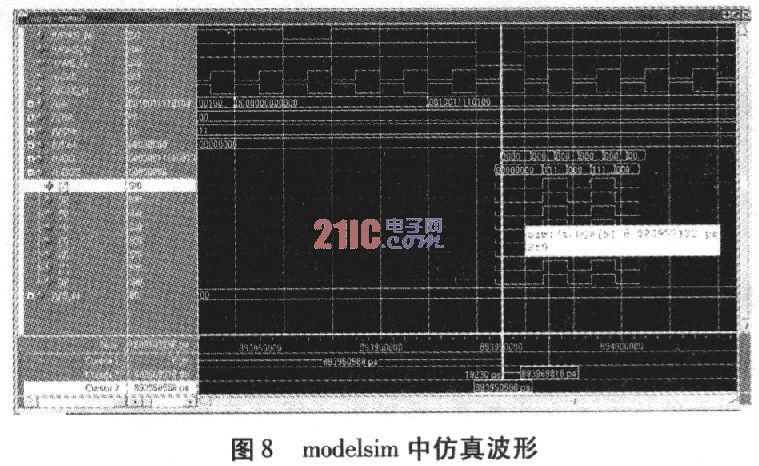

本文基于VHDL方式實(shí)現(xiàn)了QPSK數(shù)字調(diào)制解調(diào)電路的設(shè)計(jì),通過QuartusII軟件建模對程序進(jìn)行仿真,并通過引腳鎖定,下載到FPGA芯片EP1K30TC144—3中,軟件仿真和硬件驗(yàn)證結(jié)果表明了該

2020-12-18 06:03:26

我想與使用FPGA進(jìn)行內(nèi)存映射(A0-A26和D0-D15)的GPMC接口進(jìn)行通信。哪些是我需要在FPGA中考慮GPMC通信的所有控制信號?

2020-05-01 12:09:21

,最終程序編譯通過了,但是出現(xiàn)了4個(gè)時(shí)序約束問題,實(shí)際BULK OUT可以傳出數(shù)據(jù),但是BULK IN接收數(shù)據(jù)失敗。

請問是否是我所使用的方式有誤?所提供的verilog文件是否有更詳細(xì)的使用說明?

或者說,該如何使用FPGA與FX3實(shí)現(xiàn)數(shù)據(jù)的傳輸?

2024-02-28 07:44:14

在FPGA中,動態(tài)相位調(diào)整(DPA)主要是實(shí)現(xiàn)LVDS接口接收時(shí)對時(shí)鐘和數(shù)據(jù)通道的相位補(bǔ)償,以達(dá)到正確接收的目的。那么該如何在低端FPGA中實(shí)現(xiàn)DPA的功能呢?

2021-04-08 06:47:08

最近老師讓我們研究一下,如何把編好的程序下載到multisim的fpga軟件中實(shí)行仿真,如果這個(gè)可以實(shí)現(xiàn)我們學(xué)生做實(shí)驗(yàn)就可以不用到實(shí)驗(yàn)室實(shí)驗(yàn)可以在電腦上進(jìn)行實(shí)驗(yàn),希望廣大的神友們能夠幫幫忙

2017-03-29 20:51:45

我將我的APP程序放入地址為0x10000為首地址的flash內(nèi)存里,在BOOT程序中判斷進(jìn)行地址跳轉(zhuǎn),可是無法實(shí)現(xiàn)?

2023-06-27 07:58:04

會自動存儲在FPGA的內(nèi)存中。以上來自于谷歌翻譯以下為原文Hi I am using ZC706 board to transmit a modulated signal. We have

2019-05-06 07:25:49

需要通過無線的方式給FPGA芯片下載程序。 不怕復(fù)雜一點(diǎn);不怕成本高一點(diǎn);只要實(shí)現(xiàn)就行 搞個(gè)中轉(zhuǎn)的單片機(jī)?之前看到過成功地給51單片機(jī)無線下載程序,不知道可否參考這個(gè)思路? 能不能哪位大神指點(diǎn)一下啊,多謝

2015-11-17 13:29:52

本帖最后由 gk320830 于 2015-3-4 17:23 編輯

求助,有什么方式能夠用FPGA實(shí)現(xiàn)虛擬光柵的生成

2014-11-03 23:07:57

剛接觸FPGA 想用FPGA實(shí)現(xiàn)422通訊 求大牛給一個(gè)實(shí)現(xiàn)UART的VHDL的程序

2013-12-05 20:40:39

DDS的基本原理是什么,有什么性能指標(biāo)?基于FPGA的DDFS與DDWS兩種實(shí)現(xiàn)方式

2021-04-30 06:13:06

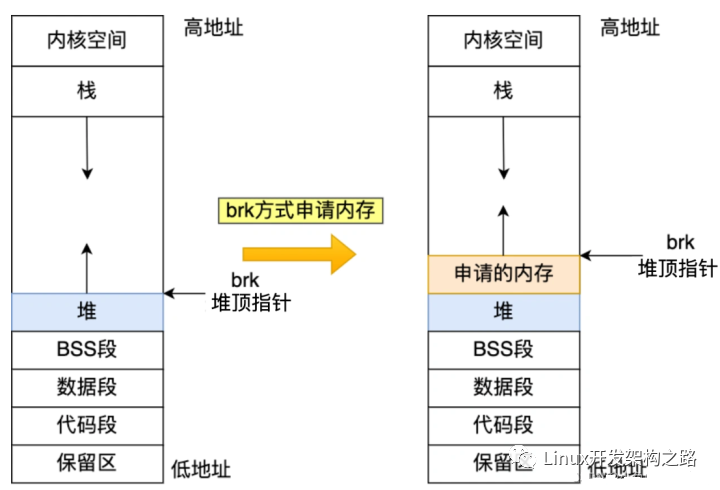

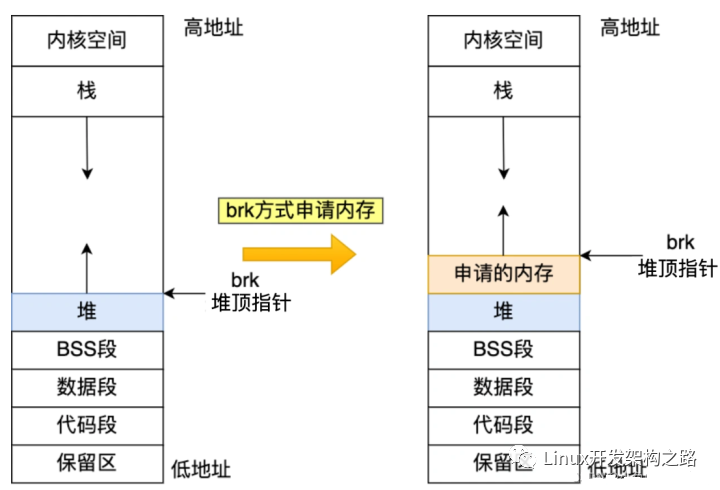

、Linux 系統(tǒng)下,有幾種堆空間分配方式?上面幾個(gè)問題,你心里有答案嗎?如果沒有,跟我一起來探究一下吧1、User space 與 Kernel space現(xiàn)代的應(yīng)用程序都運(yùn)行在一個(gè)內(nèi)存空間里,在 32 位

2020-12-26 01:39:40

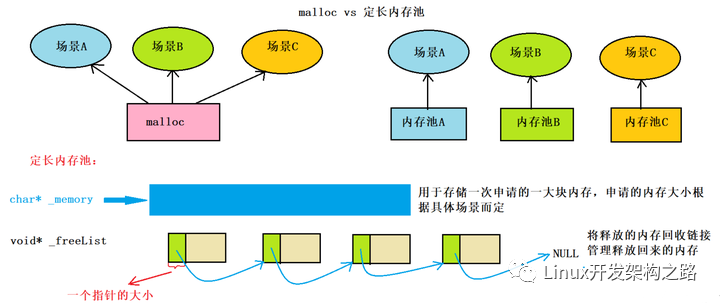

如題,最近在移植LWIP,參考原子戰(zhàn)艦V3,由于我的系統(tǒng)沒實(shí)現(xiàn)內(nèi)存管理,因此,涉及到malloc的函數(shù)我全部使用全局?jǐn)?shù)據(jù)區(qū)來開辟空間(暫時(shí)先這么粗略地實(shí)現(xiàn)),但對內(nèi)存池的內(nèi)存分配我實(shí)現(xiàn)是沒看明白,在

2019-09-02 04:36:26

介紹一種在嵌入式系統(tǒng)中使用微處理器被動串行配置方式實(shí)現(xiàn)對FPGA配置的方案,將系統(tǒng)程序及配置文件存在系統(tǒng)Flash 中,利用微處理器的I/O 口產(chǎn)生配置時(shí)序,省去配置器件;討論FPG

2009-04-15 11:02:53 13

13 NandFlash控制器的FPGA實(shí)現(xiàn)方法技巧與程序案例分享。

2017-09-21 09:40:00 78

78 首先介紹了內(nèi)存條的工作原理,內(nèi)存條電路設(shè)計(jì)的注意事項(xiàng),以及如何使用FPGA實(shí)現(xiàn)對DDR內(nèi)存條的控制,最后給出控制的仿真波形。

1 內(nèi)存條的工作原理 DDR內(nèi)存

2010-06-29 15:37:56 2269

2269

摘要:文中詳述了FPGA被動串行配置方式的時(shí)序,給出配置流程圖及實(shí)現(xiàn)的程序代碼,并通過實(shí)例驗(yàn)證了該方法的優(yōu)越

2010-07-21 14:48:48 1326

1326

本文闡述了主同步搜索的改進(jìn)型算法,并且針對這種算法提出了基于片上RAM 的實(shí)現(xiàn)方式,最大程度地節(jié)省了FPGA 的硬件資源,為WCDMA 同步的FPGA 實(shí)現(xiàn)提供了很好的解決方案。這種技術(shù)可

2011-05-14 16:45:53 30

30 附件為:VB內(nèi)存搜索程序及控件源代碼 VB內(nèi)存搜索控件-修正版,以及內(nèi)存搜索程序,在VisualBasic6.0下可順利編譯,搜索支持多種條件選擇,程序具體運(yùn)行結(jié)果請參看下圖。

2012-10-17 09:12:28 84

84 基于FPGA的SOQPSK調(diào)制方式的設(shè)計(jì)與仿真

2016-01-04 15:31:55 0

0 使用C語言編程時(shí),關(guān)于程序設(shè)計(jì)之內(nèi)存管理。

2016-05-20 17:01:11 0

0 Xilinx FPGA工程例子源碼:在FPGA上實(shí)現(xiàn)CRC算法的程序

2016-06-07 15:07:45 28

28 ? 和 ?Xilinx Ehab Mohsen? 聊到了將 ?DDR4? 與 ?Xilinx UltraScale? FPGA? 相結(jié)合可實(shí)現(xiàn)的驚人性能優(yōu)勢和功能。 立即觀看在線座談 ??

2017-02-09 06:18:33 470

470 并口通信是最常用基礎(chǔ)功能,實(shí)現(xiàn)ARM9與FPGA的并口通信有兩種方式,一種頗為巧妙,利用SMC(Static Memory Controllor),其中的使能點(diǎn)都通過寄存器可以輕松控制;另一種方式就是通過GPIO來完成。

2018-06-17 09:41:00 5930

5930 FPGA有多種配置/加載方式。粗略可以分為主動和被動兩種。主動加載是指由FPGA控制配置流程,被動加載是指FPGA僅僅被動接收配置數(shù)據(jù)。

2018-10-05 10:12:00 17251

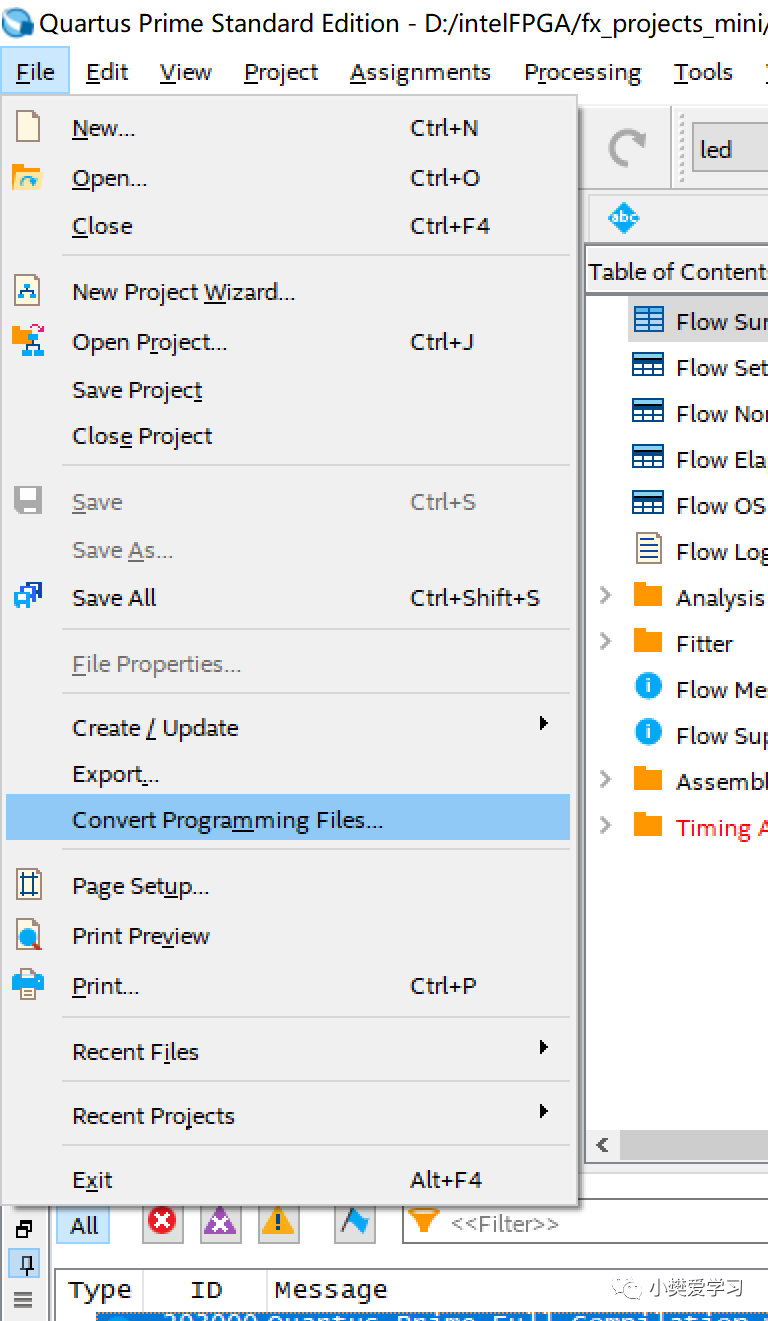

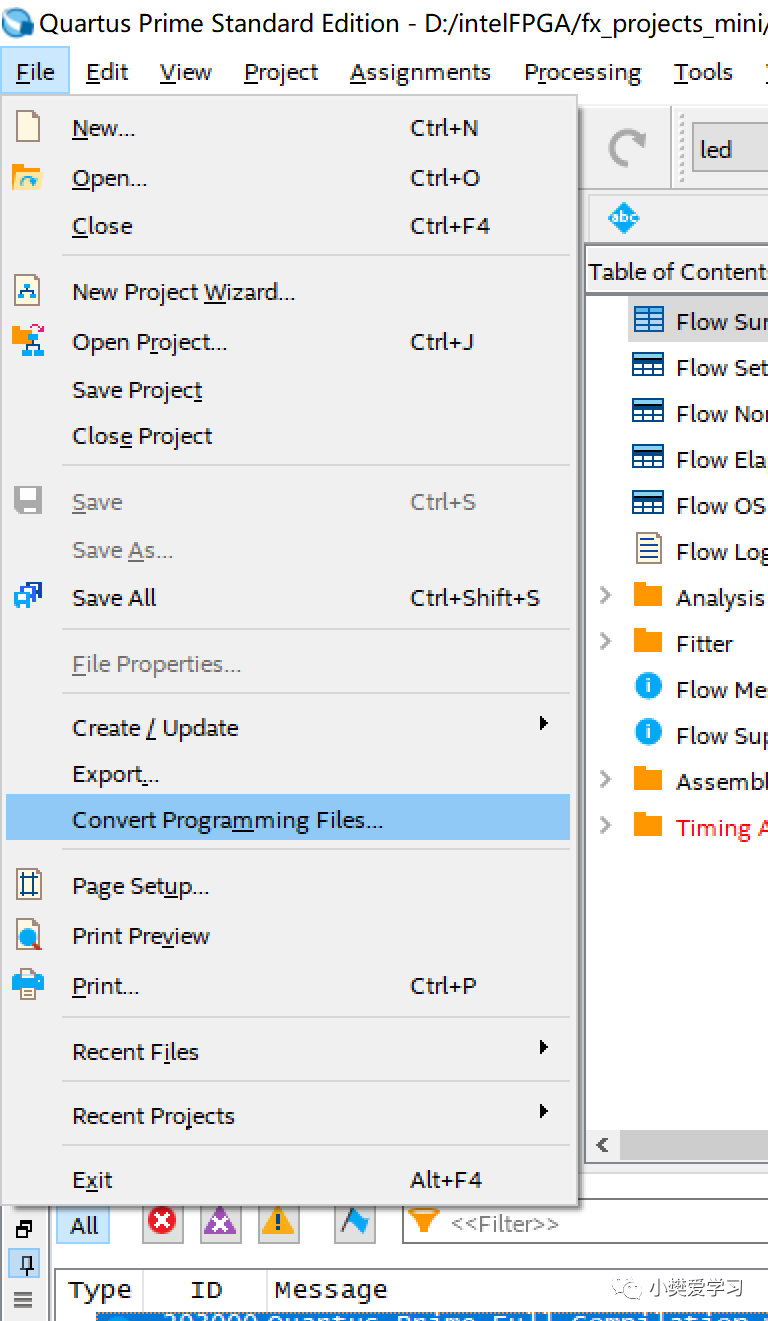

17251 學(xué)習(xí)FPGA的程序下載方式,包含altera和xilinx程序下載方式,下載程序所用格式分類以及格式轉(zhuǎn)換工具介紹。

2018-10-31 08:00:00 17

17 說到內(nèi)存的分配方式,就不得不提連續(xù)分配方式。這種方式是指為一個(gè)用戶程序分配一個(gè)連續(xù)的內(nèi)存空間,它曾被廣泛的用于20世紀(jì)60~70年代的OS中,至今仍被使用。連續(xù)分配方式可以進(jìn)一步分為單一連續(xù)分配、固定分配方式、動態(tài)分區(qū)分配以及動態(tài)重定位分配。

2019-03-03 11:22:20 1245

1245 在系統(tǒng)上電時(shí),需要從外部載入所要運(yùn)行的程序,此過程被稱為程序加載。多數(shù)情況下,從外部專用的 讀入程序。這種方式速度慢,而且只能加載固定的程序。顯然,當(dāng)系統(tǒng)需要容量大而且 FPGA要加載的程序可以

2019-03-22 16:20:14 952

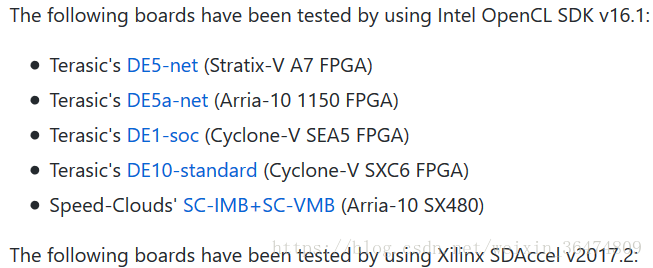

952 實(shí)現(xiàn)這一編程思想的轉(zhuǎn)變,是因?yàn)?FPGA 借助 OpenCL 實(shí)現(xiàn)了編程,程序員只需要通過 C/C++ 添加適當(dāng)?shù)?pragma 就能實(shí)現(xiàn) FPGA 編程。為了讓您用 OpenCL 實(shí)現(xiàn)的 FPGA

2020-07-16 17:58:28 6015

6015

FPGA在系統(tǒng)上電時(shí),需要從外部載入所要運(yùn)行的程序,此過程被稱為程序加載。多數(shù)情況下,FPGA從外部專用的 EPROM讀入程序。這種方式速度慢,而且只能加載固定的程序。顯然,當(dāng)系統(tǒng)需要容量大而且

2020-08-13 17:16:46 1805

1805

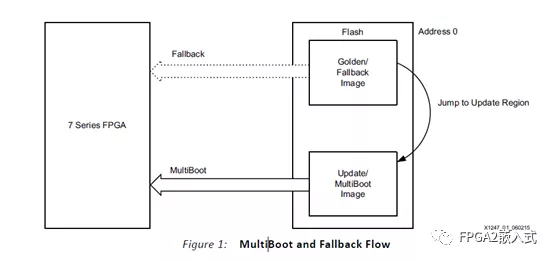

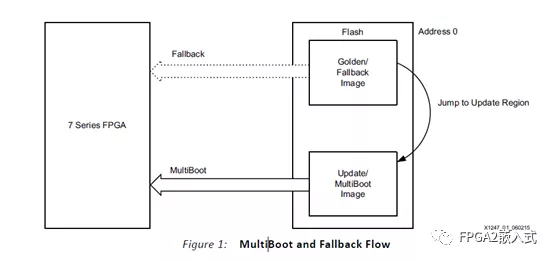

7 Series FPGAs MultiBoot功能指讓FPGA從2個(gè)或者多個(gè)BIT文件中加載一個(gè)BIT文件運(yùn)行程序,所以它的2個(gè)主要應(yīng)用如下: 1. 更新新的BIT時(shí),當(dāng)更新失敗或BIT出錯(cuò)會返回

2020-12-11 14:58:42 1461

1461

Xilinx7系列FPGA的體系結(jié)構(gòu)具有靈活的內(nèi)部內(nèi)存資源,可以配置為各種不同的大小。本白皮書詳細(xì)介紹了可用的功能,說明了各種可用內(nèi)存大小,并顯示了使用不同資源執(zhí)行不同大小內(nèi)存功能的利弊。

2020-12-09 16:15:00 8

8 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)自動售貨機(jī)的VHDL程序與仿真資料。

2020-12-21 17:10:00 23

23 數(shù)據(jù)信號,從而把EPCS**的數(shù)據(jù)讀入FPGA中,實(shí)現(xiàn)對FPGA的編程配置數(shù)據(jù)通過FPGA_DATA0引腳送入FPGA,配置數(shù)據(jù)被同步在FPGA_DCLK上,1個(gè)時(shí)鐘傳送1位數(shù)據(jù)。

2021-01-05 16:21:16 21

21 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)電子琴程序設(shè)計(jì)的程序與仿真資料免費(fèi)下載。

2021-01-18 17:17:29 36

36 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)LCD控制的VHDL程序與仿真資料免費(fèi)下載。

2021-01-18 17:19:08 10

10 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)LED控制的VHDL程序與仿真資料免費(fèi)下載。

2021-01-18 17:32:46 12

12 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)PWM電源的程序和工程文件免費(fèi)下載。

2021-01-19 15:53:24 5

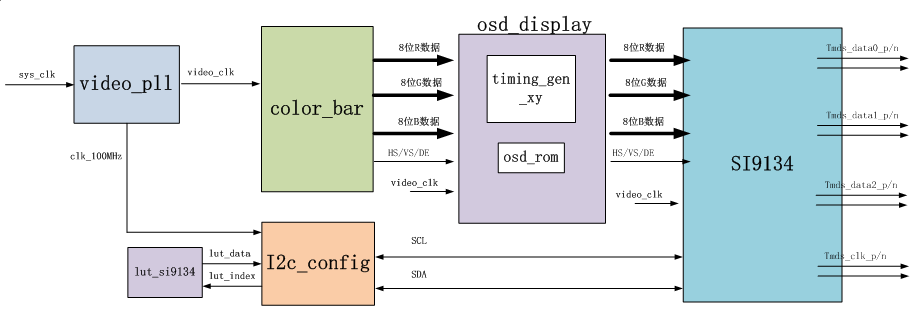

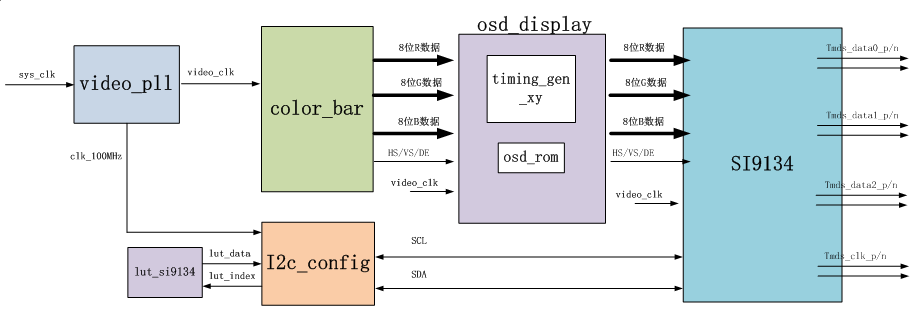

5 在HDMI輸出實(shí)驗(yàn)中講解了HDMI顯示原理和顯示方式,本實(shí)驗(yàn)介紹如何使用FPGA實(shí)現(xiàn)字符顯示,通過這個(gè)實(shí)驗(yàn)更加深入的了解HDMI的顯示方式。

2022-02-09 10:29:22 2932

2932

主要介紹基于FPGA實(shí)現(xiàn)多路模擬信號自適應(yīng)采集系統(tǒng)的設(shè)計(jì)。該系統(tǒng)主要包括軟件和硬件兩部分:硬件主要采用FPGA芯片,AD7982—1,ADG406和運(yùn)放AD824來搭建硬件平臺;軟件包括FPGA程序

2021-02-02 15:52:00 4

4 主要介紹基于FPGA實(shí)現(xiàn)多路模擬信號自適應(yīng)采集系統(tǒng)的設(shè)計(jì)。該系統(tǒng)主要包括軟件和硬件兩部分:硬件主要采用FPGA芯片,AD7982—1,ADG406和運(yùn)放AD824來搭建硬件平臺;軟件包括FPGA程序

2021-02-02 15:52:34 5

5 本文檔的主要內(nèi)容詳細(xì)介紹的是使用單片機(jī)實(shí)現(xiàn)62256擴(kuò)展內(nèi)存的C語言程序免費(fèi)下載。

2021-03-16 14:39:28 12

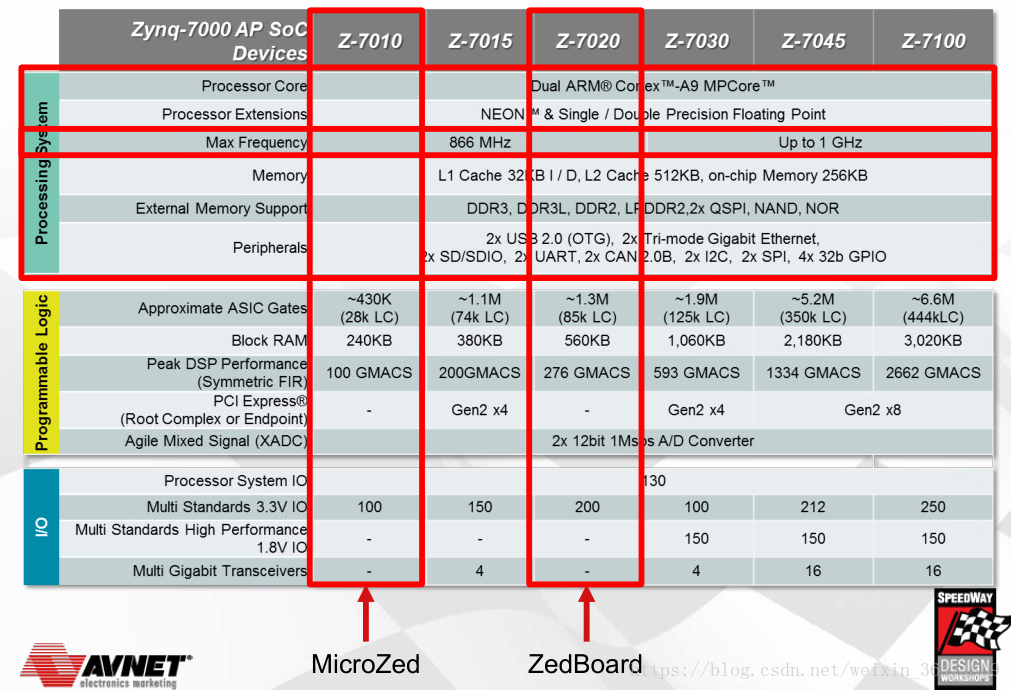

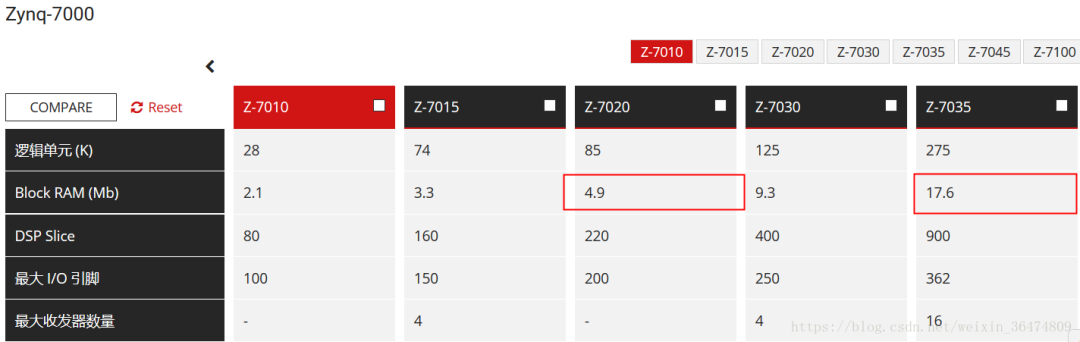

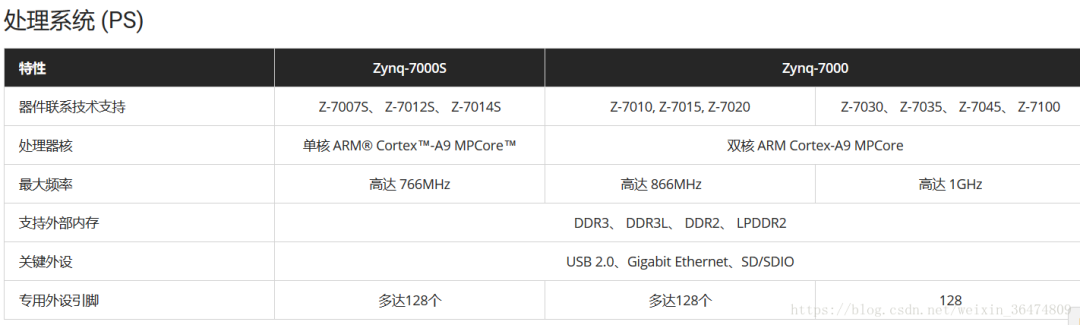

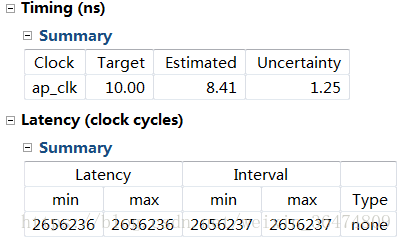

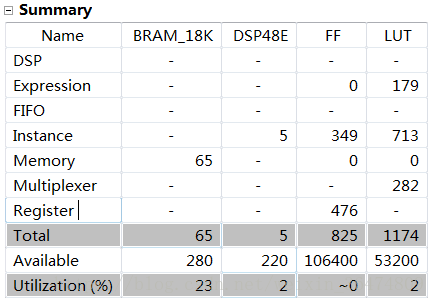

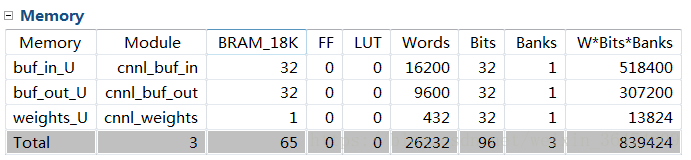

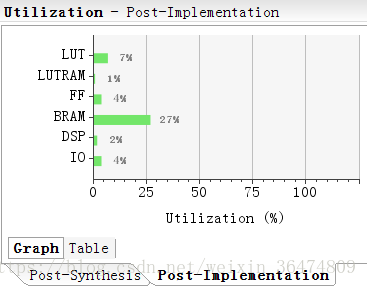

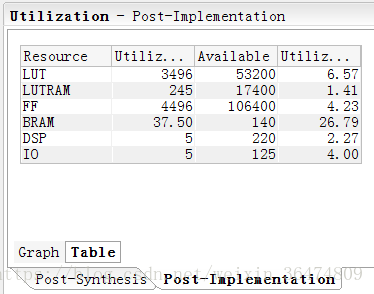

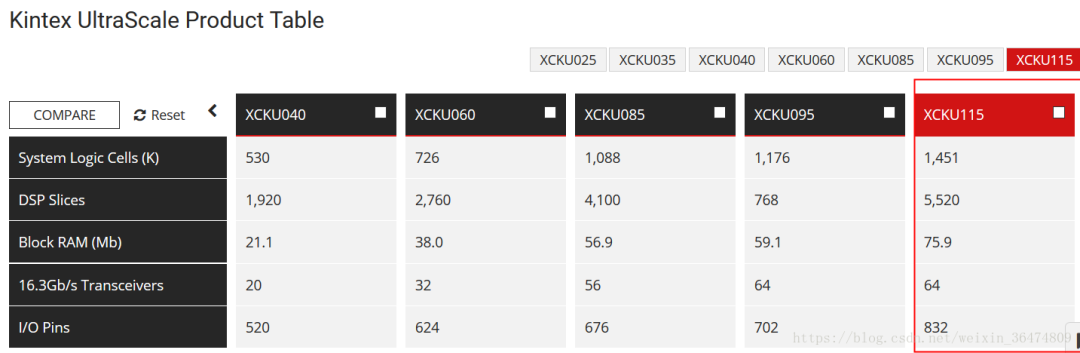

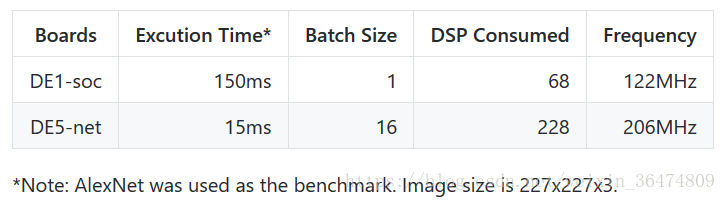

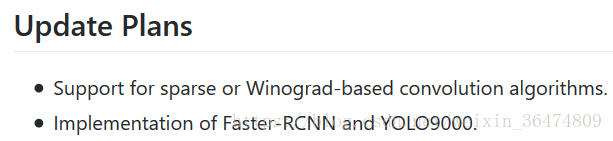

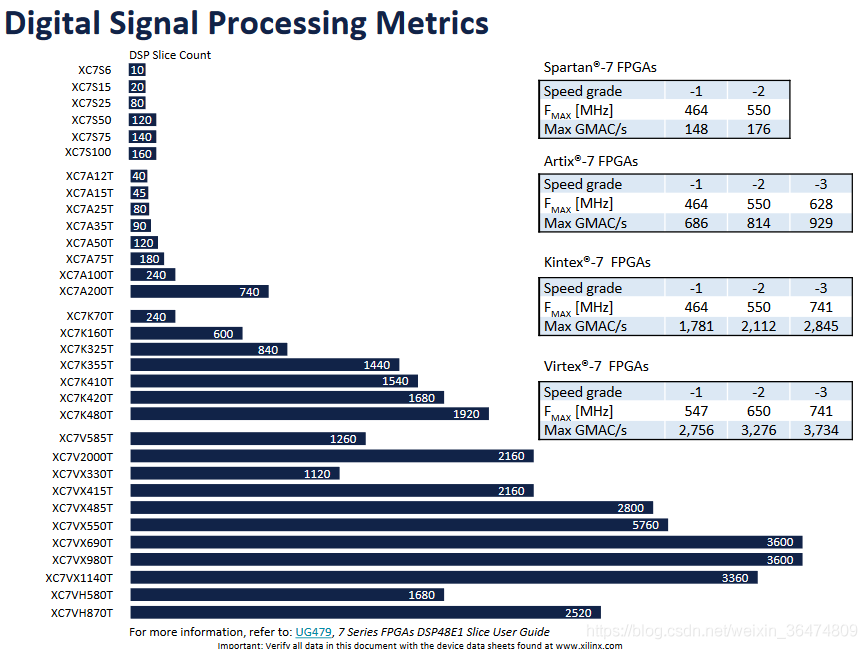

12 Xilinx zynq系列FPGA實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)評估 本篇目錄 1. 內(nèi)存占用 1.1 FPGA程序中內(nèi)存的實(shí)現(xiàn)方式 1.2 Zynq的BRAM內(nèi)存大小 1.3 一個(gè)卷積操作占用的內(nèi)存 2.

2021-04-19 11:12:02 2202

2202

C語言程序的動態(tài)內(nèi)存分為棧內(nèi)存區(qū)域和堆內(nèi)存區(qū)域兩種。棧內(nèi)存是由編譯器管理的,而堆內(nèi)存是由程序調(diào)用具體的庫函數(shù)管理的。我們今天分析下棧內(nèi)存的概念。 棧內(nèi)存的使用在很大程度上依賴于處理器的硬件機(jī)制

2021-06-29 10:34:48 1595

1595 ADC0809驅(qū)動FPGA實(shí)現(xiàn)的verilog程序(通訊電源技術(shù)雜志封面)-該文檔為ADC0809驅(qū)動FPGA實(shí)現(xiàn)的verilog程序總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-08-31 18:33:38 60

60 ? ? 程序內(nèi)存的分配 ? ????一個(gè)由C/C++編譯的程序占用的內(nèi)存分為以下幾個(gè)部分: 棧區(qū)(stack)— 由編譯器自動分配釋放 ,存放函數(shù)的參數(shù)值,局部變量的值等。其操作方式類似于數(shù)據(jù)結(jié)構(gòu)

2021-10-21 14:51:15 2079

2079 *Java、Python等內(nèi)存模型

**

**Java內(nèi)存模型

**

**Jave中的堆區(qū)與棧區(qū)是如何實(shí)現(xiàn)的

**

**Python內(nèi)存模型**

2023-02-24 14:09:56 319

319

FPGA是一種數(shù)字集成電路芯片,名稱為“現(xiàn)場可編程邏輯門陣列”FPGA的一項(xiàng)重要特點(diǎn)是其可編程特性,即用戶可通過程序指定FPGA實(shí)現(xiàn)某一特定數(shù)字電路,FPGA的的組成有CLB,IOB,可編程互聯(lián)資源,SRAM,DSP,時(shí)鐘管理模塊,CLB內(nèi)包含有Filp-Flop和LUT等,可實(shí)現(xiàn)某些組合或時(shí)序邏輯電路;

2023-03-21 14:01:05 412

412 有人說FPGA不需要上電復(fù)位電路,因?yàn)閮?nèi)部自帶上電復(fù)位信號。也有人說FPGA最好加一個(gè)上電復(fù)位電路,保證程序能夠正常地執(zhí)行。不管是什么樣的結(jié)果,這里先把一些常用的FPGA復(fù)位電路例舉出來,以作公示。

2023-05-25 15:50:45 2110

2110

只有在堆內(nèi)存里面才會發(fā)生內(nèi)存泄漏的問題,在棧內(nèi)存中不會發(fā)生內(nèi)存泄漏。因?yàn)闂?b class="flag-6" style="color: red">內(nèi)存在自動分配空間之后,還會自動釋放空間。 什么是堆內(nèi)存?存儲方式是什么樣的呢? 首先我們先來介紹一下堆內(nèi)存在 C 代碼

2023-06-22 10:29:00 683

683

FPGA程序的固化,即掉電后再上電,程序仍能正常運(yùn)行。

2023-07-19 16:41:54 1013

1013

本項(xiàng)目實(shí)現(xiàn)了一個(gè)高并發(fā)內(nèi)存池,參考了Google的開源項(xiàng)目tcmalloc實(shí)現(xiàn)的簡易版;其功能就是實(shí)現(xiàn)高效的多線程內(nèi)存管理。由功能可知,高并發(fā)指的是高效的多線程,而內(nèi)存池則是實(shí)現(xiàn)內(nèi)存管理的。 內(nèi)存

2023-11-09 11:16:57 231

231

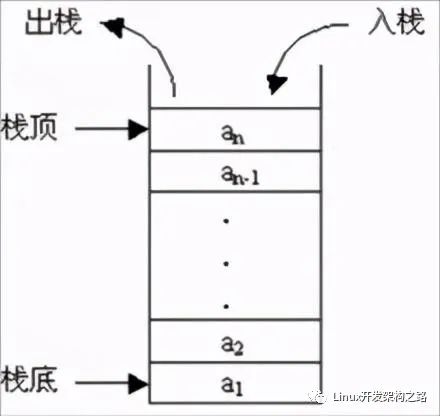

下,堆與棧表示兩種內(nèi)存管理方式; (2)數(shù)據(jù)結(jié)構(gòu)場景下,堆與棧表示兩種常用的數(shù)據(jù)結(jié)構(gòu)。 1.程序內(nèi)存分區(qū)中的堆與棧 1.1 棧簡介 棧由操作系統(tǒng)自動分配釋放 ,用于存放函數(shù)的參數(shù)值、局部變量等,其操作方式類似于數(shù)據(jù)結(jié)構(gòu)中的棧。參考如下代碼:

2023-11-11 16:21:38 468

468

。而brk()的實(shí)現(xiàn)的方式很簡單,就是通過 brk() 函數(shù)將堆頂指針向高地址移動,獲得新的內(nèi)存空間。如下圖:

2023-11-13 11:42:58 826

826

要查看Java程序的內(nèi)存分布,首先需要了解Java程序運(yùn)行時(shí)的內(nèi)存模型。 Java程序的內(nèi)存分布可以分為以下幾個(gè)部分:程序計(jì)數(shù)器、Java虛擬機(jī)棧、本地方法棧、Java堆、方法區(qū)和運(yùn)行時(shí)

2023-11-23 14:47:59 419

419

電子發(fā)燒友App

電子發(fā)燒友App

評論