安全高效的狀態(tài)機(jī)設(shè)計(jì)對(duì)于任何使用FPGA的工程師而言都是一項(xiàng)重要技能。選擇Moore狀態(tài)機(jī)、Mealy狀態(tài)機(jī)還是混合機(jī)取決于整個(gè)系統(tǒng)的需求。無論選擇哪種類型的狀態(tài)機(jī),充分掌握實(shí)現(xiàn)方案所需的工具和技巧,將確保您實(shí)現(xiàn)最佳解決方案。本文主要介紹如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī)

2013-03-29 15:02:57 12361

12361

您好Xilinx用戶。我對(duì)FPGA中的實(shí)際值計(jì)算有疑問。我用實(shí)數(shù)編寫編碼,編碼工作正常但是如果我實(shí)現(xiàn)設(shè)計(jì)我得到了真正的錯(cuò)誤bcoz。我如何在FPGA中合成該編碼。請(qǐng)幫助我。問候,卡西克。小號(hào)

2019-03-19 08:40:47

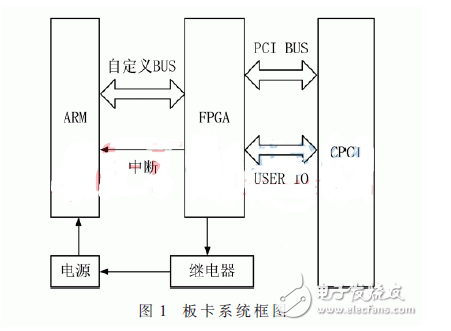

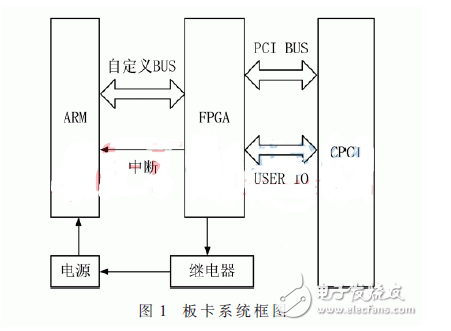

和ASIC中實(shí)現(xiàn)的硬核IP等。圖1即使如此,通用嵌入式系統(tǒng)也很難滿足現(xiàn)代設(shè)計(jì)需求。多芯片解決方案實(shí)現(xiàn)起來相對(duì)容易一些,但是成本高,缺乏設(shè)計(jì)人員所要求的靈活性以及性能/功耗指標(biāo)。采用了軟核處理器的單芯片

2021-07-14 08:00:00

FPGA(Field-Programmable Gate Array,現(xiàn)場(chǎng)可編程門陣列)是一種特殊的集成電路,其內(nèi)部結(jié)構(gòu)由大量的可配置邏輯塊和互連線組成。FPGA可以通過編程來實(shí)現(xiàn)各種數(shù)字系統(tǒng)功能

2024-01-26 10:03:55

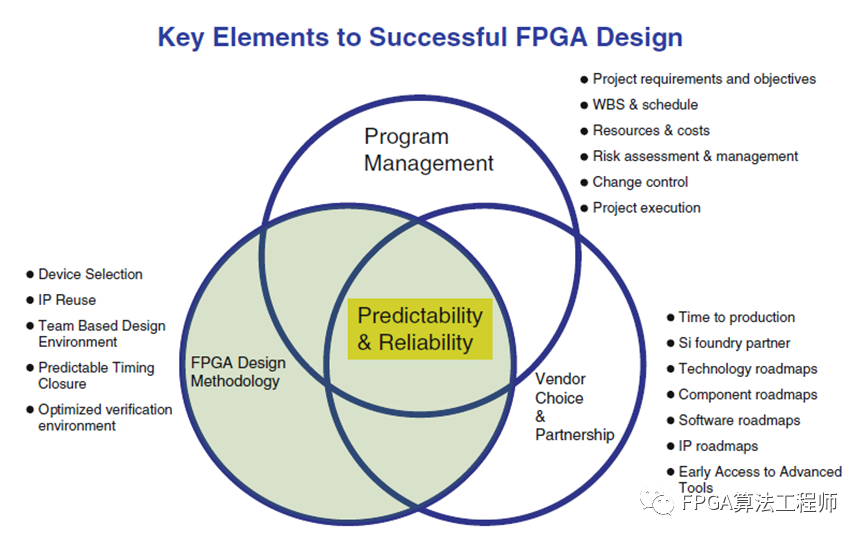

Hezi SaarFPGA是今天許多要求最嚴(yán)苛的嵌入式系統(tǒng)設(shè)計(jì)的重要元件。由于FPGA器件的價(jià)格大幅下跌,加上為設(shè)計(jì)人員帶來的便利性和靈活性,FPGA在競(jìng)爭(zhēng)激烈的全球市場(chǎng)上嵌入式設(shè)計(jì)產(chǎn)品的應(yīng)用中日

2019-07-04 06:22:02

以及最新的DSP系統(tǒng)工具的概況;接著主要介紹了計(jì)算機(jī)算法的概念、理論、有限字長(zhǎng)效用、FIR和IIR濾波器的實(shí)現(xiàn)、多速率和自適應(yīng)信號(hào)處理的FPGA實(shí)現(xiàn);最后,介紹了System Genrerator

2009-07-21 09:22:42

FPGA控制實(shí)現(xiàn)圖像系統(tǒng)

2016-08-15 10:51:31

FPGA設(shè)計(jì)中幀同步系統(tǒng)的實(shí)現(xiàn)數(shù)字通信時(shí),一般以一定數(shù)目的碼元組成一個(gè)個(gè)“字”或“句”,即組成一個(gè)個(gè)“幀”進(jìn)行傳輸,因此幀同步信號(hào)的頻率很容易由位同步信號(hào)經(jīng)分頻得出,但每個(gè)幀的開頭和末尾時(shí)刻卻無法由

2012-08-11 16:22:49

FPGA設(shè)計(jì)中幀同步系統(tǒng)的實(shí)現(xiàn)數(shù)字通信時(shí),一般以一定數(shù)目的碼元組成一個(gè)個(gè)“字”或“句”,即組成一個(gè)個(gè)“幀”進(jìn)行傳輸,因此幀同步信號(hào)的頻率很容易由位同步信號(hào)經(jīng)分頻得出,但每個(gè)幀的開頭和末尾時(shí)刻卻無法由

2012-08-11 17:44:43

FFT如何在STM32中的實(shí)現(xiàn)與應(yīng)用

2021-10-13 08:58:26

以及最新的DSP系統(tǒng)工具的概況;接著主要介紹了計(jì)算機(jī)算法的概念、理論、有限字長(zhǎng)效用、FIR和IIR濾波器的實(shí)現(xiàn)、多速率和自適應(yīng)信號(hào)處理的FPGA實(shí)現(xiàn);最后,介紹了System Genrerator

2009-07-21 09:20:11

以及最新的DSP系統(tǒng)工具的概況;接著主要介紹了計(jì)算機(jī)算法的概念、理論、有限字長(zhǎng)效用、FIR和IIR濾波器的實(shí)現(xiàn)、多速率和自適應(yīng)信號(hào)處理的FPGA實(shí)現(xiàn);最后,介紹了System Genrerator

2009-07-24 13:07:08

的不足,同時(shí)也方便在現(xiàn)場(chǎng)可編程門陣列(FPGA)中增加一些其他相關(guān)的應(yīng)用功能,因此在FPGA中實(shí)現(xiàn)CVSD語音編譯碼調(diào)制功能的前景將是非常廣闊的。這里將詳細(xì)介紹什么是CVSD?其算法分析如何在FPGA中實(shí)現(xiàn)?

2019-08-07 07:04:27

由于一個(gè)項(xiàng)目中牽涉到了文件系統(tǒng)的實(shí)現(xiàn),C語言里用鏈表可以對(duì)文件系統(tǒng)進(jìn)行實(shí)現(xiàn),但FPGA里沒有指針和地址的概念,想請(qǐng)教一下,如何對(duì)文件進(jìn)行創(chuàng)建、編輯以及刪除操作

2018-04-20 14:19:49

結(jié)果表明,系統(tǒng)結(jié)構(gòu)靈活,性價(jià)比高,數(shù)據(jù)采集能力強(qiáng),各項(xiàng)指標(biāo)均達(dá)到了設(shè)計(jì)要求,具有廣泛的實(shí)用性。2 數(shù)據(jù)采集系統(tǒng)的實(shí)現(xiàn)2.1 系統(tǒng)硬件設(shè)計(jì)2.1.1 主控模塊FPGA在本設(shè)計(jì)中,FPGA主控模塊

2018-08-09 14:28:00

和ASIC中實(shí)現(xiàn)的硬核IP等。圖1即使如此,通用嵌入式系統(tǒng)也很難滿足現(xiàn)代設(shè)計(jì)需求。多芯片解決方案實(shí)現(xiàn)起來相對(duì)容易一些,但是成本高,缺乏設(shè)計(jì)人員所要求的靈活性以及性能/功耗指標(biāo)。采用了軟核處理器的單芯片

2021-07-12 08:00:00

,希望有興趣的同志和我聯(lián)系!FPGA以太網(wǎng)傳輸系統(tǒng)介紹:1)平臺(tái):ALTERA FPGA,cyclone系列器件即可支持;2)系統(tǒng)架構(gòu):硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實(shí)現(xiàn)

2014-06-19 12:04:25

,希望有興趣的同志和我聯(lián)系!FPGA以太網(wǎng)傳輸系統(tǒng)介紹:1)平臺(tái):ALTERA FPGA,cyclone系列器件即可支持;2)系統(tǒng)架構(gòu):硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實(shí)現(xiàn)

2014-06-19 12:06:43

關(guān)于基于ARM的嵌入式系統(tǒng)中從串配置FPGA的實(shí)現(xiàn),不看肯定后悔

2021-04-15 06:29:44

為了實(shí)現(xiàn)—是彈武器瞄準(zhǔn)自動(dòng)化,本文設(shè)計(jì)了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設(shè)計(jì)了CCD驅(qū)動(dòng)時(shí)序電路,采用

2014-11-07 14:54:07

嗨,我是Xilinx FPGA的新手。我該如何在FPGA中實(shí)現(xiàn)實(shí)時(shí)時(shí)鐘或時(shí)間和日期計(jì)數(shù)器?Xilinx是否為Artix 7提供任何RTC核心或IP?非常感謝您的建議。

2020-05-22 12:41:35

大家好!我想知道如何在FPGA中使用VHDL實(shí)現(xiàn)過零檢測(cè)器。所以我想實(shí)現(xiàn)一個(gè)數(shù)字常數(shù)小數(shù)鑒別器。 firt部分提供了雙極性信號(hào),但我想知道如何在vhdl中實(shí)現(xiàn)過零檢測(cè)器。感謝您的幫助!以上來自于谷歌

2019-01-29 08:16:40

等等)中有傳播延遲。因此,這些信號(hào)從另一個(gè)信號(hào)延遲20ns。信號(hào)頻率范圍是由輸入可編程參考時(shí)鐘控制的幾KHz到20MHz。我的問題是:如何在FPGA中實(shí)現(xiàn)選定信號(hào)(IOB輸出)的準(zhǔn)確延遲,以保持接收器

2019-05-28 12:16:59

在串行數(shù)據(jù)傳輸?shù)倪^程中,如何在FPGA中利用低頻源同步時(shí)鐘實(shí)現(xiàn)LVDS接收字對(duì)齊呢?

2021-04-08 06:39:42

高性能浮點(diǎn)處理一直與高性能CPU相關(guān)聯(lián)。在過去幾年中,GPU也成為功能強(qiáng)大的浮點(diǎn)處理平臺(tái),超越了圖形,稱為GP-GPU(通用圖形處理單元)。新創(chuàng)新是在苛刻的應(yīng)用中實(shí)現(xiàn)基于FPGA的浮點(diǎn)處理。

2019-10-21 08:15:23

美好的一天!我想知道如何在FPGA上有持久的價(jià)值,我的意思是當(dāng)我修改它的值時(shí),當(dāng)塊再次運(yùn)行時(shí),值不會(huì)被改變?在Matlab中通過定義一個(gè)像:persistent u的值,它會(huì)完成,但VHDL怎么樣

2019-02-20 11:17:46

你好xilinx用戶,我正在使用FPGA實(shí)現(xiàn)人工神經(jīng)網(wǎng)絡(luò)。我想知道如何在FPGA中使用0.784,1.768..etc等數(shù)字。表示這些數(shù)字的方法是什么。以上來自于谷歌翻譯以下為原文hello

2019-03-04 13:38:31

網(wǎng)絡(luò)連接到USB主機(jī)。本文將探討其設(shè)計(jì)方法,可以在FPGA或ASIC系統(tǒng)中實(shí)現(xiàn)高效高速USB 2.0接口。圖1 基于USB的分布式***采集系統(tǒng) 在介紹整合通用串行總線接口到FPGA或ASIC系統(tǒng)的各種

2012-11-22 16:11:20

你好!正如我在標(biāo)題中提出的那樣,希望大家可以討論如何在FPGA設(shè)計(jì)中測(cè)試數(shù)字IF信號(hào)功率。以上來自于谷歌翻譯以下為原文Hello! as what I put forward

2019-01-09 10:00:59

親愛的先生,我使用spartan 6處理器在VHDL中使用DCM_SP庫實(shí)現(xiàn)了時(shí)鐘倍頻器,并且我將100mhz時(shí)鐘乘以1GHZ工作正常。但我的問題是如何在系統(tǒng)生成器中實(shí)現(xiàn)這種時(shí)鐘多路復(fù)用器的方法,是否可能,如何?請(qǐng)求幫助我。鯊魚

2019-11-05 09:43:08

如何在CubeIDE中的STM32上通過USB實(shí)現(xiàn)“printf”發(fā)送消息? 我有 NUCLEO-F207ZG。

2022-12-26 07:51:36

如何在IAR中實(shí)現(xiàn)printf函數(shù)功能?

2021-12-01 06:29:17

如何在LAB中實(shí)現(xiàn)滑動(dòng)變阻器啊?

2012-12-01 20:05:05

我正在使用 NXP S32k148 工具箱,我想在我想使用數(shù)模轉(zhuǎn)換器(即 DAC)的地方構(gòu)建模型。那么我可以在這里使用哪個(gè)工具箱?或者如何在 MBD 中實(shí)現(xiàn) DAC(數(shù)模轉(zhuǎn)換器)。

2023-04-07 12:50:57

的處理器來實(shí)現(xiàn)可接受的進(jìn)程切換時(shí)間,而且在任務(wù)級(jí)別并不合適。使用內(nèi)存保護(hù)單元 (MPU) 實(shí)現(xiàn) MCU 的完全分區(qū)隔離是可能的,但難度很大。這是討論如何在 MCU 系統(tǒng)中實(shí)現(xiàn)完全分區(qū)隔離的系列論文

2021-11-01 08:17:09

大家好,我已經(jīng)能夠使用EDK與我的“hello world”程序一起使用Microblaze。我現(xiàn)在想修改代碼,以便FPGA說出除了hello world之外的其他內(nèi)容。如何在SDK 12.1中重新

2019-01-22 07:04:30

嗨,如何在Virtex-7 FPGA中實(shí)現(xiàn)動(dòng)態(tài)部分配置?問候,Suresh Palani

2020-05-29 11:30:45

我正試圖在a7 fpga中實(shí)現(xiàn)回退多重啟動(dòng)。以下是黃金圖像的ise工具中的設(shè)置:當(dāng)我完成將黃金圖像位文件加載到fpga中時(shí),完成的led可以點(diǎn)亮。但當(dāng)我完成將黃金映像mcs文件加載到fpga中,并在

2020-06-01 06:17:37

如何在labview中實(shí)現(xiàn)圖形與坐標(biāo)想對(duì)應(yīng)啊?

2013-03-20 11:51:54

設(shè)備連接到路由器。

有人能告訴我如何在 python 中實(shí)現(xiàn) ESP TOUCH 協(xié)議嗎?這樣所有模塊連同樹莓派都可以從一個(gè)應(yīng)用程序同時(shí)配置。

2023-05-17 08:20:05

我們?nèi)?b class="flag-6" style="color: red">何在xilinx FPGA中執(zhí)行運(yùn)行時(shí)重新配置?

2020-07-16 10:24:37

在FPGA中,動(dòng)態(tài)相位調(diào)整(DPA)主要是實(shí)現(xiàn)LVDS接口接收時(shí)對(duì)時(shí)鐘和數(shù)據(jù)通道的相位補(bǔ)償,以達(dá)到正確接收的目的。那么該如何在低端FPGA中實(shí)現(xiàn)DPA的功能呢?

2021-04-08 06:47:08

便攜式設(shè)備的存儲(chǔ)器要求是什么?如何在便攜式應(yīng)用中充分發(fā)揮FPGA的優(yōu)勢(shì)?

2021-05-06 08:10:01

I2C總線接口的工作模式和特點(diǎn)如何在嵌入式操作系統(tǒng)ARM Linux中實(shí)現(xiàn)ZLG7290的驅(qū)動(dòng)?I2C總線在傳送數(shù)據(jù)過程中有哪幾種信號(hào)?

2021-04-23 06:00:44

如何在嵌入式視頻處理系統(tǒng)領(lǐng)域進(jìn)行FPGA驗(yàn)證?需要滿足什么條件?

2019-08-01 06:42:45

如何在沒有AXI接口的kintex 7 FPGA中實(shí)現(xiàn)以太網(wǎng)?請(qǐng)幫幫我

2020-08-18 09:59:04

如何在視頻監(jiān)控系統(tǒng)中使用FPGA進(jìn)行視頻處理?

2021-06-07 06:12:39

本文介紹了如何在FPGA中利用Block RAM的特殊結(jié)構(gòu)實(shí)現(xiàn)HDTV視頻增強(qiáng)算法中灰度直方圖統(tǒng)計(jì)。

2021-04-30 07:34:58

高速連續(xù)數(shù)據(jù)采集系統(tǒng)的背景及功能是什么?如何利用FPGA實(shí)現(xiàn)高速連續(xù)數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)?FPGA在高速連續(xù)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有哪些?

2021-04-08 06:19:37

在現(xiàn)代電子系統(tǒng)的設(shè)計(jì)中,高速 FPGA運(yùn)行時(shí)需將其配置數(shù)據(jù)加載到內(nèi)部SRAM 中,改變SDRAM 里面的數(shù)據(jù),從而使FPGA實(shí)現(xiàn)不同的功能,即所謂的可重構(gòu)技術(shù)[1]。但是由于其采用的是基于SRAM

2019-08-05 06:43:09

FPGA是今天許多要求最嚴(yán)苛的嵌入式系統(tǒng)設(shè)計(jì)的重要元件。由于FPGA器件的價(jià)格大幅下跌,加上為設(shè)計(jì)人員帶來的便利性和靈活性,FPGA在競(jìng)爭(zhēng)激烈的全球市場(chǎng)上嵌入式設(shè)計(jì)產(chǎn)品的應(yīng)用中日益增加并不

2022-02-09 06:42:35

應(yīng)用于LTE-OFDM系統(tǒng)的Viterbi譯碼在FPGA中的實(shí)現(xiàn)在OFDM系統(tǒng)中,為了獲得正確無誤的數(shù)據(jù)傳輸,要采用差錯(cuò)控制編碼技術(shù)。LTE中采用Viterbi和Turbo加速器來實(shí)現(xiàn)前向糾錯(cuò)。提出

2009-09-19 09:41:24

本文給出了基于FPGA高速數(shù)據(jù)采集系統(tǒng)中的輸入輸出接口的實(shí)現(xiàn),介紹了高速傳輸系統(tǒng)中RocketIO設(shè)計(jì)以及LVDS接口、LVPECL接口電路結(jié)構(gòu)及連接方式,并在我們?cè)O(shè)計(jì)的高速數(shù)傳系統(tǒng)中得到應(yīng)用。

2021-04-29 06:04:42

怎么實(shí)現(xiàn)信號(hào)發(fā)生器系統(tǒng)的FPGA設(shè)計(jì)?

2021-09-30 06:35:31

本文選用FPGA實(shí)現(xiàn)數(shù)據(jù)處理、邏輯控制,充分利用PC機(jī),結(jié)合Labwindows圖形化上層應(yīng)用軟件界面生成的虛擬測(cè)試系統(tǒng)具有較強(qiáng)的競(jìng)爭(zhēng)力。本系統(tǒng)在FPGA單板單片主控器件控制下,實(shí)現(xiàn)兩路獨(dú)立、幅值可控的信號(hào)發(fā)生器,一路虛擬存儲(chǔ)示波器,具有外部觸發(fā)信號(hào)和采樣時(shí)鐘的16路高速邏輯分析儀。

2021-05-12 06:58:02

System Generator for DSP的特點(diǎn)是什么?如何使用System Generator for DSP實(shí)現(xiàn)系統(tǒng)級(jí)建模?怎么在Matlab中實(shí)現(xiàn)數(shù)字通信FPGA硬件設(shè)計(jì)?

2021-04-29 06:20:46

10Gbps的serdes,它應(yīng)該使用那個(gè)速度的PLL。正常,PLL速度固定為P(預(yù)分頻器,主分頻器和S),我想掃描窄,所以我應(yīng)該使用小數(shù)N分頻PLL。無論如何,我找不到documnet PLL如何在FPGA中工作。有誰知道嗎?

2020-06-16 15:27:36

本帖最后由 eehome 于 2013-1-5 10:05 編輯

測(cè)控系統(tǒng)中B碼同步技術(shù)的FPGA實(shí)現(xiàn)

2012-08-06 12:37:13

測(cè)控系統(tǒng)中B碼同步技術(shù)的FPGA實(shí)現(xiàn)

2012-08-06 11:48:16

為了滿足某測(cè)控平臺(tái)的設(shè)計(jì)要求,設(shè)計(jì)并實(shí)現(xiàn)了基于FPGA的六通道HDLC并行通信系統(tǒng)。該系統(tǒng)以FPGA為核心,包括FPGA、DSP、485轉(zhuǎn)換接口等部分。給出了系統(tǒng)的電路設(shè)計(jì)、關(guān)鍵模塊及軟件

2010-09-30 16:49:30 43

43 本文將著重介紹運(yùn)用FPGA技術(shù)實(shí)現(xiàn)基群與二次群之間復(fù)接與分接系統(tǒng)的總體設(shè)計(jì)方案。

2011-08-15 17:00:27 1300

1300 本文基于802.16a協(xié)議的原理架構(gòu),本著小成本、高效率的設(shè)計(jì)思想,建立了一個(gè)基于FPGA的可實(shí)現(xiàn)流水化運(yùn)行的OFDM系統(tǒng)的硬件平臺(tái),包括模擬前端及OFDM調(diào)制器及OFDM 解調(diào)器,用來實(shí)現(xiàn)OFDM的

2012-05-25 09:38:14 5915

5915

FPGA實(shí)現(xiàn)嵌入式系統(tǒng),有需要的下來看看

2016-05-10 11:24:33 21

21 基于FPGA的高速多通道AD采樣系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)_徐加彥

2017-01-18 20:23:58 12

12 三態(tài)門在數(shù)字電路上可以說是應(yīng)用的非常廣泛,特別是一些總線上的應(yīng)用,因而,隨著數(shù)字電路的發(fā)展,就避免不了用硬件描述語言在FPGA上來設(shè)計(jì)實(shí)現(xiàn)三態(tài)門。

2017-02-08 11:37:06 7305

7305 基于FPGA的安全USB系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)_李廣位

2017-03-19 11:38:26 2

2 基于FPGA和DSP網(wǎng)絡(luò)單向時(shí)延測(cè)量系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)_唐旭

2017-03-19 11:38:26 0

0 了解如何在System Generator中使用多個(gè)時(shí)鐘域,從而可以實(shí)現(xiàn)復(fù)雜的DSP系統(tǒng)。

2018-11-27 06:42:00 3450

3450 Xilinx FPGA是支持OpenStack的第一個(gè)(也是目前唯一的)FPGA。

該視頻快速介紹了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展臺(tái)上運(yùn)行每個(gè)演示,并使用OpenStack進(jìn)行配置和管理。

2018-11-23 06:14:00 3322

3322 建立了一個(gè)基于FPGA的可實(shí)現(xiàn)流水化運(yùn)行的OFDM系統(tǒng)的硬件平臺(tái),包括模擬前端、基于FPGA的OFDM調(diào)制器和OFDM 解調(diào)器。重點(diǎn)給出了OFDM調(diào)制解調(diào)器的實(shí)現(xiàn)構(gòu)架,對(duì)FPGA實(shí)現(xiàn)方法進(jìn)行了詳細(xì)的描述,介紹了系統(tǒng)調(diào)試方法,并對(duì)系統(tǒng)進(jìn)行了性能評(píng)價(jià)。

2018-12-13 16:45:51 22

22 本文提出了一種基于FPGA的CPCI系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn),使用廉價(jià)FPGA芯片實(shí)現(xiàn)CPCI通信協(xié)議,同時(shí)利用FPGA的可編程特性實(shí)現(xiàn)電源控制、靈活中斷、外部觸發(fā)、外部通信等特殊應(yīng)用的功能,解決了CPCI協(xié)議經(jīng)過CPCI橋時(shí)的沖突問題。

2019-01-06 11:37:13 2443

2443

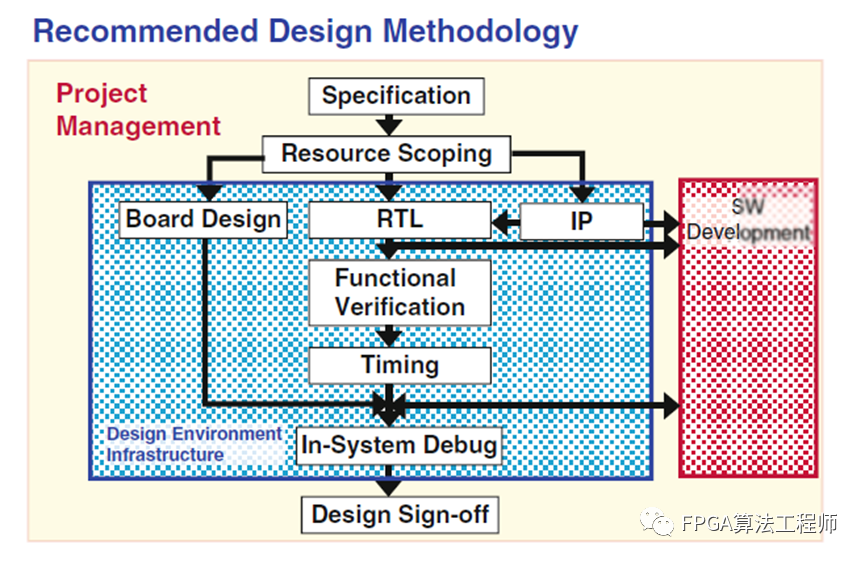

本文檔的主要內(nèi)容詳細(xì)介紹的是怎么樣才能使用FPGA實(shí)現(xiàn)數(shù)字系統(tǒng)內(nèi)容包括了:FPGA簡(jiǎn)介,為什么采用FPGA,開發(fā)平臺(tái)和設(shè)計(jì)工具,HDL(硬件描述語言),FPGA的設(shè)計(jì)原則,系統(tǒng)設(shè)計(jì)開發(fā)流程。

2020-08-11 15:29:00 9

9 偏移和包重組是在FPGA中實(shí)現(xiàn)SPI一4.2接口的核心難點(diǎn),在分析偏移和包重組原理的基礎(chǔ)E,給出基于FPGA的SPI一4.2接口的設(shè)計(jì)與實(shí)現(xiàn)方案,并對(duì)關(guān)鍵部分給出r硬件原理圖,在線測(cè)試結(jié)果證明該方案可以實(shí)現(xiàn)SPI一4.2接口的功能。

2021-01-25 14:51:21 13

13 電子發(fā)燒友網(wǎng)為你提供如何在MCU或FPGA設(shè)備中實(shí)現(xiàn)分層安全?資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-15 08:54:48 3

3 基于FPGA的光纖通信系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)的講解。

2021-05-25 16:26:19 26

26 基于FPGA的VPX時(shí)間統(tǒng)一系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

2021-06-01 09:26:40 4

4 基于FPGA的無線通信系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

2021-06-16 09:59:29 44

44 FPGA實(shí)現(xiàn)嵌入式系統(tǒng)(嵌入式開發(fā)報(bào)班哪個(gè)好)-該文檔為FPGA實(shí)現(xiàn)嵌入式系統(tǒng)原理資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-30 09:13:42 12

12 使用插值算法實(shí)現(xiàn)圖像縮放是數(shù)字圖像處理算法中經(jīng)常遇到的問題。我們經(jīng)常會(huì)將某種尺寸的圖像轉(zhuǎn)換為其他尺寸的圖像,如放大或者縮小圖像。由于在縮放的過程中會(huì)遇到浮點(diǎn)數(shù),如何在FPGA中正確的處理浮點(diǎn)數(shù)運(yùn)算是在FPGA中實(shí)現(xiàn)圖像縮放的關(guān)鍵。

2022-03-18 11:03:41 4056

4056 這是FPGA之旅的第十一例了。在前面的例子中,已經(jīng)對(duì)OLED有了一個(gè)基礎(chǔ)的了解,本例將介紹如何在OLED上實(shí)現(xiàn)字符的顯示,為后面的例程做準(zhǔn)備。

2022-09-06 09:02:18 3838

3838 OFDM中調(diào)制使用IFFT,解調(diào)使用IFFT,在OFDM實(shí)現(xiàn)系統(tǒng)中,F(xiàn)FT和IFFT時(shí)必備的關(guān)鍵模塊。在使用Xilinx的7系列FPGA(KC705)實(shí)現(xiàn)OFDM系統(tǒng)時(shí),有以下幾種選擇。

2023-07-10 10:50:52 605

605

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論