編者按——盡管協(xié)處理器架構(gòu)因其數(shù)字處理性能和吞吐量而聞名,但也為嵌入式系統(tǒng)設(shè)計(jì)者提供了實(shí)現(xiàn)項(xiàng)目管理策略的機(jī)會(huì),從而降低了開發(fā)成本并加快了上市速度。本文重點(diǎn)介紹分立式微控制器 (MCU) 和分立式現(xiàn)場(chǎng)可編程門陣列 (FPGA) 的組合,展示了這種架構(gòu)如何適合高效和迭代的設(shè)計(jì)過程。利用研究資料、實(shí)證結(jié)果和案例研究,探討這種架構(gòu)的好處,并提供示范性的應(yīng)用。讀完本文,嵌入式系統(tǒng)設(shè)計(jì)者將對(duì)何時(shí)以及如何實(shí)現(xiàn)這種多功能硬件架構(gòu)有個(gè)更好的理解。

引言

嵌入式系統(tǒng)設(shè)計(jì)者經(jīng)常會(huì)發(fā)現(xiàn)自己被卡在設(shè)計(jì)限制、性能期望以及進(jìn)度和預(yù)算問題上。事實(shí)上,甚至現(xiàn)代項(xiàng)目管理中有一些像”快速失敗”、“敏捷”、“面向未來(lái)”和“顛覆性!”這樣的流行語(yǔ)或短語(yǔ),進(jìn)一步突出了這一角色的不穩(wěn)定性。即使試圖滿足這些期望,所涉及的手法也可能是令人痛苦的,同時(shí)這些期望一直在整個(gè)市場(chǎng)上傳播著并持續(xù)被強(qiáng)化。我們需要的是一種設(shè)計(jì)方法,能夠?qū)崿F(xiàn)一個(gè)不斷演進(jìn)的迭代過程,就像大多數(shù)嵌入式系統(tǒng)一樣,從硬件架構(gòu)開始。

協(xié)處理器架構(gòu)是一種以結(jié)合了微控制器單元 (MCU) 和現(xiàn)場(chǎng)可編程門陣列 (FPGA) 技術(shù)優(yōu)勢(shì)而著稱的硬件架構(gòu),它可以為嵌入式設(shè)計(jì)者提供一個(gè)能夠滿足最苛刻要求的過程,而且它還可以為解決已知和未知挑戰(zhàn)提供必要的靈活性。通過提供能夠迭代調(diào)整的硬件,設(shè)計(jì)者可以展示進(jìn)展,達(dá)到關(guān)鍵里程碑,并充分利用快速原型設(shè)計(jì)過程。

在這個(gè)過程中,有一些關(guān)鍵的項(xiàng)目里程碑,每一個(gè)里程碑都有其獨(dú)特的價(jià)值,可以為開發(fā)工作帶來(lái)好處。在本文中,我們將提到以下術(shù)語(yǔ):用微控制器進(jìn)行數(shù)字信號(hào)處理里程碑、用微控制器進(jìn)行系統(tǒng)管理里程碑以及產(chǎn)品部署里程碑。

本文結(jié)束時(shí),我們將證明靈活的硬件架構(gòu)可以比一個(gè)較僵硬的方法更適合現(xiàn)代嵌入式系統(tǒng)設(shè)計(jì)。此外,這種方法可以使項(xiàng)目成本和產(chǎn)品上市速度都得到改善。這一立場(chǎng)將通過論據(jù)、所提供實(shí)例和案例研究獲得佐證。通過觀察該架構(gòu)所提供設(shè)計(jì)靈活性中每個(gè)里程碑的價(jià)值,我們可以清楚地看到,自適應(yīng)硬件架構(gòu)是推動(dòng)嵌入式系統(tǒng)設(shè)計(jì)發(fā)展的強(qiáng)大動(dòng)力。

探索協(xié)處理器架構(gòu)的優(yōu)勢(shì):設(shè)計(jì)靈活性和高性能處理

FPGA 設(shè)計(jì)的一個(gè)常見應(yīng)用是直接與高速模數(shù)轉(zhuǎn)換器 (ADC) 連接。信號(hào)數(shù)字化后,讀入 FPGA,然后將一些數(shù)字信號(hào)處理器 (DSP) 算法應(yīng)用于該信號(hào)。最后,F(xiàn)PGA 再根據(jù)這些結(jié)果做出決策。

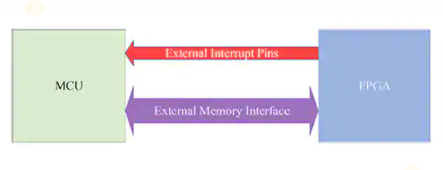

本文通篇將以這樣一個(gè)應(yīng)用將作為實(shí)例。此外,圖 1 展示了一個(gè)通用的協(xié)處理器架構(gòu),其中 MCU 和 FPGA 通過 MCU 的外部存儲(chǔ)器接口進(jìn)行連接。FPGA 被當(dāng)作是一塊外部靜態(tài)隨機(jī)存取存儲(chǔ)器 (SRAM)。信號(hào)從 FPGA 返回 MCU,充當(dāng)硬件中斷線路和狀態(tài)指示。這允許 FPGA 向 MCU 指示關(guān)鍵的狀態(tài),例如通知 ADC 轉(zhuǎn)換準(zhǔn)備好了,或發(fā)生了故障,或發(fā)生了其他值得注意的事件。

?

圖 1:通用協(xié)處理器示意圖 (MCU + FPGA)。(圖片來(lái)源:CEPD)

從上述每個(gè)里程碑的交付成果來(lái)看,可能最能看出協(xié)處理器方法的優(yōu)勢(shì)。價(jià)值不僅要評(píng)估一項(xiàng)任務(wù)或階段的成就,而且還評(píng)估這些成就所帶來(lái)的用處。通過回答以下問題有助于評(píng)估一個(gè)里程碑的交付成果的整體價(jià)值。

隨著項(xiàng)目依賴性和瓶頸的消除,其他團(tuán)隊(duì)成員的進(jìn)展現(xiàn)在能否更迅速地繼續(xù)進(jìn)行下去?

里程碑成就如何讓進(jìn)一步的并行操作成為可能?

用微控制器進(jìn)行數(shù)字信號(hào)處理的里程碑

?

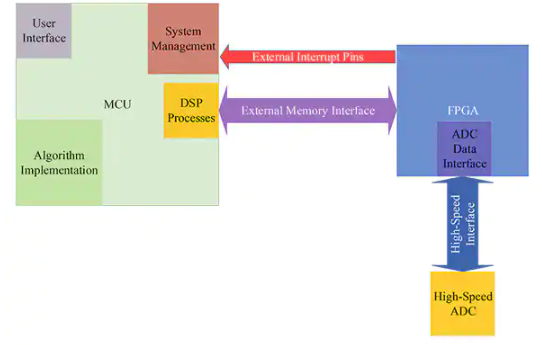

圖 2:架構(gòu)——用微控制器進(jìn)行數(shù)字信號(hào)處理。(圖片來(lái)源:CEPD)

這種硬件架構(gòu)所允許的第一個(gè)開發(fā)階段將 MCU 放在前期和中期。在同等條件下,MCU 和可執(zhí)行軟件的開發(fā)比 FPGA 和硬件描述語(yǔ)言 (HDL) 的開發(fā)更節(jié)省資源和時(shí)間。因此,通過啟動(dòng)以 MCU 為主要處理器的產(chǎn)品開發(fā),算法可以更迅速地實(shí)現(xiàn)、測(cè)試和驗(yàn)證。這使得算法和邏輯錯(cuò)誤可以在設(shè)計(jì)過程的早期被發(fā)現(xiàn),也使得信號(hào)鏈的實(shí)質(zhì)部分可以被測(cè)試和驗(yàn)證。

在這個(gè)最初的里程碑中,F(xiàn)PGA 的作用是作為一個(gè)高速數(shù)據(jù)的收集接口。它的任務(wù)是可靠地管理來(lái)自高速 ADC 的數(shù)據(jù),提醒 MCU 有數(shù)據(jù)可用,并在 MCU 的外部存儲(chǔ)器接口上提供這些數(shù)據(jù)。雖然這個(gè)角色不包括實(shí)現(xiàn)基于 HDL 的 DSP 過程或其他算法,但它仍然是非常關(guān)鍵的。

在這個(gè)階段進(jìn)行的 FPGA 開發(fā)為產(chǎn)品的最終成功奠定了基礎(chǔ),無(wú)論是在產(chǎn)品開發(fā)過程中還是在向市場(chǎng)發(fā)布時(shí)。通過只關(guān)注低級(jí)別的接口,就可以有足夠的時(shí)間來(lái)測(cè)試這些基本操作。只有當(dāng) FPGA 可靠、有把握地履行這一接口作用時(shí),才能有把握地完成這一里程碑。

這個(gè)最初的里程碑的主要交付成果包括以下好處:

整個(gè)信號(hào)路徑——所有的放大、衰減和轉(zhuǎn)換——都將被測(cè)試和驗(yàn)證。

通過最初在軟件 (C/C++) 中實(shí)現(xiàn)算法,項(xiàng)目開發(fā)的時(shí)間和精力將有所減少;這對(duì)管理層和其他利益相關(guān)者來(lái)說(shuō)具有相當(dāng)大的價(jià)值,他們必須在批準(zhǔn)未來(lái)設(shè)計(jì)階段之前看到這個(gè)項(xiàng)目的可行性。

在 C/C++ 中實(shí)現(xiàn)算法的經(jīng)驗(yàn)將直接轉(zhuǎn)移到 HDL 實(shí)現(xiàn)中——通過使用“軟件到 HDL”工具,例如 Xilinx HLS。

系統(tǒng)管理與微控制器的里程碑

?

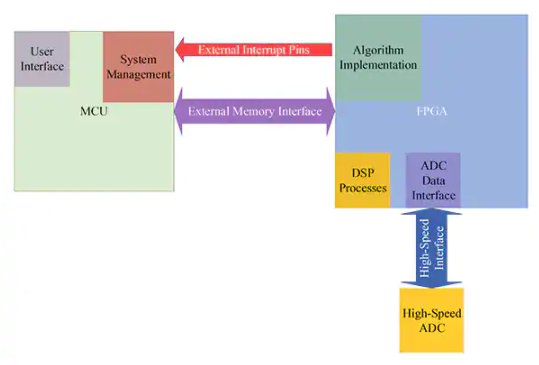

圖 3:架構(gòu)——用微控制器進(jìn)行系統(tǒng)管理。(圖片來(lái)源:CEPD)

由這種協(xié)處理器方法提供的第二個(gè)開發(fā)展階段是由 DSP 過程和算法實(shí)現(xiàn)從 MCU 轉(zhuǎn)移到 FPGA 來(lái)界定的。FPGA 仍然負(fù)責(zé)高速 ADC 接口,但通過承擔(dān)這些其他角色,F(xiàn)PGA 提供的速度和并行性得到了充分的利用。此外,與 MCU 不同,可以實(shí)現(xiàn)多個(gè) DSP 進(jìn)程和算法通道實(shí)例,并同步運(yùn)行。

基于從 MCU 的實(shí)現(xiàn)中獲得的經(jīng)驗(yàn),設(shè)計(jì)者會(huì)將這種信心帶入下一個(gè)里程碑。諸如前面提到的 Xilinx Vivado HLS 這樣的工具提供了從可執(zhí)行 C/C++ 代碼到可綜合的 HDL 的功能轉(zhuǎn)換。現(xiàn)在,仍然必須定義和實(shí)現(xiàn)時(shí)序約束、工藝參數(shù)和其他用戶偏好,但核心功能被堅(jiān)持下來(lái)并轉(zhuǎn)化為 FPGA 架構(gòu)。

對(duì)于這個(gè)里程碑,MCU 的角色就是一個(gè)系統(tǒng)管理者。FPGA 內(nèi)的狀態(tài)和控制寄存器由 MCU 監(jiān)控、更新和報(bào)告。此外,MCU 還管理著用戶界面 (UI)。這個(gè)用戶界面可以采取通過以太網(wǎng)或 Wi-Fi 連接訪問網(wǎng)絡(luò)服務(wù)器的形式,也可以是一個(gè)工業(yè)觸摸屏界面,讓用戶在使用點(diǎn)進(jìn)行訪問。從 MCU 的新的、更精細(xì)的角色中得到的關(guān)鍵啟示是:通過將其從計(jì)算密集型的處理任務(wù)中解脫出來(lái),現(xiàn)在可將 MCU 和 FPGA 運(yùn)用到其最適合的任務(wù)中來(lái)。

關(guān)鍵的可交付成果構(gòu)成了這個(gè)里程碑,并包括以下好處:

FPGA 所提供 DSP 進(jìn)程和算法實(shí)現(xiàn)的快速、并行執(zhí)行。MCU 提供了一個(gè)反應(yīng)靈敏的精簡(jiǎn) UI,并管理著產(chǎn)品的執(zhí)行過程。

由于首先在 MCU 內(nèi)進(jìn)行了開發(fā)和驗(yàn)證,算法風(fēng)險(xiǎn)得到了緩解,這些緩解措施被轉(zhuǎn)換為可綜合的 HDL。像 Vivado HLS 這樣的工具使得這種轉(zhuǎn)換變得更加容易。此外,通過集成的仿真工具,如 Vivado 設(shè)計(jì)套件,可以減輕 FPGA 特有的風(fēng)險(xiǎn)。

利益相關(guān)者不會(huì)因?yàn)閷⑦^程轉(zhuǎn)移到 FPGA 上而面臨重大風(fēng)險(xiǎn)。相反,他們可以看到并享受到 FPGA 的速度和并行性帶來(lái)的好處。觀察到明顯的性能改進(jìn)后,現(xiàn)在可以把工作重點(diǎn)放在為該設(shè)計(jì)的制造做好準(zhǔn)備。

產(chǎn)品部署里程碑

隨著計(jì)算密集型處理在 FPGA 內(nèi)得到解決,MCU 就能很地處理其系統(tǒng)管理和用戶界面角色,產(chǎn)品部署亦因此而準(zhǔn)備就緒。現(xiàn)在,本文不主張繞過 Alpha 和 Beta 版本;但是,本里程碑的重點(diǎn)是協(xié)處理器架構(gòu)為產(chǎn)品部署提供的能力。

MCU 和 FPGA 都是現(xiàn)場(chǎng)可更新器件。目前已經(jīng)取得了多項(xiàng)進(jìn)展,使得 FPGA 的更新與軟件更新一樣容易。此外,由于 FPGA 在 MCU 的可尋址存儲(chǔ)器空間內(nèi),MCU 可以作為整個(gè)系統(tǒng)的存取點(diǎn):同時(shí)為自已和 FPGA 接收更新。更新可以在每個(gè)最終用戶的基礎(chǔ)上有條件地安排、分發(fā)和定制。最后,可以進(jìn)行用戶和用例日志維護(hù)并使之與特定構(gòu)建實(shí)現(xiàn)關(guān)聯(lián)。有了這些數(shù)據(jù)集,即使在產(chǎn)品進(jìn)入現(xiàn)場(chǎng)后,性能也能繼續(xù)得到完善和提高。

也許這種整體系統(tǒng)更新能力的優(yōu)勢(shì)在天基應(yīng)用中得到了最充分的體現(xiàn)。一旦產(chǎn)品推出,維護(hù)和更新必須在遠(yuǎn)程進(jìn)行。這可以是一個(gè)簡(jiǎn)單的邏輯條件改變,或復(fù)雜到更新一個(gè)通信調(diào)制方案。FPGA 技術(shù)提供的可編程性和協(xié)處理器架構(gòu)可以滿足這一系列能力的全部要求,同時(shí)提供防輻射的元件選擇。

這個(gè)里程碑的最后一個(gè)關(guān)鍵收獲是逐步減少成本。成本降低、材料清單 (BOM) 的變化和其他優(yōu)化也可能出現(xiàn)在這個(gè)里程碑。在現(xiàn)場(chǎng)部署時(shí),可能會(huì)發(fā)現(xiàn)使用價(jià)格較低的 MCU 或性能較差的 FPGA 也能很好地運(yùn)行產(chǎn)品。由于協(xié)處理器的存在,架構(gòu)設(shè)計(jì)者不會(huì)拘泥于使用那些能力超出其應(yīng)用需求的組件。此外,如果一個(gè)組件無(wú)法使用,該架構(gòu)允許新的組件被整合到設(shè)計(jì)中。單芯片、片上系統(tǒng) (SoC) 架構(gòu),或試圖處理所有產(chǎn)品處理的高性能 DSP 或 MC,都不是這種情況。協(xié)處理器架構(gòu)是能力和靈活性的良好組合,給設(shè)計(jì)者在開發(fā)階段和向市場(chǎng)發(fā)布時(shí)提供了更多選擇和自由。

支持調(diào)查和相關(guān)案例研究

衛(wèi)星通信實(shí)例

簡(jiǎn)而言之,協(xié)處理器的價(jià)值在于幫助主處理單元減負(fù),讓任務(wù)在硬件上執(zhí)行,其中可以利用加速和精簡(jiǎn)優(yōu)勢(shì)。這種設(shè)計(jì)選擇的好處是計(jì)算速度和能力的凈增加,而且正如本文所認(rèn)為的那樣,開發(fā)成本和開發(fā)時(shí)間也會(huì)減少。也許這些好處最引人注目的一面就在空間通信系統(tǒng)領(lǐng)域。

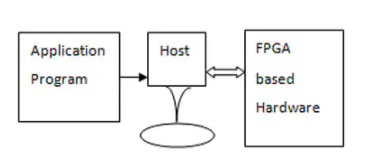

在《作為協(xié)處理器的 FPGA 式硬件》一書中,G. Prasad 和 N. Vasantha 詳細(xì)介紹了在 FPGA 中數(shù)據(jù)處理如何混合衛(wèi)星通信系統(tǒng)的計(jì)算需求,而沒有特定應(yīng)用集成電路 (ASIC) 的高非經(jīng)常性工程 (NRE) 成本或硬體系架構(gòu)處理器的特定應(yīng)用限制。正如在用微控制器進(jìn)行數(shù)字信號(hào)處理里程碑中所描述的那樣,其設(shè)計(jì)從應(yīng)用處理器開始,執(zhí)行大部分的計(jì)算密集型算法。從這一出發(fā)點(diǎn)著手,他們確定了消耗中央處理單元 (CPU) 時(shí)鐘大部分周期的軟件關(guān)鍵部分,并將這些部分遷移到 HDL 實(shí)現(xiàn)。以下圖形表示與到目前為止所介紹的高度相似,然而,他們選擇將應(yīng)用程序作為自己的獨(dú)立塊來(lái)表示,因?yàn)樗梢栽谥鳈C(jī)(處理器)或基于 FPGA 的硬件中實(shí)現(xiàn)。

?

圖 4:應(yīng)用程序、主機(jī)處理器和基于 FPGA 的硬件——用于衛(wèi)星通信實(shí)例。

通過利用外設(shè)組件互連 (PCI) 接口和主機(jī)處理器的直接存儲(chǔ)器訪問 (DMA) ,外設(shè)性能得到了極大的提高。這主要體現(xiàn)在對(duì)去隨機(jī)化過程的改進(jìn)上。當(dāng)這一過程在主機(jī)處理器的軟件中進(jìn)行時(shí),系統(tǒng)的實(shí)時(shí)響應(yīng)顯然出現(xiàn)了瓶頸。然而,當(dāng)轉(zhuǎn)移到 FPGA 時(shí),我們可以看到以下好處:

去隨機(jī)化過程實(shí)時(shí)執(zhí)行,不會(huì)造成瓶頸

主機(jī)處理器的計(jì)算開銷大大減少,現(xiàn)在它可以更好地發(fā)揮所需的記錄角色。

整個(gè)系統(tǒng)的總性能就提升了。

所有這些都是在沒有 ASIC 相關(guān)開銷的情況下實(shí)現(xiàn)的,同時(shí)還享有可編程邏輯的靈活性 [5]。衛(wèi)星通信帶來(lái)了相當(dāng)大的挑戰(zhàn),而這種方法可以可靠地滿足這些要求,并繼續(xù)提供設(shè)計(jì)靈活性。

汽車信息娛樂系統(tǒng)實(shí)例

車車娛樂系統(tǒng)是挑剔的消費(fèi)者看重的功能。與大多數(shù)汽車電子產(chǎn)品不同的是,這些設(shè)備是高度可見的,人們預(yù)期很高,希望能擁有出色的響應(yīng)時(shí)間和性能。然而,設(shè)計(jì)者往往在當(dāng)前的設(shè)計(jì)需求和未來(lái)功能所需的靈活性之間受到擠壓。在這個(gè)例子中,我們將使用信號(hào)處理和無(wú)線通信的實(shí)現(xiàn)需求來(lái)強(qiáng)調(diào)協(xié)處理器硬件架構(gòu)的優(yōu)勢(shì)。

所使用的主要汽車娛樂系統(tǒng)架構(gòu)之一是由 Delphi Delco 電子系統(tǒng)公司發(fā)布的。該架構(gòu)采用了一個(gè) SH-4 MCU 和一個(gè)配套的 ASIC,即日立的 HD64404 Amanda 外設(shè)。這個(gè)架構(gòu)滿足了汽車市場(chǎng) 75% 以上的基本娛樂功能;但它缺乏解決視頻處理應(yīng)用和無(wú)線通信的能力。通過在這個(gè)現(xiàn)有的架構(gòu)中加入 FPGA,就可以為這個(gè)已經(jīng)存在的設(shè)計(jì)增加進(jìn)一步的靈活性和能力。

?

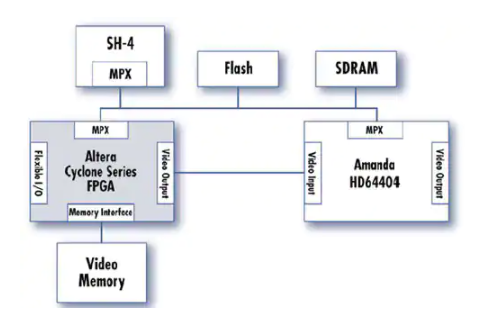

圖 5:信息娛樂系統(tǒng) FPGA 協(xié)處理器架構(gòu)實(shí)例 1。

圖 5 的架構(gòu)同時(shí)適用于視頻處理和無(wú)線通信管理。通過將 DSP 功能推給 FPGA,Amanda 處理器可以起到系統(tǒng)管理的作用,并被釋放出來(lái)以實(shí)現(xiàn)無(wú)線通信堆棧。由于 Amanda 和 FPGA 都可以訪問外部存儲(chǔ)器,數(shù)據(jù)可以在系統(tǒng)的處理器和組件之間快速交換。

?

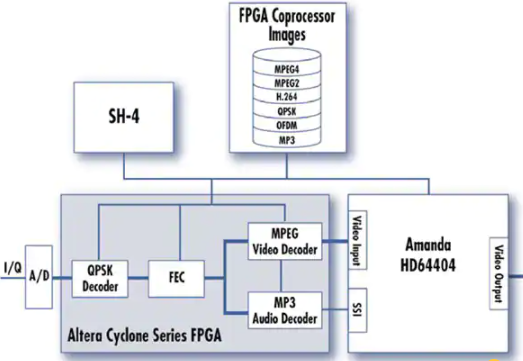

圖 6:信息娛樂系統(tǒng) FPGA 協(xié)處理器架構(gòu)實(shí)例 2。

圖 6 中的第二個(gè)信息娛樂系統(tǒng)突現(xiàn)了 FPGA 的能力,同時(shí)解決了高速模擬數(shù)據(jù)的傳入和視頻應(yīng)用所需的壓縮和編碼處理。事實(shí)上,所有這些功能都可以推給 FPGA,通過使用并行處理,這些都可以實(shí)時(shí)處理。

通過在現(xiàn)有的硬件架構(gòu)中加入 FPGA,現(xiàn)有硬件的成熟性能就可以獲得靈活性和未來(lái)適用性。即使在現(xiàn)有系統(tǒng)中,協(xié)處理器架構(gòu)也為設(shè)計(jì)者提供了選擇,否則將無(wú)法使用 [6]。

快速原型開發(fā)優(yōu)勢(shì)

快速原型開發(fā)過程的核心是就要覆蓋大量產(chǎn)品開發(fā)領(lǐng)域,因此要能并行執(zhí)行任務(wù)、快速識(shí)別“錯(cuò)誤”和設(shè)計(jì)問題以及驗(yàn)證數(shù)據(jù)和信號(hào)路徑,特別是項(xiàng)目關(guān)鍵路徑內(nèi)的數(shù)據(jù)和信號(hào)路徑。然而,要使這一過程真正產(chǎn)生精簡(jiǎn)、高效的結(jié)果,必須在所需的項(xiàng)目領(lǐng)域有足夠的專業(yè)知識(shí)。

傳統(tǒng)上,這意味著必須有一個(gè)硬件工程師,一個(gè)嵌入式軟件或 DSP 工程師,以及一個(gè) HDL 工程師。現(xiàn)在,有很多跨學(xué)科的專業(yè)人員,他們可能能夠滿足多種角色;然而在協(xié)調(diào)這些工作時(shí),仍然涉及大量的項(xiàng)目開銷。

在《用于小波協(xié)處理器的基于 FPGA 的快速原型開發(fā)平臺(tái)》一文中,作者提倡使用協(xié)處理器架構(gòu)可以讓一個(gè) DSP 工程師高效地完成所有這些角色。對(duì)于這項(xiàng)研究,該團(tuán)隊(duì)開始在 MATLAB 的 Simulink 工具中設(shè)計(jì)和仿真所需的 DSP 功能。這有兩個(gè)主要功能,即:1) 通過仿真驗(yàn)證所需的性能;2) 作為基準(zhǔn),用以比較和參考未來(lái)的設(shè)計(jì)選擇。

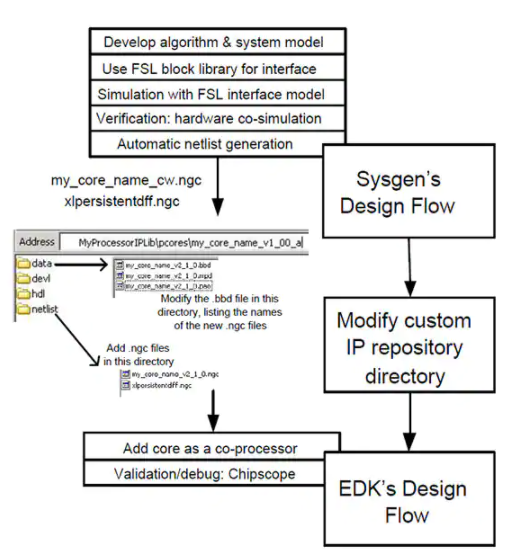

仿真之后,關(guān)鍵功能被確定下來(lái),并被劃分為不同的核心——這些是可以在 FPGA 內(nèi)合成的軟核組件和處理器。這項(xiàng)工作中最重要的一步是定義這些核心和組件之間的接口,并將數(shù)據(jù)交換性能與期望的、仿真的性能進(jìn)行比較。這一設(shè)計(jì)過程與 Xilinx 的嵌入式系統(tǒng)設(shè)計(jì)流程緊密結(jié)合,具體匯總見下圖 7。

?

圖 7:實(shí)現(xiàn)設(shè)計(jì)流程

通過將系統(tǒng)劃分為可整合的內(nèi)核,DSP 工程師可以專注于信號(hào)處理鏈中最關(guān)鍵的方面。她/他不需要成為硬件或 HDL 方面的專家,就可以在 FPGA 內(nèi)修改、路由或?qū)崿F(xiàn)不同的軟核處理器或組件。因此,只要設(shè)計(jì)者了解接口和數(shù)據(jù)的格式,他們就能完全控制信號(hào)路徑,并能完善系統(tǒng)的性能。

實(shí)證結(jié)果——離散余弦變換案例研究

實(shí)證結(jié)果不僅證實(shí)了協(xié)處理器架構(gòu)為嵌入式系統(tǒng)設(shè)計(jì)者提供的靈活性,而且還展示了現(xiàn)代 FPGA 工具的性能增強(qiáng)選項(xiàng)。像下面提到的增強(qiáng)功能,對(duì)于其他硬件架構(gòu)來(lái)說(shuō),可能無(wú)法使用或影響較小。離散余弦變換 (DCT) 被選為計(jì)算密集型算法,其從基于 C 的實(shí)現(xiàn)到基于 HDL 的實(shí)現(xiàn)的進(jìn)展是這些結(jié)果的核心。選擇 DCT 是因?yàn)檫@種算法可用于數(shù)字信號(hào)處理的模式識(shí)別和篩選 [8]。該實(shí)證結(jié)果基于一項(xiàng)實(shí)驗(yàn)室工作,由作者及其同事完成,獲得了 2020-2021 年的 Xilinx 聯(lián)盟合作伙伴認(rèn)證。

在這項(xiàng)工作中,使用了以下工具和設(shè)備:

Vivado HLS 2019 版

用于評(píng)估和仿真的設(shè)備是 xczu7ev-ffvc1156-2-e

從基于 C 語(yǔ)言的實(shí)現(xiàn)開始,DCT 算法接受兩個(gè) 16 位數(shù)的數(shù)組;數(shù)組 “a” 是 DCT 的輸入數(shù)組,數(shù)組 “b” 是 DCT 的輸出數(shù)組。因此,數(shù)據(jù)寬度 (DW) 被定義為 16,而數(shù)組內(nèi)的元素?cái)?shù) (N) 為 1024/DW,即 64。最后,DCT 矩陣的大小 (DCT_SIZE) 被置為 8,這意味著使用了一個(gè) 8×8 的矩陣。

在本文前提之下,基于 C 語(yǔ)言的算法實(shí)現(xiàn)允許設(shè)計(jì)者快速開發(fā)和驗(yàn)證算法的功能。盡管這是一個(gè)重要的考慮因素,但這種驗(yàn)證將功能置于了比執(zhí)行時(shí)間更高的權(quán)重。這種加權(quán)是允許的,因?yàn)樵撍惴ǖ淖罱K實(shí)現(xiàn)將在 FPGA 中進(jìn)行,硬件加速、循環(huán)展開和其他技術(shù)都是現(xiàn)成的。

?

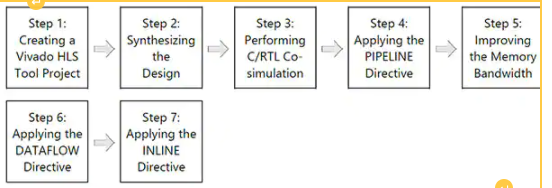

圖 8:Xilinx Vivado HLS 設(shè)計(jì)流程。

一旦 DCT 代碼在 Vivado HLS 工具中作為一個(gè)項(xiàng)目被創(chuàng)建,下一步就是開始為 FPGA 的實(shí)現(xiàn)進(jìn)行設(shè)計(jì)整合。在接下來(lái)的步驟中,將算法的執(zhí)行從 MCU 轉(zhuǎn)移到 FPGA 的一些最具影響力的好處變得更加明顯——作為參考,這一步相當(dāng)于上面討論的微控制器的系統(tǒng)管理里程碑。

現(xiàn)代 FPGA 工具允許進(jìn)行一系列的優(yōu)化和增強(qiáng),從而極大地提高復(fù)雜算法的性能。在分析結(jié)果之前,有一些重要的術(shù)語(yǔ)需要牢記。

?

表 2:FPGA 算法執(zhí)行優(yōu)化結(jié)果(資源利用)。

默認(rèn)

默認(rèn)的優(yōu)化設(shè)置來(lái)自于將基于 C 語(yǔ)言的算法轉(zhuǎn)換為可綜合 HDL 的未改變結(jié)果。沒有啟用任何優(yōu)化,這可以作為性能參考,以更好地了解其他優(yōu)化。

流水線內(nèi)循環(huán)

PIPELINE 指令指示 Vivado HLS 展開內(nèi)循環(huán),這樣新的數(shù)據(jù)就可以開始被處理,而現(xiàn)有的數(shù)據(jù)仍在流水線中。因此,新數(shù)據(jù)不必等待現(xiàn)有數(shù)據(jù)完成后再開始處理。

流水線外循環(huán)

通過對(duì)外循環(huán)應(yīng)用 PIPELINE 指令,外循環(huán)的操作現(xiàn)在被流水線化了。但內(nèi)循環(huán)的操作現(xiàn)在是同步進(jìn)行的。通過將其直接應(yīng)用于外循環(huán),延遲和間隔時(shí)間都減少了一半。

陣列劃分

這條指令將循環(huán)的內(nèi)容映射到陣列中,從而將所有的存儲(chǔ)器訪問扁平化到這些陣列中的單個(gè)元素。這樣做,會(huì)消耗更多的 RAM,但同樣的,這個(gè)算法的執(zhí)行時(shí)間也會(huì)減少一半。

數(shù)據(jù)流

這條指令允許設(shè)計(jì)者指定每個(gè)輸入讀數(shù)之間的目標(biāo)時(shí)鐘周期數(shù)。這條指令只支持頂層函數(shù)。只有暴露在這個(gè)級(jí)別的循環(huán)和函數(shù)才能從這個(gè)指令中受益。

內(nèi)聯(lián)

INLINE 指令平坦了所有循環(huán),包括內(nèi)循環(huán)和外循環(huán)。行和列進(jìn)程現(xiàn)在都可以并發(fā)執(zhí)行。所需的時(shí)鐘周期的數(shù)量被保持在最低水平,即使這樣也會(huì)消耗更多的 FPGA 資源。

結(jié)語(yǔ)

協(xié)處理器的硬件架構(gòu)為嵌入式設(shè)計(jì)者提供了一個(gè)高性能的平臺(tái),在整個(gè)開發(fā)過程中以及在產(chǎn)品發(fā)布后都能保持其設(shè)計(jì)靈活性。通過先在 C 或 C++ 中驗(yàn)證算法,進(jìn)程、數(shù)據(jù)和信號(hào)路徑以及關(guān)鍵功能都可以在相對(duì)較短的時(shí)間內(nèi)得到驗(yàn)證。然后,通過將處理器密集型算法轉(zhuǎn)換到協(xié)處理器 FPGA 中,設(shè)計(jì)者可以享受到硬件加速和更加模塊化設(shè)計(jì)的好處。

如果零件過時(shí)或需要優(yōu)化,相同的架構(gòu)可以允許這些變化。新的 MCU 和新的 FPGA 可以安裝到設(shè)計(jì)中,而所有的接口都可以保持相對(duì)不變。此外,由于 MCU 和 FPGA 都是可現(xiàn)場(chǎng)更新的,因此用戶的特定改變和優(yōu)化可以在現(xiàn)場(chǎng)和遠(yuǎn)程應(yīng)用。

最后,這種架構(gòu)將 MCU 的開發(fā)速度和可用性與 FPGA 的性能和可擴(kuò)展性融合到了一起。由于每個(gè)開發(fā)步驟都有優(yōu)化和性能提升,協(xié)處理器架構(gòu)可以滿足最具挑戰(zhàn)性的需求——無(wú)論是今天的設(shè)計(jì)還是以后的設(shè)計(jì)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論