摩爾定律指出,集成芯片可容納的晶體管數目約每18個月增加一倍,性能也將提升一倍。對于FPGA和數字IC設計開發的工程師們而言,感同身受的是,在龐大復雜的系統研發過程中,設計和驗證幾乎同等重要,甚至驗證工作將花費整個周期的70%~80%。

如何進行有效的功能驗證,是我們必須面對的課題。隨著芯片設計驗證技術的發展,SystemVerilog語言在業界獲得了廣泛應用。本文將介紹常用的驗證技術和方法。

無論是從事FPGA開發,還是數字IC設計,驗證是一個無法逃避的問題,是整個項目周期中極為重要的一環。

驗證是一個覆蓋面比較廣的課題,主要包括功能驗證、物理驗證、時序驗證等。我們常常涉及功能驗證,以確保設計能夠按照設計規范實現應有功能。為了完成功能驗證,我們需要搭建驗證平臺testbench,這也是業界最常用的驗證手段。

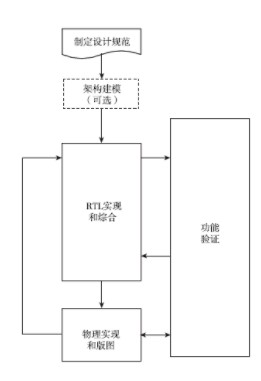

芯片設計流程

我們以專用芯片(ASIC)設計舉例,從設計規范到投片的設計流程,如圖:

與ASIC設計不同的是,在FPGA的設計流程中,沒有物理實現和版圖設計這一塊,因為FPGA已經是經過測封后的成品,只需要按照設計架構進行開發和驗證。因此,數字IC工程師與FPGA工程師常常可相互轉換。

RTL設計是將設計規范進行邏輯代碼實現的過程,我們常常使用verilog HDL或VHDL語言進行設計。通過采用相對合理的設計方案,在資源消耗、處理速率和時延上進行平衡。

功能驗證作為一個獨立模塊,但驗證過程卻相當復雜:定義測試用例,搭建測試環境,運行測試用例,以及保證功能覆蓋率。

怎樣進行有效功能驗證,確保設計可靠性,是我們最關心的課題。

驗證平臺

以FPGA開發為例,當我們完成功能模塊設計后,別急著進行綜合與實現,以及上板調試,進行行為仿真或功能仿真驗證是必要的。

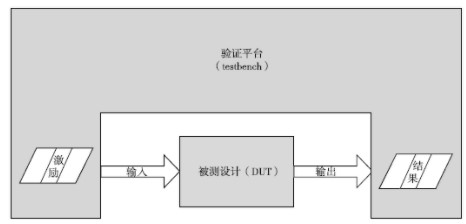

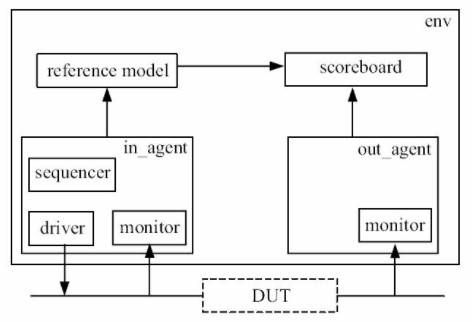

在功能驗證中,我們在被測設計(Design Under Test,DUT)外搭建驗證平臺,就像這樣:

驗證平臺可以用來做什么,又應該怎么做?

如上圖所示,對于DUT,我們需要通過testbench產生測試激勵,然后把測試激勵應用到DUT中,而DUT產生的輸出結果,我們需要進行檢查,看驗證測試是否通過,也就是,我們要確保輸出結果和期望一致。

產生用戶激勵常用方法:一種是提供確定輸入,進行直接測試(direct test);另外就是產生隨機數據,進行隨機測試(random test)。

通常,我們需要產生必要的使能信號、測試數據、地址等,通過DUT接口送入。

在高級驗證平臺種,激勵被工程師建模并封裝,進行事務級驗證(transaction based verification)。

驗證的目的,在于檢查DUT的輸出是否和期望一致。常用發方法和途徑有以下三種。

(1)通過視圖(波形窗口)檢查。我們通過仿真器查看信號波形,這也是常用的方法,不過也存在缺點,對于復雜的設計,信號接口眾多,數據量大,人眼視覺容易出現錯誤。

(2)自動化后處理對比。記錄DUT的輸出,通過運行腳本對比結果。我們可以將需要的結果寫為文件保存,導入MATLAB進行對比分析。也可將期望得到的結果與DUT輸出的結果通過程序自動對比分析。

(3)做一個實時監測器自動檢查。當然,監測器需要進行開發,當對比發生錯誤時,通過設置錯誤標志和打印信息提示,便于快速發現錯誤,節省仿真時間。

在功能驗證時,需要考慮主要功能點,提供比較完備的測試用例。對于FPGA功能模塊的驗證,或許用不上去搭建復雜的驗證平臺,但是這樣的驗證方法和思想依然可借鑒。在芯片設計領域,驗證工程師作為獨立崗位,承擔著設計把關的重任,一旦投片,基本就決定這款芯片的命運了。

像筆者這樣的FPGA工程師新手而言,主要任務就是算法實現。算法工程師把算法模型交給你,你就開始制定功能模塊實現方案、與前后級商討接口、RTL設計、仿真驗證到上板調試。相對于數字IC工程師的獨立性而言,FPGA工程師需要的技能也許更多:首先要懂算法,至少要理解算法處理流程;其次,常規技能要掌握,就是RTL設計能力;仿真驗證能力,如何設計好的testbench來驗證你的DUT,保證系統集成時不會有問題;最后還需要上板調試,需要掌握調試手段和驗證分析能力,對整個系統需要比較熟悉,常常涉及射頻和協議棧。隔行如隔山,精力也有限,因此挑戰必然存在。

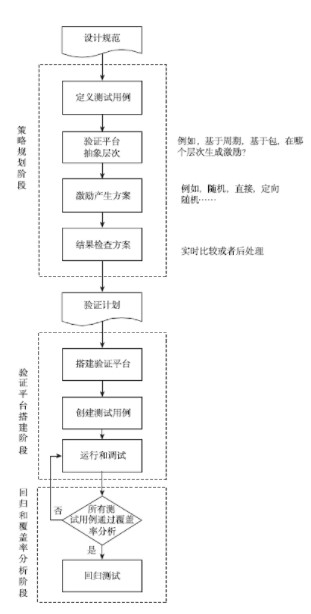

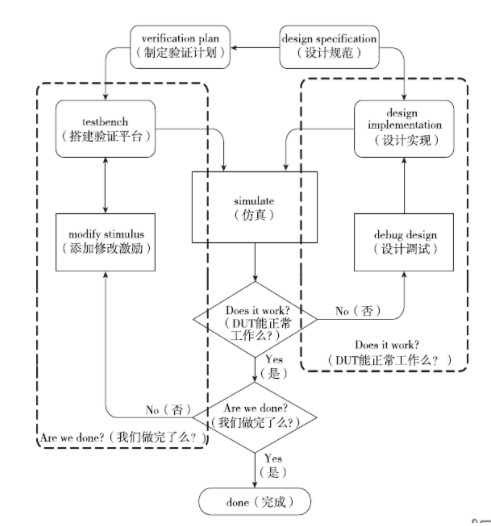

整個驗證流程,我們通過下圖來說明。

這里上圖提到的回歸測試和覆蓋率收斂,對于小白或新手而言,可能比較陌生,尤其是對于我這樣的非驗證崗人員。

一旦幾乎全部測試用例被成功執行,那么驗證就進入了回歸測試(regression test)和覆蓋率收斂階段。

回歸測試要求能夠周期的批處理運行,并且激勵能夠得到重現,成功或失敗都能夠自動檢查。

這個時候,所有測試應該在每天或每周做回歸周期性運行,查看覆蓋率,解決可能存在的bug,盡可能實現覆蓋率100%。

對于做FPGA的工程師而言,仿真時間太長,就不爽了。我們關心的是,功能驗證和邏輯驗證。覆蓋率沒有100%,也不要緊。不管是Vivado還是Quartus II自帶的仿真器,或者Modelsim,都可用來做仿真。使用Modelsim做來聯合仿真時,需要注意版本匹配和庫文件編譯。

驗證技術和方法學

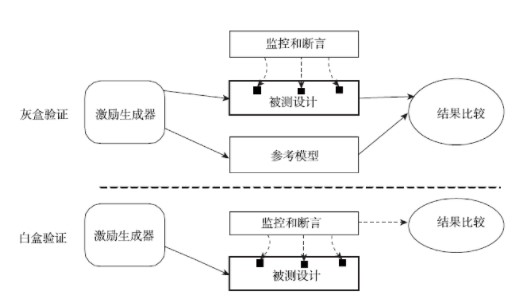

有三種常用驗證手段:白盒、黑盒和灰盒驗證。

三種主要驗證技術:形式驗證、仿真驗證和硬件加速驗證。

三種主要驗證方法學:隨機激勵生成、斷言驗證和覆蓋率驗證。

做功能驗證,目標就是驗證設計能否能夠像預期工作。然而,可能存在一些設計缺陷并沒有在輸出邊界暴露出來,檢測產生遺漏等。

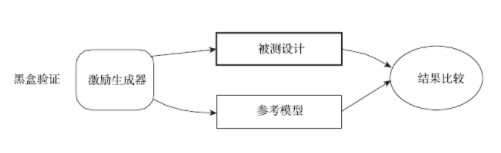

黑盒驗證:只通過其邊界信號來驗證一個模塊或設計的功能。驗證模型:

黑盒驗證有優點,也有缺點。優點就是看起來testbench搭建簡單,缺點就是DUT內部錯誤不好驗證。FPGA仿真驗證,就類似這樣。對于算法實現而言,常常利用FPGA仿真結果與MATLAB運算結果對比,比如畫個圖,畫條線,數據相減,計算方差等等。內部邏輯則可通過觀察波形來判斷,局限于復雜度不高的情況。

白盒驗證和灰盒則通過在設計內部或者外部輸出信號放置監控器或斷言來保證設計操作的正確性,不需要參考模型。

?

關于驗證技術中的形式驗證、仿真驗證和硬件輔助加速驗證等,其概念和使用方法,咱們不詳細去討論了,有興趣的朋友,去找幾本SystemVerilog驗證的參考書看看。

在功能驗證中,驗證工程師面臨著以下挑戰:

完備性:最大限度驗證DUT的行為,然而,怎樣去獲取必須被驗證的場景,提高覆蓋率。

可重用性:考慮如何優化驗證環境架構,使其可在不同場景下重用。若每做一個工程或迭代更新一個版本,都需要重新去設計testbench,那會累死三軍。

可靠性:在驗證中減少手工操作,以減少認為錯誤和節省時間,然而,搭建一個自動化系統也并非易事,需仔細分析和搭建,同時采用約束隨機進行驗證。

效率:在給定時間內,對驗證工作投入的產出最大化,提高驗證的成功率。對于設計師而言,我們常常采用重用技術,比如某個通用模塊,可在不同工程中使用,我們進行簡單移植修改即可。然而驗證就沒有這么幸運了,場景不同,激勵也不同,產生的結果也不同。

性能:驗證程序性能上的挑戰就是要如何最大化驗證程序的效率。驗證耗時費力,所以,每年在秋招春招時,大量芯片類企業招驗證工程師。筆者去年秋招時,本來投遞設計崗,然后當你筆試或者面試的時候,給你安排驗證的崗位。

功能驗證方法學,就是驗證電子系統的技術和科學。

前面,筆者在《FPGA工程師的核心競爭力—方法篇(一、二)》中,總結了UltraFast設計方法學,從而有效提高設計和效率。

而對于驗證這一環,也是有章法可循。

設計與驗證,相輔相成,如下圖:

DUT能正常工作嗎?測試功能點是什么?怎么測?功能對不對?我們做完驗證了嗎?簡直就是靈魂拷問。

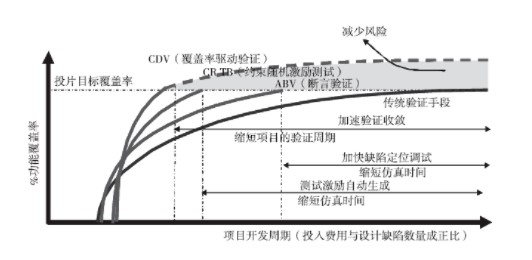

在驗證方法中,斷言驗證(ABV)、約束隨機激勵測試(CR TB)、覆蓋率驅動驗證(CDV)等技術將會極大提高驗證效率。縮短驗證周期,快速定位錯誤,加速激勵生成和有效實現驗證收斂。

對于FPGA工程師而言,在進行設計和仿真驗證中,最常用的語言是verilog HDL或VHDL,各有千秋。verilog HDL用起來比較靈活,有C語言基礎和硬件思維,就可以快速入門。VHDL語法嚴謹,有利于大規模系統集成。

SystemVerilog是業界新興的工程語言,基于verilog HDL進行了擴展,包括對硬件建模的擴展和驗證斷言方面的擴展。

SystemVerilog具有以下優點:

(1)單一,同時支持設計和驗證的標準語言。

(2)支持約束隨機的產生。

(3)支持覆蓋率統計分析。

(4)支持斷言驗證。

(5)面向對象的編程結構,有助于采用事務級的驗證和提高驗證的重用性。

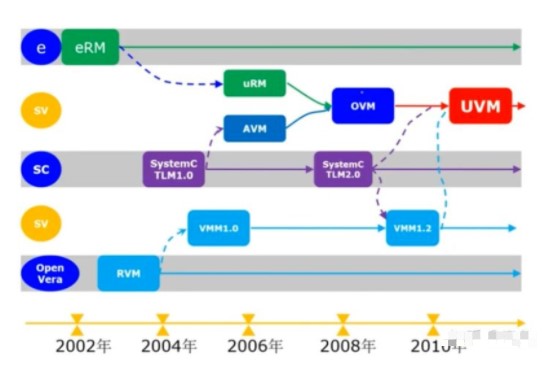

基于SystemVerilog的驗證方法學有:OVM、VMM和UVM。目前,業界最流行的是UVM。相信你在或將會在今后的“金九銀十”的秋招時,會被問到是否對UVM有所了解。如果你是看到本文了解到UVM這個概念,那么趕緊再深入了解一下。

下圖是驗證方法學的發展時間線:

UVM (Universal Verification Methodology)通用驗證方法學。它起源于 OVM(Open Verification Methdology),其正式版是在2011年2月由Accellera推出的,得到了Synopsys、Cadence和Mentor的一致支持。UVM幾乎完全繼承了OVM,同時又采納了Synopsys在VMM中的寄存器解決方案RAL。UVM繼承了OVM和VMM的優點,克服了各自的缺點,代表了驗證方法學的發展方向。

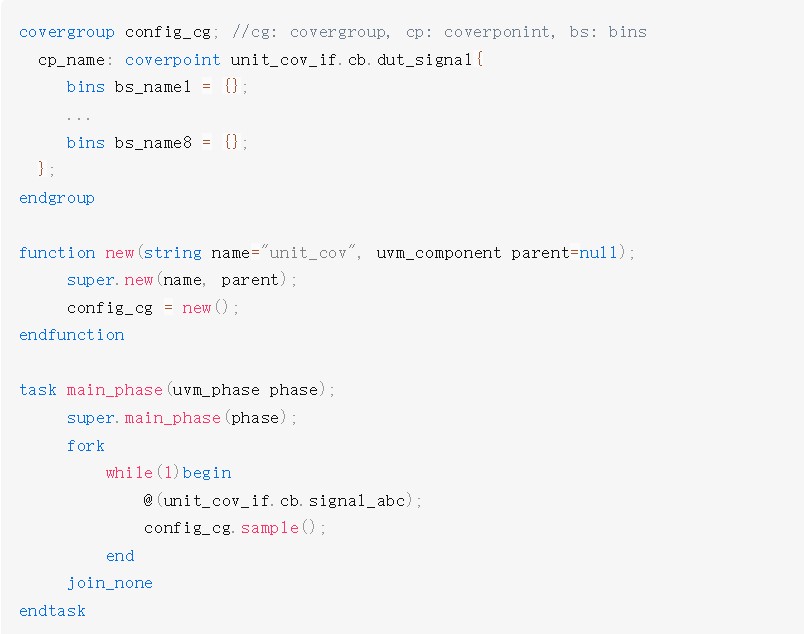

下圖是典型的UVM驗證平臺框圖:

由于SystemVerilog可完全兼容Verilog,所以你在.sv文件中加入幾行Verilog語法的程序也不會出錯。比如讀寫文件的操作,前幾天,筆者也不了解這個SystemVerilog的用法,就在微信群里問這種小兒科問題:

“SystemVerilog和Verilog在讀寫文件操作上,有什么區別?”

$fopen,$readmemh/$readmemb,$fwrite,$fclose依然可用。

SystemVerilog中可操作字符串,這對于存儲初始化文件(.mif)的讀操作比較友好,并且可跳過文件中的注釋。

SystemVerilog中信號定義,可用logic來代替Verilog中的reg和wire。

關于任務task的使用,文件指針等等,可以參閱SystemVerilog設計和驗證的書籍,講得很詳細。

審核編輯:劉清

電子發燒友App

電子發燒友App

評論